Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

04 Cache Memory

Caricato da

Sangeetha ShankaranCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

04 Cache Memory

Caricato da

Sangeetha ShankaranCopyright:

Formati disponibili

William Stallings

Computer Organization

and Architecture

8th Edition

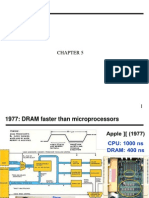

Chapter 4 Chapter 4

Cache Memory

Characteristics

Location

Capacity

Unit of transfer

Access method

Performance Performance

Physical type

Physical characteristics

Organisation

Location

CPU

Internal

External

Capacity

Word size

The natural unit of organisation

Number of words

or Bytes

Unit of Transfer

Internal

Usually governed by data bus width

External

Usually a block which is much larger than a

word

Addressable unit Addressable unit

Smallest location which can be uniquely

addressed

Word internally

Cluster on M$ disks

Access Methods (1)

Sequential

Start at the beginning and read through in

order

Access time depends on location of data and

previous location

e.g. tape e.g. tape

Direct

Individual blocks have unique address

Access is by jumping to vicinity plus

sequential search

Access time depends on location and previous

location

e.g. disk

Access Methods (2)

Random

Individual addresses identify locations exactly

Access time is independent of location or

previous access

e.g. RAM

Associative Associative

Data is located by a comparison with contents

of a portion of the store

Access time is independent of location or

previous access

e.g. cache

Memory Hierarchy

Registers

In CPU

Internal or Main memory

May include one or more levels of cache

RAM

External memory

Backing store

Memory Hierarchy - Diagram

Performance

Access time

Time between presenting the address and

getting the valid data

Memory Cycle time

Time may be required for the memory to

recover before next access recover before next access

Cycle time is access + recovery

Transfer Rate

Rate at which data can be moved

Physical Types

Semiconductor

RAM

Magnetic

Disk & Tape

Optical Optical

CD & DVD

Others

Bubble

Hologram

Physical Characteristics

Decay

Volatility

Erasable

Power consumption

Organisation

Physical arrangement of bits into words

Not always obvious

e.g. interleaved

The Bottom Line

How much?

Capacity

How fast?

Time is money

How expensive? How expensive?

Hierarchy List

Registers

L1 Cache

L2 Cache

Main memory

Disk cache Disk cache

Disk

Optical

Tape

So you want fast?

It is possible to build a computer which

uses only static RAM (see later)

This would be very fast

This would need no cache

How can you cache cache?

This would cost a very large amount

Locality of Reference

During the course of the execution of a

program, memory references tend to

cluster

e.g. loops

Cache

Small amount of fast memory

Sits between normal main memory and

CPU

May be located on CPU chip or module

Cache and Main Memory

Cache and Main Memory Hit/miss ratio

Cache/Main Memory Structure

Cache operation overview

CPU requests contents of memory location

Check cache for this data

If present, get from cache (fast)

If not present, read required block from

main memory to cache main memory to cache

Then deliver from cache to CPU

Cache includes tags to identify which

block of main memory is in each cache

slot

Cache Read Operation - Flowchart

Cache Design

Addressing

Size

Mapping Function

Replacement Algorithm

Write Policy Write Policy

Block Size

Number of Caches

Cache Addressing Virtual Memory

What is Virtual Memory ?

Access memory from logical point of view,

disregarding the amount of physical memory

available.

Address fields of machine instructions contain

virtual addresses. virtual addresses.

For reads and writes, a hardware Memory

Management Unit (MMU) translates logical into

physical addresses.

Allows to give applications a full (virtual)

memory space starting at address 0.

Virtual Memory essential to support OSs.

Most non-embedded processors support

Virtual Memory

Cache Addressing

Where does cache sit?

Between processor and virtual memory management

unit (MMU).

Between MMU and main memory

Logical cache (virtual cache) stores data using

virtual addresses

Processor accesses cache directly, not thorough physical Processor accesses cache directly, not thorough physical

cache

Cache access faster, before MMU address translation

Virtual addresses use same address space for different

applications

Must flush cache on each context switch

Physical cache stores data using main memory

physical addresses

Logical vs. Physical Caches

Size does matter

Cost

More cache is expensive

Speed

More cache is faster (up to a point)

Checking cache for data takes time

Typical Cache Organization

Comparison of Cache Sizes

Processor Type

Year of

Introduction

L1 cache L2 cache L3 cache

IBM 360/85 Mainframe 1968 16 to 32 KB

PDP-11/70 Minicomputer 1975 1 KB

VAX 11/780 Minicomputer 1978 16 KB

IBM 3033 Mainframe 1978 64 KB

IBM 3090 Mainframe 1985 128 to 256 KB

Intel 80486 PC 1989 8 KB

Pentium PC 1993 8 KB/8 KB 256 to 512 KB

PowerPC 601 PC 1993 32 KB PowerPC 601 PC 1993 32 KB

PowerPC 620 PC 1996 32 KB/32 KB

PowerPC G4 PC/server 1999 32 KB/32 KB 256 KB to 1 MB 2 MB

IBM S/390 G4 Mainframe 1997 32 KB 256 KB 2 MB

IBM S/390 G6 Mainframe 1999 256 KB 8 MB

Pentium 4 PC/server 2000 8 KB/8 KB 256 KB

IBM SP

High-end server/

supercomputer

2000 64 KB/32 KB 8 MB

CRAY MTAb Supercomputer 2000 8 KB 2 MB

Itanium PC/server 2001 16 KB/16 KB 96 KB 4 MB

SGI Origin 2001 High-end server 2001 32 KB/32 KB 4 MB

Itanium 2 PC/server 2002 32 KB 256 KB 6 MB

IBM POWER5 High-end server 2003 64 KB 1.9 MB 36 MB

CRAY XD-1 Supercomputer 2004 64 KB/64 KB 1MB

Mapping Function

Cache of 64kByte

Cache block of 4 bytes

i.e. cache is 16k (2

14

) lines of 4 bytes

16MBytes main memory

24 bit address 24 bit address

(2

24

=16M)

Direct Mapping

Each block of main memory maps to only

one cache line

i.e. if a block is in cache, it must be in one

specific place

Address is in two parts

Least Significant w bits identify unique Least Significant w bits identify unique

word

Most Significant s bits specify one

memory block

The MSBs are split into a cache line field r

and a tag of s-r (most significant)

Direct Mapping

Address Structure

Tag s-r Line or Slot r Word w

8

14 2

24 bit address

2 bit word identifier (4 byte block) 2 bit word identifier (4 byte block)

22 bit block identifier

8 bit tag (=22-14)

14 bit slot or line

No two blocks in the same line have the same Tag field

Check contents of cache by finding line and checking Tag

Direct Mapping from Cache to Main Memory

Direct Mapping

Mapping: i = j modulo m

Cache line number = i

Main memory block number = j

Number of lines in cache = m Number of lines in cache = m

Direct Mapping

Cache Line Table

Cache line Main Memory blocks held

0 0, m, 2m, 3m2s-m

1 1,m+1, 2m+12s-m+1 1 1,m+1, 2m+12s-m+1

m-1 m-1, 2m-1,3m-12s-1

Direct Mapping Cache Organization

Direct

Mapping

Example

Direct Mapping Summary

Address length = (s + w) bits

Number of addressable units = 2s+w

words or bytes

Block size = line size = 2w words or bytes

Number of blocks in main memory = 2s+ Number of blocks in main memory = 2s+

w/2w = 2s

Number of lines in cache = m = 2r

Size of tag = (s r) bits

Direct Mapping pros & cons

Simple

Inexpensive

Fixed location for given block

If a program accesses 2 blocks that map to

the same line repeatedly, cache misses are

very high very high

Victim Cache

Lower miss penalty

Remember what was discarded

Already fetched

Use again with little penalty

Fully associative Fully associative

4 to 16 cache lines

Between direct mapped L1 cache and next

memory level

Associative Mapping

A main memory block can load into any

line of cache

Memory address is interpreted as tag and

word

Tag uniquely identifies block of memory

Every lines tag is examined for a match

Cache searching gets expensive

Flexibility of deciding which block to

replace when a new block is to be read

into cache.

Associative Mapping from

Cache to Main Memory

Fully Associative Cache Organization

Associative

Mapping

Example

Tag 22 bit

Word

2 bit

Associative Mapping

Address Structure

22 bit tag stored with each 32 bit block of data

Compare tag field with tag entry in cache to Compare tag field with tag entry in cache to

check for hit

Least significant 2 bits of address identify which

8 bit word is required from 32 bit data block

e.g.

Address Tag Data Cache line

FFFFFC FFFFFC 24682468 3FFF

Associative Mapping Summary

Address length = (s + w) bits

Number of addressable units = 2s+w

words or bytes

Block size = line size = 2w words or bytes

Number of blocks in main memory = 2s+ Number of blocks in main memory = 2s+

w/2w = 2s

Number of lines in cache = undetermined

Size of tag = s bits

Set Associative Mapping

Cache is divided into a number of sets

Each set contains a number of lines

A given block maps to any line in a given

set

e.g. Block B can be in any line of set i

e.g. 2 lines per set

2 way associative mapping

A given block can be in one of 2 lines in only

one set

Set Associative Mapping

Example

13 bit set number

Block number in main memory is modulo

2

13

000000, 00A000, 00B000, 00C000 map

to same set

Mapping From Main Memory to Cache:

v Associative

Mapping From Main Memory to Cache:

k-way Associative

K-Way Set Associative Cache

Organization

Set Associative Mapping

Address Structure

Use set field to determine cache set to

look in

Tag 9 bit

Set 13 bit

Word

2 bit

look in

Compare tag field to see if we have a hit

e.g

Address Tag Data Set

number

1FF 7FFC 1FF 12345678 1FFF

001 7FFC 001 11223344 1FFF

Two Way Set Associative Mapping

Example

Set Associative Mapping Summary

Address length = (s + w) bits

Number of addressable units = 2s+w

words or bytes

Block size = line size = 2w words or bytes

Number of blocks in main memory = 2d Number of blocks in main memory = 2d

Number of lines in set = k

Number of sets = v = 2d

Number of lines in cache = kv = k * 2d

Size of tag = (s d) bits

Direct and Set Associative Cache

Performance Differences

Significant up to at least 64kB for 2-way

Difference between 2-way and 4-way at

4kB much less than 4kB to 8kB

Cache complexity increases with

associativity

Not justified against increasing cache to

8kB or 16kB

Above 32kB gives no improvement

(simulation results)

Figure 4.16

Varying Associativity over Cache Size

H

i

t

r

a

t

i

o

0.4

0.5

0.6

0.7

0.8

0.9

1.0

0.0

1k 2k 4k 8k 16k

Cachesize(bytes)

direct

2-way

4-way

8-way

16-way

32k 64k 128k 256k 512k 1M

0.1

0.2

0.3

0.4

Replacement Algorithms (1)

Direct mapping

No choice

Each block only maps to one line

Replace that line

Replacement Algorithms (2)

Associative & Set Associative

Hardware implemented algorithm (speed)

Least Recently used (LRU)

e.g. in 2 way set associative

Which of the 2 block is lru?

First in first out (FIFO) First in first out (FIFO)

replace block that has been in cache longest

Least frequently used

replace block which has had fewest hits

Random

Write Policy

Must not overwrite a cache block unless

main memory is up to date

Multiple CPUs may have individual caches

I/O may address main memory directly

Write through

All writes go to main memory as well as

cache

Multiple CPUs can monitor main memory

traffic to keep local (to CPU) cache up to

date

Lots of traffic Lots of traffic

Slows down writes

Remember bogus write through caches!

Write back

Updates initially made in cache only

Update bit for cache slot is set when

update occurs

If block is to be replaced, write to main

memory only if update bit is set

Other caches get out of sync

I/O must access main memory through

cache

N.B. 15% of memory references are

writes

Line Size

Retrieve not only desired word but a number of

adjacent words as well

Increased block size will increase hit ratio at first

the principle of locality

Hit ratio will decreases as block becomes even

bigger

Probability of using newly fetched information becomes

less than probability of reusing replaced less than probability of reusing replaced

Larger blocks

Reduce number of blocks that fit in cache

Data overwritten shortly after being fetched

Each additional word is less local so less likely to be

needed

No definitive optimum value has been found

8 to 64 bytes seems reasonable

For HPC systems, 64- and 128-byte most

common

Multilevel Caches

High logic density enables caches on chip

Faster than bus access

Frees bus for other transfers

Common to use both on and off chip

cache

L1 on chip, L2 off chip in static RAM L1 on chip, L2 off chip in static RAM

L2 access much faster than DRAM or ROM

L2 often uses separate data path

L2 may now be on chip

Resulting in L3 cache

Bus access or now on chip

Hit Ratio (L1 & L2)

For 8 kbytes and 16 kbyte L1

Unified v Split Caches

One cache for data and instructions or

two, one for data and one for instructions

Advantages of unified cache

Higher hit rate

Balances load of instruction and data fetch

Only one cache to design & implement Only one cache to design & implement

Advantages of split cache

Eliminates cache contention between

instruction fetch/decode unit and execution

unit

Important in pipelining

Pentium 4 Cache

80386 no on chip cache

80486 8k using 16 byte lines and four way set

associative organization

Pentium (all versions) two on chip L1 caches

Data & instructions

Pentium III L3 cache added off chip

Pentium 4 Pentium 4

L1 caches

8k bytes

64 byte lines

four way set associative

L2 cache

Feeding both L1 caches

256k

128 byte lines

8 way set associative

L3 cache on chip

Intel Cache Evolution

Problem Solution

Processor on which feature

first appears

External memory slower than the system bus.

Add external cache using faster

memory technology.

386

Increased processor speed results in external bus becoming a

bottleneck for cache access.

Move external cache on-chip,

operating at the same speed as the

processor.

486

Internal cache is rather small, due to limited space on chip

Add external L2 cache using faster

technology than main memory

486

Contention occurs when both the Instruction Prefetcher and

the Execution Unit simultaneously require access to the

cache. In that case, the Prefetcher is stalled while the

Execution Units data access takes place.

Create separate data and instruction

caches.

Pentium

Increased processor speed results in external bus becoming a

bottleneck for L2 cache access.

Create separate back-side bus that

runs at higher speed than the main

(front-side) external bus. The BSB is

dedicated to the L2 cache.

Pentium Pro

Move L2 cache on to the processor

chip.

Pentium II

Some applications deal with massive databases and must

have rapid access to large amounts of data. The on-chip

caches are too small.

Add external L3 cache. Pentium III

Move L3 cache on-chip. Pentium 4

Pentium 4 Block Diagram

Pentium 4 Core Processor

Fetch/Decode Unit

Fetches instructions from L2 cache

Decode into micro-ops

Store micro-ops in L1 cache

Out of order execution logic

Schedules micro-ops

Based on data dependence and resources

May speculatively execute

Execution units

Execute micro-ops

Data from L1 cache

Results in registers

Memory subsystem

L2 cache and systems bus

Pentium 4 Design Reasoning

Decodes instructions into RISC like micro-ops before L1

cache

Micro-ops fixed length

Superscalar pipelining and scheduling

Pentium instructions long & complex

Performance improved by separating decoding from

scheduling & pipelining

(More later ch14) (More later ch14)

Data cache is write back

Can be configured to write through

L1 cache controlled by 2 bits in register

CD = cache disable

NW = not write through

2 instructions to invalidate (flush) cache and write back then

invalidate

L2 and L3 8-way set-associative

Line size 128 bytes

ARM Cache Features

Core Cache

Type

Cache Size (kB) Cache Line Size

(words)

Associativity Location Write Buffer

Size (words)

ARM720T Unified 8 4 4-way Logical 8

ARM920T Split 16/16 D/I 8 64-way Logical 16

ARM926EJ-S Split 4-128/4-128 D/I 8 4-way Logical 16

ARM1022E Split 16/16 D/I 8 64-way Logical 16

ARM1026EJ-S Split 4-128/4-128 D/I 8 4-way Logical 8

Intel StrongARM Split 16/16 D/I 4 32-way Logical 32

Intel Xscale Split 32/32 D/I 8 32-way Logical 32

ARM1136-JF-S Split 4-64/4-64 D/I 8 4-way Physical 32

ARM Cache Organization

Small FIFO write buffer

Enhances memory write performance

Between cache and main memory

Small c.f. cache

Data put in write buffer at processor clock

speed speed

Processor continues execution

External write in parallel until empty

If buffer full, processor stalls

Data in write buffer not available until written

So keep buffer small

ARM Cache and Write Buffer Organization

Internet Sources

Manufacturer sites

Intel

ARM

Search on cache

Potrebbero piacerti anche

- 04 - Cache Memory (Compatibility Mode)Documento12 pagine04 - Cache Memory (Compatibility Mode)John PhanNessuna valutazione finora

- Cache MemoryDocumento72 pagineCache MemoryMaroun Bejjany67% (3)

- William Stallings Computer Organization and Architecture 7th Edition Cache MemoryDocumento67 pagineWilliam Stallings Computer Organization and Architecture 7th Edition Cache Memorydilshadsabir8911Nessuna valutazione finora

- Stallings Computer Organization and Architecture 6th Edition Chapter 4 Cache MemoryDocumento55 pagineStallings Computer Organization and Architecture 6th Edition Chapter 4 Cache Memorydarwinvargas2011Nessuna valutazione finora

- William Stallings Computer Organization and Architecture 7th Edition Chapter 4 Cache Memory CharacteristicsDocumento57 pagineWilliam Stallings Computer Organization and Architecture 7th Edition Chapter 4 Cache Memory CharacteristicsDurairajan AasaithambaiNessuna valutazione finora

- William Stallings Computer Organization and Architecture 7th Edition Cache MemoryDocumento57 pagineWilliam Stallings Computer Organization and Architecture 7th Edition Cache MemorySumaiya KhanNessuna valutazione finora

- William Stallings Computer Organization and Architecture 8th Edition Cache MemoryDocumento71 pagineWilliam Stallings Computer Organization and Architecture 8th Edition Cache MemoryRehman HazratNessuna valutazione finora

- 4.1 Computer Memory System OverviewDocumento12 pagine4.1 Computer Memory System Overviewmtenay1Nessuna valutazione finora

- 04_Cache MemoryDocumento47 pagine04_Cache MemoryuabdulgwadNessuna valutazione finora

- William Stallings Computer Organization and Architecture 6th Edition Cache MemoryDocumento45 pagineWilliam Stallings Computer Organization and Architecture 6th Edition Cache MemoryFatima ZehraNessuna valutazione finora

- William Stallings Computer Organization and Architecture 8th Edition Cache MemoryDocumento71 pagineWilliam Stallings Computer Organization and Architecture 8th Edition Cache MemoryBum TumNessuna valutazione finora

- William Stallings Computer Organization and Architecture 7th Edition Cache MemoryDocumento57 pagineWilliam Stallings Computer Organization and Architecture 7th Edition Cache MemoryMashail AliNessuna valutazione finora

- William Stallings Computer Organization and Architecture 7th EditionDocumento57 pagineWilliam Stallings Computer Organization and Architecture 7th EditionAthreyaNessuna valutazione finora

- Computer Organization and Architecture: Cache MemoryDocumento57 pagineComputer Organization and Architecture: Cache MemoryRyan R. Sarco100% (1)

- Cache Memory-Direct MappingDocumento30 pagineCache Memory-Direct MappingEswin AngelNessuna valutazione finora

- Characteristics Location Capacity Unit of Transfer Access Method Performance Physical Type Physical Characteristics OrganisationDocumento53 pagineCharacteristics Location Capacity Unit of Transfer Access Method Performance Physical Type Physical Characteristics Organisationapi-26594847Nessuna valutazione finora

- Characteristics Location Capacity Unit of Transfer Access Method Performance Physical Type Physical Characteristics OrganisationDocumento53 pagineCharacteristics Location Capacity Unit of Transfer Access Method Performance Physical Type Physical Characteristics OrganisationMarkNessuna valutazione finora

- William Stallings Computer Organization and Architecture 8th Edition Cache MemoryDocumento71 pagineWilliam Stallings Computer Organization and Architecture 8th Edition Cache MemoryRudi GunawanNessuna valutazione finora

- Stallings Computer Architecture 8th Edition Cache Memory CharacteristicsDocumento71 pagineStallings Computer Architecture 8th Edition Cache Memory CharacteristicsDoc TelNessuna valutazione finora

- Characteristics Location Capacity Unit of Transfer Access Method Performance Physical Type Physical Characteristics OrganisationDocumento53 pagineCharacteristics Location Capacity Unit of Transfer Access Method Performance Physical Type Physical Characteristics OrganisationRonel Salazar BlanzaNessuna valutazione finora

- Cache Memory-Associative MappingDocumento23 pagineCache Memory-Associative MappingEswin AngelNessuna valutazione finora

- Unit 1 Part 2 (Chapter 4) Cache MemoryDocumento53 pagineUnit 1 Part 2 (Chapter 4) Cache MemoryNITHIYA PAUL 1847244Nessuna valutazione finora

- Internal Memory Organization and ManagementDocumento43 pagineInternal Memory Organization and ManagementMeena ShahNessuna valutazione finora

- Lecture 4Documento35 pagineLecture 4Meena ShahNessuna valutazione finora

- William Stallings Computer Organization and Architecture 8th Edition Cache MemoryDocumento71 pagineWilliam Stallings Computer Organization and Architecture 8th Edition Cache MemoryAqib abdullahNessuna valutazione finora

- William Stallings Computer Organization and Architecture 7th Edition Cache MemoryDocumento51 pagineWilliam Stallings Computer Organization and Architecture 7th Edition Cache MemoryAndi Didik Wira PutraNessuna valutazione finora

- William Stallings Computer Organization and Architecture 8th Edition Cache MemoryDocumento72 pagineWilliam Stallings Computer Organization and Architecture 8th Edition Cache Memoryanon_540203628Nessuna valutazione finora

- Cache + Associations Ch-4Documento52 pagineCache + Associations Ch-4ahsan2020azizNessuna valutazione finora

- Computer Org and Arch: R.MageshDocumento48 pagineComputer Org and Arch: R.Mageshmage9999Nessuna valutazione finora

- Cache MemoryDocumento39 pagineCache MemoryhariprasathkNessuna valutazione finora

- William Stallings Computer Organization and Architecture 7th Edition Cache MemoryDocumento64 pagineWilliam Stallings Computer Organization and Architecture 7th Edition Cache Memoryrooop sagar GaimnaniNessuna valutazione finora

- Memory Hierarchy: REG Cache Main SecondaryDocumento37 pagineMemory Hierarchy: REG Cache Main SecondaryHimeshParyaniNessuna valutazione finora

- COSS - Contact Session - 4Documento34 pagineCOSS - Contact Session - 4Prasana VenkateshNessuna valutazione finora

- Computer Arch 06Documento41 pagineComputer Arch 06NaheedNessuna valutazione finora

- Computer Organization & Architecture: Cache MemoryDocumento52 pagineComputer Organization & Architecture: Cache Memorymuhammad farooqNessuna valutazione finora

- William Stallings Computer Organization and Architecture 7th Edition Cache MemoryDocumento66 pagineWilliam Stallings Computer Organization and Architecture 7th Edition Cache MemorySanket GawdeNessuna valutazione finora

- From William Stalling 8 Edition + OthersDocumento75 pagineFrom William Stalling 8 Edition + OthersTirusew AbereNessuna valutazione finora

- CH 4.ppt Type IDocumento60 pagineCH 4.ppt Type Ilaraibnawaz86Nessuna valutazione finora

- Cache MappingDocumento44 pagineCache MappingxoeaeoxNessuna valutazione finora

- Module 4: Memory System Organization & ArchitectureDocumento97 pagineModule 4: Memory System Organization & ArchitectureSurya SunderNessuna valutazione finora

- Chap 6Documento48 pagineChap 6siddhiNessuna valutazione finora

- COSS - Contact Session - 4 - With AnnotatonDocumento44 pagineCOSS - Contact Session - 4 - With Annotatonnotes.chandanNessuna valutazione finora

- Lect11 Cache BasicsDocumento22 pagineLect11 Cache BasicsVishal MittalNessuna valutazione finora

- Memory OrganizationDocumento57 pagineMemory OrganizationvpriyacseNessuna valutazione finora

- Chapter 5Documento87 pagineChapter 5supersibas11Nessuna valutazione finora

- Cache Memory - January 2014Documento90 pagineCache Memory - January 2014Dare DevilNessuna valutazione finora

- Lecture-04, Adv. Computer Architecture, CS-522Documento39 pagineLecture-04, Adv. Computer Architecture, CS-522torabgullNessuna valutazione finora

- Lecture-04 & 05, Adv. Computer Architecture, CS-522Documento63 pagineLecture-04 & 05, Adv. Computer Architecture, CS-522torabgullNessuna valutazione finora

- Lecture 5Documento24 pagineLecture 5Meena ShahNessuna valutazione finora

- Computer Organization: Lec #10: Cache Memory Bnar MustafaDocumento22 pagineComputer Organization: Lec #10: Cache Memory Bnar Mustafazara qojo (زارا)Nessuna valutazione finora

- 13 MemoryDocumento13 pagine13 MemoryNishanthoraNessuna valutazione finora

- ACA Unit 6 - Part - Virtual Memory Notes - U6Documento4 pagineACA Unit 6 - Part - Virtual Memory Notes - U6Supriya BirjeNessuna valutazione finora

- Module 5.3Documento39 pagineModule 5.3Asha DurafeNessuna valutazione finora

- Lecutre-8 Cache MemoryDocumento25 pagineLecutre-8 Cache MemoryMd. Firoz HasanNessuna valutazione finora

- CS 333 Reading Assignment and Sample ProblemsDocumento6 pagineCS 333 Reading Assignment and Sample ProblemsKaruppanan KomathyNessuna valutazione finora

- Memories: Reviewing Memory Hierarchy ConceptsDocumento37 pagineMemories: Reviewing Memory Hierarchy ConceptsshubhamvslaviNessuna valutazione finora

- Build Your Own Distributed Compilation Cluster: A Practical WalkthroughDa EverandBuild Your Own Distributed Compilation Cluster: A Practical WalkthroughNessuna valutazione finora

- CS2363 2 Marks Imp PrintDocumento15 pagineCS2363 2 Marks Imp PrintSangeetha ShankaranNessuna valutazione finora

- Jee Main 2014 Key PhysicsDocumento3 pagineJee Main 2014 Key PhysicsSangeetha ShankaranNessuna valutazione finora

- It64 Embedded Systems: Marthandam College of Engineering and TechnologyDocumento18 pagineIt64 Embedded Systems: Marthandam College of Engineering and TechnologyJoshua DuffyNessuna valutazione finora

- Eee OopsDocumento1 paginaEee OopsSangeetha ShankaranNessuna valutazione finora

- Eee OopsDocumento1 paginaEee OopsSangeetha ShankaranNessuna valutazione finora

- UNIT I Error Correction Method - ExtraDocumento9 pagineUNIT I Error Correction Method - ExtraLiNuNessuna valutazione finora

- Eee OopsDocumento1 paginaEee OopsSangeetha ShankaranNessuna valutazione finora

- Ooad Documentation Mc9248Documento138 pagineOoad Documentation Mc9248Sangeetha ShankaranNessuna valutazione finora

- B.e.cseDocumento107 pagineB.e.cseSangeetha ShankaranNessuna valutazione finora

- 2 MarksDocumento11 pagine2 MarksMonisha TolentinaNessuna valutazione finora

- Jee Main 2014 Key PhysicsDocumento3 pagineJee Main 2014 Key PhysicsSangeetha ShankaranNessuna valutazione finora

- 2010Documento1 pagina2010Sangeetha ShankaranNessuna valutazione finora

- COADocumento137 pagineCOAThonta DariNessuna valutazione finora

- Input Output Organization 11Documento60 pagineInput Output Organization 11amit_coolbuddy20Nessuna valutazione finora

- Me 2303 - Design of Machine Elements December 2010Documento3 pagineMe 2303 - Design of Machine Elements December 2010Ilaya Perumal K0% (1)

- SyllabusDocumento2 pagineSyllabusSangeetha ShankaranNessuna valutazione finora

- FDP Cse Jun2013Documento2 pagineFDP Cse Jun2013Sangeetha ShankaranNessuna valutazione finora

- Sample Resume 2Documento1 paginaSample Resume 2Sangeetha ShankaranNessuna valutazione finora

- SS ManualDocumento49 pagineSS ManualSangeetha ShankaranNessuna valutazione finora

- Object Oriented Programming ConceptsDocumento17 pagineObject Oriented Programming ConceptsPawan KaswanNessuna valutazione finora

- Java - REC - QB - 2nd EditionDocumento7 pagineJava - REC - QB - 2nd EditionSangeetha ShankaranNessuna valutazione finora

- New Rich Text DocumentDocumento1 paginaNew Rich Text DocumentSangeetha ShankaranNessuna valutazione finora

- Computernetwork For InterviewDocumento9 pagineComputernetwork For InterviewSangeetha ShankaranNessuna valutazione finora

- Unit-Ii Software RequirementsDocumento3 pagineUnit-Ii Software RequirementsSangeetha ShankaranNessuna valutazione finora

- Fundamentals of Computing & Computer Programming UNIT V - 2 Marks Functions and PointersDocumento13 pagineFundamentals of Computing & Computer Programming UNIT V - 2 Marks Functions and PointersSangeetha ShankaranNessuna valutazione finora

- Chapter 1 EditDocumento463 pagineChapter 1 Edittthanhhoa17112003Nessuna valutazione finora

- PGDCA Assignments 2021: Computer Applications, C, PythonDocumento10 paginePGDCA Assignments 2021: Computer Applications, C, PythonJimmy JohnNessuna valutazione finora

- C6x Assembly Programming EssentialsDocumento20 pagineC6x Assembly Programming EssentialsErnesto NadlorNessuna valutazione finora

- Courses Scheme & SyllabusDocumento86 pagineCourses Scheme & SyllabusAnubhav KohliNessuna valutazione finora

- Microcontroller Chapter 02Documento24 pagineMicrocontroller Chapter 02Syavira AmalyaNessuna valutazione finora

- CSE105 Computer Organization Model QuestionDocumento2 pagineCSE105 Computer Organization Model QuestionK SriNessuna valutazione finora

- Introduction to Embedded Systems Definition and ComponentsDocumento28 pagineIntroduction to Embedded Systems Definition and ComponentsCheril Mehta0% (1)

- Intellectual Property Case - SynercomDocumento3 pagineIntellectual Property Case - SynercomAlpha BetaNessuna valutazione finora

- Chapter 2 ILPDocumento89 pagineChapter 2 ILPSetina AliNessuna valutazione finora

- CPU Architectures Motorola 68000Documento10 pagineCPU Architectures Motorola 68000Nisa RoslanNessuna valutazione finora

- Skylake - Microarchitectures - IntelDocumento33 pagineSkylake - Microarchitectures - IntelCristhofer Candia MamaniNessuna valutazione finora

- MPMC Model Questions R-20Documento3 pagineMPMC Model Questions R-20Jaswanth KadaNessuna valutazione finora

- Bijupatnaikuniversity of Technology, Odisha: Curriculum and SyllabusDocumento23 pagineBijupatnaikuniversity of Technology, Odisha: Curriculum and Syllabusdilliprout.caplet2016Nessuna valutazione finora

- Syllabus of Jambeshwar UniversityDocumento32 pagineSyllabus of Jambeshwar UniversitybinalamitNessuna valutazione finora

- Essentials of Computing PDFDocumento6 pagineEssentials of Computing PDFkarox a rashNessuna valutazione finora

- Embedded Systems Unit 1 and 2 NotesDocumento51 pagineEmbedded Systems Unit 1 and 2 NoteskarnamittapalliNessuna valutazione finora

- CS501-Advanced Computer Architecture Final Term Spring 2012Documento40 pagineCS501-Advanced Computer Architecture Final Term Spring 2012muhammad zulqarnainNessuna valutazione finora

- Advanced Computer ArchitectureDocumento5 pagineAdvanced Computer ArchitecturePranav JINessuna valutazione finora

- CS 258 Parallel Computer Architecture: CS 258, Spring 99 David E. Culler Computer Science Division U.C. BerkeleyDocumento44 pagineCS 258 Parallel Computer Architecture: CS 258, Spring 99 David E. Culler Computer Science Division U.C. BerkeleyMurali SrinivasaiahNessuna valutazione finora

- Silver Oak College of Engineering and Technology: Computer Organization Module Solution - 4Documento11 pagineSilver Oak College of Engineering and Technology: Computer Organization Module Solution - 4sodutuNessuna valutazione finora

- CSA Notes Unit 3Documento43 pagineCSA Notes Unit 3BADMANNessuna valutazione finora

- DPCO Unit 4 2mark Q&ADocumento11 pagineDPCO Unit 4 2mark Q&Akanimozhi rajasekarenNessuna valutazione finora

- Cape Notes Unit1 Module 3 Content 12Documento33 pagineCape Notes Unit1 Module 3 Content 12Rayando Rajae WilliamsNessuna valutazione finora

- Guide To 80X86 Assembly: Overview of The 80X86 FamilyDocumento37 pagineGuide To 80X86 Assembly: Overview of The 80X86 FamilyjavvadiramyaNessuna valutazione finora

- Design & Verification of 16 Bit RISC ProcessorDocumento2 pagineDesign & Verification of 16 Bit RISC Processorravikanti.vinayNessuna valutazione finora

- Tia 14 SP1Documento8 pagineTia 14 SP1dgfjkhNessuna valutazione finora

- MPMC All Questions and AnswerDocumento6 pagineMPMC All Questions and AnswerMODERN TELUGAMMAYINessuna valutazione finora

- Instruction Formats: Zero, One, Two and Three Address Code ExplainedDocumento4 pagineInstruction Formats: Zero, One, Two and Three Address Code ExplainedDharamvir Saini100% (1)

- CST131 Assignment I 1819 v1 PDFDocumento4 pagineCST131 Assignment I 1819 v1 PDFjisoos in your areaNessuna valutazione finora

- Delay routine using sub-program and stackDocumento16 pagineDelay routine using sub-program and stackIrvine ChibayaNessuna valutazione finora