Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

92

Caricato da

maheshsamanapallyCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

92

Caricato da

maheshsamanapallyCopyright:

Formati disponibili

Impact of Well Edge Proximity Effect on Timing

Toshiki Kanamoto

, Yasuhiro Ogasahara

, Keiko Natsume

, Kenji Yamaguchi

,

Hiroyuki Amishiro

, Tetsuya Watanabe

and Masanori Hashimoto

Renesas Technology Corp.

4-1, Mizuhara, Itami-shi, Hyogo, Japan

E-mail: kanamoto.toshiki@renesas.com

Osaka University

1-5, Yamadaoka, Suita-shi, Osaka, Japan

AbstractThis paper studies impact of the well edge proximity

effect on digital circuit delay, based on model parameters ex-

tracted from test structures in an industrial 65nm wafer process.

The experimental results show that up to 10% of delay

increase arises by the well edge proximity effect in the 65nm

technology, and it depends on interconnect length. Furthermore,

due to asymmetric increase in pMOS and nMOS threshold

voltages, delay may decrease in spite of the threshold voltage

increase. From these results, we conclude that considering WPE

is indispensable to cell characterization in the 65nm technology.

I. INTRODUCTION

At front-end stages of CMOS wafer process, P and N types

of ions are implanted to form wells. During the implantations,

lateral scattering of the ions nearby edges of the photo-resist

causes well doping concentration, as shown in Fig. 1 [1][2][3].

The well doping concentration mainly drifts the threshold

voltage of MOS transistors. We call it well edge proximity

effect (WPE). As advanced deep well implants with high-

energy implanters are introduced to suppress parasitic bipolar

gain for latch-up protection, WPE becomes severer. In circuit

design, WPE can be suppressed by making a large separation

between gate poly and enclosing well edge.

On the other hand, as shown in Fig. 2, common cell based

designs intrinsically involve WPE, whereas analog circuit

design can make use of the large separation. The gure depicts

a part of standard cells placement. Since wells are continuous

along the cell rows and then dummy cells are placed at the

both ends of the cell rows for lithographical reasons, horizontal

proximity between gate and well edges can be negligible.

As for the vertical direction, the inner and the outer spacing

shown in the gure are uniquely determined for cell by cell.

Therefore, we should take care of WPE only for the vertical

direction in the digital cell based design.

During circuit design, a lot of effort is put into timing

convergence[4]. From a standpoint of circuit design, delay

variation due to WPE is a matter of utmost concern. We

evaluate the impact of WPE on circuit timing as a case study

in an industrial 65nm technology, and demonstrate the delay

increase quantitatively. We also point out that WPE decreases

cell delay in some conditions of input waveform and output

load.

Resist

Well

Well

STI STI

Gate

S D

Well implant

Substrate

Substrate

Fig. 1. Schematic representation of the well edge proximity effect.

II. WELL EDGE PROXIMITY EFFECT MODELING

Threshold voltage V

th

for MOSFETs with sufciently long

and wide channels are expressed by the following equation

[5].

V

th

= V FB +

s

+

s

V

bs

= V TH0 +(

s

V

bs

s

), (1)

where V FB is the at band voltage,

s

is the surface

potential, V TH0 is the threshold voltage of the device at zero

substrate bias, and is the body bias coefcient which is pro-

portional to square root of the substrate doping concentration.

BSIM4.5 species the factor of increase in the substrate doping

concentration due to WPE in terms of instance parameters

SCA, SCB, SCC and model parameters K

V TH0WE

, WEB,

WEC[5][6][7]. Amount of the V

th

shift is expressed by

dV

th

= K

V TH0WE

(SCA+WEB SCB+WEC SCC).

(2)

Here, the instance parameters SCA, SCB, SCC correspond

to proles of the extra doped well ions due to WPE, and then

they are determined by layout patterns of the MOS transistors.

We derive the model parameters K

V TH0WE

, WEB, WEC

1-4244-1124-6/07/$25.00 2007 IEEE. 115

Power

Ground

(Power)

(Ground)

Vertical inner

spacing

Vertical outer spacing

Vertical outer spacing

Gate

P+ diffusion

N+ diffusion

N well

P well

Cell row

Horizontal spacing

Horizontal spacing

Fig. 2. Well edge proximity of the standard cell region.

Fig. 3. dV

th

estimation using BSIM4.5 parameters.

by tting them to the measured dV

th

for a set of layout patterns

of test element groups. Figure 3 shows effectiveness of the

dV

th

tting. X-axis is the measured Vth shift and Y-axis is

the Vth shift in BSIM4.5 model with the derived parameters.

We can see WPE modeling is well performed.

Fig. 4. Delay increment due to WPE (FO1 small inverters chain).

III. IMPACT OF WELL EDGE PROXIMITY EFFECT ON

TIMING

We derive the model parameters explained in the previous

section for a 65nm SoC process. As shown in [3], the threshold

voltage shifts of p type MOS transistors are larger than

n type MOS transistors due to difference in the substrate

doping concentration. Actually, the maximum difference in the

threshold voltage shift reaches three times. Using the model

parameters and the instance parameters extracted from layout

patterns of standard cells for the SoC process, we achieve the

following experiments.

A. Wire length and fan-out dependency of the delay increase

First, we evaluate delay of two kinds of inverter chains by

circuit simulation. The examined inverter cell is applied to

within 100m range of wire interconnections. One inverter

chain includes the inverters with single fan-out (FO1), where

each inverter drives single inverter with the same size. The

other inverter has the inverters with 20 fan-out (FO20), where

each inverter drives 20 same size inverters. Wires connecting

the inverters, which are assumed to be in a semi-global layer

[8], vary from 1m to 100m.

Figure 4 shows the simulated cell delay[9] of the FO1

inverter chain, where relationship between gate and well edges

is as shown in Fig. 2. In the gure, rise and fall denote

rising and falling transitions of output signal of the inverter.

As seen in the gure, the delay increase due to WPE is up to

10% for this inverter chain, where the rising delay increase is

larger than the falling delay increase. It is because the rate of

the threshold voltage shift in pMOS is twice as large as the

rate in nMOS. We also see in the gure that rate of the delay

increase is reduced as the inverter drives longer wires. Buffers

inserted in a short distance are sensitive to WPE.

Figure 5 shows the simulated cell delay of the FO20 inverter

chain. This situation makes the input transient time of the

inverter cell longer compared to the FO1 case. Wire length

dependency is much smaller than the FO1 case since the output

load capacitance of the inverter is almost determined by the

FO20 of the gate capacitance.

116

Fig. 5. Delay increment due to WPE (FO20 small inverters chain).

B. Conditions of decreasing buffer delay

Next, we examine inverter chains with 24 times larger

inverters than the previous ones. MOS transistors in each

inverter cell form multiple ngers due to the limitation of cell

height. The p type MOS nger has the same size as the p

type MOS transistor in the previous inverter. On the other

hand, the n type MOS nger is twice wider than the previous

one. In general, wider MOS transistors are less affected by

WPE[6]. However, the large standard cell inverter gets the

same amount of WPE as the previous small inverter due to

the nger division. We examine the impact of WPE along

cell delay tables[9] in order to understand the impact of WPE

systematically. The cell delay tables show that falling delay

can decrease due to WPE when the input transient time is

large and the output load (fan-out) is small (Fig. 7), unlike

rising delay (Fig. 6). The reason is thought to be that decrease

in leakage current of pMOS exceeds the decrease in pull-down

current of nMOS. Figures 8 and 9 show current decreases due

to WPE. Figure 8 shows that the leakage current of pMOS is

highly suppressed by WPE, compared with current reduction

of nMOS in Fig. 9.

Then, we examine whether the case of decreasing the delay

appears in the inverter chain. Since the delay decrease can

occur when the fan-out is small, we simulate the FO1 chain.

Figure 10 shows the results. In the wire length range up

to 800m, the falling delay decrease appears. As the wire

becomes long, the wire capacitance increases the output load,

and then the falling delay decrease becomes small. As the

result, there are cases that delay decreases in spite of the

threshold voltage increase.

Fig. 6. Load capacitance and transient time dependency of delay increment

due to WPE (Large inverter, rising delay).

Fig. 7. Load capacitance and transient time dependency of delay increment

due to WPE (Large inverter, falling delay).

IV. CONCLUSION

This paper has investigated the impact of WPE on circuit

delay, applying the WPE model and extraction methodology

to circuits supposing buffer insertion cases in a cell based

design. The experimental results show that up to 10% of

delay increments are caused by WPE in a 65nm SoC process.

Further, the asymmetric increase in the threshold voltages

between p and n type MOS devices causes the situation

of decreasing delay because the decrease in leakage current

of pMOS overwhelms the decrease in pull-down current of

nMOS. From these results, we conclude that WPE in the 65nm

technology should be taken into consideration. Especially,

since the case of decreasing delay can happen, WPE should

be cared for the hold time check in the timing verication, as

well as the setup time checking. In general, since the delay

change due to WPE varies instance by instance, it should be

treated as one of the systematic variability factors[10]. As for

the digital cell based design, considering WPE is indispensable

to cell characterization in the 65nm technology.

117

Fig. 8. Current decrease due to WPE (pMOS).

Fig. 9. Current decrease due to WPE (nMOS).

Fig. 10. Delay increment due to WPE (FO1 large inverters chain).

REFERENCES

[1] T.B.Hook, J.Brown, P.Cottrell, E.Adler, D.Hoyniak, J.Johnson, R.Mann,

Lateral ion implant straggle and mask proximity effect, IEEE Transac-

tions on Electron Devices, vol.50, Issue 9, pp.19461951, Sept. 2003.

[2] I.Polishchuk, N.Mathur, C.Sandstrom, P.Manos, O.Pohland, CMOS Vt-

control improvement through implant lateral scatter elimination, Pro-

ceedings of the IEEE International Symposium on Semiconductor Man-

ufacturing 2005, pp. 193 196, Sept. 2005.

[3] Yi-Ming Sheu, Ke-Wei Su, Sheng-Jier Yang, Hsien-Te Chen, Chih-Chiang

Wang, Ming-Jer Chen, S.Liu, Modeling well edge proximity effect on

highly-scaled MOSFETs, Proceedings of the IEEE Custom Integrated

Circuits Conference 2005, pp. 831 - 834, Sept. 2005.

[4] Yiqian Zhang, Qiang Zhou, Xianlong Hong,Yici Cai, Path-based timing

optimization by buffer insertion with accurate delay model, Proceedings

of 5th International Conference on ASIC, vol.1, pp. 89-92, Oct. 2003.

[5] BSIM4.5.0 Complete Manual, University of California, Berkeley, July

2005.

[6] Guidelines for Extracting Well Proximity Effect Instance Parameters,

Compact Modeling Council, http://www.eigroup.org/CMC/proximity

[7] J.Watts, K.Su, M.Basel, Netlisting and Modeling Well-Proximity Ef-

fects, IEEE Transactions on Electron Devices, vol.53, Issue 9, pp.2179

2186, Sept. 2006.

[8] The International Technology Roadmap for Semiconductors, 2005 Edi-

tion.

[9] Library Compiler Version 2000.05 User Guide, Synopsys inc.

[10] H. Onodera, Variability: Modeling and Its Impact on Design, IEICE

Transactions on Electronics, Vol. E89-C, No. 3, pp. 342-348, March 2006.

118

Potrebbero piacerti anche

- 11Uwn3.Lppm/C Curvature-: A3V Compensated Cmos Bandgap ReferenceDocumento4 pagine11Uwn3.Lppm/C Curvature-: A3V Compensated Cmos Bandgap ReferencemaheshsamanapallyNessuna valutazione finora

- 42 SriSriTadepalliShastryGaru 2bwDocumento4 pagine42 SriSriTadepalliShastryGaru 2bwvascpragada190100% (1)

- HDFC Ergo ClaimFormDocumento3 pagineHDFC Ergo ClaimFormmaheshsamanapallyNessuna valutazione finora

- Bandgap 2009Documento27 pagineBandgap 2009jjloksNessuna valutazione finora

- Ieice2009 LdoDocumento3 pagineIeice2009 LdomaheshsamanapallyNessuna valutazione finora

- Bed Room PDFDocumento53 pagineBed Room PDFParimi VeeraVenkata Krishna SarveswarraoNessuna valutazione finora

- What Is LDODocumento18 pagineWhat Is LDOmaheshsamanapallyNessuna valutazione finora

- Lec2 JWFILESDocumento33 pagineLec2 JWFILESSanthi SriNessuna valutazione finora

- Lab Overview: ECE 410 Brief Report TemplateDocumento1 paginaLab Overview: ECE 410 Brief Report TemplatemaheshsamanapallyNessuna valutazione finora

- Voltage References and Biasing: KT/Q, For Example) - Similarly, Any Current We Produce Must Depend On Parameters ThatDocumento15 pagineVoltage References and Biasing: KT/Q, For Example) - Similarly, Any Current We Produce Must Depend On Parameters ThatmaheshsamanapallyNessuna valutazione finora

- Analog Layout Generation For Performance and ManufacturabilityDocumento1 paginaAnalog Layout Generation For Performance and ManufacturabilitymaheshsamanapallyNessuna valutazione finora

- E 0 B 49515153463 Daf 5Documento16 pagineE 0 B 49515153463 Daf 5maheshsamanapallyNessuna valutazione finora

- INF4420 02 Bandgaps PrintDocumento24 pagineINF4420 02 Bandgaps PrintmaheshsamanapallyNessuna valutazione finora

- Physical Design Interview QuestionsDocumento37 paginePhysical Design Interview Questionsmaheshsamanapally100% (1)

- CascodeDhawan LibreDocumento8 pagineCascodeDhawan LibremaheshsamanapallyNessuna valutazione finora

- Pura Than A Punya Grand A NidhiDocumento201 paginePura Than A Punya Grand A NidhimaheshsamanapallyNessuna valutazione finora

- Spoken English 2Documento247 pagineSpoken English 2maheshsamanapally100% (1)

- A CMOS Voltage Controlled Ring Oscillator With Improved Frequency StabilityDocumento9 pagineA CMOS Voltage Controlled Ring Oscillator With Improved Frequency StabilityArik ZafranyNessuna valutazione finora

- Bpasts 2013 0074Documento7 pagineBpasts 2013 0074maheshsamanapallyNessuna valutazione finora

- Gopuramu PDFDocumento246 pagineGopuramu PDFSunil KumarNessuna valutazione finora

- 1 PBDocumento7 pagine1 PBmaheshsamanapallyNessuna valutazione finora

- Reconfigurable Computing - Clocks: John MorrisDocumento15 pagineReconfigurable Computing - Clocks: John MorrismaheshsamanapallyNessuna valutazione finora

- Automating Analog Design Analysis and Productivity ToolsDocumento20 pagineAutomating Analog Design Analysis and Productivity ToolsmaheshsamanapallyNessuna valutazione finora

- Lec2 JWFILESDocumento33 pagineLec2 JWFILESSanthi SriNessuna valutazione finora

- An Efficient Layout Style For ThreeDocumento12 pagineAn Efficient Layout Style For Threejhchon2000Nessuna valutazione finora

- Hanu Mac CharitraDocumento109 pagineHanu Mac CharitramaheshsamanapallyNessuna valutazione finora

- Hindu CalendarDocumento8 pagineHindu CalendarAlbert HuangNessuna valutazione finora

- Tala Patra 32Documento17 pagineTala Patra 32maheshsamanapally67% (3)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (890)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (72)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Pactocure RBDocumento2 paginePactocure RBNNessuna valutazione finora

- Desalineamiento Acoplamientos FalkDocumento2 pagineDesalineamiento Acoplamientos FalkJuanPabloGonzalezFiblasNessuna valutazione finora

- Summertime - PianoDocumento4 pagineSummertime - PianoLazaro GarciaNessuna valutazione finora

- Magnetic Field Sensors for Automotive and Industrial ApplicationsDocumento16 pagineMagnetic Field Sensors for Automotive and Industrial Applicationskishan1234Nessuna valutazione finora

- Wireshark Basics Self StudyDocumento51 pagineWireshark Basics Self StudymzyptNessuna valutazione finora

- Synchronous Rectification For Forward Converters PDFDocumento41 pagineSynchronous Rectification For Forward Converters PDFtongaiNessuna valutazione finora

- Mitos y Leyendas de Antioquia La GrandeDocumento220 pagineMitos y Leyendas de Antioquia La GrandeGabriel Gómez PadillaNessuna valutazione finora

- Dubai Internet CityDocumento11 pagineDubai Internet Citytvsameel7208100% (1)

- MDLX Atc App Note Pi 026Documento0 pagineMDLX Atc App Note Pi 026david_benavidez_3Nessuna valutazione finora

- Jill Manning: EducationDocumento1 paginaJill Manning: EducationJill ManningNessuna valutazione finora

- Monokote Field App Manual - LRDocumento136 pagineMonokote Field App Manual - LREva Pacheco100% (3)

- Torsion - The Key To The Theory of Everything (Web)Documento8 pagineTorsion - The Key To The Theory of Everything (Web)Brainiac007100% (2)

- AND Techno-Economic Cum Pre-Investment Feasibility Report: M/S Saif BeveragesDocumento59 pagineAND Techno-Economic Cum Pre-Investment Feasibility Report: M/S Saif BeveragesMohd touseefNessuna valutazione finora

- Lme N7101Documento27 pagineLme N7101alexjoelNessuna valutazione finora

- ASG DAMA Data GovernanceDocumento25 pagineASG DAMA Data GovernanceWebVP_DAMARCNessuna valutazione finora

- ChongQing Gold Mechanical Electrical Equipment Co InstructionDocumento12 pagineChongQing Gold Mechanical Electrical Equipment Co InstructionPaulRuedaNessuna valutazione finora

- 2013 Urology CatalogDocumento233 pagine2013 Urology CatalogAna LauraNessuna valutazione finora

- Sika-Wrap Struct StrengthDocumento7 pagineSika-Wrap Struct StrengthMiky CastenNessuna valutazione finora

- Chapter 10 Asset Management 2014 From Machine To Machine To The Internet of ThingsDocumento8 pagineChapter 10 Asset Management 2014 From Machine To Machine To The Internet of ThingsDaviti GachechiladzeNessuna valutazione finora

- Imaging 101 Using SAP's Content Server: John Walls Verbella CMG, LLCDocumento59 pagineImaging 101 Using SAP's Content Server: John Walls Verbella CMG, LLCsharadcsinghNessuna valutazione finora

- How To Produce Your Book With Scribus.: Make The Front MatterDocumento3 pagineHow To Produce Your Book With Scribus.: Make The Front MattersudyNessuna valutazione finora

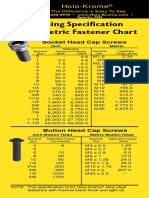

- Torquing Specification Inch & Metric Fastener Chart: Socket Head Cap ScrewsDocumento2 pagineTorquing Specification Inch & Metric Fastener Chart: Socket Head Cap ScrewsgielNessuna valutazione finora

- 7500-7520 31001-Up PM 1112847Documento1.058 pagine7500-7520 31001-Up PM 1112847multiservicmNessuna valutazione finora

- Fast Cam V 7 UpgradeDocumento2 pagineFast Cam V 7 Upgrademohsen_2670% (1)

- Conc Surf PrepDocumento6 pagineConc Surf PrepelsalseritoNessuna valutazione finora

- ACA Corrosion Technology GuideDocumento174 pagineACA Corrosion Technology Guidetridatyl100% (1)

- PC-Bedienungsanleitung Heater enDocumento33 paginePC-Bedienungsanleitung Heater enZoran Tanja JarakovićNessuna valutazione finora

- Instrumentarium Dental OP-200D, OC-200D Dental Panorama X-Ray - User ManualDocumento154 pagineInstrumentarium Dental OP-200D, OC-200D Dental Panorama X-Ray - User ManualmariaNessuna valutazione finora

- Kenwood RXD 302 A31 Service ManualDocumento27 pagineKenwood RXD 302 A31 Service Manualbarabbaladro100% (1)

- Emerson GA Drawing PDFDocumento1 paginaEmerson GA Drawing PDFSachin GuptaNessuna valutazione finora