Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Logic Gates

Caricato da

blzz2netCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Logic Gates

Caricato da

blzz2netCopyright:

Formati disponibili

1

MODULE 3

Combinational & Sequential logic

Combinational Logic

Introduction

Logic circuit may be classified into two categories

1. Combinational logic circuits

2. Sequential logic circuits

A combinational logic circuit contains logic gates only but does not contain storage

elements. A sequential logic circuit contains storage elements in addition to logic gates.

When logic gates are connected together to give a specified output for certain specified

combination of input variables, with no storage involved, the resulting network is known as

combinational logic circuit. In combinational logic circuit the output level is at all times

dependent on the combination of input level. The block diagram is shown

The combinational logic circuit with memory elements(s) is called sequential logic circuit.

It consists of a combinational circuit to which memory elements are connected to form a feed

back path. The memory elements are devices, capable of storing binary information within

them. The block diagram is shown.

By block diagram, it can be said that the output(s) of sequential logic circuit is (are) dependent

not only on external input(s) but also on the present state of the memory element(s). The next

state of the memory element(s) is also dependent on external input and the present state.

Applications

Logic gates find wide applications in Calculators and computers, digital measuring

techniques, digital processing of communications, musical instruments, games and domestic

appliances etc, for decision making in automatic control of machines and various industrial

processes and for building more complex devices such as binary counters etc.

Combinational

logic circuit

(Logic gates only)

INPUT

VARIABLES

OUTPUT

VARIABLES

Combinational

Circuit

Memory

Elements

External

Inputs

Outputs from

Combinational

circuit

Outputs from

Memory

elements

2

DESIGN OF COMBINATIONAL CIRCUITS

The design of combinational circuits starts from the verbal outline of the problem and ends

in a logic circuit diagram. The procedure involves the following steps:

1. State the given problem completely and exactly

2. Interpret the problem, and determine the available input variables and required output

variables.

3. Assign a letter symbol to each input and output variables.

4. Design the truth table, which defines the required relations between inputs and outputs.

5. Obtain the simplified Boolean expression for each output.

6. Draw the logic circuit diagram to implement the Boolean expression.

ARITHMETIC CIRCUITS

One essential function of most computers and calculators is the performance of arithmetic

operations. The logic gates designed so far can be used to perform arithmetic operations such

as addition, subtraction, multiplication and division in electronic calculators and digital

instruments. Since these circuits are electronic, they are very fast. Typically an addition

operation takes less than 1 s. We will now study some of the basic arithmetic circuits.

HALF ADDER

A Logic circuit used for the addition of two one bit numbers is referred to as a half-adder.

From the verbal explanation of a half adder, we find that this circuit needs two binary inputs

and two binary outputs. The input variables designate the augend and addend bits; the output

variables produce the sum and carry. We assign the symbols A and B to the two inputs and S

(for sum) and C (for carry) to the outputs. The truth table for the half-adder is shown below.

Here the C output is 1 only when both inputs are 1. The S output represents the least

significant bit of the sum. The logic expression for the sum output can be obtained from the

truth table. It can be written as a SOP expression by summing up the input combinations for

which the sum is equal to 1.

In the truth table, the sum output is 1 for AB and AB. Therefore, the expression for the sum is

S = AB + AB = A B.

Similarly, the logic expression for carry output can be written as a SOP expression by summing

up the input combinations for which the carry is equal to 1. In the truth table, the carry is 1 for

AB. Therefore

C = AB

This expression for C cannot be simplified. The sum output corresponds to a logic Ex-OR

function while the carry output corresponds to an AND function. So the half-adder circuit can

be implemented using Ex-OR and AND gate as shown below.

Inputs Outputs

A B S C

0

0

1

1

0

1

0

1

0

1

1

0

0

0

0

1

3

Logic Circuit Logic Symbol

This circuit is called Half-Adder, because it cannot accept a CARRY-IN from previous

additions. This is the reason that half adder circuit can be used for binary addition of lower

most bits only. For higher order columns we use a 3-input adder called full-adder.

FULL ADDER

A combinational logic circuit for adding thee bits. As seen, a half-adder has only two inputs

and there is no provision to add carry coming from the lower bit order when multi bit addition

is performed. For this purpose we use a logic circuit that can add three bits, the third bit is the

carry from the lower column. This implies that we need a logic circuit with 3 inputs and 2

outputs. Such a circuit is called a full adder. The truth table for the full-adder is as shown

below.

Inputs Outputs

A B C

in

S C

out

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

1

0

1

0

0

1

0

0

0

1

0

1

1

1

As shown there are 8 possible input combinations for the three inputs and for each case the

S and C

out

values are listed. From the truth table, the logic expression for S can be written by

summing up the input combinations for which the sum output is 1 as:

S = ABC

in

+ ABC

in

+ ABC

in

+ ABC

in

= A(BC

in

+ BC

in

) + A(BC

in

+ BC

in

)

= A(BC

in

)+ A(BC

in

)

Let BC

in

= X

Now, S = AX + AX = A X

Replacing X in the above expression we get

S = A B C

in

Similarly the logic expression for C

out

can be written as

C

out

= ABC

in

+ ABC

in

+ ABC

in

+ ABC

in

= BC

in

+ AC

in

+ AB (using the map shown)

A

B

S

C

Inputs

Outputs

HALF

ADDER

C

in

AB

C

C

AB AB AB AB

0 0 1 0

0 1 1 1

4

From the simplified expressions of S and C the full adder Circuit can be implemented using

two 2-input XOR gates, Three 2 input AND gates and one 3-input OR gate a shown below fig

(a). The logic symbol is also shown as fig (b).

Logic circuit diagram fig(a) Logic Symbol Fig(b) .

The logic symbol has two inputs A and B plus a third input C

in

called the Carry-in and two

outputs SUM and the Carry called Carry out, C

out

going to the next higher column.. A full adder

can be made by using two half adders and an OR gate as shown below

Binary Adders

2-bit Parallel Adder

As we have seen a single full-adder is capable of adding two one-bit numbers and an input

CARRY. For addition of binary numbers with more than one bit, additional full adders will be

required. When two binary numbers are added, each column generates a sum and a Carry (1 or

0) to the next higher-order adder, Column as shown for a two bit adder. It is to be noted that

B

A C

in

BC

in

AC

in

AB

CARRY

SUM

A

B

C

in

CARRY, C

out

SUM, S

FULL

ADDER

FULL ADDER

CARRY, C

out

SUM, S

D C

in

D.C

in

A B=D

A.B

C

in

B

A

HA

HA

MSB

5

either a half-adder can be used for the LSB position or the CARRY input of a full-adder is

made zero because there is no CARRY into the LSB bit position. In the figure, the LSB of the

two numbers are represented by X

0

and Y

0

. The next higher order bits are represented by X

1

and Y

1

.

4-bit parallel adder

MSB

This circuit shows a 4-bit binary parallel adder circuit. The LSBs in each number being

added (operands) go into the right-most full-adder; the high order bits are applied to the

successively higher-order adders, with the MSBs in each number being applied to the left most

full adder. The CARRY output of each adder is connected to the CARRY input of the next

higher order adder. The full adder circuit used in each position has three inputs: an X bit, a Y bit

and a C

IN

bit and it produces two outputs: a SUM bit and CARRY OUT bit. For example the

left most full-adder has inputs X

0

, Y

0

, and C

0

and it produces output S

0

and C

1

. This

arrangement is repeated for as many positions as there are in the augend and addend. Although

this illustration is for 4-bit numbers, in modern computers the number usually ranges from 8 to

64 bits. The arrangement shown is called a parallel adder because all the bits of the augend and

addend are present and are fed into the adder circuit simultaneously. This means that the

additions in each position are taking place at the same time. This is different from how we add

on paper, taking each position one at a time with LSB. Parallel addition is therefore extremely

fast.

The Half Subtractor

A logic circuit that subtracts Y (subtrahend) from X(minuend), where X and Y are 1-bit

numbers, is known as a half-subtractor. It has two inputs X (minuend) and Y (subtrahend) and

two outputs D (difference) and B (borrow), as shown in the block diagram.

The operation of this logic circuit is based on the rules of binary subtraction given in the truth

table reproduced on the basis of the subtraction process.

Inputs Outputs

X Y D B

0

0

1

1

0

1

0

1

0

1

1

0

0

1

0

0

HS

X

Y

D

B

6

The difference output in the third column has the same logic pattern as when X is XORed

with Y (same as in the case of sum). Hence an Ex-Or gate can be used to give difference of two

bits. The borrow output in the 4

th

column can be obtained by using a NOT gate and AND gate,

as shown in the circuit diagram below.

The logical equations for the difference D and borrow B are given as

D = XY + XY = X Y.

B = XY

4 bit Adder Subtractor

The 4 bit parallel binary adder/subtractor circuit shown below performs the operations of

both addition and subtraction.

It has two 4 bit inputs A

3

A

2

A

1

A

0

and B

3

B

2

B

1

B

0

. the Sel (ADD/SUB) control line

connected with the C

0

of the LSB of the full-adder, is used to perform the operations of

addition and subtraction. The Ex-OR gates are used as controlled inverters. When Sel=0 the

circuit is an adder and when Sel=1, the circuit becomes a subtractor. Each Ex-OR gate receives

input Sel and one of the inputs of B. When Sel=0, we have B 0=B. The full-adders receive

the value of B, the input carry = 0 and the circuit performs A plus B. When Sel=1, we have B

1 =B and C

0

= 1. The B inputs are all complemented and 1 is added through the input carry.

The circuit performs the operation A plus the 2s complement of B. (The exclusive OR with

output V is for detecting an overflow.)

7

MULTIPLEXERS

A multiplexer or data selector is a logic circuit that accepts several data inputs and

allows only one of them at time to get through the output. In other words, the multiplexer works

like the input selector of a home music system. Only one input is selected at a time, and the

selected input is transmitted to the single output. While on the music system, the selection of the

input is made manually, the multiplexer chooses its input based on a binary number, the address

input. The basic multiplexer, then, has several data-input lines and a single output line. It has also

data-select inputs or control signals that permit digital data on any of the inputs to be switched to

the output line. A general multiplexer (MUX) with n input ignals, m data select inputs or

control signals and one output signal is shown in the figure.

The multiplexer (MUX) acts like a digitally controlled multi position switch where the

digital code applied to the SELECT inputs determines which data inputs will be switched to the

output. The functional diagram of a 2 to 1 multiplexer is shown below:

Here the input signal I

0

will be obtained at the out put when the select signal is equal to 0 and

the signal I

1

appears at the output when the select signal is 1. So the MUX selects in this case

one out of the 2 input data sources and transmits the selected data to a single output channel.

This is called multiplexing. Now let us consider a multiplexer with 4 input signals, 2 control

signals and one output signal.

MUX

n

I

N

P

U

T

S

I

G

N

A

L

S

m CONTROL SIGNALS

1 OUTPUT

SIGNAL

8

A multiplexer of this type is known as a four to one multiplexer because of its 4 inputs and 1

output. The circuit diagram of a 4-t0-1 multiplexer is shown. Here there are 4 input bits (D

0

to D

3

),

and two control signals (A and B). Now by controlling the level of control signals A and B, any

data bit can be transmitted to the output

Other 4-to-1 multiplexers

Consider that the control inputs A and B are supplied with low level of control signals. Now

the inputs I

1

and I

2

of only AND gate A

1

is high. If data bit D

0

is low then output of AND gate

A

1

is low and if data bit D

0

is high then output of AND gate A

1

is high. So it can be said that

when AB=00, it makes only AND gate A

1

enabled and only data bit associated with this gate is

transferred to the output. All the other AND gates are disabled and data bits associated with

them cannot be transferred to the output. So outputs of all AND gates except A

1

remains low.

9

Output of OR gate, Z depend only on the output of AND gate A

1

(because only AND gate A

1

is

enabled) so ultimately value of output Z depends only on the value of D

0

.

Now consider that AB=01. It makes AND Gate A

2

enabled and all other gates disabled. In

this condition data bit D is transferred to the output z. Truth table of a four-to-one multiplexer is

shown. If n is the number of control signals in a Multiplexer, the maximum number of input

Signals that can be controlled by it = 2

n

. 16-to-1 multiplexer with 4 control lines is available in

the form of IC.

8 to 1 Multiplexer

It has 8 inputs and one output. In the logic symbols there are three select inputs S

0

, S

1

and S

2

which selects one of the eight inputs. The truth table of 8:1 multiplexer is shown below.

In this truth table, for each input combination, output is not specified as 1s and 0s.

Multiplex being a data switch does not generate a data of its own, but it simply passes external

input data from the selected input to the output. Figure below shows a logic diagram of 8 to

1 multiplexer.

Data Select

Inputs

Input

Selected

Input Output

A B D D Z

0 0 D

0

0

1

0

1

0 1 D

1

0

1

0

1

1 0 D

2

0

1

0

1

1 1 D

3

0

1

0

1

Select Lines Outputs

S

2

S

1

S

0

Z

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

10

DE

MUX

mCONTROL SIGNALS

nOUTPUT SIGNALS

1 INPUT

SIGNAL

Applications of Multiplexers

Multiplexer circuits find numerous applications in digital systems. Some of the fields where

multiplexing find immense use are data selection, data routing, operation sequencing, parallel

to serial conversion, wave form generation and logic function generation.

DEMULTIPLEXERS

The word de-multiplex means one into many. A multiplexer takes several inputs and

transmits one of them to the output as stated before. A de-multiplexer performs the reverse

operation. That is it takes a single input and distributes it over several outputs.By applying control

signals, the input signal can be steered to one of the output lines. A de-multiplexer with on input

signal, m control signals and n output signals is shown below. The de-multiplexer is also called a

Distributer or a serial-to-parallel converter.

11

The functional diagram for a de-multiplexer (DEMUX) is shown below.

This shows a 1-to-2 de-multiplexer . This contains 1 input and 2 outputs and one

control line. The select input code determines to which output the DATA input will be transmitted.

It means, the de-multiplexer takes one input data source and selectively distributes it to 1 of n

output terminals just like a multi-position switch.

1 to 4 De-multiplexer

Let us consider a de-multiplexer with 1 input signal, 2 control signals and 4 output

signals to explain, how input signal is transmitted to any of the outputs by control signals. This

type of de-multiplexer is called one-to-four de-multiplexer because it has 1 input and 4 outputs.

Truth table for 1-to-4 de-multiplexer

Select lines Input Output lines

S

1

S

0

I

0

F

3

F

2

F

1

F

0

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

0

0

0

0

0

1

0

0

0

0

0

1

0

0

0

0

0

1

0

0

0

0

0

1

0

0

0

0

0

0

The circuit diagram for a 1-to-4 de-multiplexer is shown below.

12

Here the data bit is I

0

and the control signals are S

1

and S

0

. Now by controlling the

level of control signals S

1

and S

0

input data I

0

can be transmitted to any of the outputs. The

AND gates connected to F

0

, F

1

, F

2

and F

3

are made enabled and disabled by changing the level

of control signals.

1 to 8 De-multiplexer

The circuit diagram and truth table of a one to-eight de-multiplexer is shown below

Select Lines Output Lines

a

2

a

1

a

0

x

0

x

1

x

2

x

3

x

4

x

5

x

6

x

7

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

d

0

0

0

0

0

0

0

0

d

0

0

0

0

0

0

0

0

d

0

0

0

0

0

0

0

0

d

0

0

0

0

0

0

0

0

d

0

0

0

0

0

0

0

0

d

0

0

0

0

0

0

0

0

d

0

0

0

0

0

0

0

0

d

13

DECODERS

De-multiplexer with out any input. A decoder decodes the coded input signal into an

active output signal. A decoder is similar to a de-multiplexer, with one exception there is no data

input. Inputs for the decoder are the control signals. Most digital systems require the decoding of

data. Decoding is necessary in applications such as data de-multiplexing, digital display, digital-to-

analog converters and memory addressing. A decoder is logic circuit that converts an n-bit binary

input code (data) into 2

n

output lines, such that each output line will be activated for only one of the

possible combinations of inputs. In a decoder, the number of output is greater than the number of

inputs. It is important to note that if the number of inputs and outputs are equal in a digital system

then it can be called Converters.

2 to 4 Decoder

Figure shows the circuit diagram and truth table of a 2-to-4 line decoder which is the simplest

one.

The example decoder circuit would be an AND gate because the output of an AND

gate is "High" (1) only when all its inputs are "High." Such output is called as "active High

output". If instead of AND gate, the NAND gate is connected the output will be "Low" (0) only

when all its inputs are "High". Such output is called as "active low output".

3 to 8 Decoder

A 3-to-8 decoder has three inputs (A,B,C) and eight outputs (D

0

to D

7

). Based on the

three inputs, one of the 8 outputs is selected. The truth table for the 3-to-8 decoder is shown

below.

INPUTS OUTPUTS

A B C D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

14

A B C

Enable

D

0

D

2

D

1

D

3

D

4

D

5

D

6

D

7

From the above truth table, it is clear that only one of the 8 outputs is selected based on the 3

select inputs. Also from the truth table, the logic expressions for the outputs can be written as

follows:

D

0

= ABC;D

1

= ABC;D

2

= ABC;D

3

= ABC;D

4

= ABC;D

5

= ABC; D

6

= ABC; D

7

=

ABC

Using the above expressions, the circuit of a 3-to-8 decoder can be implemented using three

NOT gates and eight 3-input AND gates as shown.

The 3 inputs A, B, and C are decoded into eight outputs, each output representing one of the

minterms of the 3 input variables. The three inverters provide the complement of the inputs and

each one of the 8 AND gates generate one of the minterms. This decoder can be used for

decoding any 3-bit code to provide 8 outputs, corresponding to 8 different combinations of the

input code. This is also called a 1-to-8 decoder, since only one of eight output lines is HIGH for

a particular input combination. For example, when ABC=010, only the AND gate-2 has HIGH

at all its inputs, and there fore D

2

=HIGH. Similarly if ABC=110, only the AND gate-6 has all

its inputs in HIGH state, and thereby D

6

=HIGH. It is also called a binary-to-Octal decoder

since the inputs represent three bit binary numbers and the outputs represent the eight digits in

the octal number system.

Enable inputs

Some decoders have one or more enable inputs which are used to control the operation of

the decoder. With the enable line held Low, the decoder functions normally and the input code

A, B, and C will determine which output is HIGH. Hence, this decoder is enabled only if the

enable line is LOW.

The block diagram of a 3-to-8 decoder IC 7442 is as shown below

15

4-to-16 Decoder

A decoder with 4 input lines and 16 output lines is shown in the figure. This is called a 4

to-16 decoder. This is also called one-of-Sixteen decoder because only one of the 16 Lines is

HIGH at a time for the particular Value of input signals. Let us consider the case when

ABCD=0000, Then only AND gate with output Z

0

has all Inputs high and so only the output Z

0

is high. Consider another case when ABCD=0101, Then only AND gate with output Z

5

has all

Inputs high and so only the output Z

5

is high. Consider one more case when ABCD=1111 Then

only AND gate with output Z

15

has all Inputs high and so only the output Z

15

is high.

From the above discussion and after considering all other cases of possible values of ABCD

(from 0000 to 1111) it is found that subscript of a high output gives the hexadecimal equivalent

of binary number ABCD. So the circuit is also called a binary-to hexadecimal decoder since

the inputs represent four bit binary number and the outputs represent the 16 digits in the

hexadecimal number system.

16

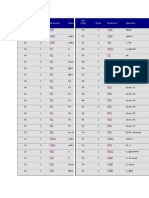

The truth table is shown below.

Decimal

digit

Binary Inputs Logic

Function

Outputs

D C B A

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

01

0

1

0

1

DCBA

DCBA

DCBA

DC BA

DCBA

DC BA

DC BA

DC B A

DCBA

D CBA

D CB A

D CB A

D CBA

D CBA

D C BA

D C B A

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

The 4-to-16 decoder is also called a 1-of-16 decoder, since only one of 16 outputs is

selected based on a particular input combination. The circuit can also be used to give a BCD-to-

decimal decoder. In this case only AND gates Z

0

to Z

9

are used, which represent the decimal

numbers 0 to 9 and all other AND gates are removed from the circuit. Values of input signal

ABCD are changed from 0000 (BCD of decimal digit 0) to 1001 (BCD equivalent of decimal

digit 9). This circuit has 10 outputs and only one output is high at a time, so it is also called a 1-

of-10 decoder.

Applications of decoders

1. Decoders are used in counter systems

2. They are used in analog-to-digital converters.

3. Decoder outputs can be used to drive a display system.(IC 7446/7447 and IC 7448/7449 are

BCD-to- seven segment decoders)

ENCODERS

An Encoder is a digital circuit that performs the inverse operation of a decoder. Hence the

opposite of the decoding process is called encoding. An encoder converts an active input signal

into a coded output signal. The block diagram is shown below.

n Inputs

m Outputs

It has n input lines and m output lines. At a time only one of the input lines is active. Internal

logic within the encoder converts this active input to a coded binary output with m bits.

17

Decimal-to-BCD encoder

One of the most commonly used input device for a digital system is a set of ten switches,

one for each numeral. These switches generate 1 or 0 logic Levels in response to turning them

ON or OFF.

When a particular number is to be fed to the digital circuit in BCD code, the switch

corresponding to that number is pressed. There is an IC available to perform this function

(74147). The truth table for this encoder is shown below.

INPUTS OUTPUTS

0 1 2 3 4 5 6 7 8 9

b

4

b

3

b

2

b

1

1

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

0

1

0

1

0

1

0

1

0

1

When switch 0 is pressed, all OR gates are inactive and so output by b

4

b

3

b

2

b

1

is 0000 which

is the BCD equivalent of digit 0. When switch 1 is pressed, the OR gate 1 is active and so

output by b

4

b

3

b

2

b

1

is 0001 which is the BCD equivalent of digit 1. In the same way when

switch 7 is pressed OR gates 3, 2 and 1 are active, so output b

4

b

3

b

2

b

1

is 0111 which is again the

BCD equivalent of digit 7.

18

Octal-to-binary encoder

Another example of an encoder is the octal-to-binary encoder whose truth table is shown below.

An octal-to-binary encoder accepts eight inputs and produces a 3 bit output code

corresponding to the activated input. The truth table shows that Y

0

(LSB of output code) must be

1 whenever the input D

1

OR D

3

OR D

5

OR D

7

is HIGH.

Thus Y0 = D

1

+ D

3

+ D

5

+ D

7

Similarly

Y

1

= D

2

+ D

3

+ D

6

+ D

7

Y

2

= D

4

+ D

5

+ D

6

+ D

7

Using the above expressions, the octal-to-binary encoder can be implemented using three 4-

input OR gates as shown below.

The circuit is designed in such a way that, when D

0

is HIGH, the binary code 000 is

generated. When D1 is HIGH, the binary code 001 is generated, and so on. The design is made

simple by the fact that only eight out of the total of 2

8

possible input conditions are used.

INPUTS OUTPUTS

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

y

2

y

1

y

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

19

Combinational

circuit

Memory

elements

Inputs

Outputs

SEQUENTIAL LOGIC

Sequential circuits

The digital circuits discussed so far have been combinational, where the outputs are entirely

dependent on the current inputs. Although every digital system is likely to have combinational

circuits, most systems encountered in practice also include storage elements, which require that

the system be described in terms of sequential logic. A block diagram of a sequential circuit is

shown below.

It consists of a combinational circuit to which storage elements are connected to form a

feed back path. The storage elements are devices capable of storing binary information. The

binary information stored in these elements at any given time defines the state of the sequential

circuit at that time. The sequential circuit receives binary information from external inputs.

These inputs, together with the present state of the storage elements, determine the binary value

of the outputs. They also determine the condition for changing the state in the storage elements.

From the block diagram we can see that the outputs in a sequential circuit are a function not

only of the inputs, but also of the present state of the storage elements. The next state of the

storage elements is also a function of external inputs and the present state. Thus, a sequential

circuit is specified by a time sequence of inputs, outputs, and internal states. Combinational

circuits are often faster than sequential circuits since the combinational circuits do not require

memory elements where as the sequential circuits need memory devices to perform their

operations in sequence. However, modern digital computers must have memories to function

properly. Thus, sequential circuits are of prime importance in modern digital devices.

Types of Sequential circuits

Sequential circuits are classified in two main categories depending on timing of their signals.

1. Synchronous or clocked sequential circuits

2. Asynchronous or un-clocked sequential circuits.

Synchronous or clocked sequential circuits

A sequential circuit whose behavior can be defined from the knowledge of its signals at

discrete instants of time is referred to as a synchronous sequential circuit. In such circuits, the

memory elements are affected only at discrete instants of time. The synchronization is obtained

by a timing device, called a system clock (or a master-clock generator) which generates a

periodic train of clock pulses. The outputs are affected only with the application of clock pulse.

Asynchronous or un-clocked sequential circuits.

A sequential circuit whose behavior depends upon the sequence in which the input

signals change is referred to as an asynchronous sequential circuit. The output is affected

whenever there is a change in the inputs. The commonly used memory elements in such circuits

are time delay devices. These circuits may be regarded as combinational circuits with feed

back. These circuits are faster than synchronous sequential circuits. However, in an

asynchronous circuit, events are allowed to occur without any synchronization. In such a case,

20

Input

Q

Q

Normal

output

Inverted

output

Q

Q

R

S

(Reset)

(set)

the system becomes unstable which results in difficulties. To have a sequential circuit, a storage

device is required to know what has happened in the past. The basic unit of storage is the flip

flop.

FLIP FLOPS

Also called as LATCH. The simplest kind of sequential circuit is a memory cell that has

only two states. It can be either a 0 or 1. Such two state sequential circuits are called flip-flops

because they flip from one state to another and then flop back. A flip-flop is also known as

bistable multivibrator, latch or toggle. The general block diagram representation of a flip-flop is

shown below.

It has one or more inputs and two outputs Q and Q . The two outputs are complementary to

each other; if Q=0 i.e. Reset, then Q =1; if Q=1 i.e. Set, then Q =0. When the flip-flop output

Q=0 or 1, it will remain in that stable state until one or more of the inputs are excited to effect a

change in the output. Since the flip flop output will remain set/reset until the trigger pulse is

given to change the state, it can be regarded as a memory device to store one binary digit.

Types of Flip-Flops

Flip-Flops are of different types depending on how their inputs and clock pulses cause

transition between two states. There are 4 basic types

1. S R (Set-Reset)/R-S flip flop

2. J-K flip-flop

3. D (delay)flip-flop

4. T (trigger or Toggle)flip-flop

R-S Flip-Flop

The S R flip flop has two inputs, namely SET (S) and RESET (R), and two outputs Q

and Q. The two outputs are complement to each other. The R-S flip-flop can be easily

implemented using NOR gates or NAND gates. The block diagram of an S-R flip-flop is as

shown below.

NOR based R S flip-flop

21

S (set)

R (reset)

Q

Q

The S-R flip-flop can be easily constructed using two NOR gates connected back to back as

shown in the figure above. The cross-coupled connections from the output of one gate to the

input of the other gate constitute a feed back path. For this reason, the circuits are classified as

asynchronous sequential circuits. The truth table for the NOR based S-R flip-flop is shown

below.

To analyze the circuit one must remember that the out put of a NOR gate is zero if any input is

1 and the output is 1 only when all the inputs are zero. From the truth table it is evident that four

possible input combinations exist for the S-R flip-flop. The outputs for these four possible input

combinations are described below.

Case 1

For S=0 and R=0, the flip-flop simply remains in its present state (Q).

Case 2

The second input condition is S=0 and R=1. The 1 at the RESET input forces the Output of

NOR gate 1 LOW (i.e. Q= 0). Now both the inputs of the NOR gate 2 are 0 and 0 and its output

Q= 1. Thus the input condition S=0 and R=1 will always RESET the flip-flop to 0. The flip-

flop will remain in the 0 state till the RESET input returns to 0.

Case 3

The third input condition is S=1 and R=0, which forces the Output of NOR gate 2 LOW

(i.e. Q= 0). Now both the inputs of the NOR gate 1 are 0 and 0 and the output of NOR gate 1 is

HIGH, i.e. Q=1. Thus the input condition S=1 and R=0 will always SET the flip-flop to 1.

Case 4

The last input condition is S=1 and R=1. This condition will produce 0 at the output of both

the NOR gates. Hence Q=0 and Q= 0. This condition violates the fact that the outputs Q and Q

are the complements of each other. In normal operation, this condition must be avoided by

making sure that 1s are applied to both inputs simultaneously.

NAND based R S flip-flop

NAND gates instead of NOR gates may also be used to form a R-S flip-flop. Circuit

diagram, symbol and truth table for such a flip-flop are shown below.

Inputs Outputs Action

S R Q Q

0

0

1

1

0

1

0

1

Q

0

1

?

Q

1

0

?

No change

Reset

Set

Forbidden

22

The operation of NAND S-R flip-flop can be analyzed in the same manner employed for

the NOR flip-flop. To under stand the operation of NAND based S-R flip-flop, one must

remember that a low at any input of a NAND gate will force its output high. The truth table for

the NAND based S-R flip-flop is different from that of a NOR based S-R flip-flop. This flip-

flop is called S-R flip-flop, i.e. here S=0 and R=1 will set the flip-flop.

Case 1

The first condition is S=0 and R= 0. When both inputs go to zero, both outputs go to 1, i.e.

Q=1 and Q=1. this condition is ambiguous and should not be used.

Case 2

The condition is S=0 and R= 1 always produces Q=1 regardless of the present state of the

flip-flop output. This condition sets the states of the flip-flop.

Case 3

The condition S=1 and R= 0 forces the lower NAND gate output to 1, i.e. Q=1. Now, both

the inputs of upper NAND gate are 1, and therefore the output of the upper NAND gate is LOW

i.e. Q=0., regardless of the prior state of the flip-flop. This condition resets (clear) the flip-flop

i.e. Q=0 and Q=1.

Case 4

The last condition S=1 and R= 01 does not affect the state of the flip-flop. It remains in its

prior state.

Comparing the NAND flip-flop and the NOR flip-flop, we see that they operate basically in

the same manner except for the following difference: The NOR flip-flop inputs are normally 0

and must be pulsed to 1 state (active HIGH) to change the state of the flip-flop outputs; the

NAND flip-flop inputs are normally 1 and must be pulsed to 0 (active LOW) to change the flip-

flop output state.

CLOCKED R-S flip-flop

The R-S flip-flop that we have seen is an asynchronous sequential logic circuit. In such a

circuit the output changes immediately with the change in its input signal. When two input

signals R and S are applied to a circuit, there is a time delay between these two signals, which

may lead to a wrong output result. In order to overcome this problem of unequal propagation

delay time of input signals, the circuit of R-S flip-flop is modified as shown below.

Inputs Outputs Action

S R Q Q

0

0

1

1

0

1

0

1

?

1

0

Q

?

0

1

Q

Forbidden

Set

Reset

No change

23

Inputs Next state of Q

C S R

0

1

1

1

1

X

0

0

1

1

X

0

1

0

1

No change

No change

Q=0; Reset state

Q=1; Set state

Intermediate

In this circuit, two AND gates and a clock pulse train input are also added to the R-S flip-

flop circuit. This circuit is so called as the clocked R-S flip-flop circuit. Clock supplies the low

and high levels of signal to AND gates C and D regularly. When clock signal is at low level,

AND gates C and D are disabled so at this time, input signals R and S cannot be transferred to

the NOR gates A and B, and therefore, NOR gates A and B, simply behave as a simple latch

circuit, holding the previous values of signal at output. The use of the clock train pulses

accordingly serves the important function of synchronizing the operations that takes place in

digital sequential circuits. They avoid problems posed due to unequal propagation delay time

associated with gates. When the clock signal is present (or at high level) AND gates C and D

are enabled, so at this time, input signals R and S are transferred to NOR gates and output Q is

changed accordingly. In summery, it can be said that there are three input signals R, S and

Clock signal (CLK) which influences the output of flip-flop. Now signal is applied to the input

R and S when clock (CLK) signal is low, so output does not change with the change in input.

When CLK signal becomes HIGH this input signal changes the output of the flip-flop according

to the truth table. So this way input signal is applied to the flip-flop at the same time and

problem of unequal propagation time of the input signal is eliminated. Clocked R-S flip-flop

circuit is a synchronous sequential logic circuit because output state of the circuit changes at

discrete clocked instant of time.

The D Flip-Flop

In a clocked R-S flip-flop two input signals are required to drive the flip-flop which is a

disadvantage with many digital circuits. In some events, both the input signals become high

which is again an undesirable condition. So these drawbacks of clocked R-S flip-flop are

overcome in D (delay) flip-flop. It is nothing but a clocked R-S flip-flop with an inverter in the

R input. The added inverter reduces the number of inputs from two to one. Some times, this

type of flip-flop is called a gated D-latch. The logic diagram, circuit diagram and symbol for D-

flip-flop are shown below.

Fig (a) symbol

24

D

CLK

S

R

CLK

Q

Q

Q

Q

A

1

A

2

D flip-flop using NAND circuit diagram

The operation can be explained using the truth table.

1. When the CLK input is low, the D input has no effect, since the set and reset inputs of the

NAND flip-flop are kept HIGH.

2. When the CLK goes high, the Q output will take on the value of the D input. If CLK=1 and

D=1 the output Q=1, i.e. it follows D input. Similarly, for CLK=1 and D=0 the flip-flop

output will be 0.

If D changes while the CLK is HIGH, Q will follow and change quickly. So D flip-flop

transfers the data bit D to Q as it is, and Q remains in the same state until the next pulse of clock

arrives. Since the transfer of data from the input to the output is delayed, the flip-flop is named

delay (D) flip-flop. The D flip-flop is either used as a delay device or as a latch to store 1 bit

of binary information.

The J K Flip-Flop (Edge-Triggered)

The J-K flip-flop is very versatile and is perhaps the most widely used type of flip-flop. The

J and K designations for the inputs have no known significance except that they are adjacent

letters in the alphabet. The functioning of J-K flop-flop is identical to that of the R-S flip-flop in

RESET, SET, and no change conditions of operation. The difference is that the J-K flip-flop has

no invalid state as does the R-S flip-flop. Therefore, the J-K flip-flop is a very versatile device

that finds wide application in digital devices such as counters, registers, arithmetic logic units,

and other digital systems. In J-K flip-flop clocked R-S flip-flop along with two AND gates are

used.

CLK Input D Output Q

1

1

0

0

1

x

0

1

No change

25

In this circuit J and K are used as input terminals and replace input terminals S and R of the

S-R flip-flop respectively. Input terminal S is supplied by AND gate A

1

to which input signals

are J and flip-flop output Q. Input terminal R is supplied by gate A

2

to which K and Q are the

input signals. The purpose of additional gates A

1

and A

2

is to provide a convenient means by

which the signals that are made to appear at S and R terminals are dependent not only on the

input signals but also on the state of the flip-flop as well. Output state of the flip-flop remains

the same when clock signal is low. But when the clock pulse arrives, input signals J and K

change the output of the flip-flop. Let us consider all four combinations of input signals.

Case 1: When clock signal is high and both input signals J and K are low then both AND

gates A

1

and A

2

are disabled and there is no change in the output state of the flip-flop.

Case 2: When input J is held at logic 0 and input K is held at logic 1. In this case AND gate

A

1

is disabled and condition of AND gate A

2

depends on the output state Q

n

of the

flip-flop. If Q

n

is low then and gate A

2

is also disabled and output state of flip-flop

Q

n+1

remains the same as before. If Q

n

is high then and gate A

2

is enabled and high

logic signal goes to R terminal which changes the output state Q

n+1

of flip-flop from

high to low. So low signal at J and high signal at K input terminals reset the flip-flop

irrespective of output state of flip-flop before the arrival of clock pulse.

Case 3: When input J is held at logic 1 and input K is held at logic 0. In this case AND gate

A

2

is disabled and condition of AND gate A

1

depends on the output state Q

n

of the

flip-flop. If Q

n

is high (or Q is low) then and gate A

1

is also disabled and output state

of flip-flop Q

n+1

remains the same as before. If Q

n

is low (or Q is high) then and gate

A

1

is enabled and high logic signal goes to S terminal which changes the output state

Q

n+1

of flip-flop from low to high. So high signal at J and low signal at K input

terminals set the flip-flop irrespective of the output state of flip-flop before arrival of

clock pulse.

Case 4: When both input signals J and K are held at logic 1. In this case condition of both

AND gates depends on the output state of the flip-flop before arrival of clock pulse.

Suppose Q

n

is high then it makes and gate A

2

enabled, which sends high level signal

to the input terminal R at the arrival of the clock pulse and flop-flop gets reset. Now

Suppose Q

n

is low then it makes and gate A

1

enabled, which sends high level signal to

the input terminal S at the arrival of the clock pulse and flop-flop gets set. Hence it can

be said that in this case the output state of the flip-flop toggles when fresh clock pulse

arrives each time.

CLK Inputs Output

Q

n+1

Action

J K

X

1

1

1

0

0

1

1

0

1

0

1

Q

n

0

1

Q

n

No change

Reset

Set

Toggle

26

Q

Q

Master Slave

Master Slave J K Flip-Flop

This is also known as Pulse Triggered. The term pulse-triggered means that the data are

entered into the flip-flop on the leading edge of the clock pulse. A master-slave J-K flip-flop

can be constructed using two J-K flip-flops as shown below.

The first flip-flop, called the master, is driven by the positive edge of the clock pulse; the

second flip-flop called the slave, is driven by the negative edge of the clock pulse. Therefore,

when the clock input has a positive edge, the master acts according to its J-K inputs, but the

slave does not respond since it requires a negative edge at the clock input. When the clock

input has a negative edge, the slave flip-flop copies the master outputs. But the master does not

respond to the feedback from Q and Q, since it requires a positive edge at its clock input. A

master-slave J-K flip-flop constructed using NAND gates is shown in the figure

It consists of two flip-flops connected in series. The first set of 4 NAND gates form the

master flip-flop and the second set from the slave flip-flop. When the clock is positive, a

change in J and IK inputs cause a change of state in the master flip-flop. During this period, the

slave retains its previous state and serves as a buffer between the master and the output. When

the clock goes negative, the master flip-flop does not respond, i.e. it maintains its previous state,

while the slave flip-flop is enabled and changes its state to that of the master flip-flop. The new

state of the slave then becomes the state of the entire master-slave flip-flop. The operation of

master-slave J-K flip-flop for different J-K input combinations can be explained as follows:

If J=1 and K=0, the master flip-flop sets on the positive clock edge. The HIGH Q output of

the master drives the input J of the slave. So, when the negative clock edge hits, the slave also

sets. The slave flip-flop copies the action of the master flip-flop.

If J=0 and K=1, the master flip-flop resets on the leading edge of the clock pulse. The

HIGH Q output of the master drives the input K of the slave. Then, the slave flip-flop resets at

the arrival of the trailing edge of the CLK pulse. Once again, the slave flip-flop copies the

action of the master flip-flop.

27

If J=K=1, the master flip-flop toggles on the positive clock edge and the slave toggles on

the negative edge. The condition J=k=0 input does not produce any change. Master-slave flip

flops operate from a complete clock pulse, and the outputs change on the negative mission.

T Flip-Flop

This flip-flop is basically a J-K flip-flop. This is also called Trigger or Toggle flip-flop.

This has only a single data input(T), a clock input and two outputs Q and Q. The T-type flip-

flop is obtained from a J-K flip-flop by connecting its J and K inputs together. The designation

T comes from the ability of the flip-flop to toggle or complement its state. The block

diagram of a T-flip-flop and its circuit implementation using J-K flip-flop are shown below.

The J and K inputs are wired together. The truth table is also shown. When the T input is in

the 0 state (i.e. J=K=0) prior to a clock pulse the Q output will not change with clocking. When

the T input is at a 1 (i.e. J=K=1) level prior to clocking, the output will be in the Q state after

clocking. In other words, if the T input is a logical 1 and the device is clocked, the output will

change state regardless of what output was prior to clocking. This is called toggling hence the

name T flip-flop. The truth table shows that when T=0, then Q

n+1

=Q

n

,i.e. the next state is the

same as the present state and no change occurs. When T=1, then Q

n+1

=Q

n

,i.e. the state of the

flip-flop is complemented.

Application of T- flip-flop

T-flip flop is most often seen in counters and sequential counting networks because of its

inherent divide-by-2 capability. When a clock pulse is applied the output changes state once in

every input cycle, thus repeating one cycle for every two input cycles. This is the action

required in many cases for binary counters.

REGISTERS

Sequential circuit and an important building block used in digital systems like multipliers,

dividers, memories, microprocessors etc. A register is a group of flip-flops. Each flip-flop is

capable of storing 1 bit of information. An n-bit register consists of a group of n-flip-flops

capable of storing n-bits of binary information. In addition to the flip-flops a register may have

combinational gates that perform certain data processing tasks. A register consists of a group of

flip-flops and gates that effect their transition. The flip-flops hold the binary information and

the gates determine how the information is transferred into the register. Various types of

registers are available commercially. The simplest register is one that consists of only flip-flops

without any gates. Figure below shows such a register constructed with four D-type flip-flops.

The common clock input triggers all flip-flops on the positive edge of each pulse and the binary

data available at the 4 inputs are transferred into the 4-bit register. The four outputs can be

sampled at any time to obtain the binary information stored in the register.

28

The clear output goes to the R(reset) input of all four flip-flops. When this Input goes to zero,

all flip-flops are reset asynchronously. The clear input is useful for clearing the register to all

0s prior to its clocked operation. The R inputs must be maintained at logic 1 during normal

clocked operation.

SHIFT REGISTERS

A register that is used to store binary information is known as a memory register. A register

capable of shifting binary information either to the right or to the left is called a shift register.

The shift register permits the stored data to move from a particular location to some other

location within the register. In a shift register the flip-flops are connected in such a way that the

bits of a binary number are entered into the shift register, shifted from one position to another

and finally shifted out. There are two methods of shifting viz., (1) serial shifting and (2) parallel

shifting. The serial shifting method shifts one bit at a time for each clock pulse in a serial

fashion, beginning with either MSB or LSB.

For example, a 4-bir register requires four clock pulses to shift a bit from the input to the

output. In parallel shifting operations all the data (input and output) get shifted simultaneously

during a single clock pulse. Hence parallel shifting method is much faster than the serial

shifting method. These two methods can be used to shift into a register and out of the register.

29

n-bit

Serial

Data

input

Serial

Data

output

n-bit

Serial

Data

input

Parallel Data outputs

MSB LSB

n-bit

Parallel Data inputs

Serial

Data

output

MSB LSB

n-bit

Parallel Data outputs

MSB LSB

MSB LSB

Parallel Data inputs

Shift registers are classified into the following four types based on how binary information

is entered or shifted out:

1. Serial-in Serial-out (SISO)

2. Serial-in Parallel-out (SIPO)

3. Parallel-in Serial-out (PISO)

4. parallel-in Parallel-out (PIPO)

The block diagrams for the 4 basic register types are shown below. Registers can be

designed using discrete flip-flops (S-R, J-K, and D type). An n-bit shift register consists of n

flip-flops and the required gates to control the shift operation. Registers are also available as

MSI devices.

Shift registers are used in digital systems for temporary storage of information, data

manipulation and transferring. In addition, they are used in counting circuits, such as simple

counters, variable modulo counters, Up/Down counters and increment counters.

SERIAL IN SERIAL OUT shift register

This type of shift register accepts data serially, i.e. one bit at a time on a single input line. It

produces the stored information on its single output also in serial form. Data may be shifted left

(from Low to high order bits) using shift-left register or shifted right (from high to low order

bits) using shift-right register.

Shift-left register:

30

A shift-left register can be built using J-K flip-flops or D-flip-flops as shown in the figure

(a) and (b). A J-K flip-flop based shift register requires connection of both J and K inputs.

Input data are connected to the J and K inputs of the right most (lowest order) flip-flop. To

input a 1, one should apply a 1 at J input, i.e. J=1 and K=0; to input a 0, a 0 at J input i.e. J=0

and k=1, should be applied. When the clock pulse is applied, the data will be shifted bit by bit

to the left. In the shift register using D flip-flops delay (D) input of the right most flip-flops is

used as a serial input line. To input a 1, one should apply a 1 at D input and to input data 0, a 0

at the D input should be applied. As shown the clock pulse is applied to all the flip-flops

simultaneously. When the shift or clock pulse occurs, each flip-flop is set or reset according to

the data at the respective flip-flop input. Thus the input data bit at the serial input line is entered

into stage A by the first shift pulse. At the same time, the data of stage A is shifted into stage B

and so on for the following stages. For each shift pulse, data stored in the register stage shifts to

the left by one stage. New data is entered into the stage A, where as the data present in stage D

are shifted out (to the left) for use by some other shift register or other building block of digital

system.

Shift right register:

31

SERIAL IN PARALLEL OUT S.R.

It consists of one serial input, and out puts are taken from all the flip-flops in parallel. A bit

serial in parallel out shift register is shown below.

In this register data is shifted in serially but shifted out in parallel. In order to shift the data

out in parallel, it is necessary to have all the data available at the outputs at the same time. Once

the data is stored, each bit appears on its respective output line and all the bits are available

simultaneously, rather than on a bit-by-bit basis as with the serial output.

Parallel in Serial Out S.R.

For a register with parallel data inputs, the bits are entered simultaneously into their respective

flip-flops, rather than a bit-by-bit Basis on one line. A four bit PISO register is illustrated in

the figure.

Let D

1

, D

2

, D3 and D

4

be the 4 parallel data-input lines and SHIFT/LOAD is a control input

that allows the 4 bits of data inputs to enter into the register in parallel or shift the data in serial.

When SHIFT/LOAD is low, the data at the parallel inputs are applied to the D inputs of the

respective flip-flop. When a clock pulse is applied the flip-flops with D=1 will be SET and the

flip-flops with D=0 will be RESET, thereby storing all 4 bits simultaneously. When

SHIFT/LOAD is HIGH the data bits shift right from one stage to the next.

Parallel In Parallel Out S.R.

In this type of register, data inputs can be shifted either in or out of the register in parallel. A 4-

bit parallel-in-parallel-out shift register is shown below.

32

COUNTERS

A counter by function is a sequential circuit consisting of a set of flip-flops connected in a

suitable manner to count the sequence of the input pulses presented to it in digital form.

Counters can be broadly classified under 3 heads as follows:

1. Asynchronous and Synchronous counters.

2. Single and multimode counters

3. Modulus Counters.

An asynchronous or ripple counter can be constructed using minimum hardware. Here each

flip-flop is triggered by the output from the previous flip-flop which limits its speed of

operation. This is also called a serial counter.

In synchronous counters, the speed limitation of ripple counters is overcome by applying

clock pulses simultaneously to all the flip-flops. Hence these are also called parallel counters.

Single mode counters operate in a single mode i.e. it counts either in the UP mode or in the

DOWN mode, where as multimode counters operate in both UP and DOWN mode.

BINARY RIPPLE COUNTER

A binary ripple counter consists of a series connection of complementing flip-flops, with the

output of each flip-flop connected to the C input of the next higher-order flip-flop. The flip-flop

holding the least significant bit receives the incoming count pulses. A complementing flip-flop

can be obtained from a J-K flip-flop with the J and K inputs tied together or from a T flip-

flop. A third possibility is to use a D flip-flop with the complement output connected to the D

input. In this way the D input is always the complement of the present state and the next clock

pulse will cause the flip-flop to complement. The logic diagram of two 4 bit binary ripple

counters is shown below. Fig. (a) Shows counter constructed with complementing flip-flops of

the T type and fig (b) shows the same with the D flip-flops.

33

Ripple counter with T flip-flop

Ripple counter with D flip-flop

The output of each flip-flop is connected to the C input of the next flip-flop in sequence.

The flip-flop holding the least significant bit receives the incoming count pulses. The T inputs

of all the flip-flops are connected to a permanent logic-1. This makes each flip-flop

complement if the signal in its C input goes through a negative transition. The bubble in front of

the dynamic indictor symbol next to C indicates that the flip-flops respond to the Negative

edge transition of the input. The negative transition occurs when the output of the previous

flip-flop to which C is connected goes from 1 to 0. To understand the operation of the 4-bit

binary ripple counter, refer to the first nine binary numbers listed in the following table.

Binary Count Sequence

A

3

A

2

A

1

A

0

0

0

0

0

0

0

0

0

1

0

0

0

0

1

1

1

1

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

Count

34

The count starts with binary 0 and increments by one with each count pulse input. After the

count of 15, the Counter goes back to 0 to repeat the count. The least Significant bit A

0

is

complemented with each count pulse input. Every time that A

0

goes from 1 to 0, it

Complements A

1.

Every time that A

1

goes from 1 to 0, it Complements A

2

. Every time that A

2

goes from 1 to 0, it Complements A

3

and so on for any other higher order bits of a ripple

counter.

For example, consider the transition from count 0011 to 0100. A

0

is complemented with the

count pulse. Since A

0

goes from 1 to 0, it triggers A

1

and complements it. As a result A

1

goes

from 1 to 0, which in turn complements A

2

, changing it from 0 to 1. A

2

does not trigger A

3

because A

2

produces a positive transition and the flip-flop responds only to negative transitions.

Thus the count from 0011 to 0100 is achieved by changing the bits one at a time, so the count

goes from 0011 to 0010, then to 0000, and finally to 0100.

The flip-flops change one at a time in succession and the signal propagates through the

counter in ripple fashion from one stage to the next. A binary counter with reverse count is

called a binary count-down counter. In a downward counter, the binary count is decremented by

1 with every input count pulse. The diagram of a binary count-down counter looks the same as

before, provided all the flip-flops trigger on the positive edge of the clock. (the bubble in the C

inputs must be absent.)

BCD Ripple Counter

A decimal counter follows a sequence of 10 states and returns to 0 after the count of 9. Such a

counter must have at least 4 flip-flops to represent each decimal digit, since a decimal digit is

represented by a binary code with at least four bits. If BCD is used, the sequence of states is as

shown in the state diagram below.

This is similar to a binary counter, except that the state after 1001 is 0000. The logic diagram of

a BCD ripple counter using JK flip-flops is shown below.

The four outputs are designated by the letter symbol Q with a numeric subscript equal to the

binary weight of the corresponding bit in the BCD code. Note that the output of Q

1

is applied to

the C inputs of both Q

2

and Q

8

and the output of Q

2

is applied to the C input of Q

4

.

The J and K inputs are connected either to a permanent 1 signal or to outputs of other flip-

flops. A ripple counter is an asynchronous sequential circuit. Signals that affect the flip-flop

transition depend on the way they change from 1 to 0. The operation of the counter can be

explained by a list of conditions for flip-flop transitions. These conditions are derived from the

logic diagram and from knowledge of how a JK flip-flop operates. When the C input goes from

1 to 0, the flip-flop is set if J=1, is cleared if K=1, is complemented if J=K=1, and is left

unchanged if J=K=0. To verify that these conditions result in the sequence required by a BCD

ripple counter, it is necessary to verify that the flip-flop transitions indeed follow a sequence of

states as specified by state diagram.

35

Q

1

changes state after each clock pulse. Q

2

complements every time Q

1

goes from 1 to 0 as

long as Q

8

=0. When Q

8

becomes 1, Q

2

remains at 0. Q

4

complements every time Q

2

goes from

1 to 0. Q

8

remains at 0 as long as Q

2

or Q

4

is 0. When both Q

2

ands Q

4

become 1, Q

8

complements when Q

1

goes from 1 to 0. Q

8

is cleared on the next transition of Q

1

. the BCD

counter shown above is a decade counter, since it counts from 0 to 9. To count in decimal from

0 to 99 we need a two-decade counter. To count in decimal from 0 to 999 we need a three-

decade counter.

Multiple decade counters can be constructed by connecting BCD counters in cascade one

for each decade. A three-decade counter is shown below

36

SYNCHRONOUS COUNTERS

Synchronous counters are different from ripple counters in that clock pulses are applied

to the inputs of all flip-flops. A common clock triggers all flip-flops simultaneously rather than

one at a time in succession as in a ripple counter. The decision whether a flip-flop is to be

complemented or not is determined from the values of the data inputs such as T of J and K at

the time of the clock edge. If T=0 or J=K=0, the flip-flop does not change state. If T=1 or

J=K=1, the flip-flop complements. The circuit diagram of a 3-bit synchronous binary counter is

shown:

In this counter two AND gates are also used with three T flip-flops. All the flip-lops are

triggered by the same clock signal. T input terminal of flip-flop A is supplied with high level

signal, so flip-flop A toggles just at the end of every pulse. T input of flip-flop B is supplied

with AND gate A

1

. AND gate A

1

turns ON only when output of flip-flop A is high and only

during his duration flip-flop toggles. Flip-flop C is supplied with the AND gate A

2

, AND gate

A

2

turns on only when outputs of flip-flop B and AND gate A

1

are high and only during this

duration flip-flop C toggles.

Initially all the flip-flops are reset to 0 so out puts Q

C

Q

B

Q

A

= 000. But just at the end of the

first clock pulse, flip-flop A toggles and output Q

A

changes from logic 0 t0 1, which also turns

on AND gate A

1

. This does not make any change in the output states of flip-flops B and C

because T input terminals of flip-flops B and C were at logic 0 before the arrival of the first

clock pulse. So out put Q

C

Q

B

Q

A

becomes 001, just at the end of the first clock pulse.

Input terminals T of the flip-flop A and B are at logic 1 before the arrival of the 2

nd

clock

pulse so they toggle just at the end of 2

nd

clock pulse. This changes output of flip-flop A to

logic 0 and output of flip-flop B to logic 1. So AND gate A

1

turns off and gate A

2

remains off.

So at the end of second clock pulse output Q

C

Q

B

Q

A

becomes 010.

Just at the end of third clock pulse only flip-flop A toggles and its output changes to logic 1.

It turns AND gate A

1

ON. It also turns AND gate A

2

ON because now both inputs of AND gate

A

2

are HIGH. Thus just at the end of 3

rd

clock pulse output Q

C

Q

B

Q

A

= 011.

Just at the end of the 4

th

clock pulse, T inputs of all flip-flops are high so all flip-flops toggle

and output Q

C

Q

B

Q

A

changes from 011 to 100. It also turns off both AND gates A

1

and A

2

.

Just at the end of the 5

th

clock pulse only flip-flop A toggles and output Q

C

Q

B

Q

A

becomes

101. This process continues with every new clock pulse as shown in the table below.

Just at the end of the 7

th

pulse, output of each flip-flop is at logic 1, and just at the end of the

8

th