Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Lab I Elc215

Caricato da

Abiel RosaTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Lab I Elc215

Caricato da

Abiel RosaCopyright:

Formati disponibili

UNIVERSIDAD DE EL SALVADOR

FACULTAD DE INGENIERA Y ARQUITECTURA

ESCUELA DE INGENIERA ELCTRICA

ELECTRNICA II

Laboratorio N1: Tcnicas de polarizacin y diseo de etapas amplificadoras con

JFETs.

Grupo de laboratorio: 02

Catedrtico: Ing. Jos Ramos Lpez.

Instructor: Guillermo Cornejo.

Alumnos: Carnet:

Br. Martnez Escobar, Jos Roberto ME09032

Br. Villalobos Alberto, Jorge Armando VA10041

Electrnica II Pgina 2

Resumen de la prctica.

En esta primer laboratorio conoceremos el uso y aplicacin del JFET (Junction Field Effect

transistor) como un dispositivo equivalente a un MOSFET de agotamiento, para lo cual

hemos realizado las 2 primeras practicas de laboratorio.

La primera asignacin de esta prctica se ha calculado I

DSS

y V

GS (off)

.

Sabiendo que I

DSS

es

la corriente que pasa por el transistor cuando V

GS

es cero; lo hemos realizado de manera

experimental en el laboratorio y en simulacin en TINA para poder comparar ambos

resultados. Luego Con un amplificador con una ganancia mayor que 50 utilizando un

2N4341, dicho amplificador se ha implementado fsicamente y se ha realizado su respectiva

simulacin, luego Diseamos un seguidor de fuente con impedancia mayor a la entrada de

1M y comprobamos los resultados prcticos con los simulados; sin mas que agregar

continuamos con el desarrollo explicacin de la practica

Materiales y equipo utilizados.

A continuacin se presenta la lista de materiales y equipo utilizados para la practica de los

circuitos realizados en este primer laboratorio:

Equipo:

Osciloscopio

Generador de seales.

Protoboard.

Materiales:

JFET 2N4341.

Amp-Op LM741.

1 Resistencias 900k.

1 Resistencia 100k.

1 Resistencia 82k.

1 Resistencia de2.2k.

2 Capacitores de 0.1 uF.

1 Capacitor de 220 uF.

Electrnica II Pgina 3

Trabajo de laboratorio

1. Descripcin del circuito:

En esta prctica medimos la I

DSS

con la ayuda del multmetro entre

y el drenaje del

transistor y V

GS (off)

midiendo el voltaje de salida.

Para encontrar I

DSS

ponemos al transistor en saturacin y con VG igual a cero.

De acuerdo a lo visto en la gua de laboratorio se procede a la construccin de los

siguientes circuitos:

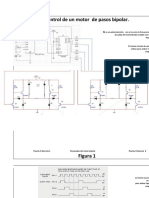

Circuitos para medir I

DSS

y V

GS (off)

Figura 1 Muestra el voltaje V

GS (off)

para el JFET 2N4341.

Parte a)

Valores obtenidos:

I

DSS

[mA] V

GS(off)

[V]

3.89 -2.81

Tabla 1 Mediciones de I

DSS

y V

GS

(off) para la practica 1 de

la parte a.

Nota: Tomando en cuenta que para calcular I

DSS

tuvimos que poner Vgs igual a cero.

Electrnica II Pgina 4

Parte b)

Conectamos un amplificador entre la fuente y la entrada del JFET y medimos de igual

manera la I

DSS

y V

GS(off)

.

Figura 1.1 Muestra el JFET 2N4341 Conectado con un Amplificador LM741 de la practica 1 parte b.

Calculando R

real

en el circuito para reducir la corriente en un factor de 100 y poder conocer

Vo dado esto llegamos a la siguiente formula:

385.60k

Ya que calculamos la R para la entrada de nuestro circuito midiendo la tensin en la salida

llegamos al siguiente resultado:

Figura 1.2 Muestra Vo medido en el laboratorio de la practica 1 parte b.

Electrnica II Pgina 5

Para el clculo de I

DSS

y V

GS (off)

con el 2N4341 encontramos un promedio de los resultados

obtenidos en el laboratorio con otros grupos y llegamos a obtener la siguiente tabla:

I

DSS

[mA] V

P

=V

O

[V]

3.50 -2.06

3.79 -2.26

3.89 -2.81

4.16 -2.81

Tabla 1.1 Valores experimentales de I

DSS

y Vo.

De ello pudimos escoger I

DSS

y V

GS (off)

Max/Min para el clculo del segundo experimento.

I

DSS

Max.[mA] I

DSS

Min. [mA] V

P

=V

O

Max.[V] V

P

=V

O

Min.[V]

4.16 3.50 -2.81 -2.06

Tabla1.2 Datos escogidos para los valores mximos y mnimos de I

DSS

y V

GS

Simulacin en TINA:

Para la I

DSS

en la Simulacin se muestra el siguiente circuito:

Figura 1.3 Medicin I

DSS

en la simulacin para el JFET 2N4341.

Figura1.4 Medicin de V

GS(

off) en la simulacin del circuito.

Electrnica II Pgina 6

Ahora compararemos los valores de I

DSS

y V

GS

Sabiendo que I

DSS

es la corriente que pasa

por el transistor cuando V

GS

es cero esto se demostrara en la siguiente grfica.

A continuacin compararemos los resultados obtenidos con los resultados tericos

graficados en octave:

Figura 1.6 Grafica de I

D

vrs V

GS

Figura 1.5 Grafica Simulada en Octave de I

D

vrs V

GS

de los datos obtenidos.

Electrnica II Pgina 7

Figura 1.6 Grafica de G

m

vrs V

GS

.

Figura 1.5 Grafica Simulada en Octave de G

m

vrs V

GS

de los datos obtenidos.

Discusin: Como podemos observar los valores encontrados de I

DSS

y V

GS (off)

son bastante

cercanos a los q se especifican en las hojas de datos; este margen de error puede atribursele

a algn leve error en la toma de mediciones; sin embargo los valores obtenidos en esta

prctica son bastante aceptables.

Electrnica II Pgina 8

2. Disear un amplificador con ganancia mayor que 50, usando un 2N4338/2N4339/2n4341

Usar las tcnicas discutidas en el laboratorio.

Introduccin: Al estudiar y analizar los amplificadores se puede observar que a la hora de

calcular sus resistencias es una decisin muy importante ya que escogerlas depende de el

conocimiento que se tenga sobre dicho tema de no ser asi podramos obtener resultados no

deseables.

Descripcin del circuito: Para el diseo de este amplificador se utilizara el diseo de

fuente comn, debido a que es una de las conexiones con un clculo de diseo ms fcil de

entender y analizar.

Figura 2.1 Circuito amplificador de ganancia. Figura 2.2 Equipo utilizado para la prctica

Av [V/V] Vp Max [V]

Max [mA]

Vp Min [V]

Min [mA] Gm [mA/V]

50 -2.81 4.16 -2.06 3.50 1

Tabla 2.1 Valores obtenidos para el diseo del Amplificador como fuente comn.

Tomamos encuenta estas ecuaciones para llevar a cabo el diseo del circuito amplificador

conganancia mayor de 50.

I. (

) (

)

II.

III.

IV.

Electrnica II Pgina 9

V.

(

VI.

(

VII.

||

||

VIII.

IX.

|

|

X.

Solucin:

) [

( )()

()

( )()

()

Electrnica II Pgina 10

() [

() [

Para el clculo de divisor de tensin:

()() ||

Electrnica II Pgina 11

Entonces:

Simultaneando da como resultado:

Resultados obtenidos:

Av [V/V] Vp Max [V]

Max [mA]

Vp Min [V]

Min [mA] Gm [mA/V]

50 -2.81 4.16 -2.06 3.50 1

Tabla 2.1 Valores obtenidos para el diseo del Amplificador como fuente comn.

Rs [k]

[k]

[V]

[k]

[k]

2.43 50 3.01 900 100

Tabla 2.2 Valores calculados para el diseo del Amplificador como fuente comn.

Discusin: Para el diseo de estos amplificadores existen mltiples soluciones, por esta

razn es necesario que todo este anlisis antes de implementar el circuito en el laboratorio

venga acompaado de su respectiva simulacin.

Electrnica II Pgina 12

Simulaciones en TINA:

Figura 2.3 Diagrama esquemtico del amplificador de la simulacin en TINA.

Estas mediciones nos dan una forma directa para lograr calcular la ganancia, que viene

dada por:

Figura 2.3 Grficas de entrada y salida amplificada de la simulacion en TINA.

Electrnica II Pgina 13

Figura 2.4 Muestra el Vo y Vi del JFET como amplificador comn en el laboratorio.

Calculamos la ganancia experimenta en el circuito mediante los resultados obtenidos en el

osciloscopio llegamos al clculo de la ganancia de la siguiente manera:

Discusin: Los resultados obtenidos en el laboratorio, al introducir una seal de 52mV, Se

obtiene la respuesta del circuito amplificador propuesto, El cual confirma que

efectivamente la ganancia del amplificador fuente comn, anda por los 50

.

Electrnica II Pgina 14

3. El seguidor fuente es una configuracin de mucha utilidad; su elevada impedancia de

entrada y baja impedancia de salida lo hacen til para transformaciones de impedancia

entre FETS y BJTs.

Introduccin: La baja impedancia de entrada es la clave para poder desarrollar los clculos

y armar un buen circuito de un seguidor fuente

Descripcin del circuito: Para esta asignacin se recomend una impedancia mayor a 1M

y mantener el mismo valor de transconductancia que se utiliz en el experimento 2 del

amplificador de ganancia que fue de Gm = 1mA/V

Frmulas a utilizar:

I.

)

II.

)

III.

Solucin

()

()

|

Debido a la impedancia de entrada que se ha pedido implementar en el sistema, se eligio

una resistencia de compuerta de

Electrnica II Pgina 15

Simulacin en TINA

Figura 3.1 Circuito del seguidor con su respectivo Vo de salida.

Obteniendo la ganancia del circuito seguidor fuente:

Para una mayor visualizacin de este circuito presentamos una grfica de entrada y salida

de este circuito realizada en TINA

Figura 3.2 Grfica de entrada y salida del seguidor fuente con el JFET simulado en TINA.

Electrnica II Pgina 16

CONCLUSIONES

En base al conocimiento adquirido con la elaboracin de este reporte hemos concluido de la

siguiente manera:

Para los datos obtenidos en el laboratorio de la practica 1 pudimos conocer los

respectivos valores de I

DSS

y V

GS (off).

Comparando cada uno de los resultados

podemos decir que estn en el rango en la hoja de especificaciones del JFET

2N4341 y se comprob que el factor de ganancia va a depender de la resistencia del

drenaje, gracias a este factor podremos variar considerablemente el voltaje en la

salida.

Una de las principales causas por las que el amplificador de ganancia 50 no

funcion en su totalidad fue debido a que en la teora y clculos los datos obtenidos

no son tan fciles de obtener en la realidad y debido a eso ya hay un margen de error

significativo por lo tanto a la hora de querer implementar nuestro diseo deben

tomarse en cuenta esas consideraciones de los valores obtenidos y los valores

verdaderos que se utilizan en el circuito.

Como pudo observarse en el laboratorio una de las claves para disear un buen

seguidor de fuente es que tenga una gran impedancia de entrada, ya que esto ayuda

a la hora de tomar mediciones.

Electrnica II Pgina 17

BIBLIOGRAFIA

Circuitos Microelectronicos, 5ta Edicin, Adel S. Sedra Kenneth C. Smith

Ing. Jos Ramos Lpez. Notas de Clase de Electrnica II. Universidad de El

Salvador, 2014.

Electrnica, 2da Edicin, Allan R. Hambley.

Electrnica II Pgina 18

ANEXOS

Configuracin del JFET 2N4341.

Hoja tcnica:

Electrnica II Pgina 19

Configuracin del Amplificador Operacional LM741

Electrnica II Pgina 20

Hoja tcnica:

Potrebbero piacerti anche

- Armónicas en Sistemas Eléctricos IndustrialesDa EverandArmónicas en Sistemas Eléctricos IndustrialesValutazione: 4.5 su 5 stelle4.5/5 (12)

- Montaje y mantenimiento de transformadores. ELEE0109Da EverandMontaje y mantenimiento de transformadores. ELEE0109Nessuna valutazione finora

- Electrónica Analógica de Comunicaciones.Documento10 pagineElectrónica Analógica de Comunicaciones.Alexander BaldecNessuna valutazione finora

- Servicios complementarios en sistemas eléctricos de potencia: Análisis y modelamientoDa EverandServicios complementarios en sistemas eléctricos de potencia: Análisis y modelamientoValutazione: 5 su 5 stelle5/5 (1)

- Taller TX-RX Examen Fin Carrera LLENO ESTUDIARDocumento7 pagineTaller TX-RX Examen Fin Carrera LLENO ESTUDIARCristian CrsNessuna valutazione finora

- Diseño de sistemas combinacionales y secuenciales en VHDLDocumento5 pagineDiseño de sistemas combinacionales y secuenciales en VHDLSANTIAGO ISRAEL LOZADA ZAMBRANONessuna valutazione finora

- Informe de Electronica TecsupDocumento19 pagineInforme de Electronica TecsupBryan Escobedo0% (2)

- Practica 1 PDFDocumento7 paginePractica 1 PDFsamir ernesto duran ortegaNessuna valutazione finora

- Amplificador Realimentado NegativamenteDocumento5 pagineAmplificador Realimentado NegativamenteDiego Ramos LamaNessuna valutazione finora

- Reporte Laboratorio 1 Electronica 2Documento9 pagineReporte Laboratorio 1 Electronica 2Ronny DiazNessuna valutazione finora

- Anual de Rácticas: E A G I E I A 3 º Curso, 1 Cuatrimestre Curso Académico 2022-2023Documento9 pagineAnual de Rácticas: E A G I E I A 3 º Curso, 1 Cuatrimestre Curso Académico 2022-2023carlos cevallosNessuna valutazione finora

- Informe de Laboratorio N ° 3Documento10 pagineInforme de Laboratorio N ° 3Josep LopezNessuna valutazione finora

- Práctica 06 Lab Electrónica II 19-19Documento6 paginePráctica 06 Lab Electrónica II 19-19Miguel AngelNessuna valutazione finora

- Informe Práctica 5 - Amplificador SumadorDocumento8 pagineInforme Práctica 5 - Amplificador SumadorByronJorqueNessuna valutazione finora

- Informe Final 2Documento11 pagineInforme Final 2JOEL HUAMAN ZARATENessuna valutazione finora

- Circuitos Electronicos 2 Informe Final 1 Configuracion en CascadaDocumento10 pagineCircuitos Electronicos 2 Informe Final 1 Configuracion en CascadaYeli FabulosaNessuna valutazione finora

- Informe Nº6-Electrónica Analógica Barzola SalazarDocumento16 pagineInforme Nº6-Electrónica Analógica Barzola SalazarElita BarzolaNessuna valutazione finora

- Comparativa de parámetros reales vs ideales de OpAmps LM324 y TL084Documento3 pagineComparativa de parámetros reales vs ideales de OpAmps LM324 y TL084Breyner StevensNessuna valutazione finora

- Guia03 201800EmComun Medida de La GananciaCircElectrónicosIIDocumento4 pagineGuia03 201800EmComun Medida de La GananciaCircElectrónicosIIgustagarotoNessuna valutazione finora

- Configuración en cascada de amplificadores operacionalesDocumento6 pagineConfiguración en cascada de amplificadores operacionalesNicolás VelásquezNessuna valutazione finora

- Configuraciones básicas OPAMP - Parte 2Documento5 pagineConfiguraciones básicas OPAMP - Parte 2Zach BrianNessuna valutazione finora

- Sin TítuloDocumento8 pagineSin TítulomarcosNessuna valutazione finora

- Amplificador con base común - Actividad 2-4Documento18 pagineAmplificador con base común - Actividad 2-4didielNessuna valutazione finora

- Reporte Practica 01 Garcia Ibarra RafaelDocumento8 pagineReporte Practica 01 Garcia Ibarra RafaelRafael Garcia IbarraNessuna valutazione finora

- Laboratorio 1 CascadaDocumento25 pagineLaboratorio 1 CascadaJOAQUIN ALESSANDRO CABRERA CHAMORRONessuna valutazione finora

- Practica 1, Electrónica 2Documento7 paginePractica 1, Electrónica 2Nicolas Jimenez OrduzNessuna valutazione finora

- Final IDocumento8 pagineFinal IMathias Chero MendozaNessuna valutazione finora

- Informe de Lab 7 de Electronica IDocumento21 pagineInforme de Lab 7 de Electronica ISergio Meneces FloresNessuna valutazione finora

- Amplificador multietapa con acoplamiento directo e impedancia de entradaDocumento10 pagineAmplificador multietapa con acoplamiento directo e impedancia de entradaVíctor Renato Díaz CajasNessuna valutazione finora

- Laboratorio 1. Aspectos Básicos Del Amplificador OperacionalDocumento7 pagineLaboratorio 1. Aspectos Básicos Del Amplificador OperacionalHenryLozanoPereiraNessuna valutazione finora

- Amplificador cascada configuraciónDocumento11 pagineAmplificador cascada configuraciónDiego Chinguel JimenezNessuna valutazione finora

- Lab 3 Jfet (Finalizado)Documento14 pagineLab 3 Jfet (Finalizado)wariocandelarioNessuna valutazione finora

- Analisisde La Pequeña ExtraDocumento22 pagineAnalisisde La Pequeña ExtraCesar MoralesNessuna valutazione finora

- Informe Final Nº1Documento8 pagineInforme Final Nº1Fady A. Rodas HuaracaNessuna valutazione finora

- Amplificación BJT con divisor de voltajeDocumento9 pagineAmplificación BJT con divisor de voltajeangelNessuna valutazione finora

- Amplificador Diferencial Con BJTDocumento8 pagineAmplificador Diferencial Con BJTHumber XsLxNessuna valutazione finora

- 3 OpamDocumento9 pagine3 OpamKatherine María Zambrano CasasNessuna valutazione finora

- Efecto de Frecuencia en Ganancia de OpAmpsDocumento3 pagineEfecto de Frecuencia en Ganancia de OpAmpsRicardo HegelNessuna valutazione finora

- Amplificador Simétrico Complementario Final NuestroDocumento5 pagineAmplificador Simétrico Complementario Final NuestroCristhian Roman VicharraNessuna valutazione finora

- Guia 06 PDFDocumento6 pagineGuia 06 PDFJei VegaNessuna valutazione finora

- Lab2 MDocumento9 pagineLab2 MJulio Orlando MedranoNessuna valutazione finora

- PRACTICA Amplificador de InstrumentacionDocumento7 paginePRACTICA Amplificador de InstrumentacionAlexNessuna valutazione finora

- p7 AmplisDocumento3 paginep7 AmplisitbaleNessuna valutazione finora

- Practica 1 AmplificacionabiDocumento8 paginePractica 1 AmplificacionabiTirone GonzálezNessuna valutazione finora

- Práctica 05 Electrónica I 21ADocumento7 paginePráctica 05 Electrónica I 21AJoffre EstradaNessuna valutazione finora

- Amplificadores diferenciales y de instrumentaciónDocumento5 pagineAmplificadores diferenciales y de instrumentaciónDayanaNessuna valutazione finora

- Amplificador Operacional AplicacionesDocumento10 pagineAmplificador Operacional AplicacionesGo DanNessuna valutazione finora

- Guia 1 de Circuitos Electronicos II 2021Documento4 pagineGuia 1 de Circuitos Electronicos II 2021CanalDTodoUnPoco PCNessuna valutazione finora

- Respuesta en Freq. Emisor ComúnDocumento2 pagineRespuesta en Freq. Emisor ComúnDayana Moreno BedoyaNessuna valutazione finora

- Lab2 Bossio NarváezDocumento11 pagineLab2 Bossio NarváezCristian BossioNessuna valutazione finora

- Gonzalez Miguel Miguel Angel - P3Documento9 pagineGonzalez Miguel Miguel Angel - P3Miguel Angel GonzalezNessuna valutazione finora

- Reporte Lab 1 IEL115Documento25 pagineReporte Lab 1 IEL115Saúl Gutiérrez ArguetaNessuna valutazione finora

- Informe Final Practicas de Laboratorio Electrónica AnálogaDocumento10 pagineInforme Final Practicas de Laboratorio Electrónica Análogajorge eduardo aza sanchezNessuna valutazione finora

- Práctica 5 Seguidor - Sum - ResDocumento20 paginePráctica 5 Seguidor - Sum - Resdiegofer90100Nessuna valutazione finora

- Lab 07Documento5 pagineLab 07Juan CuervoNessuna valutazione finora

- Practica 1 Electronica 2Documento7 paginePractica 1 Electronica 2MiguelNessuna valutazione finora

- Reporte de Practica 5 OPAMS Equipo 3Documento12 pagineReporte de Practica 5 OPAMS Equipo 3Jonathan CamarilloNessuna valutazione finora

- P4 MUII. Interfaces Analógicas 2021 - 2022Documento12 pagineP4 MUII. Interfaces Analógicas 2021 - 2022Clara PalaoNessuna valutazione finora

- Practica 1 Amplificador Emisor ComúnDocumento6 paginePractica 1 Amplificador Emisor ComúnReniey SmithNessuna valutazione finora

- Amplificadores instrumentación ancho bandaDocumento6 pagineAmplificadores instrumentación ancho bandaJavi ColorsNessuna valutazione finora

- AO integrador y derivadorDocumento10 pagineAO integrador y derivadorLalo SanchezNessuna valutazione finora

- Amplificadores Fet en CascadaDocumento10 pagineAmplificadores Fet en CascadaOmar Ruiz Rodríguez50% (2)

- Unidad 7, TermodinámicaDocumento17 pagineUnidad 7, TermodinámicaAbiel RosaNessuna valutazione finora

- Control de Fase DirectoDocumento30 pagineControl de Fase DirectoAbiel RosaNessuna valutazione finora

- FerrorresonanciaDocumento3 pagineFerrorresonanciajosemar63Nessuna valutazione finora

- EMA215, Unidad 2, EjerciciosDocumento18 pagineEMA215, Unidad 2, EjerciciosAbiel RosaNessuna valutazione finora

- Conv FuncionesDocumento4 pagineConv FuncionesLuis Carlos Ruiz CardenasNessuna valutazione finora

- 03 FourierDocumento102 pagine03 FouriergabbiyronnyNessuna valutazione finora

- Microprocesadores PDFDocumento128 pagineMicroprocesadores PDFbrayan40Nessuna valutazione finora

- Guia de Instalacion de Software Requerido para La AsignaturaDocumento14 pagineGuia de Instalacion de Software Requerido para La AsignaturaAbiel RosaNessuna valutazione finora

- Lab 01 - Pel 115Documento6 pagineLab 01 - Pel 115Abiel RosaNessuna valutazione finora

- Turbin AsDocumento4 pagineTurbin AsAbiel RosaNessuna valutazione finora

- 2-1 Inductores y CapacitoresDocumento36 pagine2-1 Inductores y CapacitoresAbiel RosaNessuna valutazione finora

- Diseño Digital Con LogicaDocumento58 pagineDiseño Digital Con LogicaJuan RamosNessuna valutazione finora

- Guía de Lab. II. Ecuaciones Diferenciales de Primer OrdenDocumento16 pagineGuía de Lab. II. Ecuaciones Diferenciales de Primer OrdenAbiel RosaNessuna valutazione finora

- Cmi115.2013 Discusion3Documento1 paginaCmi115.2013 Discusion3Abiel RosaNessuna valutazione finora

- Problemas Resueltos Cap 15 Fisica Edic 6 SerwayDocumento4 pagineProblemas Resueltos Cap 15 Fisica Edic 6 SerwayWill F. Piedrahita94% (16)

- Tarjeta de Referencia ANSI CDocumento2 pagineTarjeta de Referencia ANSI CJuan PabloNessuna valutazione finora

- Glosario MigracionesDocumento1 paginaGlosario MigracionesAbiel RosaNessuna valutazione finora

- Superposición de OndasDocumento9 pagineSuperposición de OndasAbiel RosaNessuna valutazione finora

- OclusivasDocumento8 pagineOclusivasAbiel RosaNessuna valutazione finora

- H-Matematica Ci2011Documento13 pagineH-Matematica Ci2011jonathan199319Nessuna valutazione finora

- Amplificadores A VálvulasDocumento6 pagineAmplificadores A VálvulasMiguelAndresFajardoHernandezNessuna valutazione finora

- Circuito Cortador y FijadorDocumento4 pagineCircuito Cortador y FijadorAriel VeizagaNessuna valutazione finora

- Control de Un Motor de Pasos BipolarDocumento14 pagineControl de Un Motor de Pasos BipolarJuan Jose Ontiveros MartinezNessuna valutazione finora

- APU Banco de PruebasDocumento2 pagineAPU Banco de PruebasJesús AlfredoNessuna valutazione finora

- Ejercicios de Leyes de Kirchhoff V 2.0Documento5 pagineEjercicios de Leyes de Kirchhoff V 2.0jose danielNessuna valutazione finora

- Sistema de Alimentación Ininterrumpida para Circuitos Con PICDocumento4 pagineSistema de Alimentación Ininterrumpida para Circuitos Con PICRoyer Quispe FloresNessuna valutazione finora

- Folleto Electronica de Potencia 201810Documento103 pagineFolleto Electronica de Potencia 201810Christian ZúñigaNessuna valutazione finora

- P5 14 EquipoDocumento43 pagineP5 14 EquipoDaniel ArzateNessuna valutazione finora

- Conceptos básicos de hardware, software, sistemas operativos y periféricosDocumento3 pagineConceptos básicos de hardware, software, sistemas operativos y periféricosanychat cartagenaNessuna valutazione finora

- Fundamentos de Electroìnica AnaloìgicaDocumento122 pagineFundamentos de Electroìnica Analoìgicacontacto.rhreclutamientoaNessuna valutazione finora

- Capítulo 1Documento30 pagineCapítulo 1Moisés Raymundo Rojas SantiagoNessuna valutazione finora

- Rectificador MonofásicoDocumento13 pagineRectificador MonofásicoJacquelineNessuna valutazione finora

- Circuito Cargador Solar 12VDocumento5 pagineCircuito Cargador Solar 12VProspero Araya FuentesNessuna valutazione finora

- Decodificador BCD A 7 SegmentosDocumento8 pagineDecodificador BCD A 7 Segmentoscarlos3107100% (1)

- Converted 2Documento3 pagineConverted 2Rasec Zelada TiradoNessuna valutazione finora

- Practica 9 - Modos Del 74194Documento8 paginePractica 9 - Modos Del 74194Adrian Antonio Sosa SolisNessuna valutazione finora

- Pepper 8m UmDocumento7 paginePepper 8m UmJose GarciaNessuna valutazione finora

- LAB 7-2020-II - CIRCUITOS DIGITALES II - Análisis y Diseño de Circuitos Secuenciales - Modelo Tipo Moore y Modelo Tipo MealyDocumento2 pagineLAB 7-2020-II - CIRCUITOS DIGITALES II - Análisis y Diseño de Circuitos Secuenciales - Modelo Tipo Moore y Modelo Tipo MealyLuis Misiyauri GutiérrezNessuna valutazione finora

- Universidad Privada Antenor Orrego PDFDocumento263 pagineUniversidad Privada Antenor Orrego PDFGonzales NavarroNessuna valutazione finora

- Qué Es La ImpedanciaDocumento4 pagineQué Es La ImpedanciaSONYU19Nessuna valutazione finora

- Lab 03 EtropoDocumento9 pagineLab 03 EtropoDiego A CruzNessuna valutazione finora

- BalumDocumento4 pagineBalumChristian PizanánNessuna valutazione finora

- Mapa Conceptual de La Arquitectura Laura Guevara PDFDocumento1 paginaMapa Conceptual de La Arquitectura Laura Guevara PDFNiyirethCangrejoSeguraNessuna valutazione finora

- TIRISTORESDocumento11 pagineTIRISTORESJavier SuarezNessuna valutazione finora

- Cuestionario PrevioDocumento5 pagineCuestionario PrevioCanalDTodoUnPoco PCNessuna valutazione finora

- SockerDocumento10 pagineSockerMosquera Ibarguen RichardNessuna valutazione finora

- Resolucion Directoral MTC para HomologacionDocumento28 pagineResolucion Directoral MTC para HomologacionMax Fredi Quispe AguilarNessuna valutazione finora