Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Chapter 4 - Analog Integrated Circuit Design by John Choma

Caricato da

Ariana Ribeiro LameirinhasDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Chapter 4 - Analog Integrated Circuit Design by John Choma

Caricato da

Ariana Ribeiro LameirinhasCopyright:

Formati disponibili

LECTURE SUPPLEMENT #4 . . .

[LS #4]

CHAPTER #04

Circuit Level Models And Basic

Applications Of MOS Technology

Transistors

Dr. John Choma

Professor of Electrical Engineering

University of Southern California

Ming Hsieh Department of Electrical Engineering

University Park: Mail Code: 0271

Los Angeles, California 900890271

2137404692 [USC Office]

2137407581 [USC Fax]

8183841552 [Cell]

johnc@usc.edu

PRELUDE:

In this chapter, you are introduced to MOS technology transistors and in particular, to the circuit

level models that emulate the electrical behavior of the metal-oxide-silicon field effect transistor,

or MOSFET. We present these models in a hierarchical format that proceeds from relatively sim-

ple mathematical forms to progressively more advanced embodiments that reflect trends in state

of the art circuit and system industries. These advanced structures enable an understanding of

how higher order transistor phenomena, inclusive of those that prevail in modern, deep submi-

cron technologies, affect the observable responses of high performance analog networks. Subse-

quent to demonstrating the utility of the simple models in several practical circuit applications,

we shall learn how computer-aided design and the more advanced MOSFET models coalesce to

optimize our first order designs and render them reproducible in the face of a myriad of

processing and manufacturing uncertainties. The chapter concludes with the development of

small signal MOSFET models, which are foundational to the analysis and design of linear, ana-

log MOS technology circuits.

July 2013

Chapter 4 MOSFET Models and Applications

- 313 -

4.1.0. INTRODUCTION

Integrated electronic circuits realized in metal-oxide-silicon field effect transistor

(MOSFET) technologies are used widely in the technical community. Transistors manufactured

in bipolar technologies, which we studied in the preceding chapter, compete successfully with

their MOSFET counterparts from such performance perspectives as fast switching speed, broad-

band frequency response, and low noise signal processing. Nevertheless, the MOSFET domi-

nates much of the electronic network landscape for at least three reasons. The first of these rea-

sons derives from the fact that the cross section geometry of a MOSFET, when compared to that

of a bipolar junction transistor, and particularly a SiGe BJT, is considerably simpler. This

simplicity affords relative foundry processing ease, which promotes high device yield and there-

fore cost-effective manufacturing. We might interject here that yield is a commonly invoked

integrated circuit processing metric that asserts the percentage of manufactured chip devices that

meet or exceed minimal operating requirements. A second reason underlying MOS technology

popularity is that the surface area consumed on chip, or the footprint, of a MOSFET is invariably

smaller than that of a comparably performing bipolar transistor. This feature allows increased

packing density (number of transistors per unit chip surface area), which is particularly advanta-

geous for digital signal processors that can exploit upwards of millions of transistors for proper

functionality. Finally, MOSFETs deliver good circuit performance at low standby power and

voltages, which is a welcomed attribute in light of the aforementioned high device density of

digital architectures and the portability culture in which we are immersed.

Although bipolar transistors are capable of delivering outstanding (and some would ar-

gue even superior) analog circuit performance, especially at high signal frequencies, adopting

MOSFET technology as a viable alternative for analog signal processing applications makes

sense for several reasons. One reason is that the nature of modern integrated systems is rarely

exclusively digital or exclusively analog. State of the art systems are mixed signal architectures

that combine digital and analog signal processing on the same chip. Because of the simplicity,

packing density, and power dissipation attributes of MOSFETs, the majority of digital architec-

tures, excluding perhaps those in specialized, high performance military systems, is realized in

MOS technology. Engineering prudence therefore encourages a MOSFET technology realiza-

tion of the analog cells implicit to a mixed signal framework if only to facilitate the electrical

interface between the digital and analog circuit cells.

Aside from the operating flexibility and programmability attributes of digital circuit

schema, digital circuits in microcontrollers that are embedded in mixed signal topologies are of-

ten required to ensure and sustain optimal performance in the analog signal flow paths of modern

electronic systems. Unlike most digital networks, high performance analog circuits are sensi-

tized to specific values, or at least specific ranges of values, of several of the key physical and

electrical parameters that define the static and dynamic volt-ampere characteristics of MOSFETs.

Unfortunately, attaining the requisite accuracy in the observed values of these implicit parame-

ters is progressively more challenging as we scale, or downsize, device geometries to meet the

omnipresent demands for the wider system bandwidths that are required to process ever-increas-

ing amounts of information and data. In these high performance systems, suitable compensation

of the analog signal flow paths often derive from digital subcircuits deployed to sense observable

performance metrics and compare these metrics to their respective targeted design goals. What

gets measured is a viable candidate for possible corrective action. To this end, the digital control

units are called upon to reduce the differences between sensed and targeted performance metrics

by adjusting relevant circuit branch parameters and/or the biasing conditions of transistors that

Chapter 4 MOSFET Models and Applications

- 314 -

are implicit to the signal path. In effect, the combined digital controllers and analog network be-

have as a seamless adaptive system that automatically corrects for manufacturing uncertainties,

nonzero component tolerances, increased device operating temperatures, and an array of other

environmental phenomena.

4.2.0. MOSFET DEVICE CROSS SECTION

We have seen that two types of bipolar junction transistors are available. Similarly,

MOSFETs come in two flavors: the n-channel MOSFET, or NMOS transistor, whose simplified

cross section is diagrammed in Figure (4.1), and the p-channel MOSFET, or PMOS device, we

depict in Figure (4.2). In the NMOS device, the bulk substrate is p-type, lightly doped to an

average acceptor impurity concentration of N

A

. A representative range of substrate impurity

concentration values is 5(10

14

) atoms/cm

3

< N

A

< 10

16

atoms/cm

3

. The vertical depth of the bulk

substrate, which is not symbolically highlighted in Figure (4.1), is many times larger than the

depth, Y

d

, of the source and drain diffusions or implants. The latter depth is typically of the order

of a few tenths of microns. The source and drain regions, whose widths are indicated as L

diff

and

which are connected electrically to the externally accessible source (S) and drain (D) terminals of

the MOSFET, are very strongly doped. Their donor impurity concentrations border on solid

solubility limits in that N

D

= 10

20

atoms/cm

3

or slightly larger. The width, L

diff

, is typically two-

or three-times the channel length, which we indicate as L in the diagram. In effect, the high

impurity concentration in the source region forges a robust electrical contact between the source

terminal and the source end of the bulk geometry lying directly under the indicated silicon dio-

xide layer. The same statement applies to the drain terminal and its electrical interface with the

drain end of the bulk region. The metallization contact that forms the electrical terminal of the

semiconductor bulk (B) is normally connected to the most negative potential available in the cir-

cuit into which the subject transistor is embedded. Such a connection reverse biases the PN

junctions formed between the bulk and source regions and between the bulk and drain regions.

This reverse biasing ensures that for at least low signal frequencies, the source and drain volumes

are electrically isolated from each other and from the bulk substrate. This reverse biasing serves

also to isolate electrically proximately located other chip transistors.

Lying atop the p-type bulk substrate is an insulating silicon dioxide layer of thickness

T

ox

that extends into the page by an amount equal to the gate width, W. The oxide thickness is of

the order of the low tens of angstroms, where we remind that one angstrom is 10

8

centimeter.

The oxide layer covers the channel region of length L, which separates the source region from

the drain region. Unfortunately, this oxide layer may overlap the source and drain regions by the

amount, L

d

, as we indicate in the diagram. The overlap of the source and drain regions is bad

news in that it can limit the frequency response capabilities in certain types of MOSFET amplifi-

ers. In processes boasting gate self-alignment, L

d

is ideally reduced to zero. But for state of the

art monolithic circuit processes delivering channel lengths as small as 28 nM to 130 nM, gate

self-alignment focused on reducing L

d

to no more than 5% of L is a challenge.

The gate width, W, can be no smaller than the minimum channel length that can be pro-

duced by the foundry process. Subject to this constraint, the gate aspect ratio, W/L, is a designa-

ble parameter. A designable parameter is one that we can select in accordance with our

interpretation of the operating requirements of the circuit application in which we deploy the

considered MOSFET. Depending on circuit application and associated design strategies and tar-

gets, the gate aspect ratio can be as large as several tens or even several hundreds.

Chapter 4 MOSFET Models and Applications

- 315 -

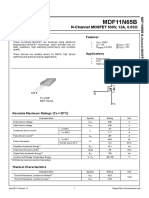

Figure (4.1). A simplified three-dimensional depiction of an n-channel MOSFET (NMOS) and its

corresponding electrical schematic symbol. The diagram is not drawn to scale.

Figure (4.2). A simplified three-dimensional depiction of a p-channel MOSFET (PMOS) and its correspond-

ing electrical schematic symbol. The diagram is not drawn to scale.

N

+

S

o

u

r

c

e

N

+

D

r

a

i

n

P Type

Substrate

[Concentration = N cm ]

A

-3

S G D

B

Silicon Dioxide

T

ox

Y

d

L

diff

L

d

L

d

W

L

G

a

t

e

S

o

u

r

c

e

D

r

a

i

n

Bulk or

Substrate

Metal or

Polysilicon

L

diff

S

G B

I

d

I

b

I

s

I

g

V

ds

V

bs

V

gs

S

V

gd

D D

P

+

S

o

u

r

c

e

P

+

D

r

a

i

n

N Type

Substrate

[Concentration = N cm ]

D

-3

S G D

B

Silicon Dioxide

T

ox

Y

d

L

d

L

d

W

L

G

a

t

e

S

o

u

r

c

e

D

r

a

i

n

Bulk or

Substrate

Metal or

Polysilicon

D

G

S

B

I

s

I

b

I

d

I

g

+

V

sd

+

V

sb

V

dg

S

V

sg

D

L

diff

L

diff

Chapter 4 MOSFET Models and Applications

- 316 -

The gate terminal (G) is formed of an electrical contact made of a metallic or a

polycrystalline silicon layer deposited directly on the gate oxide. A popular gate metal is alumi-

num. If the MOSFET under consideration is used in high temperature environments and/or in

applications that exploit low power supply voltages, polycrystalline silicon, which is commonly

referred to as polysilicon or simply poly, supplants the aluminum gate. We observe that the

insulating gate oxide layer comprises a dielectric interface between the gate metal and the

semiconductor bulk. Since the gate metal is obviously conductive and the bulk region is at least

semi-conductive, an effective parallel plate capacitance is forged between the gate contact (G)

and the bulk terminal (B). The capacitance value of this MOS capacitance, or MOSCAP, can be

controlled by static voltages applied between gate and bulk terminals. The capacitance attributed

to the source and drain overlap regions is less sensitive to changes in voltages applied from gate

to source or from gate to drain.

In addition to the simplified cross section diagram of the n-channel MOSFET, Figure

(4.1) inserts the electrical schematic symbol of an NMOS transistor. Of particular interest are

the positive reference conventions adopted for four device currents and four device voltages.

Specifically, positive drain current, I

d

, flows into the transistor, as do the gate current, I

g

, and the

bulk, or substrate, current, I

b

. On the other hand, positive source current, I

s

, flows out of the

transistor. The entire transistor structure can be accorded the stature of a giant, happy circuit

node, whence by Kirchhoffs current law,

s d g b

I I I I . = + + (4-1)

However, since the gate contact is isolated from the semiconductor bulk by an insulating oxide

layer, I

g

is zero in the steady state and at the low frequencies for which the capacitance asso-

ciated with the insulating gate dielectric behaves as an open circuit. Moreover, the bulk current,

I

b

, is likewise almost zero at low signal frequencies, provided, as is usually the case, that the bulk

terminal is connected to the most negative of available circuit potentials. This bulk biasing

serves to reverse bias the PN junctions formed between bulk and drain and between bulk and

source, thereby remanding I

b

to a superposition of invariably small PN junction leakage currents.

Accordingly, the source and drain currents, I

s

and I

d

, respectively, are almost identical when only

relatively low frequency signals are applied to a MOSFET. This observation contrasts with our

bipolar disclosures in the preceding chapter in that the bipolar device emitter current is slightly

larger than the corresponding collector current by an amount that equals the relatively small base

current. We shall demonstrate in the following pages that the static and low frequency values of

the drain, and hence the source, current are controlled dominantly by the gate to source voltage,

V

gs

, modestly by the drain to source voltage, V

ds

, and, to a far lesser extent, by the bulk to source

voltage, V

bs

. Stipulating an additional dependence of drain current on gate to drain voltage V

gd

is

superfluous, for by Kirchhoffs voltage law,

ds gs gd

V V V . = (4-2)

The p-channel MOSFET abstracted in Figure (4.2) is architecturally similar to its

NMOS counterpart. The notable differences are that the bulk substrate in PMOS is n-type and

the source and drain regions are heavily doped with p-type impurities. It follows that electrical

isolation between the source region and the bulk, as well as between the drain region and the

bulk, requires that the bulk substrate terminal of a PMOS device be connected to the most posi-

tive of available circuit potentials. All of the geometrical parameters and their representative

values remain the same as stipulated for NMOS units. The PMOS electrical schematic symbol,

which is also shown in Figure (4.2), differs from the NMOS symbol in that the directions of the

source terminal and bulk terminal arrows are reversed, as are the positive reference directions of

Chapter 4 MOSFET Models and Applications

- 317 -

all four transistor currents. While (4-1) remains applicable, the analytical expression for the

drain current, I

d

, which now flows out of the transistor, is more conveniently couched in terms of

the source to gate voltage, V

sg

, the source to drain voltage, V

sd

, and the source to bulk voltage,

V

sb

. The drain -to- gate voltage, V

dg

, derives from

sd sg dg

V V V , = (4-3)

which mirrors (4-2) if we simply multiply both sides of the last equation by negative one.

4.3.0. STATIC MOSFET MODELS

The static volt-ampere characteristics of an n-channel MOSFET relate the drain current,

I

d

, flowing into the transistor to its applied gate-source voltage, V

gs

, drain-source voltage V

ds

, and

bulk-source voltage V

bs

. The characteristics for a p-channel device are analogously defined. But

in a p-channel transistor, the drain current, I

d

, flows out of the device and is expressed as a func-

tion of the source-gate voltage, V

sg

, source-drain voltage V

sd

, and source-bulk voltage V

sb

. In

contrast to the Ebers-Moll and Gummel-Poon bipolar junction transistor models, which define

the transistor volt-ampere characteristics for all possible operating voltage scenarios, the static

volt-ampere curves of MOSFETs are more expediently determined by partitioning the

characteristics into four distinct operating regimes. These regimes are the cutoff region, the

subthreshold region, the ohmic (also known as the triode) regime, and the saturation regime. Al-

though we shall opt for the mathematical and design-oriented convenience of an approximate

four region MOSFET model, we point out that other MOSFET device models, such as the EKV

model, promote a unified approach to physically-based MOSFET modeling that is valid for all

operating regions

[1],[2]

. The EKV model is incorporated in several currently available versions of

the SPICE computer-aided design software. However, we deem the definitive physical model-

ing, which is excellently reflected by the EKV model, to be outside the scope of this circuits-

oriented textbook.

4.3.1. TRANSISTOR IN CUTOFF REGIME

A MOSFET operates in cutoff when its drain current is zero. In an n-channel device,

the condition corresponding to null drain current is a small gate-source voltage, V

gs

, which satis-

fies the inequality,

gs hf

V V , s (4-4)

where V

hf

, adjusted for applied bulk-source voltage V

bs

, is

bs

hf F F

F

V

V V 2V V 1 .

V

u

= + (4-5)

In this relationship, the Fermi potential, V

F

, is given by

sub A

F T T

i i

N N

V V V ,

n n

ln ln

| | | |

= =

| |

\ . \ .

(4-6)

where the bulk substrate concentration, N

sub

, is an acceptor impurity concentration (N

A

) in the

NMOS device. Moreover,

T

V kT q = (4-7)

is the familiar Boltzmann voltage for which k = (1.38)(10

23

) joules/K is Boltzmanns constant,

q = (1.60)(10

19

) coulombs is the magnitude of electron charge, and T represents the absolute

Chapter 4 MOSFET Models and Applications

- 318 -

temperature of the surface of the bulk substrate. Parameter n

i

symbolizes the intrinsic

semiconductor concentration of silicon (roughly 10

10

atoms/cm

3

at T = 27 C = 300.16 K). For

most NMOS transistors, V

F

is in the neighborhood of 300 mV at surface temperatures of 27 C.

Also in (4-5), V

, termed the body effect voltage, is

1

2

A s ox

A s

2

ox

ox

qN T

V qN .

C

| |

= =

|

\ .

(4-8)

In this equation,

s

is the dielectric constant of silicon, which is 1.05 pF/cm, and C

ox

is the density

(in units of farads/cm

2

) of the capacitance associated with the gate oxide layer. In particular,

ox

ox

ox

C ,

T

= (4-9)

where

ox

is the dielectric constant of silicon dioxide (345 fF/cm). Recall T

ox

to be the thickness

of the gate oxide layer. We should note that the multiplication of capacitance density C

ox

by the

product of the channel length, L, and gate width W yields the net oxide capacitance observed at

the transistor gate under equilibrium conditions. The body effect voltage, V

, is typically of the

order of only the high hundredths to low tenths of volts. Indeed, we see that for thin gate oxides,

V

in (4-8) converges toward zero.

Two issues surrounding (4-4) and (4-5) are sufficiently compelling to warrant at least

qualitative engineering attention. The first of these issues is that voltage V

hf

is a particular gate-

source voltage that corresponds to one Fermi level, V

F

, established at the interface of the gate

oxide and bulk semiconductor. In other words, (4-4) asserts that MOSFET cutoff is achieved

when the applied gate-source voltage is sufficient to establish a potential of only one Fermi level

at the semiconductor interface immediately under the gate oxide layer. The first term on the

right hand side of (4-5) obviously speaks to this Fermi interfacial potential. The second term on

the right hand side of the subject relationship corrects for applied bulk-source voltage, V

bs

. In

particular, note that negative V

bs

, which is typical of most NMOS topologies, increases V

hf

. This

situation reflects engineering expectations in that V

bs

< 0 pulls the surface potential lower than

the value evidenced for V

bs

= 0. As a result, the gate-source voltage must be increased to offset

the aforementioned pull down of surface potential. In a word, V

gs

must be progressively in-

creased to bring a transistor influenced by negative bulk-source voltage out of cutoff.

The second of the aforementioned two issues is directed toward assuring our

comprehension of the engineering significance of the Fermi potential. To this end, we submit

the simplified MOSFET cross section of Figure (4.3), which depicts an NMOS device to which

is applied a positive gate-source voltage, V

gs

, zero drain-source voltage, V

ds

, and a bulk-source

voltage, V

bs

, which is polarized to ensure either reverse or zero biasing of both the bulk-source

and the bulk-drain PN junctions. When we apply a gate-source voltage, V

gs

, we expect a signifi-

cant percentage of V

gs

to be dropped across the insulating silicon dioxide layer. In Figure (4.3),

we denote this oxide potential drop as voltage V

ox

. The corresponding voltage excess, (V

gs

V

ox

), appears as the interfacial potential, which we highlight as voltage V

y

in Figure (4.3). Ob-

serve that voltage V

y

is dropped from the interface of the oxide-semiconductor bulk to the source

so that in concert with Kirchhoffs voltage law,

gs ox y

V V V . = + (4-10)

In the absence of any significant drain-source bias, the interfacial potential is given by

1

In HSPICE and numerous other forms of SPICE circuit simulators, the body effect parameter is , where

2

= 2V

u

.

Chapter 4 MOSFET Models and Applications

- 319 -

Figure (4.3). Simplified NMOS cross section used to illustrate the engineering significance of the

Fermi potential. The diagram is not drawn to scale.

y T

o

n

V V ,

n

ln

| |

=

|

\ .

(4-11)

where parameters n and n

o

respectively denote the actual and equilibrium values of the free elec-

tron concentration at the interface point where voltage V

y

is monitored. Assuming nearly com-

plete ionization of substrate impurity atoms, the free hole concentration in an NMOS substrate

very closely equals N

A

. Additionally, the product of free hole and electron concentrations is the

square of the intrinsic carrier concentration. Thus, we can express (4-11) in as the more

enlightening alternative,

A

y T T

2

o

i

n nN

V V V .

n

n

ln ln

| |

| |

| = =

|

|

\ .

\ .

(4-12)

Equation (4-12) harbors interest because it demonstrates that an increase in voltage V

y

,

which derives from an increase in applied gate-source voltage, as per (4-10), necessarily incurs

an increase in the interfacial density, n, of free electrons. Equation (4-12) supports this conten-

tion because we know that for a given operating temperature, the intrinsic carrier concentration,

n

i

, is a constant, and the average impurity concentration, N

A

, in the semiconductor bulk is like-

wise fixed. Evidently, the immediate effect of applying positive gate-source voltage V

gs

is to at-

tract free electrons, which are the minority carriers in the p-type semiconductor bulk of NMOS,

to the oxide-bulk interface. As V

y

continues to rise, n eventually climbs to the intrinsic carrier

level, n

i

. Interfacial potential V

y

in (4-12) equates to Fermi potential V

F

in (4-11) when the elec-

tron concentration, n, at the surface equals the intrinsic carrier concentration n

i

. In other words,

when the interface potential equals one Fermi level, the semiconductor complexion of the

interfacial region changes from an obvious p-type semiconductor to an intrinsic, neutral

semiconductor; that is, it is neither p-type nor n-type. We can therefore say that when V

y

= V

F

,

the interfacial region is on the cusp of inverting from p-type to n-type semiconductor.

N

+

S

o

u

r

c

e

N

+

D

r

a

i

n

P-Type Substrate (conc. = N cm )

A

-3

S G D

B

Silicon Dioxide

V

gs

V = 0

ds

Depletion

Layer, V = 0

ds

I

d

Channel Of

Free Electrons

V 0

bs

s

V

ox

V

y

+

+

Chapter 4 MOSFET Models and Applications

- 320 -

While we associate zero drain current corresponding to the condition posed by (4-4), in

truth, a very small amount of drain current flows when positive drain-source voltage is applied.

This drain current materializes because as V

y

nears the Fermi potential, a small concentration of

electrons, nominally equivalent to the intrinsic carrier concentration, is established at the inter-

face. Because this electron concentration is very small (about 10

10

electrons/cm

3

), the resultant

drain current is typically of the order of at most femtoamperes.

The cutoff criterion for a PMOS device mirrors that of an NMOS transistor. Specifi-

cally, (4-4) and (4-10) become, with the understanding that V

hf

remains a positive voltage,

sg hf

sg ox y

V V

.

V V V

<

= +

(4-13)

It is important to interject that the annotated polarities of voltages V

ox

and V

y

are reversed from

those that are indicated in Figure (4.3). The Fermi potential, which, like V

hf

, remains a positive

number, is now

sub D

F T T

i i

N N

V V V ,

n n

ln ln

| | | |

= =

| |

\ . \ .

(4-14)

where for PMOS, N

sub

= N

D

, the donor impurity concentration of the n-type bulk. In view of (4-

14), the interface potential, V

y

, in (4-12) becomes for PMOS,

D

y T T

2

o

i

p pN

V V V ,

p

n

ln ln

| |

| |

| = =

|

|

\ .

\ .

(4-15)

where we understand that p is the free hole concentration at the interface, and p

o

is the equili-

brium value of this free charge concentration.

4.3.2. TRANSISTOR IN THE SUBTHRESHOLD REGIME

If the gate-source voltage, V

gs

, in an NMOS transistor continues to rise, thereby enabl-

ing the interfacial potential to rise above the Fermi level, V

F

, the free electron concentration at

the oxide-bulk interface surpasses its intrinsic level. This means that the interfacial region we

addressed in the preceding subsection inverts from its original p-type nature to an n-type charac-

ter. In other words, for V

gs

> V

hf

, the concentration of interfacial free electrons exceeds, albeit by

a comparatively small factor, the interfacial concentration of free holes. For

hf gs h

V V V , < < (4-16)

where V

h

is formally introduced here as the threshold, or turn on, voltage of the transistor, we say

that the channel region between the source and drain implants in the cross section diagram of

Figure (4.3) is weakly inverted. It is weakly inverted in that the channel between source and

drain volumes and immediately beneath the gate oxide has an electron concentration that is

larger than intrinsic level, but is nevertheless substantively smaller than the hole concentration,

N

A

, which originally prevailed in this region. This weak inversion condition, which is guaran-

teed by the satisfaction of (4-16), constrains the considered transistor to operate in its subthre-

shold regime.

The engineering significance of the threshold voltage, V

h

, we have introduced in (4-16)

is best appreciated in the context of a MOSFET operating in either its ohmic or saturation do-

mains. For the present, however, it can be stated that this threshold voltage is the minimum gate-

source voltage commensurate with the onset of the conduction of significant drain current when

positive drain-source voltage, V

ds

, is applied to the transistor.

Chapter 4 MOSFET Models and Applications

- 321 -

Two important points surround the threshold voltage of a MOSFET. The first of these

points is that V

h

is the specific value of gate-source voltage that establishes an interfacial poten-

tial, V

y

, which is equivalent to twice Fermi level. From (4-12) and (4-11), we see that V

y

= 2V

F

if

the concentration, n, of free electrons at the interface equals N

A

, the impurity concentration in the

bulk. In other words, threshold conditions are manifested when the oxide-bulk interface be-

comes strongly inverted. By strongly inverted, we mean that the interfacial concentration of

free electrons rises to the original interfacial free hole concentration (assuming complete impur-

ity ionization in the bulk substrate) evidenced at equilibrium.

The second of the aforementioned two threshold disclosures is that the turn on voltage

is influenced by nonzero bulk-source voltage, V

bs

, in accordance with a phenomenon known as

body effect, bulk effect, or bulk-induced threshold modulation (BITM). In particular, negative

V

bs

results in an increase in the threshold voltage, which is to say that when V

bs

pulls the bulk be-

low ground, an enhanced gate-source voltage is required to counteract this bulk voltage effect if

transistor turn on is to be sustained. The body effect expression commonly used to quantify the

relationship of threshold voltage V

h

to bulk-source voltage V

bs

is

[3]

bs

h ho F

F

V

V V 2 V V 1 1 .

2V

| |

= +

|

|

\ .

(4-17)

In this expression, V

ho

is the value of threshold voltage V

h

for the special case of zero bulk-source

voltage; that is, V

h

= V

ho

for the zero bias case inferred by V

bs

= 0. Voltage V

ho

is given by

( )

ho F F

V 2 V 2 V V .

u

= + (4-18)

Accordingly,

bs

h F F

F

V

V 2V 2 V V 1 .

2V

u

| |

| = +

|

\ .

(4-19)

We should interject that for NMOS, voltages V

F

and V

remain given by (4-6) and (4-8), respec-

tively. Because voltage V

is small, (4-19) demonstrates that for zero bulk-source bias, the thre-

shold voltage approximates twice the Fermi potential for V

bs

<< 2V

F

.

In Figure (4.4), we graphically display the nature of BITM for three different values of

gate oxide thickness. The subject plot invokes N

A

= 10

15

atoms/cm

3

and room temperature

conditions for which the intrinsic carrier concentration, n

i

, is about 10

10

atoms/cm

3

. Note that the

body effect induces a progressively smaller perturbation in the threshold voltage as the oxide

thickness diminishes. In general, however the threshold shift can be significant. For example, if

the gate oxide thickness is 100 , (V

h

V

ho

) = 52.5 mV for V

bs

= 2.5 V. Given that the zero

bias (V

bs

= 0) threshold voltage, V

ho,

is of the order of 500 mV for a device extolling a minimum

channel length of the order of 500 nM, this computed threshold shift is more than 10% of the

value of the zero bias threshold voltage.

In the subthreshold regime and for low frequency -including static- signal conditions,

the NMOS drain current, I

d

, is given approximately by

[2],[4]

,

( )

ds df

V V gs bs

d ot

T

V V

W

I I 1 ,

L V

exp e

+ | |

| |

~

|

|

\ .

\ .

(4-18)

where W/L is recalled as the designable gate aspect ratio of the transistor. We observe that for

given values of the gate-source voltage, V

gs

, the drain-source voltage, V

ds

, and the bulk-source

voltage, V

bs

, drain current I

d

scales linearly with W/L. Circuit designers are free to alter the gate

Chapter 4 MOSFET Models and Applications

- 322 -

geometries of the transistors they utilize in a circuit design undertaking, as long as gate width W

satisfies the constraint, W L L

min

, where L

min

, is the minimal channel length permitted by the

process foundry. In (4-18), saturation current I

ot

, dimensionless parameters and , and voltage

V

df

are empirically deduced from volt-ampere characteristics measured in the laboratory or from

computer simulations of characteristic curves extracted under subthreshold biasing conditions.

For most NMOS and PMOS devices featuring channel lengths L that are no longer than 180 nM,

Figure (4.4). The body effect of bulk-source voltage, V

bs

, on threshold voltage, V

h

, for various gate

oxide thicknesses (T

ox

) in an NMOS transistor. For the purpose of this demonstra-

tion, the bulk impurity concentration, N

A

, is taken to be 10

15

atoms/cm

3

. The interfa-

cial temperature of the transistor is presumed to be 27 C, for which the intrinsic car-

rier concentration, n

i

, is about 10

10

atoms/cm

3

.

18

ot

df

I 10 amperes

0.90 1

.

0.05 0.25

4 volts V 10 volts

q

s

s <

s <

s s

(4-19)

We note an extremely small saturation current, I

ot

. We should appreciate the fact that this minis-

cule saturation current interacts with a gate-source voltage that is necessarily bracketed above by

threshold potential V

h

and drain-source and bulk-source voltages applied in subthreshold regimes

that are generally as small as a volt or so. The immediate upshot of these small voltage scenes is

a very small subthreshold drain current. Typically, these drain currents rarely exceed a few

nanoamperes, and they can be as low as a few femtoamperes. Moreover, the relatively large vol-

tage, V

df

, tends to minimize drain current sensitivity to drain-source voltage. This is to say that

in subthreshold, the drain current is controlled almost exclusively by gate-source voltage V

gs

,

and, to a lesser extent, by bulk-source voltage, V

bs

.

The exponential dependence of transistor drain current on applied gate-source voltage

is reminiscent of the exponential dependence of BJT collector current on applied base-emitter

voltage. Indeed, we note that

0

20

40

60

80

100

120

140

160

180

0.0 -1.0 -2.0 -3.0 -4.0 -5.0

T

h

r

e

s

h

o

l

d

V

o

l

t

a

g

e

C

h

a

n

g

e

,

(

V

h

V

h

o

)

(

m

V

)

Bulk-Source Voltage, V

bs

(volts)

Chapter 4 MOSFET Models and Applications

- 323 -

( )

ds df

V V

gs

d bs

ot T T

V

I V

1 ,

W L I V V

ln ln e q

| | ( | |

| |

| | ( ~ + +

|

|

| |

(

\ .

\ . \ .

(4-20)

which shows that the subthreshold drain current is semi-logarithmically linear with gate-source

(and also bulk-source) voltages. Because the drain-source voltage, V

ds

, applied to subthreshold

domain MOSFETs is typically small in comparison to the voltage parameter, V

df

, drain-source

voltages generally exert little impact on the semi-logarithmic plot of drain current versus gate-

source voltage.

In this text, very few circuits exploit MOSFETs that are constrained to operate in

subthreshold regimes. One reason for this pedagogical tack is that sub-nanoampere, subthre-

shold drain currents are sufficiently small to risk their being masked by uncorrelated noise cur-

rents that are unavoidably generated in the bulk immediately below the oxide interface. Another

reason derives from the caution flag that must be planted around the fact that for the low signal

frequencies to which the volt-ampere characteristic of (4-18) abides, no less than four empiri-

cally deduced parameters are invoked. Aside from an inherent inability to adjudicate the manner

in which these empiricisms are affected by scaled device geometries, these non-physical parame-

ters render accurate prediction and reproducibility of subthreshold circuit responses improbable

in the absence of design heroics. At a minimum, such heroics include novel feedback measures

and at a maximum, they require embedded microcontrollers that literally adjust node voltages or

branch currents in response to comparing monitored subthreshold circuit performance to design

targets. Yet another reason for deemphasizing subthreshold regime operation is the anemic gains

and constricted bandwidths afforded by the small currents indigenous to transistors that operate

in subthreshold.

One notable advantage of the small drain currents evidenced in subthreshold operating

domains is the virtually negligible heat these currents generate because of classic I

2

R losses.

These virtually negligible losses explain the escalating popularity of subthreshold MOSFETs in

numerous biomedical and neurological applications. Included among these applications are

cochlear implants for the deaf, implantable neurological and biomedical sensing, monitoring, and

cell excitation electronics, and subcutaneous, fully automated, electronic drug delivery systems.

In these and related neurosciences and biomedical applications, internal temperature rises as

small as 1 C to 2 C in the brain and in other human organs are potentially catastrophic.

EXAMPLE #4.1:

The HSPICE Level 3 parameters for an NMOS transistor featuring a minimum permissi-

ble 0.5 m channel length are delineated in Table (4.1). Table (4.2), which is used later

in the text and in the exercises accompanying this chapter, gives HSPICE parameters for

a PMOS transistor that is nominally complementary to the subject NMOS device. Some

of the parameters delineated in the table are curve fit entities for which we need not be

concerned. The engineering significance of other parameters in this table, such as those

that deal with device capacitances, is addressed later in this chapter. Using L = 1 m

and W = 10 m and with the source and bulk terminals both grounded, use SPICE soft-

ware to simulate the room temperature characteristic curves, I

d

-versus- V

gs

for drain-

source voltages, V

ds

, of 0.5 V, 1.5 V, and 2.5 V. Using these simulated results, determine

the nominal range of gate-source voltages for which the transistor is constrained to oper-

ate in its subthreshold regime.

Chapter 4 MOSFET Models and Applications

- 324 -

SPICE

SYMBOL

TEXT

SYMBOL

DESCRIPTION

OF PARAMETER

VALUE UNITS

VTO V

ho

Zero Bias Threshold Voltage 550 mV

TOX T

ox

Gate Oxide Thickness 9.5 nM

GAMMA (2V

u

)

0.5

Body Effect Coefficient 0.32 volt

1/2

PHI |2V

F

| Magnitude Of Twice Fermi Potential 700 mV

XJ Y

d

Source & Drain Junction Depth 0.20 M

KP

o

C

ox

Transconductance Parameter 156 mho/volt

NSUB N

A

Average Substrate Doping Concentration 1.4(10

17

) atoms/cm

3

NFS Surface State Subthreshold Parameter 7.2(10

11

)

DELTA Threshold Versus Gate Width Parameter 0.88

LD L

d

Source-Drain Lateral Overlap 50 nM

TPG Gate Material Polarity (Ignored If VTO Is Specified) 1

UO

n

Low Field Carrier Mobility 420 cm

2

/volt-sec

THETA 1/V

ve

Vertical Field Mobility Degradation Parameter 0.23 volt

1

RSH R

sh

Source & Drain Sheet Resistance 2.0 O/Square

VMAX v

sat

Maximum Carrier Drift Velocity (1.8)(10

5

) meter/sec

KAPPA Channel Length Modulation Factor 0.011 volt

1

ETA 1/V

Threshold Parameter For Drain induced barrier lowering 0.02125

CGDO C

gdo

Gate-Drain Overlap Capacitance Density 310 pF/meter

CGSO C

gso

Gate-Source Overlap Capacitance Density 320 pF/meter

CGBO C

gbo

Gate-Bulk Overlap Capacitance Density 550 pF/meter

CJSW C

jsw

Zero Bias Sidewall Capacitance Density 320 pF/meter

CJ C

jo

Zero Bias Bulk Junction Capacitance Density 560 F/meter

2

MJ m

j

Bulk Junction Grading Coefficient 0.34

MJSW m

jsw

Sidewall Junction Grading Coefficient 0.35

PB V

j

Bulk-Drain/Bulk-Source Junction Built-In Potential 1.1 volt

LEVEL Model Type 3

Table (4.1). HSPICE LEVEL 3 model parameters for a representative 500 nM NMOS transistor. In addition to

specifying these parameters, the gate width, W, the channel length, L, and high frequency geometric

parameters P

s

, P

d

, A

s

, and A

d

, must be delineated on the model line of the SPICE circuit file. In the

absence of definitive process information, the latter four parameters are estimated in accordance with

guidelines provided later in the chapter.

SPICE

SYMBOL

TEXT

SYMBOL

DESCRIPTION

OF PARAMETER

VALUE UNITS

VTO V

ho

Zero Bias Threshold Voltage 480 mV

TOX T

ox

Gate Oxide Thickness 9.5 nM

GAMMA (2V

u

)

0.5

Body Effect Coefficient 0.28 volt

1/2

PHI |2V

F

| Magnitude Of Twice Fermi Potential 700 mV

XJ Y

d

Source & Drain Junction Depth 0.20 M

KP

o

C

ox

Transconductance Parameter 144.5 mho/volt

NSUB N

D

Average Substrate Doping Concentration 1.2(10

17

) atoms/cm

3

NFS Surface State Subthreshold Parameter 6.6(10

11

)

DELTA Threshold Versus Gate Width Parameter 0.65

LD L

d

Source-Drain Lateral Overlap 67 nM

TPG Gate Material Polarity (Ignored If VTO Is Specified) 1

UO

p

Low Field Carrier Mobility 220 cm

2

/volt-sec

THETA 1/V

ve

Vertical Field Mobility Degradation Parameter 0.18 volt

1

RSH R

sh

Source & Drain Sheet Resistance 2.0 O/Square

VMAX v

sat

Maximum Carrier Drift Velocity (1.8)(10

5

) meter/sec

KAPPA Channel Length Modulation Factor 0.078 volt

1

ETA 1/V

Threshold Parameter For Drain induced barrier lowering 0.018

Chapter 4 MOSFET Models and Applications

- 325 -

SPICE

SYMBOL

TEXT

SYMBOL

DESCRIPTION

OF PARAMETER

VALUE UNITS

CGDO C

gdo

Gate-Drain Overlap Capacitance Density 370 pF/meter

CGSO C

gso

Gate-Source Overlap Capacitance Density 370 pF/meter

CGBO C

gbo

Gate-Bulk Overlap Capacitance Density 430 pF/meter

CJSW C

jsw

Zero Bias Sidewall Capacitance Density 190 pF/meter

CJ C

jo

Zero Bias Bulk Junction Capacitance Density 930 F/meter

2

MJ m

j

Bulk Junction Grading Coefficient 0.48

MJSW m

jsw

Sidewall Junction Grading Coefficient 0.35

PB V

j

Bulk-Drain/Bulk-Source Junction Built-In Potential 0.92 volt

LEVEL Model Type 3

Table (4.2). HSPICE LEVEL 3 model parameters for the 500 nM PMOS complement to the NMOS transistor

parameterized in Table (4.1).

SOLUTION #4.1:

(1). The results of the characteristic curve simulation for gate-source voltages spanning 0 to 700

mV are displayed in Figure (4.5). It is convenient to plot this drain current on a logarithmic

scale so as to convey clearly the exponential dependence of the subthreshold drain current on

the applied gate-source voltage. From (4-17), with recognition given to the fact that SPICE

simulators plot logarithmic axes to base 10,

Figure (4.5). The subthreshold volt-ampere characteristics of the NMOS device considered in

Example (4.1). The bulk-source voltage, V

bs

, in this example is zero volts.

(2). A casual inspection of the simulated results suggests that the gate-source voltage range that

embodies the semi-logarithmically linear subthreshold domain is

gs

150 mV V 550 mV . s s

(E1-1)

If we compare (E1-3) to (4-16), we are led to believe that V

hf

150 mV and V

h

550 mV.

The HSPICE simulation executed to arrive at the curves of Figure (4.5) projects a device

threshold voltage of 563.7 mV, which is only 2.49% larger than our crude estimate of the up-

per gate-source voltage limit to subthreshold regime operation.

ENGINEERING COMMENTARY:

The empirical model parameters, , , and V

df

, can be extracted from the foregoing simulated

10

-12

10

-11

10

-10

10

-9

10

-8

10

-7

10

-6

10

-5

10

-4

0 100 200 300 400 500 600 700

D

r

a

i

n

C

u

r

r

e

n

t

(

A

m

p

e

r

e

s

)

Gate-Source Voltage, (mV) V

gs

V = 0.5 V

ds

V = 1.5 V

ds

V = 2.5 V

ds

Chapter 4 MOSFET Models and Applications

- 326 -

plots. This task is left as an exercise for the reader.

As we expect, the semi-logarithmic plots of the subthreshold drain current appear to be linear

functions of the applied gate-source voltage. Also as expected, the drain-source voltage has

minimal effect on observed subthreshold drain current. Because of this small impact, the

characteristic equation in (4-18) can be modified is such a way as to project a nominally

semi-logarithmically linear dependence on drain-source voltage.

4.3.3. TRANSISTOR IN OHMIC REGIME

NMOS transistors operate in their ohmic, or triode, regimes when two conditions are

satisfied. The first of these conditions embraces the turn on constraint,

gs h

V V , > (4-21)

which implicitly asserts that the oxide-bulk potential at the interface proximate to the source im-

plant be at least twice the Fermi potential. It follows that in the ohmic domain, the interfacial

channel region near the source site is strongly inverted. The second condition underpinning oh-

mic operation is

ds gs h

V V V . < (4-22)

A useful alternative form to (4-22) derives from an inspection of the device schematic symbol in

Figure (4.1). In particular, we see therein that

ds gs gd

V V V . = (4-23)

If we substitute (4-23) into (4-22), we arrive at an equivalent and more illuminating form of the

second condition for ohmic regime operation; namely,

gd h

V V , > (4-24)

which implies that the oxide-bulk interfacial region near the drain volume must support, like the

region near the source site, twice Fermi potential. When combined with (4-21), we therefore

conclude that (4-22), or its equivalent form in (4-24), stipulates that the necessary condition

commensurate with MOSFET operation in the ohmic regime is that the entire channel extending

from the source site to the drain volume and lying immediately beneath the oxide layer be

strongly inverted.

In the ohmic region, the drain current of an NMOS device is given by the classic

Schichman-Hodges relationship

[5]

,

ds

d n ds gs h

V W

I K V V V ,

L 2

| | | |

=

| |

\ . \ .

(4-25)

where K

n

, the transconductance coefficient (in units of mhos/volt), is

n n ox

K C ; = (4-26)

in turn, the oxide capacitance density, C

ox

, is given by (4-9). In (4-26),

n

represents the mobility

(in units of cm

2

/volt-sec) of free electrons in the strongly inverted channel lying beneath the gate

oxide layer. The electron mobility, which is literally a measure of the ability of an electron to be

moved or transported, is a function of the electric field strength established in the channel by an

applied drain-source voltage. It is also dependent on the absolute surface temperature, T, of the

device. To the latter end, a commonly invoked empirical relationship is

[6]

3 2

o

n n o

T

(T) (T ) ,

T

| |

~

|

\ .

(4-27)

Chapter 4 MOSFET Models and Applications

- 327 -

where

n

(T

o

) denotes the mobility of a free electron at the reference temperature, T

o

, which is

traditionally taken as 27 C. We note that the mobility, and hence parameter K

n

, decreases with

increasing operating temperature. Accordingly, we say that an ohmic regime MOSFET boasts a

negative temperature coefficient in that for constant gate-source and drain-source voltages, its

drain current decreases with increasing device operating temperature.

For a PMOS transistor, the ohmic regime drain current expression and its associated

parametric relationships are similar to those of the NMOS unit. In particular, a PMOS device

operates in its ohmic region for

sg h

sd sg h

V V

,

V V V

>

<

(4-28)

where it is understood that the threshold voltage, V

h

, remains positive in these expressions.

When (4-28) is satisfied, the PMOS drain current, I

d

, which flows out of the drain terminal of the

transistor, is

sd

d p sd sg h

V W

I K V V V ,

L 2

| | | |

=

| |

\ . \ .

(4-29)

where transconductance coefficient K

p

is

p p ox

K C , = (4-30)

and

p

is the mobility of holes in the strongly inverted channel of the PMOS transistor. The

temperature dependence of hole mobility mirrors that of electron mobility, per (4-27).

The operational regime under present consideration is referred to as the ohmic regime

because for very small drain-source voltages, the MOSFET emulates a voltage-controlled linear

resistance; in effect, it functions as an electronic potentiometer. We can begin to appreciate this

contention by examining the small signal conductance, say G

ds

, established between the drain

and source terminals of a MOSFET operating in its ohmic regime. By small signal conduc-

tance presented between drain and source terminals, we mean the ratio of a differentially small

change in drain current to a corresponding differentially small change in drain-source voltage, as

opposed to a straightforward drain current to drain-source voltage ratio. For an NMOS device,

(4-25) gives

( )

gs h ds

d d

ds n gs h ds

ds

ds ds

gs h

V V V

I I W

G K V V V .

V

V L V

V V

2

| |

| | | c

| |

= =

| | |

c

\ .

\ .

|

\ .

(4-31)

There are interesting aspects to this result. The first of these is that if V

ds

<< (V

gs

V

h

), which

subscribes to the ohmic constraint of (4-22),

ds gs h

ds gs h

d d

ds

V V V

ds ds

V V V

I I

G .

V V

<<

<<

c

~

c

(4-32)

Equation (4-32) suggests that the subject small signal conductance behaves as a linear conduc-

tance (or resistance). In order to clarify this contention, consider a traditional linear, two ter-

minal resistance, R, which supports a terminal voltage, V. Our friend, George Ohm, teaches I =

V/R. But for this linear, two terminal resistance, we also learn that

I I 1

.

V V R

c

= =

c

(4-33)

Chapter 4 MOSFET Models and Applications

- 328 -

which is to say that the small signal and actual conductance of a two-terminal linear resistance

are identical. By comparison of (4-33) and (4-32), we conclude that the conductance between

the drain-source terminals of a MOSFET operated with very small drain-source voltage is

indisputably linear.

The second of the aforementioned two important points is that for very small V

ds

,

( )

ds gs h

ds gs h

d

ds n gs h

V V V

ds

V V V

I W

G K V V ,

V L

<<

<<

c

| |

~

|

c

\ .

(4-34)

which underscores the fact that the observed small signal, and approximately linear, conductance

is controllable via the applied gate-source voltage, V

gs

. In a word, a MOSFET operated in its oh-

mic domain at very small drain-source voltages behaves approximately as a linear two terminal

element whose conductance (resistance) can be adjusted by the applied gate-source voltage, V

gs

.

In effect, the device behaves as an electronic (voltage-controlled) potentiometer, as opposed to a

mechanical one whose resistance is altered by physically rotating a dial that causes the resistance

between two terminals to change. Finally, we note that as V

ds

approaches the voltage difference,

(V

gs

V

h

), the conductance in (4-28) tends toward zero or equivalently, the small signal drain-

source resistance tends toward infinity. On the presumption that drain current nonetheless flows

when V

ds

tends toward (V

gs

V

h

), this means that the MOSFET behaves as an ideal current

source.

As we might surmise from the preceding arguments, MOSFETs operating in ohmic do-

mains enjoy widespread utility as electronically adjustable resistances. Such resistances prove

indispensable when manufacturing or environmental uncertainties compel adjustments in net-

work pole or zero frequencies, gain, impedances, biasing levels, or other performance metrics.

While ohmic regime MOSFETs can function as amplifiers, the gain and bandwidth afforded in

the ohmic regime are muted in comparison to the attainable performance when transistors oper-

ate in the next regime we shall consider; namely, the saturation regime.

4.3.4. TRANSISTOR IN SATURATION REGIME

In the saturation regime, the gate-source and drain-source voltages of an NMOS

transistor satisfy the dual constraints,

gs h

ds gs h dsat

V V

,

V V V V

>

>

(4-35)

where V

dsat

is termed the drain saturation voltage. In saturation, therefore, the interfacial region

near the source is strongly inverted, but the second of the two inequalities in (4-35), which is

tantamount to requiring V

gd

s V

h

, implies that the drain end of the channel is not necessarily in-

verted. Transistors typically operate in saturation for linear signal processing applications. In

this domain, the drain current is given by

( )

2

n

d gs h

K W

I V V .

2 L

| |

=

|

\ .

(4-36)

Since this drain current is postured as independent of the drain-source voltage, V

ds

, we can argue

that to the extent that (4-36) accurately reflects the saturated static characteristic curves of a

MOSFET, the MOSFET behaves as an ideal current source whose current value is controlled by

a quadratic function of gate-source voltage V

gs

. In effect, we see that the saturated MOSFET be-

haves as a nonlinear (square law), voltage controlled current source. For low-power linear

Chapter 4 MOSFET Models and Applications

- 329 -

applications, we generally wish to set the quiescent drain-source voltage as close to its drain

saturation value as input signal amplitude conditions and corresponding linearity targets permit.

The saturated drain current given by (4-36) is commonly referenced as the drain satura-

tion current, I

dsat

, which is to say that a drain current of I

dsat

corresponds to an applied drain-

source voltage of V

dsat

. Specifically,

( )

2

2

n n

d gs h dsat

dsat

K K W W

I V V V I .

2 L 2 L

| | | |

= =

| |

\ . \ .

(4-37)

We should advise caution when interpreting current I

dsat

and voltage V

dsat

as constants. While

these two metrics are theoretically independent of the drain-source voltage, V

ds

, they are

functionally dependent on gate-source and drain-source voltages. For example, we shall see that

because of mobility degradation incurred by the lateral drain to source electric fields resulting

from applied drain-source voltages, V

dsat

is dependent on V

ds

.

For PMOS devices (4-35) and (4-36) respectively become

sg h

sd sg h ssat

V V

V V V V

>

>

(4-38)

and

( )

2

p p 2

d sg h ssat

K K

W W

I V V V .

2 L 2 L

| | | |

= =

| |

\ . \ .

(4-39)

The voltage excess, (V

sg

V

h

) is properly interpreted as the source-drain saturation voltage, V

ssat

.

As in the case of the ohmic regime volt-ampere characteristics, threshold voltage V

h

remains a

positive number.

In order to ensure operation in the saturated domain, the minimum permissible drain-

source voltage is the drain saturation voltage, which for NMOS is V

dsat

, as defined by (4-35). In

contrast, the maximum permissible drain-source voltage commensurate with ohmic regime

operation is also V

dsat

. From the ohmic regime drain current expression of (4-25), we note that

when V

ds

= V

dsat

= (V

gs

V

h

), the resultant drain current is identical to the drain saturation cur-

rent, I

dsat

, given by (4-37). Thus, at the cusp of the ohmic and saturation regimes, the ohmic re-

gime current dutifully conflates with the value of the saturation region drain current.

4.3.5. SUMMARY OF TRANSISTOR CHARACTERISTICS

In the interest of future convenience, we summarize herewith the volt-ampere

characteristics of both NMOS and PMOS MOSFETS operated in cutoff, subthreshold, ohmic,

and saturated regimes. For the NMOS transistor,

( )

ds df

gs hf

V V

gs bs

ot hf gs h

T

d

ds

n ds gs h gs h ds gs h

2

n gs h gs h ds gs h

0, for V V

V V

W

I 1 , V V V

L V

I ,

V

2 V V V , V V & V V V

2

V V , V V & V V V

exp e

q

|

|

<

+ | |

| |

| |

|

s <

|

|

|

|

\ .

\ .

\ .

=

| |

> < |

|

\ .

> >

(cutoff)

(subthreshold)

(ohmic)

(saturation)

(4-40)

Chapter 4 MOSFET Models and Applications

- 330 -

where we have introduced the convenient shorthand notation of parameter |

n

as,

n

n

K W

.

2 L

| |

|

\ .

(4-41)

We should take care to note that parameter |

n

scales linearly with the gate aspect ratio of the de-

vice. For the PMOS counterpart to the NMOS transistor,

( )

sd df

sg hf

V V

sg sb

ot hf sg h

T

d

sd

p sd sg h sg h sd sg h

2

p sg h sg h sd sg h

0, for V V )

V V

W

I 1 , V V V

L V

I ,

V

2 V V V , V V & V V V

2

V V , V V & V V V

exp e

q

|

|

<

+ | |

| |

| |

|

s <

|

|

|

|

\ .

\ .

\ .

=

| |

> < |

|

\ .

> >

(cutoff

(subthreshold)

(ohmic)

(saturation)

(4-42)

where

p

p

K

W

.

2 L

| |

|

\ .

(4-43)

Figure (4.6). Sample common source volt-ampere characteristics of an n-channel transistor having a threshold

voltage, V

h

, of 500 mV and an effective scaled transconductance parameter, |

n

, of 1 mmho/volt.

Figure (4.6) graphically illustrates the MOSFET static characteristic curves with both

source and bulk terminals grounded. The representative NMOS transistor boasts a threshold vol-

tage of 0.5 V and a scaled transconductance parameter (|

n

) of 1.0 mmho/V. These curves focus

on only the ohmic and saturation relationships delineated in (4-40); that is, we have tacitly taken

subthreshold currents to be zero. We should note that as expected, the volt-ampere characteris-

tics are nominally linear for drain-source voltages in the immediate neighborhood of V

ds

= 0

volts. In addition, these low voltage curves correctly project increasing slope, and hence increas-

ing small signal conductance (decreasing small signal resistance) for increases in the gate-source

voltage. In Figure (4.6), we include a plot, shown as the dashed curve, which highlights the

0

2

4

6

8

10

12

0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5

D

r

a

i

n

C

u

r

r

e

n

t

,

I

d

,

(

m

A

)

Drain-Source Voltage, V

ds

, (volts)

V

gs

= 2 volts

V

gs

= 3 volts

V

gs

= 4 volts

V

gs

= 5 volts

Ohmic-Saturation

Boundary

Nominally Linear

Characteristics

Chapter 4 MOSFET Models and Applications

- 331 -

boundary between ohmic and saturated domains. To the left of this boundary, the ohmic

relationship in (4-40) applies, while to the right of the boundary, constant drain current given by

the saturation equation in (4-40) is evidenced. We shall shortly learn that the characteristic

curves of an actual transistor, such as the one parameterized in Table (4.1), can differ markedly

from the idealized Schichman-Hodges behavior plotted in Figure (4.6).

4.4.0. FIRST ORDER DESIGN STRATEGY

The MOSFET models defined by (4-38) and (4-40) reflect simple and arguable

idealized transistor behavior in that they tacitly ignore numerous second order phenomena that

are loom significant in scaled, deep submicron, MOS technology devices. These higher order

effects, which we shall investigate later in this chapter, include channel length modulation

(CLM), field-induced carrier mobility degradation, drain induced barrier lowering (DIBL), and

high frequency capacitive phenomena. But the Schichman-Hodges model, which is sometimes

referred to as the long channel model, for the ohmic and saturation regimes of operation is

nonetheless attractive because its analytical tractability forges an insightful understanding of first

order, circuit design results. These insights are vital to the design process because they inspire

creative design measures that mitigate the deleterious effects of the aforementioned and other

high order device phenomena. Consequently, circuit designers commonly rely on the simple

models for initial circuit design studies, with the understanding that these first order results must

ultimately be thoroughly investigated, refined, and presumably optimized through extensive

manual and computer-aided analyses that are premised on more realistic device models. The

result of these advanced analytical measures might be adjustments to biasing currents and

voltages, adjustments of gate aspect ratios, and even modifications of circuit architectures.

Another reason for invoking the simple transistor models in first order design calculations is

premised on elegantly elementary logic. In particular, if we cannot get an analog circuit to

function as we wish it to operate for approximate and presumably simple device representations,

we have little chance to get our circuit to work properly when real, refined, accurate, and

necessarily more complex device models are exploited. In other words, the exploitation of

simple device models in a successful first order design venture is a necessary, but admittedly

insufficient, condition for the realization of finalized design architectures.

4.4.1. VOLTAGE-CONTROLLED DIFFERENTIAL AMPLIFIER

Our first demonstration of the utility of the Schichman-Hodges model entails a

consideration of the simple differential amplifier depicted in Figure (4.7). In this schematic dia-

gram, transistors M1 and M2 are integrated transistors having identical gate aspect ratios. Since

the smallest circuit potential is zero, the bulk terminals of both transistors are returned directly to

ground in order to preclude forward current conduction across the bulk-source and bulk-drain

junctions. This action, of course, facilitates electrical isolation between the two active devices.

In view of the fact that the source terminals of the two devices are also grounded in the consi-

dered amplifier, the bulk-source voltages applied to the transistors are zero, thereby nullifying

BITM

2

and rendering the two transistor threshold voltages constant at their zero bias values, V

ho

.

We note that the gate-source voltages, V

gs1

and V

gs2

, applied respectively to M1 and M2 are

2

Remember that BITM stands for bulk-induced threshold modulation, or simply, body (or bulk) effect.

Chapter 4 MOSFET Models and Applications

- 332 -

di

gs1 ci

di

gs2 ci

V

V V

2

.

V

V V

2

= +

=

(4-44)

In (4-44), V

ci

is taken as an adjustable bias that is required to assure turn on of the two transistors.

Since voltage V

ci

is a component of both of the two gate-source voltages, it is traditionally re-

ferred to as a common mode input voltage. On the other hand, voltage V

di

is taken as a time

varying signal that the network is called upon to amplify. We note by (4-44) that the difference

of the two applied gate-source voltages, (V

gs1

V

gs2

), is identically V

di

, whence we shall book-

mark V

di

as the differential mode input voltage.

Figure (4.7). Schematic diagram of a simple differential amplifier realized in MOSFET

technology.

Let us assume that we wish the differential amplifier at hand to operate linearly. This is

to say that we wish the indicated output voltage, V

do

, to respond linearly to the applied differen-

tial mode input signal, V

di

. We observe that V

do

is a differential output voltage in that it

represents the difference between the voltages established at the respective drain terminals of

transistors M2 and M1. Since MOSFETs embedded in linear circuit applications are invariably

biased in their saturation regimes, we systematically ensure that for all time,

di

gs1 ci ho

di

gs2 ci ho

V

V V V

2

,

V

V V V

2

= + >

= >

(4-45)

for which a clear necessary design condition is V

ci

> V

ho

. The amount by which voltage V

ci

must

exceed threshold level V

ho

is determined by the amplitude of the applied differential mode signal,

which is to say that care must be exercised to ensure that (4-45) is accommodated for all ex-

pected values of signal voltage V

di

.

But in addition to satisfying (4-45), which merely ensures that the transistors conduct

nonzero drain currents for all time, the individual drain-source voltages of the transistors must be

+

V

ci

M1 M2

V /2

di

V /2

di

I

d1

I

d2

R R

+V

dd

+ V

do

Chapter 4 MOSFET Models and Applications

- 333 -

at least as large as their drain saturation voltages. An inspection of the subject schematic dia-

gram reveals that the drain-source voltage, V

ds1

of transistor M1 is, in terms of the M1 drain cur-

rent, I

d1

,

ds1 dd d1

V V I R. = (4-46)

On the other hand, for M2,

ds2 dd d2

V V I R , = (4-47)

where I

d2

is the instantaneous drain current conducted by transistor M2. Accordingly, we require

ds1 dd d1 gs1 ho

ds2 dd d2 gs2 ho

V V I R V V

.

V V I R V V

= >

= >

(4-48)

The relationships in (4-46) mandate that the power line voltage, V

dd

, must be sufficiently large,

while the load resistances, R, in the drain circuits cannot be too large for stipulated drain current

values.

In the saturation regime, the drain currents identified in (4-46) and (4-47) are given by

the Schichman-Hodges expressions,

( )

( )

2

d1 n gs1 ho

2

d2 n gs2 ho

I V V

,

I V V

=

=

(4-49)

where use is made of the fact that since transistors M1 and M2 are identical devices biased with

zero bulk-source voltages, they share the same transconductance coefficient, |

n

, and the same

threshold potential, V

ho

. It follows that the differential drain current, (I

d1

I

d2

), is

( ) ( )

2 2

d1 d2 n gs1 ho gs2 ho

I I V V V V .

(

=

(

(4-50)

We see that the bracketed quantity is of the algebraic form, (a

2

b

2

). It can therefore be factored

as (a + b)(a b), which no doubt enhances the pride our high school algebra teachers have in us.

Thus,

( )( )

d1 d2 n gs1 gs2 ho gs1 gs2

I I V V 2V V V .

(

= +

(4-51)

Using (4-45), this result can be couched into the more useful construct,

( )

d1 d2 n ci ho di

I I 2 V V V . = (4-52)

The differential output voltage response, V

do

, of the subject network now follows as

( ) ( )

do d1 d2 n ci ho di

V R I I 2 R V V V . = = (4-53)

It is worth texting home about the last result. The most notable aspect of (4-53) is that

for constant common mode input voltage, V

ci

, the output voltage response is a linear function of

the input differential input signal, V

di

. In other words, the amplifier linearly processes the ap-

plied signal, V

di

. This linearity follows without any a priori restrictions on either the input signal

amplitude or the precise nature of the biasing established by voltages V

dd

and V

ci

. Indeed, the

only presumption we enforced at the outset is that both transistors in the amplifier operate for all

values of V

ci

, V

di

, and V

dd

in their saturation domains.

A subliminal ramification of (4-53) is that there is no static, or DC, level associated

with the differential voltage response, V

do

. In other words, when V

di

= 0, V

do

= 0. It is one thing

to observe this apparent triviality, but it is quite another thing to understand and appreciate the

phenomenon. We begin by observing that with V

di