Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Deep Submicron CMOS Tech DSM

Caricato da

neva91Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Deep Submicron CMOS Tech DSM

Caricato da

neva91Copyright:

Formati disponibili

Slide 1

Loke et al.

Avago Technologies

Introduction to Deep Submicron

CMOS Device Technology

& Its Impact on Circuit Design

Alvin Loke, Tin Tin Wee, Mike Gilsdorf,

Tom Cynkar & Jim Pfiester

Imaging Solutions Division, Fort Collins, Colorado

IEEE Solid-State Circuits Society Seminar

Vancouver Chapter

February 23, 2006

Slide 2

Loke et al.

Avago Technologies

Outline

Part 1

CMOS Technology Trends

MOSFET Basics

Lithography

Deep Submicron FET Fabrication Sequence

Enabling Device & Equipment Technologies

Part 2

FET Non-idealities & Second-Order Effects

Impact of Technology Advances on Circuit Design

Process Variations in Manufacturing

Conclusions

Slide 3

Loke et al.

Avago Technologies

Evolution of IC Technology

0.25m CMOS

(Motorola, 1996)

Al (0.5%Cu) Al (0.5%Cu)

oxide (SiO2 ) oxide (SiO2 )

M5 M5

M4 M4

M3 M3

M2 2

M1 M1

I can see Waldo, but wheres the transistor?

1

st

Fabricated IC

(Texas Instruments, 1958)

90nm CMOS

(TSMC, 2002)

M5 M5

M4 M4

M3 M3

M2 M2

M1 M1

M9 M9

M8 M8

M7 M7

M6 M6

Cu Cu

Low Low- -K K

Is the transistor getting less important?

Slide 4

Loke et al.

Avago Technologies

Source: Thompson et al., Intel (2002)

CMOS Scaling is Alive & Well

Transistors Are Picking Up The Slack

Where are we now?

130nm & 90nm in volume manufacturing (8-inch wafers)

65nm early production in progress (12-inch wafers)

Key trends:

Gate CD* scaling is more aggressive than interconnect scaling

Scaling driven by exclusively by digital circuit needs

Source: Wu et al., TSMC (2002)

90nm Technology

59nm 59nm

* CD = critical dimension

Slide 5

Loke et al.

Avago Technologies

Why Aggressive FET Scaling?

The road to higher digital performance

C

load

reduce parasitics (largely dominated by wires & gate load)

V reduce V

DD

or logic swing, need for core & I/O FETs

I

FET

all about moving charge quickly

Major hiccup along the way

Interconnect scaling much more difficult than

anticipated, especially Cu/low-K reliability

t

delay

C

load

V

I

FET

I

dsat

C

ox

(W/L) (V

GS

V

T

)

2

How to beef up I

FET

?

Tweak with , C

ox

, L & V

T

Technology scaling not necessarily compatible with analog design

Stress-Induced

Voiding

Got redundant vias?

Slide 6

Loke et al.

Avago Technologies

Why Should Designers Care So Much

About Technology Details?

Technology dictates performance limitations

Simulating layout-extracted parasitics now even more critical

Statistical design considerations necessary for circuit functionality

Technology-related surprises keep showing up as we keep scaling

Implementation of accurate models is ALWAYS late

Live with new technology-related effects & issues before they are

included in simulations

New model implementations not necessarily accurate or reliable

Meanwhile, learn to either mitigate or exploit these effects

Keeping your foundry partner honest is key to silicon success

J ob security

Slide 7

Loke et al.

Avago Technologies

MOS Fundamentals

V

T

= FET ON voltage, i.e., gate voltage required to form inversion layer

connecting source & drain by shorting out back-to-back pn-junctions with

substrate

V

T

= V

FB

+ 2

b

+

Q

dep

C

ox

b

= ln

N

A

n

i

k

B

T

q

p-substrate

+ + + + + + + + + + + + + + + +

Q

dep

depletion

charge

n

inversion layer

poly gate

n

+

source

n

+

drain

silicon

surface

+ + + + + + + + + + + + + + +

flatband (offset) voltage

due to oxide charge &

work function difference

oxide capacitance

per unit area =

ox

/ t

ox

bulk potential

depletion charge per unit area

= qN

A

x

dep

N

A

(x

dep

1/ N

A

)

Remember E = / ?

Slide 8

Loke et al.

Avago Technologies

Electron Energy Band Diagram

Formation of Inversion Layer

V

T

= gate voltage required to reverse doping of silicon surface, i.e., move

s

by 2

b

onset of inversion

(surface is undoped)

s

M O S

s

= 0

onset of strong inversion

(V

T

condition)

s

V

T

M O S

s

= -

b

inversion

layer

V

T

= V

FB

+ 2

b

+

Q

dep

C

ox

offset bulk

drop

oxide

drop

E

C

E

V

E

i

flatband

(no field in silicon)

s

E

F

E

F

silicon

surface

M O S

s

=

b

b

= ln

N

A

n

i

k

B

T

q

Slide 9

Loke et al.

Avago Technologies

All the Action is at the Surface

V

GS

> V

T

V

DS

> 0 (net source-to-drain current flow)

Carriers easily overcome source barrier

Surface is strongly inverted

V

GS

V

T

V

DS

= 0 (no net current flow)

Source barrier is lowered

Surface is inverted

V

GS

= 0

V

DS

= 0 (no net current flow)

Large source barrier

(back-to-back diodes)

electron electron

current current

Source: Sze (1981)

Slide 10

Loke et al.

Avago Technologies

Lifes Never So Perfect

Ideal

I

DS

V

DS

Reality

Well plunge into a lot of neat second-order effects.

But first, we need to understand what physical structure

were dealing with, and how it has evolved with scaling

I

DS

V

DS

V

GS

V

GS

Ideal MOSFET = voltage-controlled current source (saturation)

Slide 11

Loke et al.

Avago Technologies

Warp Speed Ahead Short-Channel Effect (SCE)

Prominent in older CMOS technologies

How to minimize SCE?

Minimize volume of charge depleted by source/drain junctions

Higher substrate doping for thinner junction depletion regions (x

dep

1/ N )

Higher V

T

& junction capacitance not consistent with scaling

Shallower source/drain junctions

Higher source/drain resistance smaller drive currents

Tighter gate coupling to surface potential

Thinner gate oxide of surface potential direct tunneling leakage

Higher K gate dielectrics

Other SCE problems: large electric fields carrier v

sat

& degradation

V

T

Drawn Channel Length, L

V

T

rolloff at shorter L

since less charge must

be depleted to achieve

surface inversion

junction

depletion

region

poly gate

n

+

n

+

p-substrate

poly gate

n

+

n

+

p-substrate

depleted by

gate charge

Slide 12

Loke et al.

Avago Technologies

Lithography Trends

What 1m Barrier???

Refractive projection (4) optics

More aggressive CDs shorter

Higher NA lenses $$$

Larger field sizes (increased integration) $$$

Now over 25% of total wafer cost

Resolution =

k

1

NA

k

1

= (resist quality, resolution tricks)

Source: ICKnowledge.com(2003)

365nm

436nm

365nm

436nm

Slide 13

Loke et al.

Avago Technologies

Step-and-Scan Projection Lithography

Beyond 0.35m Technology

Slide both reticle & wafer across narrow

slit of light

Aberration-free high-NA optics only

required along 1-D but now requires high-

precision constant-velocity stages

Still much cheaper than high-NA optics

optimized in 2-D

6 x 6 physical reticle size (4reduction)

25 x 33mm or 26 x 32mm field size

shorter edge limited by slit width

Relatively weak intensity of deep-UV

source required development of very

sensitive chemically-amplified resists for

throughput

Source: Nikon

Deep-UV Slit Source

Excimer Laser

KrF (248nm) or ArF (193nm)

Slide 14

Loke et al.

Avago Technologies

Key Resolution Enhancement Tricks

Sharp features are lost because diffraction attenuates & distorts higher

spatial frequencies (mask behaving as low-pass optical filter)

Compensate for diffraction effects when printing feature sizes << exposure

manage sub- constructive & destructive interference

Software complexity during mask fabrication but this is foundrys problem

Optical Proximity Correction (OPC)

Add scattering features to sharpen corners

Used extensively for poly gate definition

Phase Shift Masking (PSM)

Modulate optical path through mask

Used extensively for contacts & vias

Complicated for irregular patterns

Non-Optimized Optimized

Mask

Resist

Pattern

Source: Socha, ASML (2004) Source: Plummer, Stanford (2004)

Mask

Amplitude

Of Mask

Intensity

at Wafer

Amplitude

at Wafer

180

phase

shift

Slide 15

Loke et al.

Avago Technologies

Deep Submicron FET Fabrication Sequence

Well Implantation

2

n-well p-well

Gate Oxidation &

Poly Definition

3

gate oxide

Source/Drain Extension

& Halo Implantation

4

halos

Spacer Formation &

Source/Drain Implantation

5

Salicidation

6

silicide

pFET nFET

Shallow Trench Isolation

1

STI

oxide

p-Si substrate

Slide 16

Loke et al.

Avago Technologies

Basics of LOCOS Isolation 0.35m & Earlier

Industry played lots of tricks to reduce width of birds beak &

make field oxide coplanar with active areas

Required detailed understanding of visco-elastic properties of oxide

during thermal oxidation

LOCOS ran out of gas beyond 0.25m

2

Grow thermal field oxide

1

Deposit & pattern thin Si

3

N

4

oxidation mask

Strip Si

3

N

4

oxidation mask

3

birds

beak

Depth of Focus Resolution / NA

Slide 17

Loke et al.

Avago Technologies

Shallow Trench Isolation (STI) 0.25 m & Beyond

1

2

3

4

5

Advantages over LOCOS

technologies

Reduced active-to-active

spacing (no birds beak)

Planar surface for gate

lithography

Deposit & pattern thin Si

3

N

4

etch

mask & polish stop

Etch silicon around active area

profile critical to minimize stress

Grow liner SiO

2

, then deposit conformal

SiO

2

void-free deposition is critical

CMP excess SiO

2

Strip Si

3

N

4

polish stop

etched away in

subsequent

oxide cleans

Slide 18

Loke et al.

Avago Technologies

STI Etch Profile Control

Reactive ion plasma etching (RIE)

Etching ions vertically bombard

surface to be removed

Very directional

High sputtering component causes

resist to re-deposit inside trench

Tune etch gas chemistry to keep or

remove redeposited resist for

desired etch profile (micromasking)

Source: Plummer, Stanford (2004)

Slide 19

Loke et al.

Avago Technologies

STI HDP-CVD Oxide Gapfill

High-Density Plasma Chemical-Vapor Deposition

Fills aggressive aspect ratios

Rapid cycling between successive deposition & etch

Re-sputtering nature results in very compressive oxide films

Source: Plummer, Stanford (2004)

Conformal CVD HDP CVD

keyhole

Slide 20

Loke et al.

Avago Technologies

Lets Think a Little Bit More About CMP

Ideal world for CMP: want perfect

periodicity of patterns throughout

wafer

Need to throw in dummy features to

minimize pattern density variations

optimize planarity

Polishing pad will flex

oxide CMP

dishing

wafer carrier

in situ pad

conditioner

(critical)

polishing table

polishing

pad

wafer

(facing down)

slurry

optical

endpoint

detection

CMP technology pioneered by IBM

Leveraged expertise from lens polishing

Slide 21

Loke et al.

Avago Technologies

Always Think Dummies in Any CMP Process

Dummification is key to minimize topography in any CMP process

Add dummy patterns to open spaces to minimize layout density variations

Added design complexity to check layout density & insert dummy patterns

Also critical to step dummy dies along wafer circumference

Slide 22

Loke et al.

Avago Technologies

Well Implants Lots of Transistor Variants

core vs. I/O FETs, core low-/nom-/high-V

T

variants, native vs. implanted

Core

n-well

Core

n-well

Core

p-well

I/O

n-well

Core

n-well

Core

p-well

I/O

n-well

I/O

p-well

Core

native

I/O

native

Core

n-well

Core

p-well

free lunch!!!

Slide 23

Loke et al.

Avago Technologies

Well Engineering

Retrograded well dopant profile

(implants before poly deposition)

p-well

Depth

Substrate

Doping

Deeper subsurface implant

Extra dopants to prevent subsurface

punchthrough under halos

Prevent parasitic channel formation on

active sidewall beneath source/drain

Faster diffusers (B, As/P)

Shallow & steep surface channel implant

V

T

control

Slow diffusers critical (Ga, Sb)

Very deep high-dose implant

Latchup prevention

Noise immunity

Faster diffusers (B, As/P)

STI

oxide

STI

oxide

Implant order matters to prevent ion channeling, especially for the shallow implant

substrate

background

Slide 24

Loke et al.

Avago Technologies

Gate Oxidation

Need two gate oxide t

ox

s thin for core FETs & thick for I/O FETs

1 2 3

Oxide is grown, not deposited

Need high-quality Si-SiO

2

interface with low Q

f

& D

it

Gate oxide is really made of silicon oxynitride (SiO

x

N

y

)

N content prevents boron penetration from p+ poly to channel in pFETs

Improves GOI (gate oxide integrity) reliability

Side benefit increased

ox

Foundries now offer triple gate oxide (TGO) processes with two I/O FET varieties

Grow 1

st

oxide

Strip oxide for core FETs

Grow 2

nd

oxide

I/O FET

gate oxide

Core FET

gate oxide

Si substrate

gate

oxide

Slide 25

Loke et al.

Avago Technologies

Aside on Equipment Technology Evolution

Source: Maex, IMEC (2002)

Gate oxide no longer furnace grown

Multi-chamber cluster tools now

ubiquitous

Pre-oxidation clean, gate oxidation &

poly/ARL deposition performed in

separate chambers without breaking

vacuum

Better thickness & film compositional

control (native SiO

2

grows instantly

when exposed to air)

Fast minutes-seconds per wafer vs.

hours per wafer batch

Economically feasible with trend

towards larger wafer sizes

Top

View

Slide 26

Loke et al.

Avago Technologies

Poly Gate Definition

Si substrate

Process control is everything resist & poly etch chamber conditioning is

critical (lesson to remember: dont clean residues in tea cups or woks)

Way to get smaller CDs to trim more (requires tighter control)

Dummification also necessary for poly mask (ILD0 CMP)

poly-Si

1 2 3

anti-reflection

layer (ARL)

gate

oxide

resist resist

Pattern resist Trim resist

(oxygen ash)

Etch gate stack

poly

gate

Gate CD way smaller than lithography capability

Slide 27

Loke et al.

Avago Technologies

Source/Drain & Channel Engineering

Resulting structure has:

Smaller SCE

Shallow junction where needed most

Low junction capacitance

Not to be confused with LDDs in I/O FETs

Same process with spacers but Iightly

doped drain (LDD) is used for minimizing

peak E fields that cause hot carriers &

breakdown

Extensions need to be heavily doped to

minimize series resistance

Different halo & extension/LDD implants for

each FET variant

poly gate

self-aligned source/drain extension implant

(n-type)

self-aligned high-tilt halo/pocket implant

(p-type)

p-well

p-well

poly gate

dielectric spacer formation

p-well

poly gate

self-aligned source/drain implant

(n-type)

p-well

poly gate

1

2

3

4

halos

Slide 28

Loke et al.

Avago Technologies

Control of Minimum Channel Length

Foundries get paid for wafers that hit nFET & pFET I

dsat

targets in L

min

devices

which depend strongly on channel CD

Adjust resist trim ash time to compensate for poly photo variations

Adjust halo dose to compensate for poly etch variations (modulate position of pn

junction where counterdoping occurs)

Designers can help by orienting poly gates along direction of least variation

shorter

ash time

longer

ash time

poly

higher

halo dose

lower

halo dose

well

Slide 29

Loke et al.

Avago Technologies

Rapid Thermal Processing (RTP)

Wasabi Wasabi vs. Curry

Initially developed for short anneals

Impossible to control short thermal cycles in furnaces

Want minimum diffusion for shallow & abrupt junctions

Process steps:

Annealing repair implant damage

Oxidation gate oxide

Nitridation spacers, ARL

Poly deposition gate

RTP in single-wafer multi-chamber cluster tools

RTP

T

e

m

p

e

r

a

t

u

r

e

Time

Furnace

T

e

m

p

e

r

a

t

u

r

e

Time

substantial

ramp times

Slide 30

Loke et al.

Avago Technologies

Self-Aligned Silicidation (Salicidation)

Need to reduce poly & diffusion R

s

, otherwise get severe I

FET

degradation due to

voltage drops from contacts to intrinsic FET (source degeneration)

Selectivity degraded at RTA2, i.e., metal over SiO

2

& Si

3

N

4

will form silicide

Technology progression: TiSi

x

CoSi

x

NiSi

x

Scaling requires smaller silicide grain size to minimize R

s

variations

1

Deposit sicilide metal (Ti, Co, Ni)

RTA1 (low temperature)

Selective formation of metal silicide

from direct metal reaction with Si

well

diffusion

2

Strip unreacted metal

3

RTA2 (high temperature)

Transforms silicide into low-

phase by consuming more Si

4

poly

STI

Slide 31

Loke et al.

Avago Technologies

Making Cheap Resistors

Only one extra mask can buy you unsalicided poly & diffusion resistors

Salicide block etch

SiO

2

deposition prior to salicide module

field oxide

diffusion

poly

1

protection oxide

2

Salicide block etch

3

Salicide module

salicide

Slide 32

Loke et al.

Avago Technologies

Outline

Part 1

CMOS Technology Trends

MOSFET Basics

Lithography

Deep Submicron FET Fabrication Sequence

Enabling Device & Equipment Technologies

Part 2

FET Non-idealities & Second-Order Effects

Impact of Technology Advances on Circuit Design

Process Variations in Manufacturing

Conclusions

Slide 33

Loke et al.

Avago Technologies

SPICE FET Binning

Wondered why so many SPICE transistor bins, e.g, core nFETs?

A single model cannot suffice what can possibly vary with L & W?

1 6 11 16 21

2 7 12 17 22

3 8 13 18 23

4 9 14 19 24

5 10 15 20 25

0.100.24 0.5 10 20 1.2

Drawn Channel Length (m)

0.12

0.24

0.5

1

10

900

D

r

a

w

n

C

h

a

n

n

e

l

W

i

d

t

h

(

m

)

Slide 34

Loke et al.

Avago Technologies

V

T

Variations Across FET L & Win 90nm

V

T

s for 90nm core nFET @ 85C

V

T

as L

V

T

as W

WHY?

0

.

1

0

0

.

1

6

0

.

2

5

0

.

4

0

0

.

6

3

1

.

0

0

1

.

5

8

2

.

5

1

3

.

9

8

6

.

3

1

1

0

.

0

0

0

.

1

5

0

.

3

8

0

.

9

5

2

.

3

8

5

.

9

7

1

5

.

0

0

0.12

0.14

0.16

0.18

0.20

0.22

0.24

0.26

0.28

0.30

0.32

0.34

0.36

V

T

(V)

L (m)

W (m)

0.34-0.36

0.32-0.34

0.30-0.32

0.28-0.30

0.26-0.28

0.24-0.26

0.22-0.24

0.20-0.22

0.18-0.20

0.16-0.18

0.14-0.16

0.12-0.14

0.15/0.1m

15/0.1m

15/10m

0.15/10m

short

narrow

short

wide

Think how much

gate charge is

needed to raise

surface potential

needed for surface

inversion

Slide 35

Loke et al.

Avago Technologies

Revisiting Short-Channel Effect (SCE)

V

T

Drawn Channel Length, L

V

T

rolloff at shorter L

since less charge

must be depleted to

achieve surface

inversion

junction

depletion

region

poly gate

n

+

n

+

p-substrate

poly gate

n

+

n

+

p-substrate

depleted by

gate charge

But V

T

as L is observed why?

Slide 36

Loke et al.

Avago Technologies

Reverse Short-Channel Effect (RSCE)

Mechanism Transient Enhanced Diffusion (TED)

Halo implant damage creates crystalline defects that accelerate

dopant diffusion in subsequent anneals where damage is repaired

Dopants migrate to source-to-substrate junction & raise source-to-

channel barrier height

V

T

increases

Target L

min

near V

T

peak for good process margin, i.e., minimize V

T

sensitivity to poly-CD variations

V

T

Drawn Channel Length, L

as L decreases, V

T

rises

before conventional SCE

kicks in

conventional SCE

p-well

poly gate

halo

dopant

diffusion

towards

junction

Slide 37

Loke et al.

Avago Technologies

Narrow-Channel Effect (NCE)

Prominent with LOCOS isolation

Does not exist in STI

V

T

Drawn Channel Width, W

V

T

increases for narrower W

since more gate charge is

required to deplete edge of

active area under gate

poly gate

p-substrate

Thicker oxide under gate edge

Tougher to deplete

More gate charge needed for

inversion

poly gate

field

oxide

birds

beak

Sure enough, V

T

as W is observed in 90nm time for another excuse

Slide 38

Loke et al.

Avago Technologies

Reverse Narrow Channel Effect (RNCE)

Prominent in STI technologies

Concentration of electric field

lines terminating at corner

Trench recess results from

faster oxide etch rate at STI

edge during pre-oxidation HF

wet-cleans

V

T

Drawn Channel Width, W

V

T

decreases for narrower W

due to trench recessing &

corner outdoping

Edge device turns on before center

device I-V kink in very narrow devices

trench

recess

corner

outdoping

Source: Burenkov & Lorenz, Fraunhofer Institut (2003)

Slide 39

Loke et al.

Avago Technologies

Well Proximity Effect

|V

T

| if FET is too close to resist edge due to dopant ions scattering off

resist sidewall into active area during well implants

|V

T

| depends on:

FET channel distance to well mask edge

implanted ion species/energy

Other effects: , L

eff

, R

extension

I

dsat

Well mask symmetry now critical for FET matching

Modeled in BSIM4.5

high-energy

well implant

Source: TSMC (CICC 2005)

90nm 90nm

Core Core nFET nFET

V

T

,

g

m

(

V

)

Average Distance Between MOS Channel

& Well Mask Edge

active

area

island

Slide 40

Loke et al.

Avago Technologies

ON vs. OFF Current Benchmark

1.2V 1.0V 1.2V 1.0V

Comparison of 90nm Technology Foundry Vendors

1.2V 1.0V 1.2V 1.0V

nFET pFET

0.1

1.0

10.0

100.0

1000.0

0 200 400 600 800 1000 1200

O

F

F

L

e

a

k

a

g

e

C

u

r

r

e

n

t

(

n

A

/

m

)

ON Drive Current (A/m)

No free lunch principle prevails again: high I

ON

high I

OFF

V

T

s not scaling as aggressively as V

DD

(1.0V in 90nm & 65nm)

Technology providers offer variety of V

T

s on same die to

concurrently meet high-speed vs. low-leakage needs

Slide 41

Loke et al.

Avago Technologies

Leakage Current Contributions

130nm 100nm 65nm

Source: Assenmacher, Infineon (2003)

I

SUB

Subthreshold leakage from source

I

G

Gate leakage (direct tunneling)

I

GIDL

Gate-induced drain leakage (GIDL)

I

J

Junction reverse-bias leakage

Relative contributions of OFF-state leakage (but magnitude of total leakage

getting exponentially worse for deeper submicron nodes)

p-well

poly gate

n

+

n

+

V

DD

I

G

I

GIDL

I

J

I

SUB

Slide 42

Loke et al.

Avago Technologies

Subthreshold Conduction Diode Action

Diffusion of carriers from source spilling over barrier into channel when

applying V

G

to lower

s

Want tight coupling of V

G

to

s

but have capacitive sharing with substrate

Large C

ox

high-K gate dielectrics, thinner gate oxides

Small C

Si

low substrate doping, fully-depleted SOI

Inverse subthreshold slope (S) 100mV/decade at 300K (60mV/dec ideal)

e.g., V

T

=0.2V & I

ON

= 100A I

OFF

=1A !!!

Get BJT in limit C

ox

& C

Si

0

s

= V

G

C

ox

C

ox

+ C

Si

silicon surface

potential (

s

)

C

ox

gate oxide

capacitance

C

Si

silicon

depletion

capacitance

p-substrate

gate

V

G

V

B

S = ln(10)

C

ox

+ C

Si

C

ox

k

B

T

q

source

drain V

G

Slide 43

Loke et al.

Avago Technologies

Basic Intuition on Body Effect

Body or backgate effect

More reverse bias between substrate (body) & source increases |V

T

|

Basic equation: V

T

= V

T0

+ ( 2

b

+V

SB

2

b

)

Tug-o-war between V

G

& V

B

to control surface potential through C

ox

& C

si

Silicon surface

Potential (

s

)

C

ox

gate oxide

capacitance

C

Si

silicon

depletion

capacitance

p-substrate

gate

V

G

V

B

Slide 44

Loke et al.

Avago Technologies

p-well

poly gate

n

+

n

+

V

DD

Drain-Induced Barrier Lowering (DIBL)

Worsens subthreshold leakage in short-channel devices

Soft punchthrough induced by drain-to-substrate depletion region

|V

T

| as V

D

(drain-induced SCE)

V

D

drain-to-substrate depletion region grows with more reverse bias

Lateral electric fields in drain-induced depletion region lowers source-to-

channel barrier, allowing more carriers to diffuse from source to channel

Typical DIBL magnitude: V

T

= 0.12V for V

D

= +1.2V in 90nm

reduction of electron barrier

height in conduction band (CB)

at edge of source

CB

V

DD

source drain

p-well

poly gate

n

+

n

+

Slide 45

Loke et al.

Avago Technologies

A Simple Analogy

So Many Effects, How Can We Make Life A Little Easier?

Whats happening to the surface

potential?

How is source-to-channel barrier

height affected?

p-substrate

gate

V

B

source

drain

V

D

drain

substrate

(body)

V

G

V

D

source

drain

V

G

source

drain

|V

B

|

Slide 46

Loke et al.

Avago Technologies

Gate-Induced Drain Leakage (GIDL)

Drain-to-substrate leakage due to band-to-band tunneling current in

very high-field depletion region in drain overlap region

Similar gate-induced source leakage (GISL) mechanism exists when source

is raised above gate potential

Modeled in BSIM4 not BSIM3

p-well

poly gate

n

+

drain

halo

V

DD

poly gate

gate

oxide

E-field & band bending

are strong function of V

GD

& weak function of V

DB

drain

Slide 47

Loke et al.

Avago Technologies

Gate Leakage (Direct Tunneling)

Historical Trends

Source: Taur, IBM (2002)

t

ox

has been scaling aggressively with L

min

higher I

FET

tighter gate control less SCE

Significant direct tunneling for t

ox

< 2nm

Gate leakage = f (t

ox

, V

G

)

Tunneling probability exp (- t

ox

)

Hole & electron tunneling in CB & VB

High-K gate dielectric achieves same C

ox

with much thicker t

ox

Modeled in BSIM4 not BSIM3

Slide 48

Loke et al.

Avago Technologies

Poly Depletion & Surface Charge Centroid Effects

Increasing discrepancy between electrical & physical gate oxide

thicknesses since charge is not intimately in contact with oxide interface

Modeled in BSIM4 more accurate I-V & C-V calculations

Si surface charge

centroid few s away

from oxide interface

n

+

poly gate

p-well

gate

oxide

poly depletion (band

bending) results from

nonzero conductivity

gate charge centroid

few s away from

oxide interface

C

ox

=

ox

/ EOT

EOT =Equivalent Oxide Thickness

Source: Wong, IBM (2002)

C C

ox ox

1.5nm (15 1.5nm (15 ) )

poly poly- -Si Si

gate gate

Si Si

substrate substrate

gate gate

oxide oxide

Slide 49

Loke et al.

Avago Technologies

-0.5

-0.4

-0.3

-0.2

-0.1

0.0

0.1

0.2

0.3

0.4

0.5

0.1 1 10

1

L

i

n

e

a

r

V

T

a

t

8

5

o

C

(

V

)

L, Drawn Channel Length (m)

high-V

T

nom-V

T

low-V

T

low-V

T

nom-V

T

high-V

T

pFET

nFET

Using FETs with Multiple V

T

s

One Foundry Example

Be very careful when using multiple-V

T

FETs, especially in analog land

V

T

separation typically advertised only for L L

min

long L

no V

T

between

low-V

T

& nom-V

T

devices

Foundry may use different mechanisms for setting V

T

in low-V

T

vs. high-V

T

devices

Want to share as many implant masks as possible to save $$$

V

T

adjustment: channel implant vs. halo implant

short L

V

T

0.1V

between devices

V

T

V

T

Simulated Core FET V

T

(W=0.6m)

Slide 50

Loke et al.

Avago Technologies

Lateral Channel Surface Doping Under Gate Oxide

One Foundry Example

short-channel

FET

low-V

T

FET

long-channel

FET

nom-V

T

FET high-V

T

FET

source

extension

drain

extension

channel

halo implant dose is significant

to total channel dose

in short-channel FETs

large channel implant dose is

significant to total channel

dose regardless of L

Slide 51

Loke et al.

Avago Technologies

-0.6

-0.5

-0.4

-0.3

-0.2

-0.1

0.0

0.1

0.2

0.3

0.4

0.5

0.6

-40 -20 0 20 40 60 80 100 120 140 160

L

i

n

e

a

r

V

T

(

V

)

Temperature (C)

high-V

T

nom-V

T

low-V

T

low-V

T

nom-V

T

high-V

T

pFET

nFET

-0.82mV/C

-0.67mV/C

-0.55mV/C

-0.88mV/C

-1.04mV/C

-1.08mV/C

V

T

vs. Temperature

|V

T

| as T

T

E

g

n

i

b

for constant N

A

|V

T

|

V

T

can vary a lot with temperature

Worse I

OFF

due to |V

T

| & S

Temperature sensitivity depends on

W& L

b

= ln

N

A

n

i

k

B

T

q

E

g

as Atomic Spacing

Simulated Linear V

T

for 0.6/0.1m

90nm Core FET

E

g

E

V

E

C

Where are all the non-valent

electron energy levels?

Slide 52

Loke et al.

Avago Technologies

0

1

0

2

0

3

0

4

0

5

0

6

0

7

0

8

0

9

0

1

0

0

1

1

0

Temperature (C)

0.0

0.2

0.4

0.6

0.8

1.0

1.2

0

1

0

2

0

3

0

4

0

5

0

6

0

7

0

8

0

9

0

1

0

0

1

1

0

Gate Overdrive

Threshold Voltage

V

o

l

t

a

g

e

(

V

)

Temperature (C)

0

1

0

2

0

3

0

4

0

5

0

6

0

7

0

8

0

9

0

1

0

0

1

1

0

Temperature (C)

Voltage Headroom vs. Temperature

Huge issue in 90nm CMOS analog design (V

DD

=1.0V)

Must operate FET with small gate overdrive to device in saturation

T but V

T

With decreasing gate overdrive, worst case headroom may occur

at cold temperature

Not applicable to CMOS where gate overdrive >> V

T

nom-V

T

90nm

core nFET

50A

V

GS

I

dsat

C

ox

(W/L) (V

GS

- V

T

)

2

W/L=0.3/0.3m W/L=1.2/0.3m W/L=4.8/0.3m

W/L

Slide 53

Loke et al.

Avago Technologies

Impact of Halos on r

out

Halo at source side suppresses SCE in short-channel devices

Halo at drain side creates Drain-Induced Threshold Shift (DITS) in long-channel devices

Drain bias very effective in modulating drain halo barrier V

T

I

ds

Worse DIBL compared to uniform-doped FET

Can degrade FET r

out

by 10-100!!!

Critical limitation for building current sources

(cascoding difficult with low V

DD

)

Asymmetric FETs with only source-side halo

shown to improve r

out

significantly

Less degradation for devices with weaker halos

Modeled in BSIM4 not BSIM3, but still need improvement

Source: Cao et al., UC Berkeley (1999)

halo

uniform-doped

CB

V

D

source drain

Slide 54

Loke et al.

Avago Technologies

Impact of Halos on Gate Capacitance

Halo implant increases off-state gate capacitance

Impact is worst for short-channel devices where

halos contribute most significantly to channel

doping

BSIM3 & BSIM4 models can reasonably account

for poly depletion & charge centroid effects, but

implementation is largely mathematical fitting

0

2

4

6

8

10

-2.0 -1.5 -1.0 -0.5 0.0 0.5 1.0 1.5 2.0

Measurement

Simulation - Original Fit

Simulation - Improved Fit

C

p

a

r

a

l

l

e

l

(

p

F

)

V

gs

(V)

range of interest

depletion

Source

Gate

edge of depletion region

retrograded

well

halo

relative

doping

LOW HIGH

inversion

Source

Gate

inversion layer

C-V Characteristics of VCO Varactor

depletion

capacitance

modeling error

Slide 55

Loke et al.

Avago Technologies

Contact-to-Poly Capacitance

tungsten

contact

poly-Si

gate

Cross-sectional SEM of 90nm CMOS

active area

STI

oxide

nitride

spacer

contact-to-poly

capacitance

Can add substantial parasitic capacitive coupling between gate &

source/drain

Worse if Miller multiplication exists, i,e, diffusion node is not AC ground

& moves in opposite direction to gate signal

Nitride spacer makes matters worse

active

poly

gate

source/

drain

spacer

contact ILD0

Slide 56

Loke et al.

Avago Technologies

Active Area Mechanical Stress (LOD) Effect

Silicon is piezoelectric electrical properties (m*, E

g

, V

T

, ) depends on

mechanical stress state

Compression slower nFET, faster pFET

Tension faster nFET, slower pFET

STI compression in Si channel due to 10x CTE mismatch between Si &

SiO

2

and compressive stress of HDP-CVD SiO

2

film

I

ds

can easily change by 15-20% affects digital device ratios

Channel stress is strong function of distance from poly to active edge

Can play tricks with tensile spacer &

silicide films to relieve channel stress

Modeled in BSIM4 not BSIM3

high compression lower compression

Source: Xi et al., UC Berkeley (2003)

SA SB SA SB

Slide 57

Loke et al.

Avago Technologies

Layout Implications of LOD Effect

I

IN

85C

Layout Guidelines for Optimal Matching

Same L & W

Same active area size, shape &

orientation (SA, SB)

Same environment

Example: Current Mirror

I

OUT

I

IN

I

OUT

Source: ST Microelectronics (2004)

I

IN

I

OUT

I

IN

I

OUT

GND

GND

GND

BAD!

CHEAP FIX

ANAL RETENTION

Slide 58

Loke et al.

Avago Technologies

Characterizing Process Variations

Statistical variations in IC manufacturing variations in FET

characteristics

Circuits must function across operating V

DD

& temperature but also

across statistically acceptable process tolerances

Summarized by spread in nFET & pFET V

T

s, or in I

dsat

s, i.e., use V

T

or I

dsat

to summarize cumulative effect of ALL process variances

Consider die-to-die, wafer-to-wafer & lot-to-lot variations

pFET

I

dsat

nFET

I

dsat

TT

FF

SS FS

SF

I

dsat

(V

DD

V

T

)

2

pFET

V

T

nFET

V

T

TT

FF

SS

FS

SF

acceptable

F = fast

T = typical

S = slow

Slide 59

Loke et al.

Avago Technologies

Correlated vs. Uncorrelated Process Variations

Elliptical 2-D Gaussian distribution from natural variations with no

deliberate retargetting of process parameters

Tougher to control poly CD than implant doses

1.5

2.0

2.5

3.0

3.5

4.0

3.0 3.5 4.0 4.5 5.0 5.5 6.0 6.5 7.0 7.5 8.0

10/0.13m nFET I

dsat

(mA)

1

0

/

0

.

1

3

m

p

F

E

T

I

d

s

a

t

(

m

A

)

3.0

2.5

Measurements

SPICE Targets

TT TT

FF FF

SS SS

FS FS

SF SF

correlated variations due

to common processes

e.g., poly photo/etch CD &

gate oxide thickness

uncorrelated variations

due to uncommon

processes e.g., channel

& well ion implants

Slide 60

Loke et al.

Avago Technologies

Skew Process for Design Margin Verification

Process wafers with I

dsat

s that target SPICE corners of acceptable distribution

Statistical distribution is cumulative result of ALL variations for processes

targetted as NOMINAL

Countless possibilities of tweaks to achieve skew nFET/pFET I

dsat

combination

Fab typically employs SIMPLE means of retargetting nFET & pFET I

dsat

s with

very few deliberate non-nominal process tweaks

FF vs. SS

Adjust poly CD, no change in gate oxide thickness

Nominal implant doses

FS vs. SF

Adjust surface channel or halo implant dose

Nominal poly CD & gate oxide thickness

Consequences

Nominal & skew results frequently miss intended targets since nominal (by

definition) can land anywhere in distribution

Not 100% representative of natural process corners

Decent approximation for vanilla digital circuits

May be bad approximation for some analog & high-speed digital circuits if

they are insensitive to selected tweaks

Slide 61

Loke et al.

Avago Technologies

Impact of FET Mismatch

130nm Differential Amplifier Example

in+ in-

out+ out-

bias

waveforms

should be

differential

Extensive work in FET mismatch modeling, pioneered for data converters

Pelgroms basic model (applicable not just to FETs)

WL

T

V

1

Slide 62

Loke et al.

Avago Technologies

Technology Options Looking Forward

Make faster FETs by increasing C

ox

or

Increase C

ox

High-K gate dielectric (e.g., HfSiON) tighter gate coupling, lower

gate leakage

Metal/silicided gate (e.g., W) circumvent poly gate depletion

Development is facing tough integration problems (low crystallization

temperature, interface quality, hysteresis, mobility)

Likely not ready for initial 45nm production

Increase

Apply mechanical strain to channel perturbs m* in E-k diagram

Improved I

on

/I

off

performance without sacrificing leakage

Remember: nFET likes tension, pFET likes compression

Emphasis on gate & source/drain straining, not substrate straining

Already used by Intel & IBM at 90nm, TSMC starting at 65nm

I

dsat

C

ox

(W/L) (V

GS

V

T

)

2

Slide 63

Loke et al.

Avago Technologies

Strain Engineering

Basis of High Performance in 65nm & 45nm

IBM example using Dual Stress Liners (DSL) nitride liners

N P N P N P

tensile Compr

N

P

Tensile nit

Compr nit Contact

ST

Source: Chan, IBM (CICC 2005)

Slide 64

Loke et al.

Avago Technologies

The Silicon-On-Insulator (SOI) Niche

Only PD-SOI in production so far

Applications: high-end processors (e.g., IBM Cell, AMD)

Whats hot?

Low junction capacitance

No body effect allows taller FET stack with low V

DD

Steeper subthreshold characteristic (FD-SOI only)

Whats not?

Substrate memory effect substrate hacky-sacked capacitively

Substrate heating buried oxide is good insulator

Expensive substrate

In most applications, bulk CMOS is still the way to go

buried oxide

buried oxide

partially-depleted (PD-SOI) fully-depleted (FD-SOI)

Slide 65

Loke et al.

Avago Technologies

The Near Future of Patterning

Immersion Lithography

Remember oil immersion microscopy in biology class?

Extend resolution of refractive optics by squirting water puddle on wafer

surface prior to exposure

n

water

~1.45 vs. n

air

~ 1

Tedious but much cheaper than big switch to 157nm reflective optics

Will be mainstream at 45nm

NA = n sin = d / 2 f

Source: ICKnowledge.com(2003)

Resolution =

k

1

NA

Slide 66

Loke et al.

Avago Technologies

Conclusions

CMOS scaling continues to be driven by digital circuit needs,

analog modules available at a premium

New learning expected in 65nm & 45nm CMOS front-end as

we cope with design implications of strain engineering

Back-end advances in 65nm & 45nm CMOS are incremental

Always a time lag for SPICE models to include new effects

Huge issue since tapeout mistakes are costlier than ever

Need to work closely with technology providers to quickly

find out about these new effects

Account for them or avoid them!!!

Statistical & layout considerations more critical than ever

Designers with intimate knowledge of technology are best

positioned to avoid pitfalls & to turn bugs into features

Slide 67

Loke et al.

Avago Technologies

References (Part 1)

International Technology Roadmap for Semiconductors, Front End Processes (2003 Edition), 2003.

Technology Backgrounder: Immersion Lithography, ICKnowledge.com, 2003.

Technology Backgrounder: Atomic Layer Deposition, ICKnowledge.com, 2003.

H.-S. P. Wong, Beyond the Conventional Transistor, IBM Journal of Research & Development, vol. 46, no. 2/3, pp.

133-168, Mar. 2002.

C. R. Cleavelin, Front End Manufacturing Technology, IEEE IEDM Short Course on The Future of Semiconductor

Manufacturing, Dec. 2002.

D. Harame, RF Device Technologies, IEEE IEDM Short Course on RF Circuit Design for Communication Systems,

Dec. 2002.

S. Thompson et al., A 90nm Logic Technology Featuring 50nm Strained Silicon Channel Transistors, 7 Levels of Cu

Interconnect, Low k ILD, and 1m

2

SRAM Cell, IEEE IEDM Tech. Digest, pp. 61-64, Dec. 2002.

C. C. Wu et al., A 90nm CMOS Device Technology with High-Speed , General-Purpose, and Low-Leakage

Transistors for System on Chip Applications, IEEE IEDM Tech. Digest, pp. 65-68, Dec. 2002.

J . D. Plummer et al., Silicon VLSI Technology Fundamentals, Practice and Modeling, Prentice-Hall, 2000.

S.M. Sze, Physics of Semiconductor Devices (2

nd

ed.), J ohn Wiley & Sons, 1981.

Slide 68

Loke et al.

Avago Technologies

References (Part 2)

V. W. C. Chan et al., Strain Engineering for CMOS Performance Improvement, IEEE Custom Integrated Circuit Conf.,

Sept. 2005.

T. B. Hook et al., Lateral Ion Implant Straggle and Mask Proximity Effect, IEEE Trans. Electron Devices, vol. 50, no. 9,

pp. 1946-1951, Sept. 2003.

J . Assenmacher, BSIM4 Modeling and Parameter Extraction, Technical Univ. Berlin Analog Integrated Circuits

Workshop, Mar. 2003.

X. Xi et al., BSIM4.3.0 MOSFET Model Users Manual, The Regents of the University of California at Berkeley, 2003.

Y. Taur, CMOS Design Near the Limit of Scaling, IBM Journal of Research & Development, vol. 46, no. 2/3, pp. 213-

222, Mar. 2002.

C. R. Cleavelin, Front End Manufacturing Technology, IEEE IEDM Short Course on The Future of Semiconductor

Manufacturing, Dec. 2002.

R. Rios et al., A Three-Transistor Threshold Voltage Model for Halo Processes, IEEE IEDM Tech. Digest, pp. 113-116,

Dec. 2002.

R.A. Bianchi et al., Accurate Modeling of Trench Isolation Induced Mechanical Stress Effects on MOSFET Electrical

Performance, IEEE IEDM Tech. Digest, pp. 117-120, Dec. 2002.

B. Razavi, Design of Analog CMOS Integrated Circuits, McGraw-Hill, 2001.

K. M. Cao et al., Modeling of Pocket Implanted MOSFETs for Anomalous Analog Behavior, IEEE IEDM Tech. Digest,

pp. 171-120, Dec. 1999.

A. Chatterjee et al., Transistor Design Issues in Integrating Analog Functions with High Performance Digital CMOS,

IEEE Symp. VLSI Technology Tech. Digest, pp. 147-148, J une 1999.

T. H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, Cambridge University Press, 1998.

D. P. Foty, MOSFET Modeling with SPICE: Principles and Practice, Prentice-Hall, 1996.

A. Beiser, Concepts in modern Physics (4

th

ed.), McGraw-Hill, 1987.

Potrebbero piacerti anche

- FinFET History Fundamentals FutureDocumento55 pagineFinFET History Fundamentals FutureMurali Shanmuga Sundaram100% (2)

- Design and Simulation of Double Gate Fets Using Atlas: National Institute of Technology RourkelaDocumento33 pagineDesign and Simulation of Double Gate Fets Using Atlas: National Institute of Technology RourkelaPraveen KumarNessuna valutazione finora

- MOS Integrated Circuit DesignDa EverandMOS Integrated Circuit DesignE. WolfendaleNessuna valutazione finora

- Ece-V-fundamentals of Cmos Vlsi (10ec56) - SolutionDocumento41 pagineEce-V-fundamentals of Cmos Vlsi (10ec56) - SolutionSanthosh Chandu C100% (2)

- VLSI DesignDocumento181 pagineVLSI Designprabhug22Nessuna valutazione finora

- Lecture05 Ee474 Layout PDFDocumento74 pagineLecture05 Ee474 Layout PDFKesani Venkat Narsimha ReddyNessuna valutazione finora

- Can Nanotechnology Revive Field Emission Display Technology?Documento45 pagineCan Nanotechnology Revive Field Emission Display Technology?Nickk KrrishnaNessuna valutazione finora

- Nanoelectronics and at Imec: More-than-MooreDocumento52 pagineNanoelectronics and at Imec: More-than-MooreMas MoNessuna valutazione finora

- CH 03Documento37 pagineCH 03chilledkarthikNessuna valutazione finora

- Ch. 7 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsDocumento43 pagineCh. 7 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsChenming Hu100% (1)

- Sic Mos Trench Self Align Micromachines-14-02212Documento12 pagineSic Mos Trench Self Align Micromachines-14-02212terry chenNessuna valutazione finora

- Ch. 3 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsDocumento40 pagineCh. 3 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsChenming Hu100% (1)

- Fabrication of Fet: Dr. R. Ramaprabha (Sec A)Documento10 pagineFabrication of Fet: Dr. R. Ramaprabha (Sec A)Kapildev KumarNessuna valutazione finora

- Double-Gate Fully-Depleted SOI Transistors For Low-Power High-Performance Nano-Scale Circuit DesignDocumento6 pagineDouble-Gate Fully-Depleted SOI Transistors For Low-Power High-Performance Nano-Scale Circuit Designmrsathish2020Nessuna valutazione finora

- Fermilab Initiatives in 3D Integrated Circuits and SOI Design For HEPDocumento38 pagineFermilab Initiatives in 3D Integrated Circuits and SOI Design For HEPhasanfarazhdfNessuna valutazione finora

- Organic Thin Film TransistorsDocumento38 pagineOrganic Thin Film TransistorsTabish ImranNessuna valutazione finora

- ENCS333: Homework 3 Due October 31Documento4 pagineENCS333: Homework 3 Due October 31GREATJUSTGREATNessuna valutazione finora

- Chp1-2 Print BookDocumento40 pagineChp1-2 Print Bookbalaji_gawalwad9857Nessuna valutazione finora

- CMOS/Processing TechnologyDocumento15 pagineCMOS/Processing TechnologyYidnekachwe MekuriaNessuna valutazione finora

- EE476 VLSI Digital Circuits Summer 2011 Lecture 02: IC ManufacturingDocumento42 pagineEE476 VLSI Digital Circuits Summer 2011 Lecture 02: IC ManufacturingTrung LyamNessuna valutazione finora

- IC Manufacturing SMT Process FlowDocumento41 pagineIC Manufacturing SMT Process FlowAnirban KarNessuna valutazione finora

- MS and MIS PresentationDocumento15 pagineMS and MIS PresentationHajerNessuna valutazione finora

- Concepts in VLSI DesignDocumento59 pagineConcepts in VLSI DesignA.K.M.TOUHIDUR RAHMANNessuna valutazione finora

- CMOS Process: Material Mainly Taken From UMBC, Kang and CampbellDocumento38 pagineCMOS Process: Material Mainly Taken From UMBC, Kang and CampbellSmitha KollerahithluNessuna valutazione finora

- Lec1 IntroductionDocumento36 pagineLec1 IntroductionSalim SanNessuna valutazione finora

- PCIRF 3 1 LayoutDocumento61 paginePCIRF 3 1 LayoutMarius FerdyNessuna valutazione finora

- Electronic Devices in MTL Annual Report 1998Documento20 pagineElectronic Devices in MTL Annual Report 1998tbsuirNessuna valutazione finora

- 2.2 Basic Integrated Circuit Processes: ObjectiveDocumento15 pagine2.2 Basic Integrated Circuit Processes: Objectivetutul_kNessuna valutazione finora

- Outlook On CMOS Device ScalingDocumento40 pagineOutlook On CMOS Device ScalingSimone CarettaNessuna valutazione finora

- Microsoft Powerpoint - Vlsi Design AspectDocumento89 pagineMicrosoft Powerpoint - Vlsi Design AspectAKASHDIP DUTTANessuna valutazione finora

- Unit 1 Lecture Notes UpdatedDocumento53 pagineUnit 1 Lecture Notes UpdatedrsrinivasavaradanNessuna valutazione finora

- Trends in IC TechnologyDocumento26 pagineTrends in IC Technologyhale_209031335Nessuna valutazione finora

- Fabrication Technology: - Planarising Cleaning - Deposition - Patterning Implantation HeatDocumento40 pagineFabrication Technology: - Planarising Cleaning - Deposition - Patterning Implantation HeatRavi HosamaniNessuna valutazione finora

- NMOS ProcessingDocumento41 pagineNMOS ProcessingwizardvenkatNessuna valutazione finora

- Vlsi Question BankDocumento14 pagineVlsi Question BankGokila Vani50% (2)

- ScalingDocumento32 pagineScalingNK NKNessuna valutazione finora

- Microelectronics and IC TechnologyDocumento268 pagineMicroelectronics and IC TechnologyJayson Gasper Diaz AysonNessuna valutazione finora

- Short-Channel Effect Immunity (CMOS Technology Boosters)Documento33 pagineShort-Channel Effect Immunity (CMOS Technology Boosters)arjun raghavan.vNessuna valutazione finora

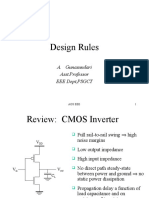

- Design Rules: A. Gunasundari Asst - Professor Eee Dept, PSGCTDocumento35 pagineDesign Rules: A. Gunasundari Asst - Professor Eee Dept, PSGCTS.DharanipathyNessuna valutazione finora

- EE241 - Spring 2005: ISSCC 2005Documento28 pagineEE241 - Spring 2005: ISSCC 2005milmalNessuna valutazione finora

- Monolithic 3D DRAM Technology: Click To Edit Master Subtitle StyleDocumento38 pagineMonolithic 3D DRAM Technology: Click To Edit Master Subtitle StyleManish SaraswatNessuna valutazione finora

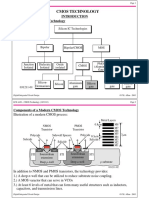

- CMOS Tech-2UP (12 - 11 - 03)Documento29 pagineCMOS Tech-2UP (12 - 11 - 03)Mountsinai CscNessuna valutazione finora

- Thin Dielectric Layers Characterization Using Corona-Oxide-Semiconductor Measurement TechniqueDocumento54 pagineThin Dielectric Layers Characterization Using Corona-Oxide-Semiconductor Measurement TechniqueTejpreet Singh BediNessuna valutazione finora

- E3-327 (3) - M SOI MOSFET Oct 2013Documento56 pagineE3-327 (3) - M SOI MOSFET Oct 2013Tara VishinNessuna valutazione finora

- Fabrikasi ICDocumento47 pagineFabrikasi ICNanamaliamNessuna valutazione finora

- Lecture 030 - Deep Submicron (DSM) Cmos TechnologyDocumento14 pagineLecture 030 - Deep Submicron (DSM) Cmos TechnologywatelzbuddyNessuna valutazione finora

- Dančak2018 Chapter TheFinFETATutorialDocumento33 pagineDančak2018 Chapter TheFinFETATutorialAhmed KamalNessuna valutazione finora

- 01 EE6306 - MOS Transistor TheoryDocumento74 pagine01 EE6306 - MOS Transistor TheoryononahjNessuna valutazione finora

- Effect of Increasing Chip DensityDocumento30 pagineEffect of Increasing Chip DensityAhmad KhalidNessuna valutazione finora

- Question AnswerDocumento7 pagineQuestion AnswerSaurabh KumarNessuna valutazione finora

- Vlsi Unit - 1Documento64 pagineVlsi Unit - 1gayatrigullipalli2003Nessuna valutazione finora

- Vlsi Basic Viva Questions and Answers PDFDocumento12 pagineVlsi Basic Viva Questions and Answers PDFAnonymous BVp7iZNessuna valutazione finora

- Special Report Soi Wafer Technology For Cmos Ics: Robert Simonton President, Simonton AssociatesDocumento11 pagineSpecial Report Soi Wafer Technology For Cmos Ics: Robert Simonton President, Simonton AssociatesMoaaz AhmedNessuna valutazione finora

- 2.2 Basic Integrated Circuit Processes: ObjectiveDocumento15 pagine2.2 Basic Integrated Circuit Processes: ObjectiveLalit BurrakNessuna valutazione finora

- 1) Explain Zener Breakdown and Avalanche Breakdown?: A Thermally Generated Carrier (Part of Reverse Saturation Current)Documento50 pagine1) Explain Zener Breakdown and Avalanche Breakdown?: A Thermally Generated Carrier (Part of Reverse Saturation Current)shobhit_srivastava_6Nessuna valutazione finora

- Token Ring Technology ReportDa EverandToken Ring Technology ReportNessuna valutazione finora

- Beginning Digital Electronics through ProjectsDa EverandBeginning Digital Electronics through ProjectsValutazione: 5 su 5 stelle5/5 (1)

- Plasma Etching Processes for Interconnect Realization in VLSIDa EverandPlasma Etching Processes for Interconnect Realization in VLSINicolas PossemeNessuna valutazione finora

- Rail To Rail Amplifier ProjectDocumento19 pagineRail To Rail Amplifier Projectneva91Nessuna valutazione finora

- Rail To Rail Output - Symmetric Error AmpsDocumento4 pagineRail To Rail Output - Symmetric Error AmpsStephen MarshallNessuna valutazione finora

- Flipped Voltade Follower PDFDocumento16 pagineFlipped Voltade Follower PDFneva91Nessuna valutazione finora

- MontecarloDocumento44 pagineMontecarloAnand Krishna GhattyNessuna valutazione finora

- HM303-6 EnglDocumento24 pagineHM303-6 Englneva91Nessuna valutazione finora

- A 560HD-Camera-SystemDocumento4 pagineA 560HD-Camera-SystemFernando Arroyo SanchezNessuna valutazione finora

- Datasheet PDFDocumento45 pagineDatasheet PDFSonidos SotoNessuna valutazione finora

- Emerging Technologies of Flexible Pressure SensorsDocumento24 pagineEmerging Technologies of Flexible Pressure Sensorsrizky ibnuNessuna valutazione finora

- Molicel P42aDocumento1 paginaMolicel P42aAlexandru Mihai TomaNessuna valutazione finora

- f3 Chapter 07Documento46 paginef3 Chapter 07Roza RozaNessuna valutazione finora

- Cerberus DmsDocumento6 pagineCerberus DmsWERMERMNessuna valutazione finora

- 4.LTE Physical Layer ProcedureDocumento82 pagine4.LTE Physical Layer ProcedureTri Frida Ningrum100% (1)

- 8K/16K 5.0V Microwire Serial EEPROM: FeaturesDocumento12 pagine8K/16K 5.0V Microwire Serial EEPROM: FeaturesStephensonNessuna valutazione finora

- Mitsubishi E700 Variable Frequency Drive (VFD) Instruction ManualDocumento322 pagineMitsubishi E700 Variable Frequency Drive (VFD) Instruction ManualMROstop.com75% (4)

- Yamaha ddk-7 PDFDocumento178 pagineYamaha ddk-7 PDFSally Di MartinoNessuna valutazione finora

- Proposed Curriculum Full Draft PDFDocumento251 pagineProposed Curriculum Full Draft PDFAadi BurlagaddaNessuna valutazione finora

- ECEPurdue MOSFET Lundstrom L2.3v3bDocumento22 pagineECEPurdue MOSFET Lundstrom L2.3v3balNessuna valutazione finora

- Mitutoyo - Mikroskopy Pomiarowe TM Seria - E14013 - 2015Documento4 pagineMitutoyo - Mikroskopy Pomiarowe TM Seria - E14013 - 2015D.T.Nessuna valutazione finora

- Delta-Q IC Series: User Manual: Important Safety and Operating InstructionsDocumento5 pagineDelta-Q IC Series: User Manual: Important Safety and Operating InstructionsGaryNessuna valutazione finora

- Site MasterDocumento5 pagineSite MasterJaved hashimNessuna valutazione finora

- Charles Proteus SteinmetzDocumento7 pagineCharles Proteus SteinmetzKelvinNessuna valutazione finora

- Coach Fast Track Lesson Plan PT 1Documento63 pagineCoach Fast Track Lesson Plan PT 1Albert Ian CasugaNessuna valutazione finora

- SportDog In-Ground FenceDocumento24 pagineSportDog In-Ground Fencesc83Nessuna valutazione finora

- IEEE STD 404-2012 RedlineDocumento89 pagineIEEE STD 404-2012 Redlineanonimoefra100% (1)

- 2016 Fall Week 1 LectureDocumento40 pagine2016 Fall Week 1 LectureTrai TranNessuna valutazione finora

- ATX PC Power Supply Diagnostic FlowchartDocumento31 pagineATX PC Power Supply Diagnostic FlowchartWali SauyunanNessuna valutazione finora

- Eva Ibbotson Journey To The River Sea PDFDocumento2 pagineEva Ibbotson Journey To The River Sea PDFBryan0% (4)

- Accuphase M8000Documento4 pagineAccuphase M8000griphonicusNessuna valutazione finora

- Panasonic LCD HDTV TC-L32X1 TC-L37X1 Chassis LH90 Service ManualDocumento63 paginePanasonic LCD HDTV TC-L32X1 TC-L37X1 Chassis LH90 Service ManualElectronica Leon Espinoza100% (4)

- Computer System ServicingDocumento11 pagineComputer System ServicingArman Santiago100% (1)

- Persistence of Vision PDFDocumento4 paginePersistence of Vision PDFkaushikmohantyNessuna valutazione finora

- Unisonic Technologies Co., LTD: Voltage Mode PWM Control CircuitDocumento7 pagineUnisonic Technologies Co., LTD: Voltage Mode PWM Control CircuitEnica LiviaNessuna valutazione finora

- Review of Pole Placement & Pole Zero Cancellation Method For Tuning PID Controller of A Digital Excitation Control SystemDocumento10 pagineReview of Pole Placement & Pole Zero Cancellation Method For Tuning PID Controller of A Digital Excitation Control SystemIJSTENessuna valutazione finora

- Security Door Controls SDC 413NDocumento4 pagineSecurity Door Controls SDC 413NJMAC SupplyNessuna valutazione finora

- 2 DofDocumento3 pagine2 DofRui GonçalvesNessuna valutazione finora