Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

ARM Processor Course Report Analysis

Caricato da

sunilsm0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

63 visualizzazioni18 pagineThe document is a semester closing report for the course ARM Processor taught in the 7th semester of the electronics and communication department. It provides details about the course such as the number of classes held, percentage of syllabus covered, topics not covered and reasons. It also includes general observations about the course textbook and recommendations for additions to the syllabus such as project-based teaching and learning with another applied course to make the subject more interesting. The report was submitted to the departmental undergraduate curriculum committee.

Descrizione originale:

Semester Closure report

Titolo originale

Scr Ec424 Ssm Aug Dec 2013

Copyright

© © All Rights Reserved

Formati disponibili

PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoThe document is a semester closing report for the course ARM Processor taught in the 7th semester of the electronics and communication department. It provides details about the course such as the number of classes held, percentage of syllabus covered, topics not covered and reasons. It also includes general observations about the course textbook and recommendations for additions to the syllabus such as project-based teaching and learning with another applied course to make the subject more interesting. The report was submitted to the departmental undergraduate curriculum committee.

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

63 visualizzazioni18 pagineARM Processor Course Report Analysis

Caricato da

sunilsmThe document is a semester closing report for the course ARM Processor taught in the 7th semester of the electronics and communication department. It provides details about the course such as the number of classes held, percentage of syllabus covered, topics not covered and reasons. It also includes general observations about the course textbook and recommendations for additions to the syllabus such as project-based teaching and learning with another applied course to make the subject more interesting. The report was submitted to the departmental undergraduate curriculum committee.

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 18

SEMESTER CLOSING REPORT - SCR

Course: ARM Processor[EC424]

Semester : VII semester Division : A,B Duration: 16 weeks ( 20/08/2013 06/12/2013)

Course Teacher : Mr. Sunil S. Mathad Department : Electronics & Communication

No. of Classes held : 43 % of syllabus covered : 100 %

Topics not covered and reasons : - NA -

General Information / observations:

1. General opinion about the text book from students was,

it was like a handbook.

2. One from a generation as a typical model like, they have

studied 8051 as a typical example of microcontroller

would have been matter .i.e A base on A RM7TDMI

processor then additional chapter just depicting the

further enhancements or changes on to the basic model.

3. Some concepts not directly related to ARM, more

related to Computer architecture such as Memory and

Cache were difficult to convey, as somewhere there is a

feeling Computer Architecture should be a Prerequisite.

4. Unless there are labs or Practical students will not be

able to appreciate the subject.

5. Some kind of self-drive is required by the students to

learn the subject.

Recommendations for deletion from syllabus:

Not Recommended

Recommendations for addition to syllabus:

Project Based teaching learning with another course which may be an

application/product development will make the subject interesting as well as

prominent.

Submitted to DUGC- ECE Dept. Signature of the Faculty Member

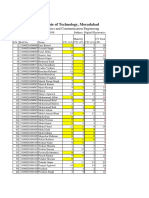

PEOs POs COs

CAT-1 CAT-2 CAT-3 Average

Match SUPPORT CONFIDENCE Match SUPPORT CONFIDENCE Match SUPPORT CONFIDENCE SUPPORT CONFIDENCE

I, II,III C,J 1,6,5 51.93 70.086 63.12 77.97 55.32 75.91 56.79 57.26

I,II K 2,4 - - 75 68.35 - - 60.37

73.26

III D,K 3,4 - - - - - 45.74 78.16 45.74

78.16

VII Semester

Division A

Attempted

Attempted

Satisfactorly Attempted

Attempted

Satisfactorly Attempted

Attempted

Satisfactorly Attempted

Attempted

Satisfactorly Attempted

Attempted

Satisfactorly Attempted

Attempted

Satisfactorly

1 2SD10EC003 Achyut Patil 0 0 0 0 0 0 0 0 0 0 0 0

2 2SD10EC004 Adarsh R Kulkarni 1 1 1 1 1 0 0 0 1 1 1 0

4 2SD10EC006 Ajit nadumani 0 0 0 0 0 0 0 0 0 0 0 0

5 2SD10EC009 Anand Ilkal 0 0 0 0 0 0 0 0 0 0 0 0

6 2SD10EC012 Miss.Anusha K R 0 0 0 0 1 1 1 1 1 1 0

7 2SD10EC013 Miss.Arati R Katekar 1 1 1 1 0 0 0 0 1 0 1 0

8 2SD10EC014 Miss.Ashwini S Doddamani 1 1 1 1 0 0 0 0 0 0 0 0

9 2SD10EC017 Chaitanya A Kulkarni 1 1 1 1 0 0 0 0 1 0 1 1

10 2SD10EC019 Miss.Manojna C H 1 1 1 1 0 0 0 0 1 1 1 1

11 2SD10EC020 Chinnappa P. kalyal 1 1 1 1 0 0 0 0 1 0 1 0

12 2SD10EC023 Durgappa 0 0 0 0 1 1 1 1 1 0 1 0

13 2SD10EC026 Govind Kumar Mali 1 1 1 1 0 0 0 0 1 0 1 0

14 2SD10EC028 Guru Shashank H N 0 0 0 0 0 0 0 0 0 0 0 0

15 2SD10EC029 Hanamant Nagappa Mangasuli 1 1 1 1 0 0 0 0 1 0 1 0

16 2SD10EC037 J.V. Manjunath 1 1 1 1 0 0 0 0 0 0 0 0

17 2SD10EC043 Miss.Karishma Kunder 0 0 0 0 1 1 1 1 1 0 1 1

18 2SD10EC045 Kunal Karan 0 0 0 0 1 0 1 1 1 0 1 1

19 2SD10EC048 Mahamedyusoof M 1 1 1 1 0 0 0 0 1 1 1 1

20 2SD10EC055 Miss.Medha R. 1 1 1 1 0 0 0 0 1 0 0 0

21 2SD10EC057 Shreyas Anil Nadagouda 1 0 1 0 0 0 0 0 0 0 1 1

22 2SD10EC059 Naik Avinash Y 0 0 0 0 1 1 1 1 1 0 0 0

23 2SD10EC065 Nikit Mahesh Gadag 1 0 1 1 0 0 0 0 1 0 1 1

24 2SD10EC123 Miss.Kamalaxi N Naganur 1 1 1 1 0 0 0 0 1 0 1 0

25 2SD11EC401 Amaresh Chavadi 1 0 1 1 0 0 0 0 1 0 1 0

26 2SD11EC414 Maltesh Pujar 1 1 1 1 0 0 0 0 0 0 1 0

27 2SD11EC426 Sachin Revannavar 0 0 1 1 0 0 0 0 0 0 0 0

28 2SD11EC432 ShivarajKumar Sonnad 1 1 1 1 0 0 0 0 0 0 1 1

29 2SD11EC434 Sunil B Bilagi 1 0 0 0 1 1 1 0 0 0 1 0

30 2SD11EC435 Sunil Kumar M Ijeri 0 0 0 0 1 1 1 1 0 0 1 0

31 2SD09EC067 PraveenKumar V Bhave 1 1 1 0 0 0 0 0 1 0 0 0

32 2SD10EC068 Nitesh Mahto 0 0 0 0 1 1 1 1 1 1 1 0

33 2SD10EC071 Miss.Poornima M 1 1 1 1 0 0 0 0 1 1 1 1

34 2SD10EC072 Pradeep Singh Yadav 0 0 0 0 1 1 1 1 1 0 1 0

35 2SD10EC078 Rajkumar M Walikar 1 1 1 1 0 0 0 0 1 0 1 1

36 2SD10EC079 Miss.Raksha S. 0 0 0 0 0 0 0 0 0 0 0 0

37 2SD10EC086 Ravikiran B Desai 0 0 0 0 1 1 1 1 1 1 1 1

38 2SD10EC092 Sandeep Kumar 1 1 1 1 0 0 0 0 1 0 1 0

39 2SD10EC093 Sangeet Suman 0 0 0 0 0 0 0 0 0 0 0 0

40 2SD10EC096 Sarvesh Anand 0 0 0 0 1 1 1 1 0 0 1 0

41 2SD10EC099 Shashank Jagadish 1 1 1 1 0 0 0 0 1 0 1 0

42 2SD10EC100 Shashank N Hegde 1 1 1 1 0 0 0 0 1 0 1 0

43 2SD10EC049 Miss.Maitri R Patil 0 0 1 1 1 1 0 0 1 0 1 0

44 2SD10EC113 Miss.Varsha D Shiveshwar 1 1 1 1 0 0 0 0 1 0 1 0

45 2SD10EC118 Vinay S G 0 0 0 0 1 1 1 1 0 0 1 0

46 2SD11EC400 Ali Asgar N Ritti 0 0 0 0 1 1 1 1 1 1 1 0

47 2SD11EC420 Naveen Kumar Hosmani 1 1 1 1 0 0 0 0 1 1 1 1

48 2SD11EC429 Satish Kumbari 0 0 0 0 1 1 1 1 1 0 1 1

26 22 27 25 16 14 14 13 31 8 35 13

strength 55.3191 56.25 33.3333 29.1667 64.5833 72.9167

confidence 84.6154 92.5926 87.5 92.8571 25.8065 37.1429

Avg Strength 51.9282

Avg Confidence 70.0857

CO: 1 PO: c,j

CAT-I

CO: c,j PO: CO: c,j PO: CO: c,j PO:

S.D.M College of Engineering & Technology, Dharwad

Worksheet for CLOCAM

Sl.NO USN

Q1.a Q1.b Q2.a Q2.b Q3.a Q3.b

CO: c,j PO: Name of the Candidates CO: 1 PO: c,j

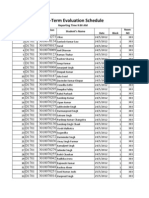

VII Semester

Division A

Attempted

Attempted

Satisfactorly Attempted

Attempted

Satisfactorly Attempted

Attempted

Satisfactorly Attempted

Attempted

Satisfactorly Attempted

Attempted

Satisfactorly Attempted

Attempted

Satisfactorly

1 2SD10EC003 Achyut Patil 0 0 0 0 1 1 1 1 1 0 1 1

2 2SD10EC004 Adarsh R Kulkarni 1 1 1 1 1 1 1 1 1 0 1 1

3 2SD10EC006 Ajit nadumani 1 1 1 1 0 0 0 0 1 0 1 1

4 2SD10EC009 Anand Ilkal 1 1 1 1 0 0 0 0 1 0 1 1

5 2SD10EC012 Miss.Anusha K R 0 0 0 0 1 0 1 0 1 0 1 1

6 2SD10EC013 Miss.Arati R Katekar 0 0 0 0 1 1 1 1 1 0 1 1

7 2SD10EC014 Miss.Ashwini S Doddamani 0 0 0 0 1 1 1 1 1 0 1 1

8 2SD10EC017 Chaitanya A Kulkarni 0 0 0 0 0 0 0 0 0 0 0 0

9 2SD10EC019 Miss.Manojna C H 0 0 0 0 1 1 1 1 1 1 1 1

10 2SD10EC020 Chinnappa P. kalyal 1 1 1 1 0 0 0 0 1 0 1 1

11 2SD10EC023 Durgappa 1 1 1 0 0 0 0 0 1 0 1 0

12 2SD10EC026 Govind Kumar Mali 0 0 0 0 1 1 1 1 1 0 1 0

13 2SD10EC028 Guru Shashank H N 1 1 1 1 0 0 0 0 1 0 1 1

14 2SD10EC029 Hanamant Nagappa Mangasuli 1 1 1 1 0 0 0 0 1 1 1 1

15 2SD10EC037 J.V. Manjunath 1 1 1 1 0 0 0 0 1 0 1 0

16 2SD10EC043 Miss.Karishma Kunder 0 0 0 0 1 1 1 1 1 0 1 1

17 2SD10EC045 Kunal Karan 1 1 1 1 0 0 0 0 1 0 1 0

18 2SD10EC048 Mahamedyusoof M 1 1 1 1 0 0 0 0 1 1 1 1

19 2SD10EC055 Miss.Medha R. 0 0 0 1 1 1 1 0 1 0 1 1

20 2SD10EC057 Shreyas Anil Nadagouda 1 1 1 1 0 0 0 0 1 0 0 0

21 2SD10EC059 Naik Avinash Y 1 1 1 1 1 1 0 0 1 0 1 1

22 2SD10EC065 Nikit Mahesh Gadag 0 0 0 0 1 1 1 1 1 0 1 0

23 2SD10EC123 Miss.Kamalaxi N Naganur 0 0 0 0 1 1 1 1 1 0 1 1

24 2SD11EC401 Amaresh Chavadi 0 0 0 0 1 1 1 1 1 0 1 1

25 2SD11EC414 Maltesh Pujar 0 0 0 0 1 1 1 1 0 0 1 0

26 2SD11EC426 Sachin Revannavar

0 0 1 1 0 0 0 0 0 0 0 0

27 2SD11EC432 ShivarajKumar Sonnad 0 0 0 0 1 1 1 1 1 0 1 1

28 2SD11EC434 Sunil B Bilagi

0 0 0 0 1 1 1 1 1 0 1 1

29 2SD11EC435 Sunil Kumar M Ijeri

0 0 0 0 1 1 1 1 1 0 1 1

30 2SD09EC067 PraveenKumar V Bhave 0 0 0 0 1 1 1 1 1 0 1 1

31 2SD10EC068 Nitesh Mahto 0 0 0 0 1 1 1 1 1 0 1 0

32 2SD10EC071 Miss.Poornima M 0 0 0 0 1 1 1 1 1 1 1 1

33 2SD10EC072 Pradeep Singh Yadav 0 0 0 0 1 1 1 1 1 0 1 0

34 2SD10EC078 Rajkumar M Walikar 0 0 0 0 1 1 1 1 1 0 1 1

35 2SD10EC079 Miss.Raksha S. 0 0 0 0 1 1 1 1 1 0 1 0

36 2SD10EC086 Ravikiran B Desai 0 0 0 0 1 1 1 1 1 0 1 1

37 2SD10EC092 Sandeep Kumar 1 1 1 1 0 0 0 0 1 1 1 1

38 2SD10EC093 Sangeet Suman 0 0 0 0 1 1 1 1 1 0 1 0

39 2SD10EC096 Sarvesh Anand 0 0 0 0 0 0 0 0 0 0 0 0

40 2SD10EC099 Shashank Jagadish 1 1 1 1 0 0 0 0 1 1 0 0

41 2SD10EC100 Shashank N Hegde 0 0 0 0 1 0 1 1 1 1 1 1

42 2SD10EC049 Miss.Maitri R Patil

0 0 0 0 1 1 1 1 1 0 1 0

43 2SD10EC113 Miss.Varsha D Shiveshwar 1 0 1 1 1 1 0 0 1 0 1 0

44 2SD10EC118 Vinay S G 0 0 0 0 1 1 1 1 1 0 1 1

45 2SD11EC400 Ali Asgar N Ritti

1 1 1 1 0 0 0 0 1 0 1 1

46 2SD11EC420 Naveen Kumar Hosmani

1 1 1 1 0 0 0 0 1 0 1 1

47 2SD11EC429 Satish Kumbari

1 1 1 1 0 0 0 0 1 0 1 1

18 17 19 19 29 27 27 25 43 7 42 30

Strength 38.29787 40.42553 61.70213 57.44681 91.48936 89.3617 75

Confidence 94.44444 100 93.10345 92.59259 16.27907 71.42857 68.35092

CO: c,j PO:

CAT-II

S.D.M College of Engineering & Technology, Dharwad

Worksheet for CLOCAM

Sl.NO USN

Q1.a Q1.b Q2.a Q2.b Q3.a Q3.b

CO: c,j PO: Name of the Candidates CO: 1 PO: c,j CO: 1 PO: c,j CO: c,j PO: CO: c,j PO:

VII Semester

Division A

Attempted

Attempted

Satisfactorl

y Attempted

Attempted

Satisfactorly Attempted

Attempted

Satisfactorly Attempted

Attempted

Satisfactorly Attempted

Attempted

Satisfactorly Attempted

Attempted

Satisfactorly

1 2SD10EC003 Achyut Patil 1 0 1 1 0 0 0 0 1 0 1 0

2 2SD10EC004 Adarsh R Kulkarni 1 0 0 0 1 0 0 0 1 1 1 1

3 2SD10EC006 Ajit nadumani 1 0 0 0 0 0 0 0 1 0 1 1

4 2SD10EC009 Anand Ilkal 1 1 1 1 0 0 0 0 1 1 1 1

5 2SD10EC012 Miss.Anusha K R 1 1 1 1 0 0 0 0 1 0 1 1

6 2SD10EC013 Miss.Arati R Katekar 1 1 1 1 0 0 0 0 1 1 1 1

7 2SD10EC014 Miss.Ashwini S Doddamani 1 1 1 1 0 0 0 0 1 1 1 1

8 2SD10EC017 Chaitanya A Kulkarni 1 0 0 0 0 0 1 1 1 1 1 1

9 2SD10EC019 Miss.Manojna C H 0 0 0 0 0 0 0 0 0 0 0 0

10 2SD10EC020 Chinnappa P. kalyal 0 0 0 0 1 0 1 1 1 1 1 1

11 2SD10EC023 Durgappa 1 0 1 1 0 0 0 0 1 0 1 1

12 2SD10EC026 Govind Kumar Mali 1 1 1 1 0 0 0 0 1 1 1 1

13 2SD10EC028 Guru Shashank H N 0 0 0 0 1 1 1 1 1 0 1 0

14 2SD10EC029 Hanamant Nagappa Mangasuli 1 0 0 0 0 0 1 0 1 0 1 1

15 2SD10EC037 J.V. Manjunath 1 1 1 1 0 0 0 0 1 1 1 0

16 2SD10EC043 Miss.Karishma Kunder 1 1 1 1 0 0 0 0 1 1 1 1

17 2SD10EC045 Kunal Karan 1 0 0 0 1 1 1 1 1 0 1 0

18 2SD10EC048 Mahamedyusoof M 0 0 0 0 0 0 0 0 0 0 0 0

19 2SD10EC055 Miss.Medha R. 1 0 1 1 0 0 0 0 1 1 1 1

20 2SD10EC057 Shreyas Anil Nadagouda 1 1 1 1 0 0 0 0 1 1 1 1

21 2SD10EC059 Naik Avinash Y 1 0 0 0 0 0 0 0 1 1 1 1

22 2SD10EC065 Nikit Mahesh Gadag 1 1 1 1 0 0 0 0 1 1 1 1

23 2SD10EC123 Miss.Kamalaxi N Naganur 1 1 1 1 0 0 0 0 1 1 1 1

24 2SD11EC401 Amaresh Chavadi 1 1 1 1 0 0 0 0 1 1 1 1

25 2SD11EC414 Maltesh Pujar 1 1 0 0 0 0 0 0 1 1 1 1

26 2SD11EC426 Sachin Revannavar 1 1 1 1 0 0 0 0 1 1 1 1

27 2SD11EC432 ShivarajKumar Sonnad 1 1 1 1 0 0 0 0 1 1 1 1

28 2SD11EC434 Sunil B Bilagi 1 1 1 0 0 0 0 0 1 1 1 1

29 2SD11EC435 Sunil Kumar M Ijeri 1 1 1 1 0 0 0 0 1 1 1 1

30 2SD09EC067 PraveenKumar V Bhave 1 1 1 1 0 0 0 0 1 1 1 1

31 2SD10EC068 Nitesh Mahto 1 0 1 1 0 0 0 0 1 0 1 0

32 2SD10EC071 Miss.Poornima M 0 0 0 0 0 0 0 0 0 0 0 0

33 2SD10EC072 Pradeep Singh Yadav 1 1 1 1 0 0 0 0 1 1 1 1

34 2SD10EC078 Rajkumar M Walikar 0 0 0 0 0 0 0 0 0 0 0 0

35 2SD10EC079 Miss.Raksha S. 0 0 1 1 0 0 0 0 0 0 1 0

36 2SD10EC086 Ravikiran B Desai 0 0 0 0 0 0 0 0 0 0 0 0

37 2SD10EC092 Sandeep Kumar 1 0 1 1 0 0 0 0 1 1 1 1

38 2SD10EC093 Sangeet Suman 0 0 1 1 0 0 0 0 0 0 1 0

39 2SD10EC096 Sarvesh Anand 1 1 1 1 0 0 0 0 1 1 1 1

40 2SD10EC099 Shashank Jagadish 0 0 0 0 0 0 0 0 0 0 0 0

41 2SD10EC100 Shashank N Hegde 1 1 1 1 0 0 0 0 1 1 1 0

42 2SD10EC049 Miss.Maitri R Patil 1 0 0 0 1 1 0 0 1 0 1 0

43 2SD10EC113 Miss.Varsha D Shiveshwar 1 1 1 1 0 0 0 0 1 1 1 1

44 2SD10EC118 Vinay S G 1 1 1 1 0 0 0 0 1 1 1 1

45 2SD11EC400 Ali Asgar N Ritti 1 1 1 1 0 0 0 0 1 1 1 1

46 2SD11EC420 Naveen Kumar Hosmani 1 1 1 1 0 0 0 0 1 1 1 1

47 2SD11EC429 Satish Kumbari 1 0 1 1 0 0 0 0 0 0 0 0

37 24 31 30 5 3 5 4 38 29 40 31

Strength 78.7234 65.9574 10.6383 10.6383 80.85106 85.10638

Confidence 64.8649 96.7742 60 80 76.31579 77.5

CO: c,j PO:

CAT-III

S.D.M College of Engineering & Technology, Dharwad

Worksheet for CLOCAM

Sl.NO USN

Q1.a Q1.b Q2.a Q2.b Q3.a Q3.b

CO: c,j PO: Name of the Candidates CO: 1 PO: c,j CO: 1 PO: c,j CO: c,j PO: CO: c,j PO:

SDM College of Engineering and Technology, Dharwad

Department of Electronics and Communication

B.E. Electronics and Communication Engineering

Continuous Assessment Test-I

Semester: VII Date: 21/09/2013

Course Title: ARM Processors

Course Code: EC424 Duration: 60 min

Course Instructor: Mr.Sunil S Mathad. Max Marks: 20

All Questions carry equal marks

1. Describe Instruction Set for Embedded Systems with respect to ARM Design Philosophy.

Or

Describe Embedded System Hardware with ARM based embedded Device as an example

2. Elaborate upon ARM processor modes and banked registers with complete ARM register set.

Or

Explain about Memory hierarchy, type, width with respect to embedded systems taking ARM

based system as an example.

3. Briefly explain about the ARM Nomenclature. If an ARM processor is numbered as ARM926EJ-

S what can be inferred from the numbers.

----x----

SDM College of Engineering and Technology, Dharwad

Department of Electronics and Communication

B.E. Electronics and Communication Engineering

Continuous Assessment Test-I

Semester: VII Date: 21/09/2013

Course Title: ARM Processors

Course Code: EC424 Duration: 60 min

Course Instructor: Mr.Sunil S Mathad. Max Marks: 20

All Questions carry equal marks

1. Describe Instruction Set for Embedded Systems with respect to ARM Design Philosophy.

Or

Describe Embedded System Hardware with ARM based embedded Device as an example

2. Elaborate upon ARM processor modes and banked registers with complete ARM register set.

Or

Explain about Memory hierarchy, type, width with respect to embedded systems taking ARM

based system as an example.

3. Briefly explain about the ARM Nomenclature. If an ARM processor is numbered as ARM926EJ-

S what can be inferred from the numbers.

----x----

SDM College of Engineering and Technology, Dharwad

Department of Electronics and Communication

B.E. Electronics and Communication Engineering

Continuous Assessment Test-I I

Semester: VII Date: 31/10/2013

Course Title: ARM Processors

Course Code: EC424 Duration: 60 min

Course Instructor: Mr.Sunil S Mathad. Max Marks: 20

Q3 is compulsory. Answer anyone from Q1 and Q2

1. A) Brief about ARM Program Status Register(PSR) along with the fields, neatly depicting their

positions in the bit pattern. 4M

B) Demonstrate the usage of LDR and SDR instructions for single byte, halfword and Word

transfer. 6M

OR

2. A) Write an Assembly language Program to compute GCD of two numbers 5M

B) Tabulate the summary of thumb register usage 5M

3. A) With an example explain ARM-Thumb interleaving 5M

B) Elaborate upon addressing methods for stack operations 5M

----x----

SDM College of Engineering and Technology, Dharwad

Department of Electronics and Communication

B.E. Electronics and Communication Engineering

Continuous Assessment Test-II

Semester: VII Date: 31/10/2013

Course Title: ARM Processors

Course Code: EC424 Duration: 60 min

Course Instructor: Mr.Sunil S Mathad. Max Marks: 20

Q3 is compulsory. Answer anyone from Q1 and Q2

1. A) Brief about ARM Program Status Register(PSR) along with the fields, neatly depicting their

positions in the bit pattern. 4M

B) Demonstrate the usage of LDR and SDR instructions for single byte, halfword and Word

transfer. 6M

OR

2. A) Write an Assembly language Program to compute GCD of two numbers 5M

B) Tabulate the summary of thumb register usage 5M

3. A) With an example explain ARM-Thumb interleaving 5M

B) Elaborate upon addressing methods for stack operations 5M

----x----

SDM College of Engineering and Technology, Dharwad

Department of Electronics and Communication

B.E. Electronics and Communication Engineering

Continuous Assessment Test-III

Semester: VII Date: 2/12/2013

Course Title: ARM Processors

Course Code: EC424 Duration: 60 min

Course Instructor: Mr.Sunil S Mathad. Max Marks: 20

Q3 is compulsory. Answer anyone from Q1 and Q2

1. A) Elaborate upon efficient use of C types 5M

B) With a flow chart explain the working of nested interrupt handler. 5M

OR

2. A) Explain about the Prioritized Direct Interrupt Handler 4M

B) For the following piece of structures draw the memory layouts 6M

(i) struct {

char a;

int b;

char c;

short d;

}

(ii) struct {

char a;

char c;

short d;

int b;

}

(iii)__packed struct {

char a;

int b;

char c;

short d;

}

3. A) Elaborate upon writing loops efficiently in C for ARM 5M

B) Explain about the IRQ and FIQ exceptions. What makes FIQ different from IRQ ? why FIQ

is Fast Interrupt Request? 5M

SDM College of Engineering and Technology, Dharwad

Department of Electronics and Communication

B.E. Electronics and Communication Engineering

Continuous Assessment Test-I

Semester: VII Date: 21/09/2013

Course Title: ARM Processors

Course Code: EC424 Duration: 60 min

Course Instructor: Mr.Sunil S Mathad. Max Marks: 20

All Questions carry equal marks

1. Describe Instruction Set for Embedded Systems with respect to ARM Design Philosophy.

The ARM instruction set differs from the pure RISC definition in several ways that make

the ARM instruction set suitable for embedded applications:

Variable cycle execution for certain instructionsNot every ARM instruction executes in

a single cycle. For example, load-store-multiple instructions vary in the number of execution

cycles depending upon the number of registers being transferred. The transfer can occur on

sequential memory addresses, which increases performance since sequential memory

accesses are often faster than random accesses. Code density is also improved since multiple

register transfers are common operations at the start and end of functions.

Inline barrel shifter leading to more complex instructionsThe inline barrel shifter is a

hardware component that preprocesses one of the input registers before it is used by a n

instruction. This expands the capability of many instructions to improve core performance

and code density.

Thumb 16-bit instruction setARM enhanced the processor core by adding a second 16-

bit instruction set called Thumb that permits the ARM core to execute either 16- or 32-bit

instructions. The 16-bit instructions improve code density by about 30% over 32-bit fixed-

length instructions.

Conditional executionAn instruction is only executed when a specific condition has been

satisfied. This feature improves performance and code density by r educing branch

instructions.

Enhanced instructionsThe enhanced digital signal processor (DSP) instructions were

added to the standard ARM instruction set to support fast 1616-bit multiplier operations and

saturation. These instructions allow a f aster-performing ARM processor in some cases to

replace the traditional combinations of a processor plus a DSP.

Or

Describe Embedded System Hardware with ARM based embedded Device as an example

2. Elaborate upon ARM processor modes and banked registers with complete ARM register set.

Or

Explain about Memory hierarchy, type, width with respect to embedded systems taking ARM

based system as an example.

Hierarchy

Type

ROM, Flash ROM,DRAM, SRAM, SDRAM

Width

The memory width is the number of bits the memory returns on each accesstypically

8, 16, 32, or 64 bits. The memory width has a direct effect on the overall performance and

cost ratio.

3. a . Briefly explain about the ARM Nomenclature. If an ARM processor is numbered as

ARM926EJ-S what can be inferred from the numbers.

ARM926EJ-S

9-Family

2-Cache and MMU

6-include tightly coupled SRAM memory

b. Explain about the Interrupts and Exceptions of ARM processors

Reset vector is the location of the first instruction executed by the processor when power is

applied. This instruction branches to the initialization code.

Undefined instruction vector is used when the processor cannot decode an instruction.

Software interrupt vector is called when you execute a SWI instruction. The SWI instruction is

frequently used as the mechanism to invoke an operating system routine.

Prefetch abort vector occurs when the processor attempts to fetch an instruction from an address

without the correct access permissions. The actual abort occurs in the decode stage.

Data abort vector is similar to a prefetch abort but is raised when an instruction attempts to

access data memory without the correct access permissions.

Interrupt request vector is used by external hardware to interrupt the normal execution flow of

the processor. It can only be raised if IRQs are not masked in the cpsr.

Priority

Address Exception type Exception Mode (1=high,6=low)

0x00000000 Reset Supervisor 1

0x00000004 Undefined instruction Undefined 6

0x00000008 Software Interrupt Supervisor 6

0x0000000C Abort (prefetch) Abort 5

0x00000010 Abort (data) Abort 2

0x00000014 Reserved Reserved Not applicable

0x00000018 IRQ IRQ 4

0x0000001C FIQ FIQ 3

SDM College of Engineering and Technology, Dharwad

Department of Electronics and Communication

B.E. Electronics and Communication Engineering

Continuous Assessment Test-I

Semester: VII Date: 31/10/2013

Course Title: ARM Processors

Course Code: EC424 Duration: 60 min

Course Instructor: Mr.Sunil S Mathad. Max Marks: 20

Q3 is compulsory. Answer anyone from Q1 and Q2

1. A) Brief about ARM Program Status Register(PSR) along with the fields, neatly depicting their

positions in the bit pattern.

B) Demonstrate the usage of LDR and STR instructions for single byte, halfword and Word

transfer. 6M

OR

2. A) Write an Assembly language Program to compute GCD of two numbers 5M

Or

gcd

CMP r1, r2

SUBGT r1, r1, r2

SUBLT r2, r2, r1

BNE gcd

B) Tabulate the summary of thumb register usage 5M

Summary of Thumb register usage.

Registers Access

r0r7 fully accessible

r8r12 only accessible by MOV, ADD, and CMP

r13 sp limited accessibility

r14 lr limited accessibility

r15 pc limited accessibility

cpsr only indirect access

spsr no access

3. A) With an example explain ARM-Thumb interleaving 5M

return address in the link register lr:

CODE32

LDR r0, =thumbRoutine+1 ; enter Thumb state

BLX r0 ; jump to Thumb code

; continue here

CODE16

thumbRoutine

ADD r1, #1

BX r14 ; return to ARM code and state

B) Elaborate upon addressing methods for stack operations 5M

SDM College of Engineering and Technology, Dharwad

Department of Electronics and Communication

B.E. Electronics and Communication Engineering

Continuous Assessment Test-III

Semester: VII Date: 2/12/2013

Course Title: ARM Processors

Course Code: EC424 Duration: 60 min

Course Instructor: Mr.Sunil S Mathad. Max Marks: 20

Q3 is compulsory. Answer anyone from Q1 and Q2

1. A) Elaborate upon efficient use of C types 5M

The Efficient Use of C Types

For local variables held in registers, dont use a char or short type unless 8-bit or 16-bit

modular arithmetic is necessary. Use the signed or unsigned int types instead. Unsigned

types are faster when you use divisions.

For array entries and global variables held in main memory, use the type with the

smallest size possible to hold the required data. This saves memory footprint. The ARMv4

architecture is efficient at loading and storing all data widths provided you traverse arrays by

incrementing the array pointer. Avoid using offsets from the base of the array with short type

arrays, as LDRH does not support this.

Use explicit casts when reading array entries or global variables into local variables,

or writing local variables out to array entries. The casts make it clear that for fast operation

you are taking a narrow width type stored in memory and expanding it to a wider type in the

registers. Switch on implicit narrowing cast warnings in the compiler to detect implicit casts.

Avoid implicit or explicit narrowing casts in expressions because they usually cost

extra cycles. Casts on loads or stores are usually free because the load or store instruction

performs the cast for you.

Avoid char and short types for function arguments or return values. Instead use the int

type even if the range of the parameter is smaller. This prevents the compiler performing

unnecessary casts.

B) With a flow chart explain the working of nested interrupt handler. 5M

OR

2. A) Explain about the Prioritized Direct Interrupt Handler 4M

Prioritized Direct Interrupt Handler

Handles higher-priority interrupts in a shorter time. Goes directly to the specific ISR.

Low interrupt latency.

Advantage: uses a single jump and saves valuable cycles to go to the ISR.

Disadvantage: each ISR has a mechanism to set the external interrupt mask to stop

lower- priority interrupts from halting the current ISR, which adds extra code to each ISR

B) For the following piece of structures draw the memory layouts 6M

(i) struct {

char a;

int b;

char c;

short d;

}

(ii) struct {

char a;

char c;

short d;

int b;

}

(iii)__packed struct {

char a;

int b;

char c;

short d;

}

3. A) Elaborate upon writing loops efficiently in C for ARM 5M

Writing Loops Efficiently

Use loops that count down to zero. Then the compiler does not need to allocate

a register to hold the termination value, and the comparison with zero is free.

Use unsigned loop counters by default and the continuation condition i!=0

rather than i>0. This will ensure that the loop overhead is only two instructions.

Use do-while loops rather than for loops when you know the loop will iterate at

least once. This saves the compiler checking to see if the loop count is zero.

Unroll important loops to reduce the loop overhead. Do not overunroll. If the

loop overhead is small as a proportion of the total, then unrolling will increase

code size and hurt the performance of the cache.

Try to arrange that the number of elements in arrays are multiples of four or

eight. You can then unroll loops easily by two, four, or eight times without

worrying about the leftover array elements.

B) Explain about the IRQ and FIQ exceptions. What makes FIQ different from IRQ ? why FIQ

is Fast Interrupt Request? 5M

An IRQ or FIQ exception causes the processor hardware to go through a standard

procedure (provided the interrupts are not masked):

1. The processor changes to a specific interrupt request mode, which reflects the

interrupt being raised.

2. The previous modes cpsr is saved into the spsr of the new interrupt request

mode.

3. The pc is saved in the lr of the new interrupt request mode.

4. Interrupt/s are disabledeither the IRQ or both IRQ and FIQ exceptions are

disabled in the cpsr. This immediately stops another interrupt request of the same

type being raised.

5. The processor branches to a specific entry in the vector table.

FIQ has more banked registers and hence context saving latency can be avoided and

while serving FIQ service routine it disables further IRQ and FIQs and known or predictable

latency.

Potrebbero piacerti anche

- Top 10 25.11.23Documento18 pagineTop 10 25.11.23sachingowdacvNessuna valutazione finora

- NBA CO - PO - PSO AL (Autosaved) - MECHATRONICSDocumento32 pagineNBA CO - PO - PSO AL (Autosaved) - MECHATRONICSSaravana Kumar MNessuna valutazione finora

- CE61003 Bridge EngineeringDocumento3 pagineCE61003 Bridge EngineeringecostarNessuna valutazione finora

- Provisional Hostel Allotment List of First Year Boys StudentsDocumento18 pagineProvisional Hostel Allotment List of First Year Boys StudentsShaurya SinghNessuna valutazione finora

- AU - SDE-M.Sc. Physics - PCP-First Year Students-Attendance 17-03-2023 To 02-04-2023Documento3 pagineAU - SDE-M.Sc. Physics - PCP-First Year Students-Attendance 17-03-2023 To 02-04-2023VIKASH PATELNessuna valutazione finora

- Padmashree Dr. V.B. Kolte-Patil College of EngineeringDocumento18 paginePadmashree Dr. V.B. Kolte-Patil College of Engineeringvijay patilNessuna valutazione finora

- HCL 2010 SelectssDocumento6 pagineHCL 2010 SelectssgopidineshNessuna valutazione finora

- Nss Attendance 2023Documento2 pagineNss Attendance 2023Sangeetha T rNessuna valutazione finora

- Chess Results ListDocumento3 pagineChess Results ListDasharath NagvekarNessuna valutazione finora

- MID-I Marks Sheet, EEE Even Sem A Y 2013-14Documento12 pagineMID-I Marks Sheet, EEE Even Sem A Y 2013-14satish reddyNessuna valutazione finora

- Fy2 Roll Call 2023-24Documento2 pagineFy2 Roll Call 2023-24Raj SharmaNessuna valutazione finora

- No Username Nama Peserta Kode Server Nama Ruang Sesi 1 Gelom BangDocumento2 pagineNo Username Nama Peserta Kode Server Nama Ruang Sesi 1 Gelom BangYagus TaofikNessuna valutazione finora

- Major Seating PlanDocumento8 pagineMajor Seating PlanSuiajNessuna valutazione finora

- Student Id Syjc 2019 20 PDFDocumento17 pagineStudent Id Syjc 2019 20 PDFAnushree SalviNessuna valutazione finora

- Daftar Nama Mahasiswa Bantuan UktDocumento3 pagineDaftar Nama Mahasiswa Bantuan UktZulyana PutriNessuna valutazione finora

- MIT2015 Placement Report PDFDocumento2 pagineMIT2015 Placement Report PDFankitmanwal08Nessuna valutazione finora

- B.tech._Developing Soft Skills (1)Documento3 pagineB.tech._Developing Soft Skills (1)rishit.pal.ug21Nessuna valutazione finora

- AeroDocumento18 pagineAeroCalNessuna valutazione finora

- Berita Acara Ujian Praktek Kerja Lapang (Kelas MSP)Documento4 pagineBerita Acara Ujian Praktek Kerja Lapang (Kelas MSP)Adi Noman SusantoNessuna valutazione finora

- Kelompok A Dan B: Analisis Tema 6 Pat Kelas Iv SDN Gendro Ii Tutur TAHUN 2021/2022Documento41 pagineKelompok A Dan B: Analisis Tema 6 Pat Kelas Iv SDN Gendro Ii Tutur TAHUN 2021/2022Didik NurNessuna valutazione finora

- Infosys VJIT 080708Documento46 pagineInfosys VJIT 080708Rama Krishna0% (1)

- Book 11Documento4 pagineBook 11Soham SahareNessuna valutazione finora

- Cse2001 Dsa End Term Attn SheetDocumento239 pagineCse2001 Dsa End Term Attn SheetShubham PathakNessuna valutazione finora

- Selected ListDocumento10 pagineSelected ListSiddharth JainNessuna valutazione finora

- Meter Not Working But CNA-1Documento9 pagineMeter Not Working But CNA-1Raj YadavNessuna valutazione finora

- List of Eligible Candidate To Appear For Physical Efficiency Test For The Fire FighterDocumento153 pagineList of Eligible Candidate To Appear For Physical Efficiency Test For The Fire FighterOmkar NaikNessuna valutazione finora

- 12.campus Notice of Applied Cloud Computing On 29th November and 1st December 2017Documento3 pagine12.campus Notice of Applied Cloud Computing On 29th November and 1st December 2017Rahul MishraNessuna valutazione finora

- Marks KOE039Documento2 pagineMarks KOE039harsh sainiNessuna valutazione finora

- End-Term Evaluation Schedule Reporting 9 AMDocumento7 pagineEnd-Term Evaluation Schedule Reporting 9 AMVipan BaggaNessuna valutazione finora

- FinalDocumento56 pagineFinalsatrio bagusNessuna valutazione finora

- Extc 20-21Documento28 pagineExtc 20-21Shailaja UdtewarNessuna valutazione finora

- Merit List Neet 25 18022024Documento1 paginaMerit List Neet 25 18022024vnaynewadNessuna valutazione finora

- 11.campus Notice of 3D Foundry Tech On 07 August 2017Documento3 pagine11.campus Notice of 3D Foundry Tech On 07 August 2017Rahul MishraNessuna valutazione finora

- List of Important Telephone NumbersDocumento14 pagineList of Important Telephone NumbersRa Gaia100% (1)

- Rollsheet Btech 1 Even 2011Documento48 pagineRollsheet Btech 1 Even 2011Vinit SalujaNessuna valutazione finora

- Accenture Assessment ScheduleDocumento24 pagineAccenture Assessment Schedulepushpayandrapati97Nessuna valutazione finora

- JNTU 2002 - 06 TOP 100 - ECE - HITECH ContibutionDocumento3 pagineJNTU 2002 - 06 TOP 100 - ECE - HITECH Contibutionapi-3704956Nessuna valutazione finora

- M.sc. Environmental Studies Entrance Test ResultDocumento27 pagineM.sc. Environmental Studies Entrance Test ResultShamim AkhtarNessuna valutazione finora

- 14.campus Notice of C2L Biz Solutions On 22 August 2017Documento4 pagine14.campus Notice of C2L Biz Solutions On 22 August 2017Rahul MishraNessuna valutazione finora

- 2016-6-Press Note - Interview Result of HP Subordinate Allied Service 2015Documento3 pagine2016-6-Press Note - Interview Result of HP Subordinate Allied Service 2015VivekNessuna valutazione finora

- Analisisi KLS 3CDocumento12 pagineAnalisisi KLS 3CLina Dedena NurelNessuna valutazione finora

- 16.campus Notice of DePronto Infotech On 14 October 2017Documento4 pagine16.campus Notice of DePronto Infotech On 14 October 2017Rahul MishraNessuna valutazione finora

- S.No Rank G.No Name Bank Ifsc Code Account NoDocumento4 pagineS.No Rank G.No Name Bank Ifsc Code Account NoNarayana SwamyNessuna valutazione finora

- Roll 10 29052023Documento12 pagineRoll 10 29052023Stark CNessuna valutazione finora

- Data PTK Uptd Pendidikan Wilayah Bojongasih: NO. Nama Nip/ Ni PPPK NuptkDocumento10 pagineData PTK Uptd Pendidikan Wilayah Bojongasih: NO. Nama Nip/ Ni PPPK NuptkALVHANI RUWIANSYAHNessuna valutazione finora

- Samalkot Train TimingsDocumento16 pagineSamalkot Train Timingsramanaidu1Nessuna valutazione finora

- Janmashtami N Purushotham 2023 Prasadam Courier Ronika22Documento150 pagineJanmashtami N Purushotham 2023 Prasadam Courier Ronika22darshangiridhariNessuna valutazione finora

- S1S2 JM 03-09-2023Documento3 pagineS1S2 JM 03-09-2023ombharambe1412Nessuna valutazione finora

- Date 4.9.2010: Subject: Student Concession PassesDocumento3 pagineDate 4.9.2010: Subject: Student Concession PassesMohan JainNessuna valutazione finora

- Final Results SEA GAMES 2013 Show Jumping TeamDocumento8 pagineFinal Results SEA GAMES 2013 Show Jumping TeamChalermcharn YotviriyapanitNessuna valutazione finora

- A978238190 24963 15 2022 Koc03che110Documento6 pagineA978238190 24963 15 2022 Koc03che110Ashish KumarNessuna valutazione finora

- Globla's Student FeesDocumento29 pagineGlobla's Student Feesrathore01Nessuna valutazione finora

- HMDA Officers Contact ListDocumento9 pagineHMDA Officers Contact ListShyamSunderNessuna valutazione finora

- Udaipur DirectoryDocumento14 pagineUdaipur DirectoryKavita ShekhawatNessuna valutazione finora

- Roll-12 14092023Documento720 pagineRoll-12 14092023Sachin KumarNessuna valutazione finora

- Ece Dept Weekly Test MarksDocumento3 pagineEce Dept Weekly Test MarkssakthikothandapaniNessuna valutazione finora

- HNI Investors Mobile Numbers PDFDocumento189 pagineHNI Investors Mobile Numbers PDFGirija Umath83% (6)

- Recognizing and Correcting Developing Malocclusions: A Problem-Oriented Approach to OrthodonticsDa EverandRecognizing and Correcting Developing Malocclusions: A Problem-Oriented Approach to OrthodonticsEustáquio A. AraújoNessuna valutazione finora

- Gpu Cat1 Scheme Apr2021Documento5 pagineGpu Cat1 Scheme Apr2021sunilsmNessuna valutazione finora

- GPU CAT3 5thjun2021 SchemeDocumento4 pagineGPU CAT3 5thjun2021 SchemesunilsmNessuna valutazione finora

- GPU CAT2 5thMAY2021 Scheme (AutoRecovered)Documento5 pagineGPU CAT2 5thMAY2021 Scheme (AutoRecovered)sunilsmNessuna valutazione finora

- PCB LabDocumento26 paginePCB LabsunilsmNessuna valutazione finora

- ACA Dec 2011 - 2Documento2 pagineACA Dec 2011 - 2Suneel ShastryNessuna valutazione finora

- Gpu Cat3 5thjun2021Documento1 paginaGpu Cat3 5thjun2021sunilsmNessuna valutazione finora

- Gpu Cat2 5thmay2021Documento1 paginaGpu Cat2 5thmay2021sunilsmNessuna valutazione finora

- Raga Time BenefitsDocumento6 pagineRaga Time BenefitssunilsmNessuna valutazione finora

- Gpu Cat1 Apr2021Documento2 pagineGpu Cat1 Apr2021sunilsmNessuna valutazione finora

- Brochure - FDP - 2020 - ECEDocumento2 pagineBrochure - FDP - 2020 - ECEsunilsmNessuna valutazione finora

- DLDDocumento138 pagineDLDMudassar HanifNessuna valutazione finora

- Digital CommunicationDocumento2 pagineDigital CommunicationsunilsmNessuna valutazione finora

- POs and PEsDocumento2 paginePOs and PEssunilsmNessuna valutazione finora

- 1 Jfets and MesfetsDocumento0 pagine1 Jfets and Mesfetsnaveednad2003556Nessuna valutazione finora

- Historical Concepts and Key Concepts in Single Subject ResearchDocumento19 pagineHistorical Concepts and Key Concepts in Single Subject ResearchsunilsmNessuna valutazione finora

- Sleep Deprivation 05-09Documento60 pagineSleep Deprivation 05-09sunilsmNessuna valutazione finora

- ASIC Design FlowDocumento10 pagineASIC Design FlowNguyen Hoang MinhNessuna valutazione finora

- Xenomia TroubleshootingDocumento14 pagineXenomia TroubleshootingsunilsmNessuna valutazione finora

- Shell InoDocumento13 pagineShell Inoericdravenll6427Nessuna valutazione finora

- POs and PEsDocumento2 paginePOs and PEssunilsmNessuna valutazione finora

- 3-Values - Attitudes - Personality and Emotions - 2Documento24 pagine3-Values - Attitudes - Personality and Emotions - 2shahjehankhoso100% (1)

- Knowledge in Perception and Illusion: Richard L GregoryDocumento6 pagineKnowledge in Perception and Illusion: Richard L Gregorynavneet kumarNessuna valutazione finora

- Inferiority Complex Theory of Human BehaviorDocumento16 pagineInferiority Complex Theory of Human Behaviorsunilsm100% (1)

- QuotesDocumento34 pagineQuotessunilsmNessuna valutazione finora

- MOS BJT ComparisonDocumento2 pagineMOS BJT ComparisonKashka IraniNessuna valutazione finora

- Risc Vs Cisc: Kate EricsonDocumento20 pagineRisc Vs Cisc: Kate EricsontryutyNessuna valutazione finora

- Digital Electronics Lab Manual for III Semester B.Tech (ECEDocumento57 pagineDigital Electronics Lab Manual for III Semester B.Tech (ECEAravind BalasundaramNessuna valutazione finora

- Chip Design Magazine April-May 2010Documento48 pagineChip Design Magazine April-May 2010sunilsmNessuna valutazione finora

- PipelineDocumento82 paginePipelinesunilsmNessuna valutazione finora

- Module2 - 8051 Instruction Set - UpdatedDocumento32 pagineModule2 - 8051 Instruction Set - UpdatedPraveen G MNessuna valutazione finora

- Genetec Silent Install ParametersDocumento6 pagineGenetec Silent Install ParametersetronmanNessuna valutazione finora

- VG Commands: LSVG Display All VgsDocumento19 pagineVG Commands: LSVG Display All VgsnarendrakaduskarNessuna valutazione finora

- Unit Ii Data Link Layer 10Documento20 pagineUnit Ii Data Link Layer 10prof_ktNessuna valutazione finora

- Dsa HashingpptDocumento8 pagineDsa HashingpptSamyak TantradiNessuna valutazione finora

- Scrip para Obtener Las Respuestas en QuizizzDocumento6 pagineScrip para Obtener Las Respuestas en QuizizzJhon Huanca50% (2)

- Big Data AnalyticsDocumento3 pagineBig Data AnalyticsAthithya RNessuna valutazione finora

- Pass SAP HANA on Power Level 2 Quiz with 84Documento19 paginePass SAP HANA on Power Level 2 Quiz with 84Boris Montoya100% (1)

- 3 The MPEG Data StreamDocumento12 pagine3 The MPEG Data Streamanshab bedariNessuna valutazione finora

- ScopesDocumento9 pagineScopesAlexandru OlariNessuna valutazione finora

- Grafana Setup FileDocumento25 pagineGrafana Setup FileElvis RadunaNessuna valutazione finora

- MP+STUDIO Manual V175Documento198 pagineMP+STUDIO Manual V175asdfNessuna valutazione finora

- Iwcf Question and AnswerDocumento4 pagineIwcf Question and AnswerHendra Jurbon50% (14)

- 33 Simulation of The DVB H Channel Coding and Transmission in MATLABDocumento3 pagine33 Simulation of The DVB H Channel Coding and Transmission in MATLABsafaNessuna valutazione finora

- Osi ModelDocumento94 pagineOsi Modelsumit_12100% (1)

- RB450GDocumento10 pagineRB450GMamajokoNessuna valutazione finora

- Framing and MethodsDocumento13 pagineFraming and Methodsarya_himanshi100% (1)

- Central User Administration - Guide To Setup & Administration of The CUADocumento3 pagineCentral User Administration - Guide To Setup & Administration of The CUAAkash ChaddhaNessuna valutazione finora

- Odi CDC Backend ProcessDocumento4 pagineOdi CDC Backend ProcessasifsubhanNessuna valutazione finora

- CPE 325: Embedded Systems Laboratory Laboratory Assignment #4Documento2 pagineCPE 325: Embedded Systems Laboratory Laboratory Assignment #4Sheeraz AliNessuna valutazione finora

- InfoPLC Net AC500 SD Rev 3 2Documento46 pagineInfoPLC Net AC500 SD Rev 3 2wilker_alves488Nessuna valutazione finora

- Intrusion Detection and Malware Analysis: Signature-Based IDSDocumento14 pagineIntrusion Detection and Malware Analysis: Signature-Based IDSAkshrayKcNessuna valutazione finora

- Real World Orchard CMS - Part 3 - Creating The Twitter WidgetDocumento9 pagineReal World Orchard CMS - Part 3 - Creating The Twitter WidgetBalvvant Singh BistNessuna valutazione finora

- File and Resource AttacksDocumento61 pagineFile and Resource AttacksAbdul Mateen UkkundNessuna valutazione finora

- Practice Exercises: Doctype Element Element Element Element Pcdata PcdataDocumento2 paginePractice Exercises: Doctype Element Element Element Element Pcdata PcdataDivyanshu BoseNessuna valutazione finora

- Juniper Ex4200 Factory ResetDocumento2 pagineJuniper Ex4200 Factory ResetrevxchrisNessuna valutazione finora

- BGP CommunitiesDocumento4 pagineBGP CommunitiesDiego Diaz RamosNessuna valutazione finora

- Author - A.Kishore: Standby Database TypeDocumento36 pagineAuthor - A.Kishore: Standby Database TypeAdnan KhanNessuna valutazione finora

- 03 FA31323EN32GA0 fmx2 PDFDocumento50 pagine03 FA31323EN32GA0 fmx2 PDFkalwar98esNessuna valutazione finora

- How to Filter a Website in RouterOSDocumento15 pagineHow to Filter a Website in RouterOSWandi BudianaNessuna valutazione finora