Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Diagrama Bloques Computadora

Caricato da

lobo20110 valutazioniIl 0% ha trovato utile questo documento (0 voti)

90 visualizzazioni14 pagineCopyright

© © All Rights Reserved

Formati disponibili

DOC, PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

© All Rights Reserved

Formati disponibili

Scarica in formato DOC, PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

90 visualizzazioni14 pagineDiagrama Bloques Computadora

Caricato da

lobo2011Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato DOC, PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 14

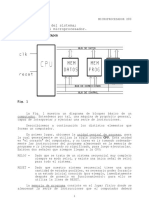

DIAGRAMA A BLOQUES DE UNA COMPUTADORA

BUS DE DATOS: Interconecta los dispositivos de entrada/salida, la memoria

RAM y el CU!

BUS DE DIRECCIO"ES: Se #tili$a para direccional las localidades de memoria

y los dispositivos de entrada/salida!

ROCESADOR

Se considera el cere%ro de la comp#tadora !Controla la

operaci&n de la comp#tadora y lleva a ca%o las '#nciones del

procesamiento de datos! (eneralmente se le conoce como

cp# por la si)la en in)les de central process #nit! Esta

'ormado por la #nidad de control la #nidad aritm*tica l&)ica y

re)istros!

+a #nidad de control es el n,cleo del procesador s#s '#nciones son:

A- +eer e interpretar las instr#cciones de los pro)ramas!

B- Diri)ir la operaci&n de los componentes internos del procesador!

C- Controlar el 'l#.o de entrada/salida de pro)rama y datos en RAM!

+A U"IDAD DE CO"TRO+ ESTA /ORMADA OR:

RE(ISTRO DE I"TRUCCIO": Contienen la con'i)#raci&n 0#e identi'ica a la

instr#cci&n 0#e en ese momento se esta e.ec#tando!

RE(ISTRO DE ROOSITO (E"ERA+: Memorias de alta velocidad 0#e

almacena los datos 0#e re0#ieren procesamiento inmediato e in'ormaci&n de

control!

CO"TADOR DE RO(RAMA: Contiene la direcci&n de RAM de la si)#iente

instr#cci&n 0#e se e.ec#tara! Al inicio contiene la primera direcci&n del

pro)rama! Cada ve$ 0#e se termina #na instr#cci&n, se incrementa

a#tom1ticamente en #no!

RE+O2: El relo. es #n circ#ito oscilador 0#e )enera p#lsos a #na 'rec#encia

constante! Estos p#lsos sincroni$an la e.ec#ci&n de cada instr#cci&n! Si en #na

comp#tadora el relo. tiene #n periodo de 344ns se dice 0#e tra%a.a a 34 M 5$!

E+ DECODI/ICADOR: Se encar)a de e6traer el c&di)o de operaci&n de la

instr#cci&n 0#e esta en el re)istro de instr#cci&n lo anali$a y determina el

con.#nto de pasos elementales en 0#e se descompone esa instr#cci&n

concreta y emite, a trav*s del sec#anciador, las se7ales necesarias al resto de

elementos para s# e.ec#ci&n!

E+ SECUE"CIADOR: Env8a mediante el %#s de datos se7ales de controla

tam%i*n llamadas microordenes a los componentes del sistema! Estas

microordenes sincroni$adas por el relo. 5acen 0#e se vaya e.ec#tando la

instr#cci&n!

U"IDAD ARITMETICA +O(ICA

Se le conoce como al#, si)las en in)les de 9arit5metic lo)ia #nit -! Es #n

con.#nto de circ#itos electr&nicos di)itales 0#e reali$an operaciones aritm*ticas

y l&)icas elementales! Se com#nica con las otras #nidades a trav*s del %#s! +a

al# esta constit#ida por :

Circ#ito operacional: Es #n con.#nto de

comp#ertas %1sicas or)ani$adas en

di'erentes arre)los para llevar aca%o las

operaciones!

Re)istros de entrada: (#ardan los datos

0#e necesita #na instr#cci&n para ser

e'ect#ada

Ac#m#lador: (#arda los res#ltados de las operaciones reali$adas por el circ#ito

operacional! Se conecta con los re)istros de entrada 9en caso de encadenaci&n-

y con el %#s de datos para la transmisi&n de res#ltados a la #nidad de control o a

la memoria!

Re)istro de estado: (r#po de %iesta%les 0#e )#ardan condiciones de la ,ltima

operaci&n 0#e p#eda a'ectar a operaciones posteriores

MEMORIA RIMARIA

Circ#itos donde se almacenan en 'orma temporal los pro)ramas y los datos!

+a in'ormaci&n procesada por el cp# se almacena normalmente en la memoria

principal 5asta 0#e termina la e.ec#ci&n del pro)rama! E6isten di'erentes tipos de

memoria primaria:

ROM 9read only memory-! :iene pro)ramada de 'a%rica

solo p#ede leerse #n e.emplo es el %ios

/las5: 9memoria instant1nea- memoria no vol1til 0#e el #s#ario p#ede alterar

es parte de m#c5os dispositivos de entrada/salida y de almacenamiento!

Cac5e: Tra%a.a de 'orma similar a la ram pero acelera y 'acilita a#n m1s la

transmisi&n de datos e instr#cciones! Se dice 0#e es ; o < veces m1s r1pida

0#e la ram pero es m#c5o mas cara se #%ica entre el procesador y la ram

RAM 9random access memory- memoria de lect#ra/escrit#ra #s#almente se

conoce como memoria principal todos los pro)ramas y datos de%en tras'erirse a

ram desde #n dispositivo de entrada! +a memoria esta dividida en celdas

n#meradas consec#tivamente! A esta n#meraci&n se le conoce como direcci&n

de memoria! +a memoria ram es vol1til!

E+EME"TOS DE U"A MEMORIA

3- Re)istro de memoria de datos contiene la direcci&n de memoria de celda en

la 0#e se va a reali$ar #na operaci&n de lect#ra o de escrit#ra!

=- Re)istro de intercam%io de memoria en operaciones de lect#ra reci%e el

dato 0#e se lee para enviarle a otra #nidad a trav*s del %#s! Si la operaci&n

es escrit#ra entonces el %#s reci%e #n dato procedente de otra #nidad!

>- Selector de memoria: conecta la celda con la 0#e va a reali$ar #na

operaci&n con el re)istro de intercam%io de memoria

MEMORIA SECU"DARIA

Son los diversos dispositivos en los c#ales se almacena in'ormaci&n en 'orma

semipermanente !los datos de almacenan en la memoria sec#ndaria y l#e)o se

llevan a la memoria ram act#almente e6iste #na )ran variedad de medios de

almacenamiento sec#ndario entre estos podemos mencionar: disco 'le6i%le

cintas ma)n*ticas disco d#ro CD ROM dvd etc!

CICLO de Instruccin

+a e.ec#ci&n de #na instr#cci&n invol#cra dos 'ases: la primera es la 'ase de

%,s0#eda de la instr#cci&n

En donde se 5ace la trans'erencia de la instr#cci&n 0#e se va a e.ec#tar desde

la RAM a la Unidad de Control! +a se)#nda es la 'ase de e.ec#ci&n la c#al

consiste en la reali$aci&n de todas las acciones 0#e

Con'orman la instr#cci&n en s8!

FASE DE BUSQUEDA

3- +a #nidad de control env8a #n micro orden para 0#e el Contador de

ro)rama pase s# contenido

Al Re)istro de Direcci&n de Memoria!

=- El selector activa la celda!

>- El contenido de la celda pasa al Re)istro de Intercam%io de Memoria

?- +a instr#cci&n pasa al Re)istro de Instr#cci&n

;- El Decodi'icador anali$a la instr#cci&n, se prepara para activar el circ#ito 0#e

reali$a la operaci&n En la A+U e in'orma al sec#enciador!

<- El contador de pro)rama se a#to incrementa en 3!

FASE DE EJECUCIN

3! Se transmite la direcci&n de la primera instr#cci&n del Re)istro de Instr#cci&n

al Re)istro de Direcci&n de Memoria!

=! El selector conecta la celda al Re)istro de Intercam%io de Memoria y e6trae

el operando 3!

>! El operando pasa del Re)istro de Intercam%io de Memoria al Re)istro de

Entrada 3!

?! Se transmite la direcci&n del se)#ndo operando del Re)istro de Instr#cci&n

al Re)istro de Direcci&n de Memoria!

;! El selector conecta la celda al Re)istro de Intercam%io de Memoria y e6trae

el operando >!

<! El operando pasa del Re)istro de Intercam%io de Memoria al Re)istro de

Entrada =!

@! El sec#enciador manda #n micro orden a la A+U para 0#e e.ec#te la

operaci&n! El res#ltado se (#arda en el Ac#m#lador!

A! El res#ltado pasa de la Al# al Re)istro de Intercam%io de Memoria!

B! Se trans'iere la direcci&n donde se va a )#ardar el res#ltado al Re)istro de

Direcci&n de

Memoria!

34! Se activa la celda con el Selector y el res#ltado pasa del Re)istro de

Intercam%io de Memoria a la celda de memoria!

Potrebbero piacerti anche

- Partes Internas Del MicroprocesadorDocumento12 paginePartes Internas Del MicroprocesadorAlfredo HBNessuna valutazione finora

- El Computador RISC & CISCDocumento32 pagineEl Computador RISC & CISCKEVIN SHARIFF MANTILLA MEZANessuna valutazione finora

- 1.0.el Computador-RISC - CISCDocumento32 pagine1.0.el Computador-RISC - CISCBryan Daniell Arrivasplata RojasNessuna valutazione finora

- Microprocesadores CuestionarioDocumento11 pagineMicroprocesadores CuestionarioGastón GallegosNessuna valutazione finora

- Introducción A Los MicrocontroladoresDocumento12 pagineIntroducción A Los MicrocontroladoresJunior FigueroaNessuna valutazione finora

- Apuntes HardwareDocumento7 pagineApuntes Hardwareripela49011Nessuna valutazione finora

- Examen de Certificación Práctica CCENT #1y2Documento85 pagineExamen de Certificación Práctica CCENT #1y2María Gabriela CárdenasNessuna valutazione finora

- Tecnicas Que Se Han Implementado Dentro Del Microprocesador para Mejorar Su RendimientoDocumento3 pagineTecnicas Que Se Han Implementado Dentro Del Microprocesador para Mejorar Su RendimientoRenzo Bassallo LeonNessuna valutazione finora

- TP MicrocontroladoresDocumento3 pagineTP MicrocontroladoresBruno TorrejonNessuna valutazione finora

- Prueba de Primer Modulo Alfabetizacion DigitalDocumento2 paginePrueba de Primer Modulo Alfabetizacion DigitalNadia AndradeNessuna valutazione finora

- Guia 1 Informatica Basica.Documento10 pagineGuia 1 Informatica Basica.lumarirairaNessuna valutazione finora

- Teoria AssemblerDocumento36 pagineTeoria Assemblerjaime_parada3097Nessuna valutazione finora

- 1.2.1 El Procesador y Sus Registros - OdpDocumento22 pagine1.2.1 El Procesador y Sus Registros - OdpErwin MontesNessuna valutazione finora

- Programación en Lenguaje EnsambladorDocumento35 pagineProgramación en Lenguaje EnsambladorRodrigo GarciaNessuna valutazione finora

- Assembler InterrupcionesDocumento6 pagineAssembler InterrupcionesMaricel Huamani MezaNessuna valutazione finora

- Automatización tratamiento aguas residualesDocumento8 pagineAutomatización tratamiento aguas residualesAndres MartínezNessuna valutazione finora

- Diagrama Bloques ComputadoraDocumento6 pagineDiagrama Bloques ComputadoraLuis Felipe OsorioNessuna valutazione finora

- Memorias programables: ROM y PROMDocumento22 pagineMemorias programables: ROM y PROMA.JNessuna valutazione finora

- Unidad Central de ProcesoDocumento5 pagineUnidad Central de ProcesoJose NainNessuna valutazione finora

- Diagrama bloques computadoraDocumento15 pagineDiagrama bloques computadoraAnabelJulianaVarhenVilelaNessuna valutazione finora

- Sistemas Operativos ISCDocumento233 pagineSistemas Operativos ISCFernando Fuentes BetancourtNessuna valutazione finora

- Arquitectura interna del microprocesador Z80Documento85 pagineArquitectura interna del microprocesador Z80Victor Hugo Hernandez100% (1)

- Tutorial SimuprocDocumento10 pagineTutorial SimuprocIrving Jesus Sanchez CamposNessuna valutazione finora

- PROFIBUS VDFDocumento12 paginePROFIBUS VDFClemente Serrano JuradoNessuna valutazione finora

- Uf ProcesadorDocumento0 pagineUf Procesadormavimu_20Nessuna valutazione finora

- Ejercicios de MMEDocumento4 pagineEjercicios de MMEfraanmp93Nessuna valutazione finora

- Organización Del ProcesadorDocumento12 pagineOrganización Del ProcesadorGeovanny Quiroz MoncerradNessuna valutazione finora

- Repertorio de Instrucciones-Características y FuncionesDocumento49 pagineRepertorio de Instrucciones-Características y FuncionesxdadaNessuna valutazione finora

- Sistemas Microprocesados PDFDocumento40 pagineSistemas Microprocesados PDFrubenutnNessuna valutazione finora

- Autómatas ProgramablesDocumento7 pagineAutómatas ProgramablesTom FarroNessuna valutazione finora

- Unidad Central de Proceso o UCPDocumento3 pagineUnidad Central de Proceso o UCPPablo MontoyaNessuna valutazione finora

- Romero Mendez Nelson Unidad 4 Sistemas ProgramablesDocumento8 pagineRomero Mendez Nelson Unidad 4 Sistemas ProgramablesNelson Romero MéndezNessuna valutazione finora

- Lab MC P3 1618200Documento9 pagineLab MC P3 1618200luis gonzalezNessuna valutazione finora

- Introduccion A Grafcet PDFDocumento524 pagineIntroduccion A Grafcet PDFChava TututiNessuna valutazione finora

- La Memoria ROMDocumento8 pagineLa Memoria ROMJesus Marchan NavarroNessuna valutazione finora

- Z80 microprocesador arquitecturaDocumento85 pagineZ80 microprocesador arquitecturaSebastián SandovalNessuna valutazione finora

- Sistemas EmbebidosDocumento86 pagineSistemas EmbebidosfrednielsNessuna valutazione finora

- Taller de OrganizaciónDocumento5 pagineTaller de OrganizaciónGREGORY HUACONNessuna valutazione finora

- Comandos OSIDocumento3 pagineComandos OSIAlfredNessuna valutazione finora

- UntitledDocumento7 pagineUntitledBRUHNessuna valutazione finora

- Unidad IDocumento10 pagineUnidad IJose Manuel Godoy EscribarNessuna valutazione finora

- Ensayo Unidad 1 Arquitectura CISC y RISCDocumento15 pagineEnsayo Unidad 1 Arquitectura CISC y RISCing_jonny23Nessuna valutazione finora

- Introduccion PVMDocumento31 pagineIntroduccion PVMtorpocoe6797Nessuna valutazione finora

- Manual de Mantenimiento de ComputadorasDocumento84 pagineManual de Mantenimiento de ComputadorasMari MedranoNessuna valutazione finora

- Circutos Digitales y Microprocesador (Diseño de Motor Paso A Paso Con Arduino)Documento20 pagineCircutos Digitales y Microprocesador (Diseño de Motor Paso A Paso Con Arduino)Jose MorenoNessuna valutazione finora

- Preguntas Iniciales Diagnostico Grado 10Documento13 paginePreguntas Iniciales Diagnostico Grado 10kiara1202Nessuna valutazione finora

- Curso Basico PLCDocumento49 pagineCurso Basico PLCSaul Garcia AguilarNessuna valutazione finora

- Modelo OsiDocumento61 pagineModelo OsiJesica Reyes FloresNessuna valutazione finora

- Componentes de Una ComputadoraDocumento22 pagineComponentes de Una ComputadoraAbdiel OmañaNessuna valutazione finora

- Informe InstruccionesDocumento32 pagineInforme InstruccionesAnthony ValleNessuna valutazione finora

- PLC cuestionarioDocumento6 paginePLC cuestionarioBrayan Iza MHNessuna valutazione finora

- Diagrama de Computadora y Funcionamiento-El Fenómeno CibernéticoDocumento8 pagineDiagrama de Computadora y Funcionamiento-El Fenómeno CibernéticoAli SerranoNessuna valutazione finora

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeDa EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeNessuna valutazione finora

- UF0852 - Instalación y actualización de sistemas operativosDa EverandUF0852 - Instalación y actualización de sistemas operativosValutazione: 5 su 5 stelle5/5 (1)

- Comprobación y optimización del programa cnc para el mecanizado por arranque de viruta. FMEH0109Da EverandComprobación y optimización del programa cnc para el mecanizado por arranque de viruta. FMEH0109Nessuna valutazione finora

- UF1275 - Selección, instalación, configuración y administración de los servidores de transferencia de archivosDa EverandUF1275 - Selección, instalación, configuración y administración de los servidores de transferencia de archivosNessuna valutazione finora

- Operaciones Auxiliares de Mantenimiento de Sistemas Microinformáticos (MF1208_1)Da EverandOperaciones Auxiliares de Mantenimiento de Sistemas Microinformáticos (MF1208_1)Nessuna valutazione finora

- UF0512 - Transmisión de información por medios convencionales e informáticosDa EverandUF0512 - Transmisión de información por medios convencionales e informáticosNessuna valutazione finora

- Aprendizaje CooperativoDocumento38 pagineAprendizaje CooperativoglovinNessuna valutazione finora

- TEMA 4 - Los Sistemas de Coordinación y de RegulaciónDocumento35 pagineTEMA 4 - Los Sistemas de Coordinación y de Regulaciónlobo2011Nessuna valutazione finora

- Examen Diagnostico de AgroecologiaDocumento3 pagineExamen Diagnostico de Agroecologialobo2011Nessuna valutazione finora

- Desarrollo Sostenible UNESCODocumento53 pagineDesarrollo Sostenible UNESCORobinson Chiran AcostaNessuna valutazione finora

- TEMA 5 - El Sistema LocomotorDocumento37 pagineTEMA 5 - El Sistema Locomotorlobo2011Nessuna valutazione finora

- Apuntes para El Estudio de La Agri Cultura de Granada Y Su Tierra en Los Primeros Años de La ConquistaDocumento18 pagineApuntes para El Estudio de La Agri Cultura de Granada Y Su Tierra en Los Primeros Años de La ConquistaeplajoscypqmcfeuekNessuna valutazione finora

- CanicasrojasDocumento17 pagineCanicasrojaslobo2011Nessuna valutazione finora

- ¿Qué Es Un Gerente?Documento9 pagine¿Qué Es Un Gerente?lobo2011Nessuna valutazione finora

- El Mayor Éxito Es Ser FelizDocumento31 pagineEl Mayor Éxito Es Ser Felizlobo2011Nessuna valutazione finora

- TERNURADocumento33 pagineTERNURAGabrielaCuadraditoUróborosSerendipiaNessuna valutazione finora

- Circuitos y Sistemas DigitalesDocumento175 pagineCircuitos y Sistemas DigitalesCarlos Espinoza100% (11)

- Tema 6 - El Sistema InmunitarioDocumento47 pagineTema 6 - El Sistema Inmunitariolobo2011Nessuna valutazione finora

- FabulaDocumento11 pagineFabulalobo2011Nessuna valutazione finora

- Calculo Diferencial Integral Func Una Var PDFDocumento683 pagineCalculo Diferencial Integral Func Una Var PDFVíctor Raúl Macedo Q.Nessuna valutazione finora

- TEMA 3 - Sistema CardiopulmonarDocumento41 pagineTEMA 3 - Sistema CardiopulmonarRoberto Cruz ValenzuelaNessuna valutazione finora

- Práctica 1-Disección de Un Corazón de CerdoDocumento4 paginePráctica 1-Disección de Un Corazón de Cerdolobo2011Nessuna valutazione finora

- Aula Historia Natural Del Cancer-1Documento18 pagineAula Historia Natural Del Cancer-1luisNessuna valutazione finora

- Práctica 2-Toma de Signos VitalesDocumento4 paginePráctica 2-Toma de Signos Vitaleslobo2011Nessuna valutazione finora

- AstrologiaDocumento756 pagineAstrologiadany_scribd89% (9)

- Definición Cáncer ControversiaDocumento34 pagineDefinición Cáncer Controversialobo2011Nessuna valutazione finora

- Organización Básica Del Cuerpo Humano PDFDocumento34 pagineOrganización Básica Del Cuerpo Humano PDFRoberto Cruz ValenzuelaNessuna valutazione finora

- X - Respuesta Inmune EspecificaDocumento3 pagineX - Respuesta Inmune Especificalobo2011Nessuna valutazione finora

- Tema G-15Documento12 pagineTema G-15lobo2011Nessuna valutazione finora

- Astrología Cientifica Simplificada - Max HeidelDocumento136 pagineAstrología Cientifica Simplificada - Max HeidelJessica Rubio100% (2)

- Matematicas Aplicadas A La Biologia PDFDocumento177 pagineMatematicas Aplicadas A La Biologia PDFdievdNessuna valutazione finora

- Guía básica del zodiacoDocumento12 pagineGuía básica del zodiacomarcos3333Nessuna valutazione finora

- Conceptos Basicos de Biologia Molecular PDFDocumento28 pagineConceptos Basicos de Biologia Molecular PDFAngelRamNessuna valutazione finora

- Celula PDFDocumento24 pagineCelula PDFAndrea ChinchillaNessuna valutazione finora

- Introduccion A Biologia para PrincipiantesDocumento18 pagineIntroduccion A Biologia para PrincipiantesPaulina LizzethNessuna valutazione finora

- 11 Bioquimica 1Documento74 pagine11 Bioquimica 1dolomaniaNessuna valutazione finora

- Aliena SlidesCarnivalDocumento18 pagineAliena SlidesCarnivalJohnattan CastroNessuna valutazione finora

- Buenas Prácticas JPA y Taylor - Heinsohn Business TechnologyDocumento6 pagineBuenas Prácticas JPA y Taylor - Heinsohn Business TechnologyBen AvrahamNessuna valutazione finora

- Serie de TaylorDocumento6 pagineSerie de TaylorOscar Gabriel Chávez GómezNessuna valutazione finora

- Separar Nombres y APELLIDOS ExcelDocumento3 pagineSeparar Nombres y APELLIDOS ExcelPippo Huaman CornelioNessuna valutazione finora

- Icewind Dale Manual SpaDocumento127 pagineIcewind Dale Manual SpaAngélica Fosar GonzálezNessuna valutazione finora

- Herramientas GerencialesDocumento7 pagineHerramientas GerencialesKris BeltranNessuna valutazione finora

- Clase2 MantenimientoTablasSQLDocumento29 pagineClase2 MantenimientoTablasSQLJuan Paredes CamposNessuna valutazione finora

- Certificados de Equipos PTW 107Documento4 pagineCertificados de Equipos PTW 107JUAN JOSE VESGA RUEDANessuna valutazione finora

- MIT515-MIT525-MIT1025-MIT1525 DS Es V07Documento8 pagineMIT515-MIT525-MIT1025-MIT1525 DS Es V07David PeredoNessuna valutazione finora

- Autenticación y Comprobación de Cuentas de UsuarioDocumento10 pagineAutenticación y Comprobación de Cuentas de UsuarioLuis FloresNessuna valutazione finora

- Rof InpeDocumento22 pagineRof InperadxagielNessuna valutazione finora

- Densidad Del SueloDocumento4 pagineDensidad Del SueloFrankLanceNessuna valutazione finora

- El StoryboardDocumento6 pagineEl Storyboardpepetin1965Nessuna valutazione finora

- InformeDocumento11 pagineInformeVictor Juan Jimenez Flores50% (2)

- Auditoria para No Auditores PDFDocumento1.146 pagineAuditoria para No Auditores PDFlucarrilNessuna valutazione finora

- Historia de OracleDocumento28 pagineHistoria de OracleAnyela De LeonNessuna valutazione finora

- Dispositivos de salida, tipos de impresiones y definición de Word y ExcelDocumento7 pagineDispositivos de salida, tipos de impresiones y definición de Word y ExcelJacqueline Negrita RiveraNessuna valutazione finora

- Sistema BinarioDocumento4 pagineSistema BinarioleidykhNessuna valutazione finora

- Abrir Caja Fuerte Fac MataróDocumento3 pagineAbrir Caja Fuerte Fac MatarójenningsnfnbecbzfcNessuna valutazione finora

- Traductor en Tiempo RealDocumento26 pagineTraductor en Tiempo RealD Jesus MendozaNessuna valutazione finora

- FEL Registro y ConfiguracionDocumento45 pagineFEL Registro y ConfiguracionJesus Emmanuel Perez PallaresNessuna valutazione finora

- Gmail, ProtonMail, ZohoDocumento8 pagineGmail, ProtonMail, ZohoOliver Wod CPNessuna valutazione finora

- Estructuras No LinealesDocumento42 pagineEstructuras No LinealesBenjamin Bautista MejiaNessuna valutazione finora

- 1-Encriptacion de DatosDocumento30 pagine1-Encriptacion de DatosFifufa MarquezNessuna valutazione finora

- Ejercicios Adobe InDesign Cap 1Documento9 pagineEjercicios Adobe InDesign Cap 1Alba Gomez SierrasNessuna valutazione finora

- KOMPLETE AUDIO 6 Manual Spanish PDFDocumento60 pagineKOMPLETE AUDIO 6 Manual Spanish PDFAnonymous JWrxeO2xNessuna valutazione finora

- Sistema de Ecuaciones LinealesDocumento6 pagineSistema de Ecuaciones LinealesSegundo Rodriguez TacillaNessuna valutazione finora

- Act 4 Metodo NumericoDocumento10 pagineAct 4 Metodo NumericoAxela HernandezNessuna valutazione finora

- Operaciones Con RadicalesDocumento7 pagineOperaciones Con RadicalesLamia DominguezNessuna valutazione finora

- IV. Subneteo Con VLSMDocumento53 pagineIV. Subneteo Con VLSMJroNessuna valutazione finora