Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

DVDV II Backend

Caricato da

Parth ShahTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

DVDV II Backend

Caricato da

Parth ShahCopyright:

Formati disponibili

Seat No.: ________ Enrolment No.

______________

GUJARAT TECHNOLOGICAL UNIVERSITY

M.E II

st

SEMESTEREXAMINATION JULY- 2012

Subject code: 725201 Date: 06/07/2012

Subject Name: Digital VLSI Design II-BE

Time: 10:30 am 13:00 pm Total Marks: 70

Instructions:

1. Attempt all questions.

2. Make suitable assumptions wherever necessary.

3. Figures to the right indicate full marks.

Q.1 (a) Draw a diagram that illustrates a standard backend flow from synthesis to GDSII. Make sure you

include testability. How would the flow change?

07

(b) What is the difference between a Wireload model & TLUplus file? When are they used and what is

their importance in IC design

07

Q.2 (a) List all the libraries / files that you use for Physical design & GLS. Write a brief note about each

one of them

07

(b) What are multi-cycle paths, false paths and case-analysis in static timing? 07

OR

(b) In a design that violates setup time constraints, would you recommend option A or option B below?

J ustify?

A. Increase the operating voltage

B. Iterate through backend till timing is met

07

Q.3 (a) What are the steps involved in the Floor planning stage and what is their importance? 07

(b) What is setup & hold time. How do they affect the timing of a digital circuit with any equations? 07

OR

Q.3 (a) A design has been synthesized for 300MHz. However, after place and route, the results of

Primetime indicate that there are timing violations. The WNS is -0.4ns and the TNS is -1.2ns. What

is the frequency that this design can run at now, if we were to ignore this violation and send the

design for fabrication?

07

(b) In a company there is a situation that one chip is timing critical and another chip is area critical.

What are the different optimization steps you suggest in a typical design flow?

07

Q.4 (a) In scan chains, what type of violations is more likely: setup or hold? Why? What would you do to

fix them? What is the avoidance strategy?

07

(b) What is a Milkyway environment? What are the different components of it? 07

OR

Q.4 (a) How do you find the max_transition violations in a design? What is the command? Once the

violations are found, what is the fix?

07

(b) Describe the command import_designs with all the steps executed as a part of it with a simple

example

07

Q.5 (a) Explain the following terms

A. Critical Path B. Congestion C. Scan Chain D. Stuck at Fault

07

(b) Describe the behavior of the circuit for 0111100011 input sequence with timing diagram and derive

any name for the circuit

07

OR

Q.5 (a) Explain the following terms

A.TNS B. WNS C. PVT Conditions D. Clock Uncertainty and J itter

07

(b) What is the difference between a wire delay and cell delay? How do they affect the timing of the

digital circuit?

07

*************

1

Potrebbero piacerti anche

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Fingerprint Attendance System With GSM InterfaceDocumento21 pagineFingerprint Attendance System With GSM InterfaceParth ShahNessuna valutazione finora

- Fingerprint Attendance System With GSM InterfaceDocumento21 pagineFingerprint Attendance System With GSM InterfaceParth ShahNessuna valutazione finora

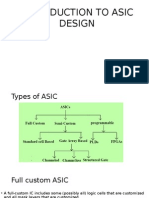

- Different Types of ASICDocumento21 pagineDifferent Types of ASICParth Shah100% (1)

- DSP PaperDocumento3 pagineDSP PaperParth ShahNessuna valutazione finora

- Mini Project - FSMDocumento5 pagineMini Project - FSMParth ShahNessuna valutazione finora

- CathodeDocumento4 pagineCathodeParth ShahNessuna valutazione finora

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Building System Design LabDocumento11 pagineBuilding System Design LabAireuxs AdjarainiNessuna valutazione finora

- Standard Truss Garage PlanDocumento12 pagineStandard Truss Garage PlanCJ10aNessuna valutazione finora

- DFCM - Variable Refrigerant FlowDocumento20 pagineDFCM - Variable Refrigerant FlowGemini HRMNessuna valutazione finora

- Alignment StandardsDocumento6 pagineAlignment StandardsFidelFornolles100% (2)

- Dimensional Measurement PlanningDocumento4 pagineDimensional Measurement PlanningKeith AdminNessuna valutazione finora

- Course Information - Internal: L T U eDocumento105 pagineCourse Information - Internal: L T U eCheerag DuggalNessuna valutazione finora

- Base Plate DesignDocumento6 pagineBase Plate DesignBoris GalindoNessuna valutazione finora

- Curriculum VitaeDocumento2 pagineCurriculum VitaeMahardika NobelNessuna valutazione finora

- Charles W. Barbrey: Cbarbre@clemson - EduDocumento2 pagineCharles W. Barbrey: Cbarbre@clemson - EduChase BarbreyNessuna valutazione finora

- Technical Solutions Engineer Internship - JDDocumento2 pagineTechnical Solutions Engineer Internship - JDRishi RusiaNessuna valutazione finora

- PosterDocumento1 paginaPosterPravin KenNessuna valutazione finora

- Verilog CodeDocumento60 pagineVerilog CodePriyanka JainNessuna valutazione finora

- PIP STE05121 Anchor Bolt Design Guide PDFDocumento56 paginePIP STE05121 Anchor Bolt Design Guide PDFjamilNessuna valutazione finora

- Syllabus 73185352Documento147 pagineSyllabus 73185352Gaurav MishraNessuna valutazione finora

- Biomedical Instrumentation Important Question PaperDocumento8 pagineBiomedical Instrumentation Important Question Papersganesan0Nessuna valutazione finora

- Volume 2 Building Works Ss R 2012Documento262 pagineVolume 2 Building Works Ss R 2012bbaplNessuna valutazione finora

- Tech Spec Flow OrificeDocumento63 pagineTech Spec Flow OrificeSHIVAJI CHOUDHURY100% (1)

- Multivector PDFDocumento3 pagineMultivector PDFlee robert olivar0% (1)

- Autodesk Product Keys PDFDocumento1 paginaAutodesk Product Keys PDFnahidNessuna valutazione finora

- FINAL Object Oriented Programming Lab ManualDocumento80 pagineFINAL Object Oriented Programming Lab ManualKartik SaxenaNessuna valutazione finora

- Construction Schedule With S-CurveDocumento23 pagineConstruction Schedule With S-CurveJp Gallardo100% (2)

- Curs Ing Ec - An I - Sem I - 2010Documento76 pagineCurs Ing Ec - An I - Sem I - 2010Cosmin Burcea-BlendeaNessuna valutazione finora

- Risk Assessment of Floating Offshore Wind Turbine Based On Correlation FMEADocumento7 pagineRisk Assessment of Floating Offshore Wind Turbine Based On Correlation FMEA洪琳雅Nessuna valutazione finora

- Quality Assurance Report (Documentation) - WaterDocumento24 pagineQuality Assurance Report (Documentation) - Waterpdmu regionixNessuna valutazione finora

- Gate Iitd Ac in EEKey PHPDocumento2 pagineGate Iitd Ac in EEKey PHPshagun gargNessuna valutazione finora

- Wing WallDocumento6 pagineWing WallHironmoy DashNessuna valutazione finora

- Pages From KERPEN CableDocumento2 paginePages From KERPEN CablerelaxjackNessuna valutazione finora

- 35inch Concrete Median Barrier Cast-In-PlaceDocumento1 pagina35inch Concrete Median Barrier Cast-In-PlaceSudathipTangwongchaiNessuna valutazione finora

- NDT Weld Visual Inspection ProcedureDocumento4 pagineNDT Weld Visual Inspection Procedureg_sancheti100% (2)

- AACE Journal - Cost Engineering Mar - Apr 2023Documento43 pagineAACE Journal - Cost Engineering Mar - Apr 2023sengoNessuna valutazione finora