Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

1

Caricato da

VidyaViharDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

1

Caricato da

VidyaViharCopyright:

Formati disponibili

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO.

2, FEBRUARY 2013

793

Transformerless Inverter With Virtual DC Bus Concept for Cost-Effective Grid-Connected PV Power Systems

Yunjie Gu, Wuhua Li, Member, IEEE, Yi Zhao, Student Member, IEEE, Bo Yang, Chushan Li, Student Member, IEEE, and Xiangning He, Fellow, IEEE

AbstractIn order to eliminate the common-mode (CM) leakage current in the transformerless photovoltaic (PV) systems, the concept of the virtual dc bus is proposed in this paper. By connecting the grid neutral line directly to the negative pole of the dc bus, the stray capacitance between the PV panels and the ground is bypassed. As a result, the CM ground leakage current can be suppressed completely. Meanwhile, the virtual dc bus is created to provide the negative voltage level for the negative ac grid current generation. Consequently, the required dc bus voltage is still the same as that of the full-bridge inverter. Based on this concept, a novel transformerless inverter topology is derived, in which the virtual dc bus is realized with the switched capacitor technology. It consists of only ve power switches, two capacitors, and a single lter inductor. Therefore, the power electronics cost can be curtailed. This advanced topology can be modulated with the unipolar sinusoidal pulse width modulation (SPWM) and the double frequency SPWM to reduce the output current ripple. As a result, a smaller lter inductor can be used to reduce the size and magnetic losses. The advantageous circuit performances of the proposed transformerless topology are analyzed in detail, with the results veried by a 500-W prototype. Index TermsCommon mode (CM) current, photovoltaic (PV) system, switched capacitor, transformerless inverter, unipolar sinusoidal pulse width modulation (SPWM), virtual dc bus.

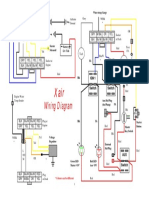

Fig. 1.

CM current path for the transformerless PV inverter.

Fig. 2.

Equivalent circuit for the CM current path.

I. INTRODUCTION

HE distributed photovoltaic (PV) power generation systems have received increasing popularity in both the commercial and residential areas [1][3]. In most occasions, the inverters are used to feed the PV power into the utility grid. It is important for the PV inverter to be of high efciency, due to the relatively high price of the PV panels [4], [5]. Small size is also strongly desired for the low-power and single-phase systems, especially when the inverters are installed indoor.

Manuscript received February 13, 2012; revised April 19, 2012; accepted May 24, 2012. Date of current version September 27, 2012. This work was supported in part by the National Nature Science Foundation of China (50907058), in part by the National Basic Research Program of China (973) (2012CB215106), in part by the Zhejiang Province Science and Technology Program (2011C21056), and in part by the Fundamental Research Funds for the Central Universities (2011QNA4011). Recommended for publication by Associate Editor Henry S. H. Chung. The authors are with the College of Electrical Engineering, Zhejiang University, Hangzhou 310027, China (e-mail: dmonkey@zju.edu.cn; woohualee@zju.edu.cn; diabloturen@zju.edu.cn; yangbo@zju.edu.cn; lcswws@zju.edu.cn; hxn@zju.edu.cn). Color versions of one or more of the gures in this paper are available online at http://ieeexplore.ieee.org. Digital Object Identier 10.1109/TPEL.2012.2203612

In the traditional grid-connected PV inverters, either a linefrequency or a high-frequency transformer is utilized to provide a galvanic isolation between the grid and the PV panels. Removing the isolation transformer can be an effective solution to increase the efciency and reduce the size and cost [6]. However, if the transformer is omitted, the common-mode (CM) ground leakage current may appear on the parasitic capacitor between the PV panels and the ground [7], [8]. The existence of the CM current may reduce the power conversion efciency, increase the grid current distortion, deteriorate the electric magnetic compatibility, and more importantly, give rise to the safety threats [9]. The CM current path in the grid-connected transformerless PV inverter system is illustrated in Fig. 1. It is formed by the power switches, lters, ground impedance ZG , and the parasitic capacitance CPV between the PV panels and the ground. According to [10], the CM current path is equivalent to an LC resonant circuit in series with the CM voltage, as shown in Fig. 2. The CM voltage vCM is dened by vCM = vAO + vBO L2 L1 + (vAO vBO ) 2 2(L1 + L2 ) (1)

where vAO is the voltage difference between points A and O, vBO is the voltage difference between points B and O, and L1 and L2 are the output lter inductors.

0885-8993/$31.00 2012 IEEE

794

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO. 2, FEBRUARY 2013

If the switching action of the inverter generates highfrequency CM voltage, the CM current iCM may be exited on the LC circuit. From this point of view, the topology and modulation strategy adopted for the transformerless PV power system should guarantee that vCM is constant or only varies at low frequency, such as 50 Hz/60 Hz line frequency. A simple way to realize this goal is to use the full-bridge inverter with the bipolar sinusoidal pulse width modulation (SPWM), of which the CM voltage is xed at half the dc bus voltage. Comparing with the bipolar SPWM, the unipolar SPWM has better performance in terms of the output current ripple and switching losses, but cannot be directly used for the full-bridge inverter in the transformerless application, because it generates the switching frequency CM voltage. For this reason, some state-of-the-art topologies, such as the H5 inverter, the HERIC inverter, etc., have been developed based on the full-bridge inverter, to keep vCM constant when the unipolar modulation is used [11][16]. Some of these topologies are exhibited in Fig. 3. By inserting extra switches into the fullbridge inverter either on the dc or ac side, the dc bus can be disconnected from the grid when the inverter output voltage is at zero voltage level, so that the CM current path is cut off. Such solutions need two lter inductors with independent iron cores, which may lead to a rise in the size and cost. Moreover, the dc and ac sides cannot be perfectly disconnected by the power switch because of the switch parasitic capacitance, so the CM current may still exist [10]. Another kind of solution is to use the half-bridge inverter with the grid neutral line directly connected to the midpoint of the dc bus, as shown in Fig. 4. In this way, the voltage across the parasitic capacitor is clamped to be constant by the dc bus capacitor. However, this method has an important disadvantage that the required dc bus voltage should be doubled compared with the full-bridge topologies. For the 220 Vac system, it can be as high as 700 V. Although the three-level neutral point clamped (NPC) circuit can help improve the performance of the half-bridge inverter, the dc bus voltage is still high [17], [18]. Besides the aforementioned classic circuits, there are other topologies proposed in recent literature works, some of which are listed in Fig. 5. The Karschny inverter [19] and the paralleledbuck inverter [20] are derived from the buckboost and buck circuits, respectively. These solutions have high reliability, but are not capable of supplying the reactive power to the grid. The inverter proposed in [21] employs a capacitor voltage divider to keep the CM voltage constant, but is regarded to be of higher conduction losses. In this paper, a novel topology generation strategy called the virtual dc bus concept is proposed for the transformerless gridconnected PV inverter. In this solution, the grid neutral line is connected directly to the negative pole of the dc bus, so that the voltage across the parasitic capacitor is clamped to zero. As a result, the CM current is eliminated completely. Meanwhile, the virtual dc bus is created to help generate the negative output voltage. The required dc bus voltage is still the same as the full-bridge, and there is not any limitation on the modulation strategy since the CM current is removed naturally by the circuit

Fig. 3. Full-bridge-based topologies for the transformerless inverter: (a) H5 circuit [11]; (b) HERIC circuit [12]; (c) H6 circuit with ac bypass [13]; (d) H6 circuit with dc bypass [15].

structure. In this way, the advantages of the full-bridge- and halfbridge-based solutions are combined together. Based on the aforementioned innovative idea, a novel inverter topology is proposed with the virtual dc bus concept by employing the switched capacitor technology. The proposed inverter can be modulated with the unipolar SPWM and double frequency SPWM. It consists of only ve power switches and a single lter inductor, so the cost of the semiconductor and magnetic components can be reduced. This paper is organized as follows. The virtual dc bus concept is explained in Section II. Based on it, a novel inverter topology

GU et al.: TRANSFORMERLESS INVERTER WITH VIRTUAL DC BUS CONCEPT FOR COST-EFFECTIVE GRID-CONNECTED PV POWER SYSTEMS

795

Fig. 4. Half-bridge-based topologies. (a) Conventional half-bridge inverter. (b) NPC half-bridge inverter.

with the switched capacitor is derived in Section III, and the modulation strategy and operation principle are described in detail. The current stress caused by the operation of the switched capacitor is analyzed in Section IV. The circuit performance is evaluated in Section V. The experimental results of a 500-W prototype with 20 kHz switching frequency are given in Section VI to verify the analysis. A summary is given in the nal section. II. VIRTUAL DC BUS CONCEPT The concept of the virtual dc bus is depicted in Fig. 6. By connecting the grid neutral line directly to the negative pole of the PV panel, the voltage across the parasitic capacitance CPV is clamped to zero. This prevents any leakage current owing through it. With respect to the ground point N, the voltage at midpoint B is either zero or +Vdc , according to the state of the switch bridge. The purpose of introducing the virtual dc bus is to generate the negative output voltage, which is necessary for the operation of the inverter. If a proper method is designed to transfer the energy between the real bus and the virtual bus, the voltage across the virtual bus can be kept the same as the real one. As shown in Fig. 6, the positive pole of the virtual bus is connected to the ground point N, so that the voltage at the midpoint C is either zero or Vdc . The dotted line in the gure indicates that this connection may be realized directly by a wire or indirectly by a

Fig. 5. Other transformerless inverter topologies: (a) Karschny inverter [19]; (b) paralleled-buck inverter [20]; (c) H6 inverter with capacitor voltage divider [21].

power switch. With points B and C joined together by a smart selecting switch, the voltage at point A can be of three different voltage levels, namely +Vdc , zero, and Vdc . Since the CM current is eliminated naturally by the structure of the circuit, there is not any limitation on the modulation strategy, which means that the advanced modulation technologies such as the unipolar SPWM or the double-frequency SPWM can be used to satisfy various PV applications. III. DERIVED TOPOLOGY AND MODULATION STRATEGY Based on the virtual dc bus concept, a novel inverter topology is derived as an example to show the clear advantages of the proposed methodology, which is shown in Fig. 7. It consists of ve power switches S1 S5 and only one single lter inductor Lf . The PV panels and capacitor C1 form the real dc bus while the virtual dc bus is provided by C2 . With the switched capacitor technology, C2 is charged by the real dc bus through S1 and S3 to maintain a constant voltage. This topology can be modulated with the unipolar SPWM and double-frequency SPWM. The detailed analysis is introduced as follows.

796

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO. 2, FEBRUARY 2013

Fig. 6.

Virtual dc bus concept.

Fig. 9.

Double-frequency SPWM for the proposed topology.

Fig. 7.

Proposed topology.

half grid cycle, ug > 0. S1 and S3 are turned ON and S2 is turned OFF, while S4 and S5 commutate complementally with the carrier frequency. The capacitors C1 and C2 are in parallel and the circuit rotates between states 1 and 2 as shown in Fig. 10. During the negative half cycle, ug < 0. S5 is turned ON and S4 is turned OFF. S1 and S3 commutate with the carrier frequency synchronously and S2 commutates in complement to them. The circuit rotates between states 3 and 2. At state 3, S1 and S3 are turned OFF while S2 is turned ON. The negative voltage is generated by the virtual dc bus C2 and the inverter output is at negative voltage level. At state 2, S1 and S3 are turned ON while S2 is turned OFF. The inverter output voltage vAN equals zero; meanwhile, C2 is charged by the dc bus through S1 and S3 . B. Double-Frequency SPWM The proposed topology can also work with double-frequency SPWM to achieve a higher equivalent switching frequency, as shown in Fig. 9. In the double-frequency SPWM, the ve power switches are separated into two parts, and are modulated with two inverse sinusoidal waves respectively. S1 , S2 , and S3 are modulated with ug1 , while S4 and S5 are modulated with ug2 . During the positive half grid cycle, the circuit rotates in the sequence of state 4 state 1 state 2 state 1, and the output voltage vAN varies between +Vdc and the zero with twice of the carrier frequency. During the negative half grid cycle, the circuit rotates in the sequence of state 4 state 3 state 2 state 3, and the output voltage vAN varies between Vdc and zero. The aforementioned two modulation strategies both have their own advantages. The double-frequency SPWM can provide a higher equivalent switching frequency so that the size and weight of the lter inductor can be reduced. On the other hand, the unipolar SPWM can guarantee that the virtual dc bus C2 is charged by the real bus every switching cycle, so that the

Fig. 8.

Unipolar SPWM for the proposed topology.

A. Unipolar SPWM The waveform for the unipolar SPWM of the proposed inverter is displayed in Fig. 8. The gate drive signals for the power switches are generated according to the relative value of the modulation wave ug and the carrier wave uc . During the positive

GU et al.: TRANSFORMERLESS INVERTER WITH VIRTUAL DC BUS CONCEPT FOR COST-EFFECTIVE GRID-CONNECTED PV POWER SYSTEMS

797

Fig. 11.

Equivalent circuits for states 2 and 3: (a) state 2; (b) state 3.

For all of the four operation states, there is no limitation on the direction of the output current igrid , since the power switches with antiparallel diodes can achieve bidirectional current ow. Therefore, the proposed topology has the capability of feeding reactive power into the grid to help support the stability of the power system. The proposed topology is also immune against transient overvoltage of the grid. During the mains positive voltage spikes, the voltage at point A is clamped at Vdc by C1 and the antiparallel diodes of S1 and S4 . Similarly, during the negative voltage spikes, the voltage at point A is clamped at Vdc by C2 and the antiparallel diodes of S2 and S5 . Therefore, the mains transient overvoltage does not pose a safety threat for the inverter. IV. CURRENT STRESS ANALYSIS One important characteristic of the proposed topology is the utilization of the switched capacitor technology. The operation of the switched capacitor may exert some extra current stress on the power switches, which reduces the efciency and increases the current stress on the devices. It is necessary to limit this current to an acceptable value to ensure the reliability of the inverter. In this section, the current stress is analyzed quantitatively with design guidelines provided. The analysis below is based on the unipolar SPWM and unit output power factor. A. Current Stress Calculation

Fig. 10. Four operation states for the proposed topology: (a) state 1; (b) state 2; (c) state 3; (d) state 4.

current stress on S1 and S3 caused by the operation of the switched capacitor can be reduced. In this paper, the unipolar SPWM is chosen as an example for the performance evaluation and experimental verication.

During the negative half cycle, the circuit switches between states 2 and 3. At state 3, C1 is charged by the PV panels, while C2 is discharged by the grid current. As a result, the voltage difference between them increases. When the circuit switches to state 2, C2 is charged by C1 through S1 and S3 so that the voltage difference decreases. The equivalent circuits of states 2 and 3 are displayed in Fig. 11, in which the power switch is modeled as a resistor in series with a constant voltage drop, the capacitor is regarded as

798

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO. 2, FEBRUARY 2013

an ideal capacitor in series with a resistor, and the PV panel is taken as a current source. Since the inverter is controlled in the current source mode, the output inductor Lf can also be regarded as a current source. The reference direction of the current and voltage is marked in the gure for convince in analysis. It can be concluded that the extra current on S1 and S3 is caused by the voltage difference of C1 and C2 . Dening a new variable v = vC 1 vC 2 2Von , the state equation for states 2 and 3 can be derived separately state 2 : v igrid RS3 IPV IPV RC 1 dv = + dt R CS R CS C1 R CS (2) state 3 : in which R = RS1 + RS3 + RC 1 + RC 2 CS = C1 C2 C1 + C2 (4) (5) IPV dv igrid = dt C1 C2 (3)

Equations (2) and (3) can be combined into a single equation as v igrid RS3 IPV IPV RC 1 dv = (1 + s(t)) + dt R CS R CS C1 R CS s(t) IPV igrid C1 C2 (6)

Fig. 12. Comparison of theoretical and simulated results: (a) voltage difference v; (b) current through S3 iS 3 , and output current ig rid .

where s(t) is the switch function which is in relevant to the circuit state 1, when the circuit is at state 1 s(t) = 0, when the circuit is at state 2 (7) 1, when the circuit is at state 3. With the classical switching cycle averaging method, (6) can be linearized and rearranged into the following form: d v dt

TS

If v T s is solved from (8) and (11), the average value of the current stress can then be expressed as the function of v T s iS1 iS3

T2

= =

v v

TS

+ igrid + igrid

T S RS3

+ IPV RC 1 igrid

R

TS TS

(12)

TS

RS3 + IPV RC 1

T2

(13) in which iS1 T 2 and iS3 T 2 are the average values of iS1 and iS3 at stage 2. To verify the validity of the aforementioned theoretical analysis, a simulation model is built with Saber software, and the results are compared in Fig. 12. The system conguration and parameters for the simulation are the same as those used in the experimental prototype. The analytical and simulated results provide some insights into the characteristics of the current stress caused by the switched capacitor. It can be seen that the current stress and the voltage difference v vary in synchronous with the grid current igrid . The maximum value comes at the time when igrid reaches its negative peak. B. Switched Capacitor Optimization The goal of the optimization is to limit the maximum current stress on the power switches to guarantee an adequate safety margin. As pointed out previously, the maximum current

TS

(1 + d(t)) IPV igrid T S d(t) = + R CS C1 C2 (8)

RS3 igrid T S (1 + d(t)) RC 1 IPV (1 + d(t)) R CS R CS

Ts

in which TS is the switching cycle, x(t)

TS

is the averaging operator x(t)dt (9)

1 TS

t+ TS t

and d(t) is the generalized duty cycle d(t) = s(t)

TS

(10)

Neglecting the phase shift caused by the lter inductor, d(t) and igrid can be described as two synchronous sinusoidal waves d(t) = Dm sin(t), igrid (t)

TS

= Im sin(t)

(11)

in which is the grid angle frequency, Dm is the maximum duty cycle, and Im is the amplitude of the output current.

GU et al.: TRANSFORMERLESS INVERTER WITH VIRTUAL DC BUS CONCEPT FOR COST-EFFECTIVE GRID-CONNECTED PV POWER SYSTEMS

799

stress comes at the negative peak value of igrid . At this time, d v T s /dt = 0, igrid T s = Im , and d(t) = Dm , and the current stress is iS1 iS3

T 2 m ax T 2 m ax

analysis is based on the unipolar SPWM and unit output power factor. A. Conduction Losses in the Power Devices

1 2

C1 +1 C1 + C2

T 2 m ax

Dm Im 1 Dm

(14) (15)

= iS1

+ Im .

It can be seen from (14) that the maximum current stress is affected by three parameters, namely Dm , Im , and the ratio of C1 /(C1 +C2 ). Im is determined by the power rating of the inverter, while Dm is set by the ratio of the grid voltage and the dc bus voltage. The only parameter which could be leveraged by the designer is C1 /(C1 +C2 ). Equation (14) indicates that the ratio of C1 /(C1 +C2 ) should be as small as possible to minimize the current stress. However, it should be noticed that (14) is the average value neglecting the ripple current. The real value is the sum of the average and the ripple value iS n m ax = iS n

T 2 m ax

+ iS n ,

n = 1,3.

(16)

During the positive half cycle, the proposed inverter works just like the unipolar modulated full-bridge inverter. At state 1, the output current igrid ows through S1 and S4 ; at state 2, igrid ows through S3 and S5 . There are always two switches on the path of igrid . During the negative half cycle, however, the situation is different. On one hand, there are still two switches on the path of igrid . On the other hand, the charging of the switched capacitor C2 gives rise to some extra current on S1 and S3 . This charging current causes some extra conduction losses. If the bipolar devices, such as insulated gate bipolar transistors (IGBT) and diodes, are used as the power switches, the conduction voltage drop Von is not signicantly affected by the conduction current, and therefore can be treated as a constant value in the conduction losses estimation. Based on this approximation, the average conduction losses in a power switch in a grid cycle can be derived as Von 0 |ion (t)|dt |Von ion (t)| dt Von Q = = (21) T T T in which T is the grid period, ion is the current through the power switch, and Q is the absolute value of the charge owing through the switch in a grid cycle. From (21), it can be seen that the average losses in a power switch are proportional to the charge it transported. In light of this, the extra losses pext are determined by the extra charge owing through the power switch, caused by the capacitor charging. Because the voltage of C2 keeps in balance in a grid cycle, the extra charge Qext is equal to the charge taken away from C2 by igrid : pon =

T T 0 T

According to the equivalent circuit shown in Fig. 11, iS1 , 3 can be derived as iS1 = iS3 = TS (1 + d(t)) iS1 R CS 2 TS 1 Dm iS1 R CS 2

T2 .

(17)

Hence, the real maximum value of the current stress is iS1 m ax = iS1

T 2 m ax

T 2 m ax

(18) (19)

iS3 m ax = iS1 m ax + Im .

In light of (18), R CS should be as large as possible to limit the ripple current. As the increase of R results in larger conduction losses, the reasonable approach is to increase CS = C1 C2 /(C1 +C2 ). It is easy to see that this is in contrast to the aforementioned strategy of reducing C1 /(C1 +C2 ). As a tradeoff, the principles below can be utilized for circuit design in choosing the value of the switched capacitors R CS > TS , C1 < C2 . (20)

Qext =

T /2

s(t)igrid (t) dt

(22)

R CS >TS guarantees that the time constant of the switched capacitor is larger than the switching period, so that iS1 , 3 is only a small part of iS1 , 3 . It is better for C1 to be smaller than C2 to reduce C1 /(C1 +C2 ). In the experimental verication below, the ratio of C1 /(C1 +C2 ) is set to be 1/3, and iS1m ax and iS3m ax are approximately 3Im and 4Im , respectively. The maximum current stress appears on S3 , and its peak to average current ratio is about 3.47 according to the simulation results. V. PERFORMANCE ANALYSIS In this section, the performances of the proposed circuit are analyzed in detail, including the losses distribution, the output voltage characteristics, and the CM current elimination capability. Since the H5 circuit is taken as one of the best solutions for the transformerless PV inverters, the fair performance comparison between the proposed inverter and the H5 inverter is made to explore the clear advantages of the proposed solution. The

where igrid (t) is the output current and s(t) is the switch function dened in (7). The integration limits from T/2 to T represent the negative half cycle. As igrid is almost unchanged in a single switching cycle, the switching cycle averaging method can be utilized to simplify the calculation

T

Qext =

T /2 T

s(t)igrid (t) dt d(t) igrid (t) dt.

s(t)

T /2

TS

igrid (t)

TS

dt (23)

=

T /2

TS

Substituting (11) into (23), Qext can be derived by

T

Qext =

T /2

|Dm sin(t)Im sin(t)| dt =

Im Dm T . 4

(24)

Since Qext ows through two switches, namely S1 and S3 , the extra losses can be expressed as pext = 1 2Von Qext = Von Im Dm . T 2 (25)

800

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO. 2, FEBRUARY 2013

The conduction losses of the conventional full-bridge inverter are 4 pfb = Von Im . (26) The total conduction losses of the proposed converter are the combination of (25) and (26) 4 1 Von Im + Von Im Dm . (27) 2 For the 220 Vac power system with 400 V dc bus voltage, Dm is equal to 0.78, and the conduction losses of the proposed topology increase about 30% compared with the full-bridge inverter. Similar analysis can be done for the H5 topology. The additional power switch inserted on the dc side, which is S5 in Fig. 3(a), also causes extra losses. The analytical expression for the conduction losses in S5 is pprop = pS5 = Von T Von T

T 0 T 0

In the experimental prototype, the aluminum electrolyte capacitors are used for C1 and C2 . With a typical dissipation factor of 0.15, the theoretical estimation of pswcap is equal to 1.6 W at full load, while the losses caused by the intrinsic ripple current are only 0.7 W. One way to deal with this issue is to use larger capacitors. In the experimental prototype, the total capacitance used for the proposed topology is two times greater than that of the H5 circuit. Also, a small 10 F thin lm capacitor is connected in parallel with the aluminum electrolyte one to absorb the high-frequency pulsating current. This helps alleviate the ESR losses in the capacitor as well.

C. Switching Losses During the positive half cycle, only two switches, namely S4 and S5 , commutate at the carrier frequency, so the switching losses are the same as the traditional full-bridge inverter. During the negative half cycle, S1 , S2 , and S3 commutate at the carrier frequency. Although the number of high-frequency switches increases to 3, it can be seen from the following analysis that the switching losses almost keep the same. For convenience of description, the power transistor and the antiparallel diode for the switch Sn is denoted as Tn and Dn respectively, where n = 1, 2, . . . , 5. At state 2, T1 , T3 , and T5 are turned ON, while the current actually ows through T1 , D3 , and T5 , as shown in Fig. 13(a). When the circuit switches from state 2 to state 3, T1 and T3 are turned OFF rst before T2 is turned ON due to the effect of the dead time. As a result, there will be a transition state between the two states, as shown in Fig. 13(c). During this transition state, the inductor Lf freewheels through D3 , so the voltage across T1 and T3 may not rise immediately after turned OFF, so that the switching losses can be neglected. When the dead time is passed, T2 is turned ON. The inductor current is forced to commutate from D3 to T2 , and the circuit changes into state 3. When the circuit rotates from state 3 to state 2, it also enters the transition state rst. Because of the dead time, T2 is turned OFF while T1 and T3 are not turned ON yet, and the inductor current is forced to commutate from T2 to D3 . After D3 is conducting, the voltage across S1 and S3 reduces to zero approximately. Therefore, when T1 and T3 are turned ON after the transition state, they will not suffer signicant switching losses. In summary, only T2 and D3 operate in the forced commutation mode during the negative half cycle, and the voltage and current commutated are Vdc and igrid , respectively. Therefore, the operation of the switched capacitor does not cause the increase in switching losses. The number of forced commutations for the diodes and transistors in a single switching cycle is summarized in Table I. Similar analysis can be performed on the H5 circuit as well, and the result is listed in Table II. It can be seen that the number of forced commutation for the transistors is doubled for the H5 circuit, while the commutation voltage reduces to Vdc /2, so the resultant switching losses can be assumed to be at the same level.

|s(t)igrid (t)| dt (28)

1 |Dm sin(t)Im sin(t)| dt = Von Im Dm 2

in which s(t) is the switch function for the H5 circuit 1, when the H5 output voltage is + Vdc s(t) = 0, when the H5 output voltage is 0 (29) 1, when the H5 output voltage is Vdc . It can be seen that pS5 takes the same form as pext of the proposed circuit, so the conduction losses in the power devices are the same. It should be pointed out that the aforementioned calculation is based on the assumption that Von does not change with ion . However, for the proposed topology, the currents on S1 and S3 will increase signicantly due to the switched capacitor, so the real conduction losses are slightly larger than the theoretical value. B. Conduction Losses in Switched Capacitors The operation of the switched capacitor also increases the conduction losses in the capacitor due to its equivalent series resistance (ESR). The ESR losses are evaluated to give further guidelines on the capacitor design. For the proposed topology, the conduction losses in ESR can be divided into two parts. The rst part is caused by the ripple current which is intrinsic to all voltage source inverters, including the traditional full-bridge and half-bridge circuits and the newly developed topologies such as H5, HERIC, etc. The second part is caused by the inrush current during the charging of the switched capacitors. These additional losses only occur at state 2 in the negative half cycle, and their value can be calculated by pswcap = 1 (RC 1 + RC 2 ) T

T

(1 + s(t))i2 S 1 (t)dt

T /2

(30)

in which s(t) is the switch function dened in (7).

GU et al.: TRANSFORMERLESS INVERTER WITH VIRTUAL DC BUS CONCEPT FOR COST-EFFECTIVE GRID-CONNECTED PV POWER SYSTEMS

801

D. Losses in the Filter Inductor Under the same switching frequency, the output voltage waveforms of the proposed circuit and the H5 circuit are identical to each other. This results in similar output current ripple and magnetic losses, if the same lter inductor congurations are used. Nevertheless, the H5 circuit has to employ two inductors with separated iron cores, while the proposed circuit only needs one. This may lead to a reduction in the size of the iron core, although the total inductor value is still the same.

E. CM Current Elimination As explained previously, the key point for the full-bridgebased solutions, including H5 and HERIC, is to insert extra switches into the traditional full-bridge inverter to disconnect the line side with the dc side, when the inverter output voltage is at zero voltage level. Unfortunately, this disconnection is incomplete because of the parasitic capacitance on the power switches. As a result, high-frequency CM current may still ow through these capacitors. Therefore, it is necessary to add extra lters into these topologies to absorb this CM current [21][23]. As for the proposed topology, the stray capacitance between the PV panels and the ground is directly bypassed. Due to the conguration of the virtual dc bus, the CM current is eliminated completely. In conclusion, the conduction and switching losses in the power devices of the proposed topology are quite similar to those of the H5 circuit. The main drawback is that larger capacitors are needed to reduce the ESR losses in the capacitor and ensure their life time. This issue can be alleviated by adding a thin lm capacitor in parallel to the aluminum electrolyte one to absorb the high-frequency pulsating current. Fortunately, the clear advantage of the proposed topology is that it has better performance in eliminating the CM current. The solution with virtual dc bus concept provides a new idea for developing the transformerless inverter for the PV applications.

Fig. 13. Current path during commutation: (a) state 2; (b) state 3; (c) transition state between 2 and 3.

VI. EXPERIMENTAL VERIFICATION A 500-W prototype is built to verify the functionality of the proposed topology and the idea of the virtual dc bus concept. The terminal voltage for a 500-W PV panel is typically 4060 V. The high step-up converter proposed in [24] can be used to acquire the 400 V dc bus. Since the input and output terminals of the stepup converter share a common ground, the grid neutral line is still connected to the negative pole of the PV panel. Therefore, the front-end high step-up converter does not affect the elimination of the CM current for the proposed topology. The LCL lter is used to reduce the output current ripple, as shown in Fig. 14. The detailed conguration and parameters are listed in Table III. The picture for the prototype is depicted in Fig. 15. The experimental waveform of output current and grid voltage is displayed in Fig. 16. The current THD is 2.1% and the power factor is over 0.99. The current harmonic distribution is shown in Fig. 17. The output current well meets the standards in IEEE 519.

TABLE I SUMMARY OF FORCED COMMUTATIONS FOR THE PROPOSED TOPOLOGY

TABLE II SUMMARY OF FORCED COMMUTATIONS FOR THE H5 CIRCUIT

802

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO. 2, FEBRUARY 2013

Fig. 17. Fig. 14. LCL lter used in prototype.

Current harmonics distribution.

TABLE III PROTOTYPE CONFIGURATIONS

Fig. 18.

Simulation waveform for reactive power generation.

Fig. 19.

Current stress on S3 .

Fig. 15.

Picture for the laboratory prototype.

Fig. 16.

Output current and grid voltage.

Since the voltage across C2 is not completely symmetrical during the positive and negative half cycle for the proposed topology, the dc current elimination algorism is required to limit the dc current injected into the grid. The measured dc bias of igrid is below 10 mA for the prototype, which is less than 0.5% of the rated output current. This is in accordance with the IEEE 1547 standard for interconnecting distributed resources with the power system. To verify the reactive power capability of the proposed circuit, a simulation waveform is exhibited in Fig. 18, in which the power factor is set at 0.94. With this characteristic, the proposed circuit is able to adjust the reactive power to help regulate the grid voltage. The current stress on S3 is shown in Fig. 19. The extra current stress only appears in the negative half cycle and the peak current on S3 is approximately 4Im . This is in accordance with

GU et al.: TRANSFORMERLESS INVERTER WITH VIRTUAL DC BUS CONCEPT FOR COST-EFFECTIVE GRID-CONNECTED PV POWER SYSTEMS

803

Fig. 20.

Enlarged gure for current stress on S3 .

Fig. 21.

CM current of H5 circuit.

Fig. 22. Current stress under different capacitor ratios for the proposed circuit: (a) C1 /C2 = 1/2; (b) C1 /C2 = 2/1.

the theoretical and simulation result in Section IV. The partial enlargement look of Fig. 19 is provided in Fig. 20. One important advantage for the proposed topology with virtual dc bus is the complete elimination of CM current. As mentioned in Section V, for the full-bridge-based topologies, high-frequency CM current may still exist due to the parasitic capacitances on the power switches. To verify this, a prototype of the H5 inverter is also built with the same conguration as Table III. The capacitance between the PV panels and the ground CPV is emulated with a thin lm capacitor of 75 nF. Fig. 21 gives the CM current and the voltage on S5 of the H5 prototype. It is clear to see that the parasitic capacitance on the power switches is in resonant with the equivalent CM inductor [10]. The resonance frequency is about 100 kHz and the peakpeak value of iCM can be as high as 50 mA for the 500-W prototype. Although this CM current value may be reduced by using different power switches and parameters, the potential risk always exists. Therefore, it is necessary to add extra lters to deal with this problem. By contrast, in the proposed solution, CPV is directly bypassed by connecting the neutral line to the negative pole of the dc bus, so the CM current is zero in theory. This conclusion is conrmed by the experimental result, in which no observable CM current is detected. The current stress on S3 under different capacitor ratios is compared in Fig. 22. The sum of C1 + C2 is xed, while the ratio of C1 /C2 is changed to verify the analysis in (20). It is better for C1 to be smaller than C2 for reduction of the current stress. The efciency of the proposed topology is compared with other solutions under the same condition, as shown in Fig. 23.

Fig. 23.

Efciency Comparison.

The experiments are done with the same electrical parameters and components, which are listed in Table III. The only difference is the topology and modulation strategy. The result indicates that the proposed circuit has smaller power losses than the bipolar SPWM modulated full-bridge inverter, mainly because of the reduction in magnetic and switching losses. There is no signicant difference between H5 and the proposed topology. It is explained in Section V that the conduction and switching losses on the semiconductor devices are quite similar for the two circuits. The total capacitance used for the proposed topology is enlarged to compensate for the extra ESR losses caused by the switched capacitor. VII. CONCLUSION The concept of the virtual dc bus is proposed to solve the CM current problem for the transformerless grid-connected PV

804

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 28, NO. 2, FEBRUARY 2013

inverter. By connecting the negative pole of the dc bus directly to the grid neutral line, the voltage on the stray PV capacitor is clamped to zero. This eliminates the CM current completely. Meanwhile, a virtual dc bus is created to provide the negative voltage level. The required dc voltage is only half of the halfbridge solution, while the performance in eliminating the CM current is better than the full-bridge-based inverters. Based on this idea, a novel inverter topology is proposed with the virtual dc bus concept by adopting the switched capacitor technology. It consists of only ve power switches and a single lter inductor. The proposed topology is especially suitable for the small-power single-phase applications, where the output current is relatively small so that the extra current stress caused by the switched capacitor does not cause serious reliability problem for the power devices and capacitors. With excellent performance in eliminating the CM current, the virtual dc bus concept provides a promising solution for the transformerless grid-connected PV inverters. REFERENCES

[1] J. P. Benner and L. Kazmerski, Photovoltaics gaining greater visibility, IEEE Spectr., vol. 36, no. 9, pp. 3442, Sep. 1999. [2] Z. Zhao, M. Xu, Q. Chen, J.-S. Lai, and Y. Cho, Derivation of boost-buck converter based high-efciency robust PV inverter, in Proc. IEEE Energy Convers. Cong. Expos., Sep. 1216, 2010, pp. 14791484. [3] R. W. Erickson and A. P. Rogers, A microinverter for building-integrated photovoltaics, in Proc. 24th Annu. IEEE Appl. Power Electron. Conf. Expos., Feb. 1519, 2009, pp. 911917. [4] S. B. Kjaer, J. K. Pedersen, and F. Blaabjerg, A review of single-phase grid-connected inverters for photovoltaic modules, IEEE Trans. Ind. Appl., vol. 41, no. 5, pp. 12921306, Sep./Oct. 2005. [5] E. Koutroulis and F. Blaabjerg, Design optimization of grid-connected PV inverters, in Proc. 26th Annu. IEEE Appl. Power Electron. Conf. Expos., Mar. 611, 2011, pp. 691698. [6] T. Kerekes, R. Teodorescu, P. Rodr guez, G. V azquez, and E. Aldabas, A new high-efciency single-phase transformerless PV inverter topology, IEEE Trans. Ind. Electron., vol. 58, no. 1, pp. 184191, Jan. 2011. [7] O. Lopez, F. D. Freijedo, A. G. Yepes, P. Fernandez-Comesaa, J. Malvar, R. Teodorescu, and J. Doval-Gandoy, Eliminating ground current in a transformerless photovoltaic application, IEEE Trans. Energy Convers., vol. 25, no. 1, pp. 140147, Mar. 2010. [8] E. Gub a, P. Sanchis, A. Urs ua, J. Lopez, and L. Marroyo, Ground currents in single-phase transformerless photovoltaic systems, Prog. Photovolt., Res. Appl., vol. 15, pp. 629650, 2007. [9] S. V. Araujo, P. Zacharias, and B. Sahan, Novel grid-connected nonisolated converters for photovoltaic systems with grounded generator, in Proc. IEEE Power Electron. Spec. Conf., Jun. 1519, 2008, pp. 5865. [10] B. Yang, W. Li, Y. Gu, W. Cui, and X. He, Improved transformerless inverter with common-mode leakage current elimination for a photovoltaic grid-connected power system, IEEE Trans. Power Electron., vol. 27, no. 2, pp. 752762, Feb. 2012. [11] V. Matthias, G. Frank, B. Sven, and H. Uwe, German Patent H5-Topology, DE 102004030912 B3, Jan. 2006. [12] S. Heribert, S. Christoph, and K. Juergen, German Patent HERICTopology, DE 10221592 A1, Apr. 2003. [13] W. Yu, J.-S. Lai, H. Qian, C. Hutchens, J. Zhang, G. Lisi, A. Djabbari, G. Smith, and T. Hegarty, High-efciency inverter with H6-type conguration for photovoltaic non-isolated ac module applications, in Proc. 25th Annu. IEEE Appl. Power Electron. Conf. Expos., Feb. 2125, 2010, pp. 10561061. [14] W. Cui, B. Yang, Y. Zhao, W. Li, and X. He, A novel single-phase transformerless grid-connected inverter, in Proc. 37th Annu. Conf. IEEE Ind. Electron. Soc., Nov. 710, 2011, pp. 11261130. [15] B. Yang, W. Li, Y. Deng, X. He, S. Lambert, and V. Pickert, A novel single-phase transformerless photovoltaic inverter connected to grid, in Proc. 5th IET Int. Conf. Power Electron., Mach. Drives, Apr. 1921, 2010, pp. 16. [16] R. Gonzalez, J. Lopez, P. Sanchis, E. Gubia, A. Ursua, and L. Marroyo, High-efciency transformerless single-phase photovoltaic inverter, in

[17] [18] [19] [20] [21] [22] [23] [24]

Proc. 12th Int. Power Electron. Motion Control Conf., Aug. 30Sep. 1, 2006, pp. 18951900. R. Gonzalez, E. Gubia, J. Lopez, and L. Marroyo, Transformerless singlephase multilevel-based photovoltaic inverter, IEEE Trans. Ind. Electron., vol. 55, no. 7, pp. 26942702, Jul. 2008. H. Xiao and S. Xie, Transformerless split-inductor neutral point clamped three-level PV grid-connected inverter, IEEE Trans. Power Electron., vol. 27, no. 4, pp. 17991808, Apr. 2012. K. Dietrich, German Patent Wechselrichter: DE 19642522 C1, Apr. 1998. S. V. Araujo, P. Zacharias, and R. Mallwitz, Highly efcient single-phase transformerless inverters for grid-connected photovoltaic systems, IEEE Trans. Ind. Electron., vol. 57, no. 9, pp. 31183128, Sep. 2010. D. Barater, G. Franceschini, and E. Lorenzani, Unipolar PWM for transformerless grid-connected converters in photovoltaic plants, in Proc. Int. Conf. Clean Electr. Power, Jun. 911, 2009, pp. 387392. H. Xiao, S. Xie, Y. Chen, and R. Huang, An optimized transformerless photovoltaic grid-connected inverter, IEEE Trans. Ind. Electron., vol. 58, no. 5, pp. 18871895, May 2011. T. Kerekes, R. Teodorescu, P. Rodr guez, G. V azquez, and E. Aldabas, A new high-efciency single-phase transformerless PV inverter topology, IEEE Trans. Ind. Electron., vol. 58, no. 1, pp. 184191, Jan. 2011. Y. Zhao, W. Li, Y. Deng, and X. He, High step-up boost converter with passive lossless clamp circuit for non-isolated high step-up applications, IET Power Electron., vol. 4, no. 8, pp. 851859, Sep. 2011.

Yunjie Gu received the B.Sc. degree in electrical and electronicengineering from Zhejiang University, Hangzhou, China, in 2010, where he is currently working toward the Ph.D. degree in electrical engineering. His research interests include power converters and control of renewable energy power systems.

Wuhua Li (M09) received the B.Sc. and Ph.D. degree in applied power electronics and electrical engineering from Zhejiang University, Hangzhou, China, in 2002 and 2008, respectively. From September 2004 to March 2005, he was an Intern, and from January 2007 to June 2008, a Research Assistant in GE Global Research Center, Shanghai, China. From July 2008 to April 2010, he was with the College of Electrical Engineering, Zhejiang University, as a Postdoctoral Fellow. In May 2010, he became a Lecturer at Zhejiang University. In December 2010, he was promoted as an Associate Professor. From July 2010 to September 2011, he was a Ryerson University Postdoctoral Fellow in the Department of Electrical and Computer Engineering, Ryerson University, Toronto, ON, Canada. His research interests include high-efciency power converters and renewable energy power conversion system. He has published more than 70 technical papers and holds more than 20 issued/pending patents.

Yi Zhao (S10) was born in Liaoning, China, in 1983. He received the B.Sc. degree from the College of Electrical and Electronic Engineering, Huazhong University of Science and Technology, Wuhan, China, in 2006. He is currently working toward the Ph.D. degree at the College of Electrical Engineering, Zhejiang University, Hangzhou, China. His research interests include dc/dc converters and PV power system.

GU et al.: TRANSFORMERLESS INVERTER WITH VIRTUAL DC BUS CONCEPT FOR COST-EFFECTIVE GRID-CONNECTED PV POWER SYSTEMS

805

Bo Yang was born in Sichuan, China, in 1981. He received the B.Sc. degree in applied power electronics from Zhejiang University, Hangzhou, China, in 2004, where he is currently working toward the Ph.D. degree in electrical engineering. His research interests include PV power system, power converter modeling, and digital control techniques.

Chushan Li (S10) received the B.E.E. degree from the Department of Electrical Engineering, Zhejiang University, Hangzhou, China, in 2008, where he is currently working toward the Ph.D. degree at the College of Electrical Engineering. From April to September in 2008, he was an Intern in the Power Application Design Center, National Semiconductor (Hong Kong) Company, Ltd. From December 2010 to October 2011, he was a Visiting Scholar with the Freedm Center, North Carolina State University, where he was involved in research on solid-state transformer and smart grid. His research interests include renewable energy technology and acac power conversion in utility applications.

Xiangning He (M95SM96F10) received the B.Sc. and M.Sc. degrees from the Nanjing University of Aeronautical and Astronautical, Nanjing, China, in 1982 and 1985, respectively, and the Ph.D. degree from Zhejiang University, Hangzhou, China, in 1989. From 1985 to 1986, he was an Assistant Engineer at the 608 Institute of Aeronautical Industrial General Company, Zhuzhou, China. From 1989 to 1991, he was a Lecturer at Zhejiang University. In 1991, he received a Fellowship from the Royal Society of U.K., and conducted research in the Department of Computing and Electrical Engineering, Heriot-Watt University, Edinburgh, U.K., as a Postdoctoral Research Fellow for two years. In 1994, he joined Zhejiang University as an Associate Professor, where he became a Full Professor in the College of Electrical Engineering in 1996. He was the Director of the Power Electronics Research Institute and the Head of the Department of Applied Electronics, and he is currently the Vice Dean of the College of Electrical Engineering, Zhejiang University. He is the author or coauthor of more than 200 papers and one book Theory and Applications of Multi-level Converters. He holds 12 patents. His research interests include power electronics and their industrial applications. Dr. He received the 1989 Excellent Ph.D. Graduate Award, the 1995 Elite Prize Excellence Award, the 1996 Outstanding Young Staff Member Award, and the 2006 Excellent Staff Award from Zhejiang University for his teaching and research contributions. He received ve Scientic and Technological Progress Awards from the Zhejiang Provincial Government and the State Educational Ministry of China in 1998, 2002, and 2009, respectively, and ve Excellent Paper Awards. He is a Fellow of the Institution of Engineering and Technology (formerly IEE), U.K.

Potrebbero piacerti anche

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5795)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Zelio Control RM4TU02Documento2 pagineZelio Control RM4TU02Susi SumeilyahNessuna valutazione finora

- Speed Control of DC MotorDocumento19 pagineSpeed Control of DC MotorVijaya LakshmiNessuna valutazione finora

- MV Switchgear Alfa12 PDFDocumento36 pagineMV Switchgear Alfa12 PDFYassine AlloucheNessuna valutazione finora

- Wiring Diagram: Rotax Engine Wiring Water Temp GaugeDocumento1 paginaWiring Diagram: Rotax Engine Wiring Water Temp Gaugejacktheripper100% (1)

- VCBDocumento19 pagineVCBmadan_153Nessuna valutazione finora

- 056-022 Breaker ControlDocumento4 pagine056-022 Breaker Controlluis gomezNessuna valutazione finora

- Esquemas 125-130a35122 PDFDocumento10 pagineEsquemas 125-130a35122 PDFJosé Carlos Martínez TascónNessuna valutazione finora

- Can You Find What Is The Type of Motor Used For These Applications?Documento17 pagineCan You Find What Is The Type of Motor Used For These Applications?nandhakumarme0% (1)

- Solar-Installer-Handbook IEC SchneiderDocumento52 pagineSolar-Installer-Handbook IEC SchneiderPutri Vardabella VeshiaNessuna valutazione finora

- Ara Knaian PHD ThesisDocumento206 pagineAra Knaian PHD Thesispepper100Nessuna valutazione finora

- Field Inspection Testing Electrical EquipmentDocumento21 pagineField Inspection Testing Electrical Equipmentkisan singh100% (2)

- ViewPDFServlet PDFDocumento1 paginaViewPDFServlet PDFkush guptaNessuna valutazione finora

- Bpe Micro ProjectDocumento9 pagineBpe Micro ProjectIshwari JadhavNessuna valutazione finora

- Amp KW ChartDocumento1 paginaAmp KW ChartMohammad Amer50% (4)

- Powerqualitynotes UNIT 1Documento6 paginePowerqualitynotes UNIT 1lvb123Nessuna valutazione finora

- District Rate 2079-2080Documento41 pagineDistrict Rate 2079-2080CGengineering ConsultantNessuna valutazione finora

- MNS-SG - Technical Presentation 2013Documento29 pagineMNS-SG - Technical Presentation 2013Jorge Luis Mallqui BarbaranNessuna valutazione finora

- P1470Documento6 pagineP1470Priya SingNessuna valutazione finora

- Dse7320 Installation InstructionsDocumento2 pagineDse7320 Installation Instructions032359rwNessuna valutazione finora

- I B R Material Cum Release Note Received Details (2) - RBPLDocumento8 pagineI B R Material Cum Release Note Received Details (2) - RBPLManikandan elumalaiNessuna valutazione finora

- Introduction of Small Modular Reactors 2Documento10 pagineIntroduction of Small Modular Reactors 2Kerwa MdachiNessuna valutazione finora

- Automatic Power Factor Correction Using Capacitive BankDocumento38 pagineAutomatic Power Factor Correction Using Capacitive BankharishmaNessuna valutazione finora

- Experiment - 1 Object:-Study and Test The Firing Circuit of Three Phase Half Controlled Bridge Converter. TheoryDocumento6 pagineExperiment - 1 Object:-Study and Test The Firing Circuit of Three Phase Half Controlled Bridge Converter. Theorysahumanish9240Nessuna valutazione finora

- Variable Speed DriveDocumento1 paginaVariable Speed DriveKenneth LewisNessuna valutazione finora

- Vocational Training at Cesc LimitedDocumento45 pagineVocational Training at Cesc LimitedRohit BaruaNessuna valutazione finora

- University of Zimbabwe: Power Electronics and Motion Control: Ee420Documento8 pagineUniversity of Zimbabwe: Power Electronics and Motion Control: Ee420shania msipaNessuna valutazione finora

- Testing and Commissioning of 66 33 KV SubstationDocumento9 pagineTesting and Commissioning of 66 33 KV Substationm khNessuna valutazione finora

- Havells Rotary HandleDocumento1 paginaHavells Rotary HandleSourabh RoyNessuna valutazione finora

- Ufc - 3 - 550 - 01 (Exterior Electrical Power Distribution)Documento54 pagineUfc - 3 - 550 - 01 (Exterior Electrical Power Distribution)Samiullah AmarkhelNessuna valutazione finora