Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Implementing Hamming Code Using VLSI

Caricato da

naveednad2003556Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Implementing Hamming Code Using VLSI

Caricato da

naveednad2003556Copyright:

Formati disponibili

International Journal of Engineering Trends and Technology- Volume4Issue2- 2013

Implementation of Hamming code using VLSI

Nutan Shep1, Mrs. P.H. Bhagat2

Department of Electronics & Telecommunication Dr.B.A.M.U,Aurangabad Government College of Engineering Aurangabad (M.S.) ,India-431005

Abstract-This paper tries to explain the implementation of hamming code using VLSI. In the present world the field of communication has got many applications, and in every field the data is encoded at the transmitter and transferred on a communication channel and received at the receiver after it is decoded. During the transmission of data it might get corrupted because of some noise on the channel. So it is necessary for the receiver to have some function which can detect the error in the received data. Hamming code is one of such forward error correcting code which has got many applications. In this paper the algorithm for hamming code is discussed and then implementation of it in verilog is done to get the results. Hamming code is an improvement over parity check method. Here a code is implemented in verilog in which 4-bit of information data is transmitted with 3-redundancy bits. In order to find the value of these redundancy bits a code is written in verilog which will be simulated in Xillinx 9.1 software. The result of simulation and test bench waveforms are also shown. Keywords: VLSI, verilog, xillinx, redundancy, parity, Hamming.

occurred. In this sense, extended hamming codes are single error correcting and double-error detecting and often reffered to as SECDED.[3][4] In this paper we have written Verilog code for finding error location and correct the bit which is corrupted. At the destination, we receive 7-bit of data with 4 redundancy bits. This received data may be corrupted due to noise. To remove this noise we find the address of the error bit then correct them. To find the location of error bit and correct them we write code in Verilog language.This paper is organized as follows: the concept of hamming code along with the application of it, Verilog language, Why Verilog is preffered over VHDL, Implementation of hamming code, Performance and experimental results, conclusion and references. II. HAMMING CODE Hamming code are the linear block code which are invented by Richard.W. Hamming. They are an improvement over simple parity code method. Hamming codes are valid only when the hamming distance between the bits is less then or equal to one. By contrast, the simple parity code cannot correct errors, and can only detect an odd number of errors. They are the type of binary codes. The idea of hamming distance is the central concept in coding the error control. The hamming distance between the two words (of the same size) is the number of differences between the corresponding bits.The hamming distance can easily be found if we apply the Xor operation on the two words and count the number of 1s in the result. The hamming distance is a value always greater then zero. If we find the hamming distance between any two words it will be the result of the Xoring of the two bits. Like the hamming distance between d (000,011) is 2 because 000 xor 011 is 011(two 1s) and the hamming distance between d(10101,11110) is 3 because 10101 xor 11110 is 01011(three 1s).[3][7] Hamming code method works only on two methods(even parity, odd parity) for generating redundancy bits. The number of redundancy bits are generated using a formula. The number of redundancy depends on the number of information data bits. The formula is: 2^r = D+r+1...(1) Here, r = number of redundancy bits D = number of information data bits

I. INTRODUCTION One of the major issues in the field of communication is the secure and error free transmission of data from transmitter to receiver. And for error free transmission there are number of technologies. One of the technologies which is used for correcting forward error is the Hamming code technology. Around 1947 Richard W. Hamming developed this technology to detect and correct single bit errors in transmitted data. In Hamming code error detection and correction technique to get error free data at destination, we encrypt information data according to even and odd parity method before transmission of information at source end.[3][1] In telecommunication, Hamming codes are a family of linear error correcting codes. Hamming codes can detect upto two and correct upto one bit errors. By contrast the simple parity code cannot correct errors, and can detect only odd number of errors. Hamming code are special in that they are perfect codes, that is they achieve the hightest possible rate for codes with their block length and minimum distance. Because of the simplicity of hamming codes, they are widely used in computer memory. In this context one often uses an extended hamming code with one extra parity bit. Extended hamming code achieve a distance of 4, which allows the decoder to distinguish between the situation in which at most one bit error occurred and the situation in which two bit error

ISSN: 2231-5381

http://www.internationaljournalssrg.org

Page 186

International Journal of Engineering Trends and Technology- Volume4Issue2- 2013

If we calculate the number of redundancy bits for an 4 bit of information then it comes to be 3 redundancy bit. Redundancy bits are those extra bits which are required to detect and correct errors. The redundancy bits are added to the information bit at the transmitter and removed at the receiver. The receiver is able to detect the error and correct it because of the redundancy bits. Hamming codes are used as forward error correcting codes in the Bluetooth standard, and to protect data stored in semiconductor memories. Hamming codes are generally used in computing, telecommunication, and other applications including data compression, and turbo codes. They are also used for low cost and low power applications. III. VERILOG LANGUAGE Verilog is one fo the two most common Hardware Description languages(HDL) used by integrated circuits(IC)designers. The other one is VHDL. Verilog can be used to describe designs at four levels of abstraction. They are the algorithmic level, the register transfer level, the gate level and the switch level.[6] A. USING VERILOG FOR SIMULATION The basic structure of Verilog in which all hardware components and testbenches are described is called a module. Language constructs, in accordance to Verilog syntax and semantics form the inside of a module. These constructs are designed to facilitate the description of hardware components for simulation, synthesis, and specification of testbenches to specify test data and monitor circuit responses. A module that encloses a designs description can be described to test the module under design, in which case it is regarded as the testbench of the design. After a design passes basic the functional validations, it must be synthesized into a netlist of components of a target library. The target library is the specification of the hardware that the design is being synthesized to. Verilog constructs used in the Verilog description of a design for its verification or those for timing checks and timing specifications are not synthesizable. A verilog design that is to be synthesized must use language constructs that have a clear hardware correspondence. The figure below shows a block diagram specifying the synthesis process. Circuit being synthesized and specification of the target library are the inputs of a synthesis tool. The outputs of synthesis are a netlist of components of the target library, and timing specification and other physical details of the synthesized design. Often synthesis tools have an option to generate this netlist in Verilog.

Fig 2 synthesis of a verilog design

C. POST-SYNTHESIS

SIMULATION

When the netlist is provided by the synthesis tool that uses verilog for the description of the netlist components(Fig 1), the same testbench prepared for the pre-synthesis simulation can be used with this gate-level description. This simulation, which is often regarded as post-synthesis simulation, uses timing information generated by the synthesis tool and yields simulation results with detailed timing. Since the same testbench of the high-level design is applied to the gatelevel description, the resulted waveform or printed data must be the same.[5][6]

Figure 1 Simulation in verilog

The above model consists of a design with a verilog testbench. Verilog constructs (shown by dotted lines) of the Verilog model being tested are responsible for the description of its hardware, while language constructs used in a testbench are in charge of providing appropriate input data or applying data stored in a text file to the module being tested, and analysis or display of its outputs. Simulation output is generated in the form of a waveform for visual inspection or data files for record or for machine readability.[5][6] B. USING

VERILOG FOR SYNTHESIS

Fig 3 Post synthesis simulation

This can be seen when comparing Fig 1 and 3, while the only difference is that the post-synthesis simulation includes timing details. IV.WHY

VERILOG PREFFERED OVER VHDL

We are preffering verilog language over VHDL because of the

ISSN: 2231-5381

http://www.internationaljournalssrg.org

Page 187

International Journal of Engineering Trends and Technology- Volume4Issue2- 2013

following reasons. Step 1. Represent each data bit with a column vector as follows: 1 0 d1 = 0 0 0 d2 = 1 0 0 0 d3 = 0 1 0 0 0 d4 = 0 1 Step 2. Represent each parity bit with a column vector containing a 1 in the row corresponding to each data bit included in the computation and a zero in all other rows. Using the parity bit definitions from the example above:[7][2] 0 1 1 1 1 0 1 1

1.Verilog means verification of logic. It is built in C mostly

easy to learn. 2. It gives the simple and effective way of describing the digital circuits. It is intended for modeling, simulation and analysis. 3. They are highly portable and self documenting . 4.They provides many descriptive style like structural, register transfer level and behavioral. 5.Design described in HDL are technology independent, easy to design and debug, and are usually more readable than schematics, particularly for large circuits. 6.The way the code is written will greatly effect size and speed of the synthesized circuit.[5][8] V. IMPLEMENTATION OF HAMMING CODE In this section , the design of hamming code encoder and decoder in Verilog language will be done. Here we have used the (7,4) algorithm. The algorithm is called a (7, 4) code, because it requires seven bits to encoded four bits of data. The extra three bits are parity bits. Each of the three parity bits are parity for three of the four data bits, and no two parity bits are for the same three data bits. All of the parity bits are even parity. Example: Given: data bits d1, d2, d3, and d4 A (7, 4) Hamming code may define parity bits p1, p2, and p3 as p1 = d2 + d3 + d p2 = d1 + d3 + d4 p3 = d1 + d2 + d4 (2) (3) (4)

p1 =

p2 =

There's a fourth equation for a parity bit that may be used in Hamming codes: p4 = d1 + d2 + d3 (5)

Valid Hamming codes may use any three of the above four parity bit definitions. Valid Hamming codes may also place the parity bits in any location within the block of 7 data and parity bits. Two Hamming codes with different parity bits or parity bits in a different bit position are considered equivalent. They will produce different results, but they are still Hamming codes. One method for transforming four bits of data into a seven bit Hamming code word is to use a 47 generator matrix [G].[2][4] Define d to be the 14 vector [d1 d2 d3 d4] It's possible to create a 47 generator matrix [G] such that the product modulo 2 of d and [G] (d[G]) is the desired 17 Hamming code word. Here's how it's done:

1 1 p3 = 1 0 Step 3. Create a generator matrix, [G], by arranging the column vectors from the previous steps into a 47 matrix such that the columns are ordered to match their corresponding bits in a code word. To create a generator that produces code words with the bits ordered p1, p2, p3, d1, d2, d3, d4 (3 parity bits followed by 4 data bits) use the vectors from the previous steps and arrange them into the following columns [p1 p2 p3 d1 d2 d3 d4] .[1][2] The results are following 47 generator matrix: p1 p2 p3 d1 d2 d3 d4

ISSN: 2231-5381

http://www.internationaljournalssrg.org

Page 188

International Journal of Engineering Trends and Technology- Volume4Issue2- 2013

0 1 1 1 1 0 1 1 1 1 0 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1

G =

H =

1 0 0 0 1 1 1 0 1 0 1 0 1 1 0 0 1 1 1 0 1

Arranging the columns in any other order will just change the positions of bits in the code word. Example: Encode the data value 1010 using the Hamming code defined by the matrix G (above). 0 1 1 1 1 0 1 1 1 1 0 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1

Multiplying the 37 matrix [H] by a 71 matrix representing the encoded data produces a 31 matrix called the "syndrome". There are two useful proprieties of the syndrome. If the syndrome is all zeros, the encoded data is error free. If the syndrome has a non-zero value, flipping the encoded bit that is in the position of the column in [H] that matches the syndrome will result in a valid code word.[2] Example: Using the parity check matrix from the example above we can correct and verify the code word 1011011.

[1 0 1 0 ]

= 1 1 1 1 0 0 0 1 1 1 1 0 1 0 1 0 1 1 * 1 = 1 0 1 0 0 1 1 1 0 1 1 0 A column of all 1s is not the column of all 0s, so there is a parity error. Looking back at the matrix [H], you will see that the seventh column is all 1s, so the seventh bit is the errored bit. Changing the seventh bit produces the code word 1011010. 1 0 1 1 0 1 0

[1 0 1 1 0 1 0] So 1010 encodes to 1011010. Equivalent Hamming codes represented by different generator matrices will produce different results. In a world without errors decoding a Hamming code word would be very easy. Just throw out the parity bits. The encoding example produced a 7 bit code word. Its parity bits are 101 and its data bits are 1010. If you receive a 1011010, just decode it as 1010. But what happens if you receive a code word with an error and one or more of the parity bits are wrong?[7][1] Suppose the Hamming code defined by the matrix G in the example above is being used and the code word 1011011 is received. How is that word decoded? The first step is to check the parity bits to determine if there is an error. Arithmetically, parity may be checked as follows: p1 = d2 + d3 + d4 = 0 + 1 + 1 = 0 p2 = d1 + d3 + d4 = 1 + 1 + 1 = 1 p3 = d1 + d2 + d4 = 1 + 0 + 1 = 0 In this case every parity bit is wrong. p1, p2, and p3 should have been 010, but we received 101.Parity may also be validated using matrix operations. A 37 parity check matrix [H] may be constructed such that row 1 contains 1s in the position of the first parity bit and all of the data bits that are included in its parity calculation. Row 2 contains 1s in the position of the second parity bit and all of the data bits that are included in its parity calculation. Row 3 contains 1s in the position of the third parity bit and all of the data bits that are included in its parity calculation. Example: Using the code from example above, the matrix H may be defined as follows:

1 0 0 0 1 1 1 0 1 0 1 0 1 1 * 0 0 1 1 1 0 1

0 0 0

Sure enough 1011010 is a valid code word. As I stated at the top of this section remove the parity bits to get the encoded value. In this case 1011011 was likely transmitted as 1011010, which encodes 1010. VI. PERFORMANCE AND EXPERIMENTAL RESULT We have written a code in verilog for hamming[7,4] code. The code is running succefully. In this code we are initializing a data of 4 bit and calculating its parity bit by the above general algorithm. It requires to calculate the parity bit by matrix multiplication and modulo-2 addition. The parity bit required for four bit data is three bit. These bits are calculated and the code is written using case statement.[5][6] We have done encoding and decoding of the data in the same code. A variable syndrome is used to decode the data and to calculate the parity bit. Syndrome is calculated by multiplying a 3x7 matrix[H] by a 7x1 matrix representing the encoded data produces a 3x1 matrix, called syndrome. The syndrome has two useful properties. First if the syndrome is all zeros,

ISSN: 2231-5381

http://www.internationaljournalssrg.org

Page 189

International Journal of Engineering Trends and Technology- Volume4Issue2- 2013

the encoded data is error free. But if the syndrome has a nonzero value, then flip the encoded bit that is in the position of the column in [H] that matches the syndrome will result in a valid code word.[6] Before viewing the test bench waveform we will show the input/output ports of hamming encoder and decoder.

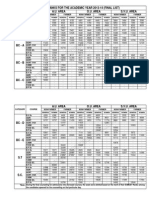

TABLE 1 INPUT/OUTPUT PORTS Fig 6 Given output data

Signal Data_in Edc_in Data_out error syndrome

Description Input data Calculates the parity bit Outputs data It is 0 when syndrome is 0 Connection between hardware elements

The figure below gives the simulation result of the test bench waveform.I shows that when we send the input data 8h55 to the input variable the syndrome calculates the parity bit and transmits the data bit and in the result we get output data bit as 8h55.

The test bench waveform below shows that we have given a input data of 8 bit.The data is 01010101 i.e 8h55 in hexadecimal.The figure below shows only the value of the data.

Fig 7 simulation result

VII. CONCLUSION Thus we have tried to implement hamming code in verilog language and shown the output results. Hamming codes have improved the way of communication by detecting and correcting errors. We have also given the reason that why we are preffering verilog language over VHDL.

Fig 4 Test bench waveform

ACKNOWLEDGEMENT

I gratefully acknowledge all the people who assisted me during this work. It is a pleaser to thank to all the members who encouraged me for this journal presentation, whose words are great encouragement to me. I enjoyed and learnt many more things from this event. Finally, I will welcome all the suggestions from anybody which will definitely nice one. If you found any mistake or error please suggest for the same. Finally, I gratefully acknowledge to all Institute members because of them I got inspiration to write and present this journal in this event.

The figure below shows the in detail bits of input data. Like the 8th bit contains 0,7th bit contains 1,6th bit contains 0 and so on.

REFERENCES

[1] Data communication and networking, Behrouz A. Forouzan, 4th edition, Tata McGrawHill publication. [2] http://hamming (7,4) code Discussion and implementation. [3] Hardware implementation of a single bit error code correction by constantion IANA, Gheorghe SERBAN, Ion TUTANESCU, Petre ANGHE-LESCU. [4] Information Theory Coding and Cryptography by Ranjan Bose. [5] http://www.xillinx.com/training/xillinx-training- courses.pdf. [6] Verilog HDL:A guide to digital design and synthesis,second edition by Sameer Palnitkar. [7] Hamming W.Richard. Coding and information and theory, Prentice-Hall chapter 3. [8] ISE 9.1 Quick Start Tutorial, available at http:/ www.xillinx.com/itp/ xillinx9/books/docs/qst/q.

Fig 5 Input data

In the next figure we are giving the bits to edc_in variable which helps in calculating the parity bits. The variable edc_in contains 1010 i.e 4hA in hexadecimal.

ISSN: 2231-5381

http://www.internationaljournalssrg.org

Page 190

Potrebbero piacerti anche

- Hamming Code PDFDocumento4 pagineHamming Code PDFFind ProgrammerNessuna valutazione finora

- Turbo Codes Tutorial on Error Correcting Coding SchemesDocumento27 pagineTurbo Codes Tutorial on Error Correcting Coding SchemesAbdallah BalahaNessuna valutazione finora

- Implementing (7, 4) Hamming Code Using CPLD On VHDLDocumento6 pagineImplementing (7, 4) Hamming Code Using CPLD On VHDLmohanNessuna valutazione finora

- Jsaer2015 02 01 01 15Documento15 pagineJsaer2015 02 01 01 15jsaereditorNessuna valutazione finora

- Hamm CodeDocumento35 pagineHamm CodepalakNessuna valutazione finora

- Hamming CodeDocumento5 pagineHamming CodeNarayanaNessuna valutazione finora

- LDPC Encoding and Decoding For High Memory and DSP ApplicationsDocumento62 pagineLDPC Encoding and Decoding For High Memory and DSP Applicationskalyan.427656Nessuna valutazione finora

- Performance Evaluation of CDMA Router For Network-On-ChipDocumento11 paginePerformance Evaluation of CDMA Router For Network-On-ChipAnonymous e4UpOQEPNessuna valutazione finora

- Bit Error Optimization of Coded Ofdm System Over RDocumento10 pagineBit Error Optimization of Coded Ofdm System Over RzelalemaschaleyNessuna valutazione finora

- FPGA Implementation of Convolutional Encoder and Hard Decision Viterbi DecoderDocumento5 pagineFPGA Implementation of Convolutional Encoder and Hard Decision Viterbi DecoderSiva KrishnaNessuna valutazione finora

- Brijesh Rita JainDocumento3 pagineBrijesh Rita JainTun ĐứcNessuna valutazione finora

- A FEC Decoding in LTE and WiMAX SystemsDocumento4 pagineA FEC Decoding in LTE and WiMAX SystemsseventhsensegroupNessuna valutazione finora

- Channel coding schemes for 5G short messagesDocumento7 pagineChannel coding schemes for 5G short messagesAbdunabi MuhamadievNessuna valutazione finora

- A Survey On Designing of Turbo Encoder & Turbo DecoderDocumento8 pagineA Survey On Designing of Turbo Encoder & Turbo DecoderIJAFRCNessuna valutazione finora

- Block CodingDocumento2 pagineBlock CodingJasmeen kaurNessuna valutazione finora

- Performance Evaluation For Convolutional Codes Using Viterbi DecodingDocumento6 paginePerformance Evaluation For Convolutional Codes Using Viterbi Decodingbluemoon1172Nessuna valutazione finora

- Algorithm Implementation Using Interactive Input For LBC FinalDocumento16 pagineAlgorithm Implementation Using Interactive Input For LBC FinalPrajwal PrabhuNessuna valutazione finora

- 927-930 IJER - 2016 - 1226 Zina CDocumento6 pagine927-930 IJER - 2016 - 1226 Zina CInnovative Research PublicationsNessuna valutazione finora

- NCTT2003 - 01188314Documento5 pagineNCTT2003 - 01188314UkAYsNessuna valutazione finora

- Design and Verification of High Speed Protocols and Algorithms in Digital Communication Systems Using Verilog and VHDLDocumento5 pagineDesign and Verification of High Speed Protocols and Algorithms in Digital Communication Systems Using Verilog and VHDLChristo ElginNessuna valutazione finora

- The Use of Matlab For The Simulation of The Burst Error CorrectionDocumento5 pagineThe Use of Matlab For The Simulation of The Burst Error CorrectionJuzze LimerNessuna valutazione finora

- Laboratory 2 Error Correction - v4Documento2 pagineLaboratory 2 Error Correction - v4Sahan KaushalyaNessuna valutazione finora

- Error Coding Reed SolomonDocumento28 pagineError Coding Reed SolomonAnumNessuna valutazione finora

- Turbo Product Codes Based On Convolutional CodesDocumento8 pagineTurbo Product Codes Based On Convolutional CodesIeħor BissNessuna valutazione finora

- Design and Implementation of Reconfigurable Coders For Communication SystemsDocumento6 pagineDesign and Implementation of Reconfigurable Coders For Communication SystemsAnonymous ltM6Bv4IvNessuna valutazione finora

- Multiplier RelatedDocumento6 pagineMultiplier RelatedKanaga VaratharajanNessuna valutazione finora

- The Principles of Coding in Digital Communications: 1.1 Error Control SchemesDocumento34 pagineThe Principles of Coding in Digital Communications: 1.1 Error Control SchemespathmakerpkNessuna valutazione finora

- Structure: Chapter 1: Error Control CodingDocumento66 pagineStructure: Chapter 1: Error Control Codingabhilash gowdaNessuna valutazione finora

- International Journal of Engineering Research and Development (IJERD)Documento5 pagineInternational Journal of Engineering Research and Development (IJERD)IJERDNessuna valutazione finora

- Chapter-1: 1.1: Coding TheoryDocumento35 pagineChapter-1: 1.1: Coding Theoryhari chowdaryNessuna valutazione finora

- Cyclic Redundancy CheckDocumento40 pagineCyclic Redundancy CheckVinnu VinniNessuna valutazione finora

- Includes Report, Presentation,: SynopsysDocumento2 pagineIncludes Report, Presentation,: SynopsysasitNessuna valutazione finora

- Error CDDocumento6 pagineError CDproblemslo420Nessuna valutazione finora

- Implementation of Berlekamp Algorithm For Error Detection and Correction of Multiple Random Errors Using Reed-Solomon CodesDocumento4 pagineImplementation of Berlekamp Algorithm For Error Detection and Correction of Multiple Random Errors Using Reed-Solomon CodesInternational Journal of computational Engineering research (IJCER)Nessuna valutazione finora

- Forward error correction codesDocumento6 pagineForward error correction codessensonghaNessuna valutazione finora

- Performance Review of Serially Concatenated RSC-RSC Codes Using Non-Iterative Viterbi Decoding TechniqueDocumento6 paginePerformance Review of Serially Concatenated RSC-RSC Codes Using Non-Iterative Viterbi Decoding TechniqueJacob BauerNessuna valutazione finora

- Design of LDPC Decoder Using FPGA: Review of Flexibility: Asisa Kumar Panigrahi, Ajit Kumar PandaDocumento6 pagineDesign of LDPC Decoder Using FPGA: Review of Flexibility: Asisa Kumar Panigrahi, Ajit Kumar PandaresearchinventyNessuna valutazione finora

- 32-Bit RISC Processor With Concurrent Error DetectionDocumento7 pagine32-Bit RISC Processor With Concurrent Error DetectionRoney JosephNessuna valutazione finora

- Forward Error CorrectionDocumento5 pagineForward Error CorrectionmkawserNessuna valutazione finora

- Digital Steganography: Data Hiding by Using Video SignalDocumento5 pagineDigital Steganography: Data Hiding by Using Video SignalClaudiu StanciuNessuna valutazione finora

- Communication Protocols Augmentation in VLSI Design ApplicationsDocumento5 pagineCommunication Protocols Augmentation in VLSI Design ApplicationsMoorthy VenkatachalamNessuna valutazione finora

- RTL Implementation of Viterbi Decoder Using VHDL: Hiral Pujara, Pankaj PrajapatiDocumento7 pagineRTL Implementation of Viterbi Decoder Using VHDL: Hiral Pujara, Pankaj PrajapatiInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- LDPC - Low Density Parity Check CodesDocumento6 pagineLDPC - Low Density Parity Check CodespandyakaviNessuna valutazione finora

- Review On VHDL Based Design of Convolutional Encoder Using Vedic Mathematics and Viterbi Decoder Using Parallel Processing Ijariie1637Documento4 pagineReview On VHDL Based Design of Convolutional Encoder Using Vedic Mathematics and Viterbi Decoder Using Parallel Processing Ijariie1637yogitaNessuna valutazione finora

- Error Detection and CorrectionDocumento10 pagineError Detection and CorrectionnvbondNessuna valutazione finora

- Snug04 Bromley Smith PaperDocumento16 pagineSnug04 Bromley Smith PaperDheeraj SinglaNessuna valutazione finora

- Main Project On Design of LTE Turbo Encoder: By: P.Kavithapriya N.Reshma S.V.Sandhya T.Nagaswetha M.B.DevikaDocumento22 pagineMain Project On Design of LTE Turbo Encoder: By: P.Kavithapriya N.Reshma S.V.Sandhya T.Nagaswetha M.B.DevikaSherin TajNessuna valutazione finora

- Error Detection CorrectionDocumento22 pagineError Detection CorrectionJagdish BhanushaliNessuna valutazione finora

- Implementation of Reed Solomon Error Correcting CodesDocumento48 pagineImplementation of Reed Solomon Error Correcting CodesmanojpeehuNessuna valutazione finora

- InteressanteDocumento6 pagineInteressanteMarta FernandesNessuna valutazione finora

- Turbo Code: Technical Seminar Report OnDocumento22 pagineTurbo Code: Technical Seminar Report OnPrasant Kumar BarikNessuna valutazione finora

- Implementation of Adaptive Viterbi DecoderDocumento7 pagineImplementation of Adaptive Viterbi DecoderseventhsensegroupNessuna valutazione finora

- Demonstration For Implementation of Basic Operational Blocks Related To Viterbi Algorithm in Software by Using VB NET Programming LanguageDocumento8 pagineDemonstration For Implementation of Basic Operational Blocks Related To Viterbi Algorithm in Software by Using VB NET Programming LanguageThobius JosephNessuna valutazione finora

- UNIT - 3 - Data-Link LayerDocumento157 pagineUNIT - 3 - Data-Link Layerpatilamrutak2003Nessuna valutazione finora

- A New Approach For Fec Decoding Based On The BP Algorithm in Lte and Wimax SystemsDocumento6 pagineA New Approach For Fec Decoding Based On The BP Algorithm in Lte and Wimax SystemsBuvanesh BuviNessuna valutazione finora

- InterleavingDocumento3 pagineInterleavingRaveendranath KRNessuna valutazione finora

- Channel Coding: Theory, Algorithms, and Applications: Academic Press Library in Mobile and Wireless CommunicationsDa EverandChannel Coding: Theory, Algorithms, and Applications: Academic Press Library in Mobile and Wireless CommunicationsNessuna valutazione finora

- Network Coding: Fundamentals and ApplicationsDa EverandNetwork Coding: Fundamentals and ApplicationsMuriel MedardNessuna valutazione finora

- Serial Port Complete: COM Ports, USB Virtual COM Ports, and Ports for Embedded SystemsDa EverandSerial Port Complete: COM Ports, USB Virtual COM Ports, and Ports for Embedded SystemsValutazione: 3.5 su 5 stelle3.5/5 (9)

- APPSC ASOs Computer Science Paper - II - 2012Documento18 pagineAPPSC ASOs Computer Science Paper - II - 2012naveednad2003556Nessuna valutazione finora

- Problems To Ace Coding InterviewsDocumento24 pagineProblems To Ace Coding Interviewsnaveednad2003556Nessuna valutazione finora

- Coin Change ProblemDocumento3 pagineCoin Change Problemnaveednad2003556Nessuna valutazione finora

- Englishcolorad 22.07.2014Documento1 paginaEnglishcolorad 22.07.2014naveednad2003556Nessuna valutazione finora

- Basic GPS concept explainedDocumento3 pagineBasic GPS concept explainednaveednad2003556100% (1)

- Quite SleepDocumento66 pagineQuite Sleepnaveednad2003556Nessuna valutazione finora

- Naveed ResumeDocumento4 pagineNaveed Resumenaveednad2003556Nessuna valutazione finora

- Career PDF CWE Clerks IV AdvtDocumento34 pagineCareer PDF CWE Clerks IV Advtnaveednad2003556Nessuna valutazione finora

- ECE Adhoc Advt. MAy 2014Documento2 pagineECE Adhoc Advt. MAy 2014naveednad2003556Nessuna valutazione finora

- Employment News Men Jun 2014 FinalDocumento2 pagineEmployment News Men Jun 2014 Finalnaveednad2003556Nessuna valutazione finora

- ASIC Power Groid AnalysisDocumento121 pagineASIC Power Groid AnalysisNilesh IngaleNessuna valutazione finora

- Agriculture Last Ranks 2013-14Documento2 pagineAgriculture Last Ranks 2013-14Vinay ReddyNessuna valutazione finora

- How To Become A Great FinisherDocumento2 pagineHow To Become A Great Finishernaveednad2003556Nessuna valutazione finora

- PHD MPhil BrochureDocumento9 paginePHD MPhil Brochurenaveednad2003556Nessuna valutazione finora

- Postal MtsDocumento8 paginePostal Mtsnaveednad2003556Nessuna valutazione finora

- Java J2EE Job Interview Companion - K.arulkumaranDocumento237 pagineJava J2EE Job Interview Companion - K.arulkumaranAnu SreekumarNessuna valutazione finora

- Efficient Implementation of Hummingbird Cryptographic Algorithm On A Reconfigurable PlatformDocumento5 pagineEfficient Implementation of Hummingbird Cryptographic Algorithm On A Reconfigurable Platformnaveednad2003556Nessuna valutazione finora

- Staff Selection Commission P&P-II Section: Notice ForDocumento1 paginaStaff Selection Commission P&P-II Section: Notice Fornaveednad2003556Nessuna valutazione finora

- IBPS PO4 CLK 4 RRB 3 CalenderDocumento2 pagineIBPS PO4 CLK 4 RRB 3 CalenderSreejith Sundar PalavilaNessuna valutazione finora

- App Faculty Recruitment14Documento4 pagineApp Faculty Recruitment14naveednad2003556Nessuna valutazione finora

- Approved Annual Programme 2014Documento1 paginaApproved Annual Programme 2014Kiran KumarNessuna valutazione finora

- Cryptanalysis of Hummingbird-1Documento23 pagineCryptanalysis of Hummingbird-1naveednad2003556100% (1)

- The Hummingbird-2 Lightweight Authenticated Encryption AlgorithmDocumento14 pagineThe Hummingbird-2 Lightweight Authenticated Encryption Algorithmnaveednad2003556Nessuna valutazione finora

- Sbi Assistant Clerk Notification 2014Documento5 pagineSbi Assistant Clerk Notification 2014Telugu VaahiniNessuna valutazione finora

- BER and SNRDocumento8 pagineBER and SNRshervinshNessuna valutazione finora

- Enhanced FPGA Implementation of The Hummingbird Cryptographic AlgorithmDocumento11 pagineEnhanced FPGA Implementation of The Hummingbird Cryptographic Algorithmnaveednad2003556Nessuna valutazione finora

- The Advantages and Disadvantages of FIFO MehtodDocumento5 pagineThe Advantages and Disadvantages of FIFO Mehtodnaveednad2003556100% (1)

- 2-Lecture Notes Lesson3 6Documento4 pagine2-Lecture Notes Lesson3 6kstu1112Nessuna valutazione finora

- Dataflow Modeling and Design For Cognitive Radio NetworksDocumento6 pagineDataflow Modeling and Design For Cognitive Radio Networksnaveednad2003556Nessuna valutazione finora

- Guide To OPCDocumento9 pagineGuide To OPCpartho143Nessuna valutazione finora

- Data Normalization TechniquesDocumento22 pagineData Normalization TechniquesNaurah BaitiNessuna valutazione finora

- SAS Procedures by NameDocumento14 pagineSAS Procedures by Namekshen2001Nessuna valutazione finora

- Idle Time ProcessDocumento7 pagineIdle Time ProcessAun RazaNessuna valutazione finora

- IBM I2 Analyst's Notebook FamilyDocumento6 pagineIBM I2 Analyst's Notebook FamilyAngel Julian TrejoNessuna valutazione finora

- Sheet8 SolutionDocumento4 pagineSheet8 SolutionSyed Furqan AlamNessuna valutazione finora

- OCS DCC DescriptionDocumento39 pagineOCS DCC Descriptionilo rohyNessuna valutazione finora

- Enhancements List RST 2011 UR2Documento3 pagineEnhancements List RST 2011 UR2albertvyNessuna valutazione finora

- Revision BIOS Tweaking GuideDocumento6 pagineRevision BIOS Tweaking GuideHeroLanderNessuna valutazione finora

- ABAP Email Funcationality.Documento1 paginaABAP Email Funcationality.Satish NamballaNessuna valutazione finora

- ATM DescriptionDocumento8 pagineATM DescriptionKomal SrivastavNessuna valutazione finora

- Conceptual Data Modeling TechniquesDocumento30 pagineConceptual Data Modeling Techniquesschow906291100% (1)

- Technical Handover Document BTEL RBTDocumento29 pagineTechnical Handover Document BTEL RBTKardinar RudiyantoNessuna valutazione finora

- Flash VocabularyDocumento2 pagineFlash Vocabularyapi-262193618Nessuna valutazione finora

- SrinivasDocumento3 pagineSrinivasRavi YalalaNessuna valutazione finora

- Excel to Internal Table FunctionDocumento3 pagineExcel to Internal Table FunctionOrhan Özgür Yamaç GöktaşNessuna valutazione finora

- Install KUKA - Sim 2.1 enDocumento11 pagineInstall KUKA - Sim 2.1 enpepeNessuna valutazione finora

- Ecs-Unit IDocumento29 pagineEcs-Unit Idavid satyaNessuna valutazione finora

- Bios SG 401 PDFDocumento270 pagineBios SG 401 PDFVASP NIT RourkelaNessuna valutazione finora

- Big BasketDocumento13 pagineBig BasketHimanshu Thakur25% (4)

- History and Features of Java Programming LanguageDocumento17 pagineHistory and Features of Java Programming LanguageAsutosh RanjanNessuna valutazione finora

- HP Compaq 8000 EliteDocumento4 pagineHP Compaq 8000 EliteJohari Yovera DelgadoNessuna valutazione finora

- sql92 IcaDocumento58 paginesql92 IcaJulio Cuevas CasanovaNessuna valutazione finora

- Definition - What Does Mean?: Artificial Intelligence (AI)Documento3 pagineDefinition - What Does Mean?: Artificial Intelligence (AI)Dhinesh KaviraajNessuna valutazione finora

- Davidmc-Easydis Read This FirstDocumento6 pagineDavidmc-Easydis Read This FirstsanistoroaeNessuna valutazione finora

- ImsDocumento445 pagineImsdhaneshplNessuna valutazione finora

- PLSQL 9 1 PracticeDocumento6 paginePLSQL 9 1 PracticeCrisanAndreiNessuna valutazione finora

- Resume - VMware With WinodwsDocumento3 pagineResume - VMware With Winodwshari423Nessuna valutazione finora

- IBM AIX Version 7.1 Differences GuideDocumento452 pagineIBM AIX Version 7.1 Differences GuidedevenderrajuNessuna valutazione finora