Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

MPMC LP

Caricato da

senthilvlTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

MPMC LP

Caricato da

senthilvlCopyright:

Formati disponibili

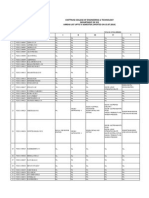

CHETTINAD COLLEGE OF ENGINEERING AND TECHNOLOGY DEPARTMENT OF ECE LESSON PLAN Subject Name: MICROPROCESSOR & MICROCONTROLLER Subject

C!"e : EC#$%& Facu)t* : Mr+P+SENTHIL

AIM To learn the architecture, addressing modes, instruction set, programming of different microprocessors OB,ECTI(ES

Branc : ECE Year ' Sem : III' ( Facu)t* C!"e: FECO$#

To learn basics of microprocessor and in detail about 8086. To learn instruction set and addressing modes of 8086 To learn Microprocessor Peripheral Interfacing To learn in detail about 8051 microcontroller To learn several applications of Microprocessor

T e!r* ' C)a-- : MICROPROCESSOR & MICROCONTROLLER .n/t+I : Intr!"uct/!n t! 0 B/t an" 12 B/t M/cr!3r!ce--!r- 4 H'5 Arc /tecture Tar6et H!ur- : 7 Te8t B!!9 : T1+ rishna ant, !Microprocessors and Microcontrollers "rchitecture, programming and s#stem design using

8085, 8086, 8051 and 80$6%. P&I '00(.

S+N!

Date

Per/!" Re:"+

T!3/c- t! be C!;ere"

Re< B!!9 ' Pa6e Number

M!"e !< teac /n6 B)ac9 B!ar"'OHP' LCD'ED.SATT ' F/e)" ;/-/t B)ac9b!ar"

Actua) Date !< C!m3)et/!n

Remar9-

1%+=+1$

'

11+=+1$

11+=+1$

1#+=+1$

1$+=+1$

Introduction to Microprocessor, memor#, ")*, cloc+, addressing modes and instruction set Machine language program, "ssembl# language program, assembler directives, compilers and operating s#stems "ddress bus, data bus and control bus, Tristate bus, cloc+ generation, I12 mapped and Memor# mapped I12 interface Parallel 3 serial data transfer, "rchitectural advancements of microprocessors 3 4#stem design Pipelining, cache memor#,

1,1(-'$.

10.(.1/ 11.(.1/

1,'$-/0.

B)ac9b!ar"

11.(.1/

1,/5-00.

B)ac9b!ar"

1'.(.1/

1,01.

B)ac9b!ar"

1/.(.1/

1,05-50.

B)ac9b!ar"

15.(.1/

Page 1 of 5

6 ( 8

1>+=+1$ 12+=+1$ 1=+=+1$

1 1 1

10+=+1$

10

17+=+1$

11

#%+=+1$

1' 1/

##+=+1$

memor# management, virtual memor# s#stem &ard5are "rchitecture of 1,1'(8086 1/5. 5,/-10. 67ternal memor# addressing 1,10'105. Memor# or I12 read15rite for 1,106minimum mode, some 10$. important companion chips Memor# read15rite bus 1,15$c#cle, 8086 s#stem 16/. configurations Memor# interfacing, 1,160Interrupts and 9irect 16$. memor# access 5,'1-'(. "ssembl# )anguage 135 Programming ,8 bit 3 16 bit.: Practice "ssembl# )anguage 135 Programming ,16 bit.: Practice ;lass Test-1

16.(.1/

LCD

8lac+board 8lac+board 8lac+board 8lac+board 8lac+board 8lac+board

1(.(.1/ 18.(.1/ 1$.(.1/ '0.(.1/ ''.(.1/

'/.(.1/

T e!r* ' C)a-- : MICROPROCESSOR & MICROCONTROLLER .n/t II : 12 B/t M/cr!3r!ce--!r In-truct/!n Set an" A--emb)* Lan6ua6e Pr!6ramm/n6 Tar6et H!ur- : 7 Te8t B!!9 : T1+ rishna ant, !Microprocessors and Microcontrollers "rchitecture, programming and s#stem design using

8085, 8086, 8051 and 80$6%. P&I '00(

S+N!

Date

Per/!" Re:"+

T!3/c- t! be C!;ere"

Re< B!!9 ' Pa6e Number

M!"e !< teac /n6 B)ac9 B!ar"'OHP' LCD'ED.SATT ' F/e)" ;/-/t

Actua) Date !< C!m3)et/!n '0.(.1/ /0.(.1/ /1.(.1/ 1.8.1/ '.8.1/ /.8.1/

Remar9-

1 '

#$+=+1$ #&+=+1$ $%+=+1$ $1+=+1$ 1+0+1$ #+0+1$ $+0+1$ >+0+1$ 2+0+1$

1 '

'

0 5 6

' 1 1

Programmer<s model of 8086 and operand t#pes =egister, Immediate, direct memor# and register indirect addressing modes 8ase plus inde7 register, register relative, base plus inde7 register relative and string addressing modes The 8086 assembler directives 9ata transfer group "rithmetic instruction set

1,185188. 1,18$1$1. 0,11'1'0. 1,1$'1$6. 0,1'11'0. 1,1$('0'.

8lac+board 8lac+board 8lac+board

8lac+board 8lac+board 8lac+board

5.8.1/ 6.8.1/ (.8.1/

Page ' of 5

( 8 $ 10

=+0+1$ 0+0+1$ 1#+0+1$ 1&+0+1$ 12+0+1$

1 1 ' 1

)ogical group and miscellaneous instruction groups ;ontrol transfer instruction set, etc "ssembl# )anguage Programming : 8086 ;lass Test-'

5,(0-81. 1,'00'''. 5,06-0(.

8lac+board 8lac+board 8lac+board

8.8.1/ 1'.8.1/ 10.8.1/ 16.8.1/

1(.8.1/ ''.8.1/

T e!r* ' C)a-- : MICROPROCESSOR & MICROCONTROLLER .n/t III : M/cr!3r!ce--!r Per/3 era) Inter<ac/n6 te8t B!!9 S+N! Date

Tar6et H!ur- : 7

: T#+ 9ouglas > &all, !Microprocessors and Interfacing, Programming and &ard5are% TM&,'006. Per/!" Re:"+ T!3/c- t! be C!;ere" Re< B!!9 ' Pa6e Number

M!"e !< teac /n6 B)ac9 B!ar"'OHP' LCD'ED.SATT ' F/e)" ;/-/t

Actua) Date !< C!m3)et/!n

Remar9-

1=+0+1$

' / 0 5 6 ( 8 $ 10

##+0+1$ ##+0+1$ #2+0+1$ $%+0+1$ $+7+1$ &+7+1$ >+7+1$ 2+7+1$ 11+7+1$

1 1 1 1 1 1 1 1 1

?eneration of I12 ports, Programmable Peripheral Interface ,8'55., 4ampleand- &old circuit and Multiple7er PPI programming e#board and 9ispla# interface e#board and 9ispla# ;ontroller ,8'($. e#board and 9ispla# program Programmable Interval Timers ,8'5/. 9igital-to-"nalog ;onverter "nalog-to-9igital ;onverter ;=T Terminal Interface and Printer Interface

;lass Test-/

1,'06'60.

8lac+board

''.8.1/

11,/05/0$. 1,'6''65. 1,'81'$0. 5,'66'(8. 135 1,/1//1$. 5,'/5'0/. 1,//5//$. 1,/05/0$.

8lac+board 8lac+board );9 8lac+board 8lac+board 8lac+board 8lac+board 8lac+board

'6.8.1/ /0.8.1/ /.$.1/ 0.$.1/ 5.$.1/ 6.$.1/ 11.$.1/ 1'.$.1/ 1/.$.1/

T e!r* ' C)a-- : MICROPROCESSOR & MICROCONTROLLER .n/t I( : 0 B/t M/cr!c!ntr!))er? H'5 Arc /tecture@ In-truct/!n Set an" Pr!6ramm/n6 Tar6et H!ur- : 7 Te8t B!!9 : T1+ rishna ant, !Microprocessors and Microcontrollers "rchitecture, programming and s#stem design using

8085, 8086, 8051 and 80$6%. P&I '00(.

Page / of 5

S+N!

Date

Per/!" Re:"+

T!3/c- t! be C!;ere"

Re< B!!9 ' Pa6e Number

M!"e !< teac /n6 B)ac9 B!ar"'OHP' LCD'ED.SATT ' F/e)" ;/-/t

Actua) Date !< C!m3)et/!n

Remar9-

1 ' / 0 5 6 ( 8 $ 10 11

1#+7+1$ 1$+7+1$ 12+71$ 1=+7+1$ #%+7+1$ #1+7+1$ #$+7+1$ #>+7+1$ #2+7+1$ #2+7+1$ #=+7+1$

1 1 1 1 1 1 1 1 1 1 1

"rchitecture and Memor# organi@ation of 8051 4pecial Aunction =egisters

1,01$0'/. 1,0'00/0. Port operation /,11/116. Memor# Interfacing and I12 1,0/8Interfacing 00'. Programming the 8051 1,00/resources 00$. 8051 Interrupts 1,050061. Programmer<s model of 8051 1,0655and operand t#pes 06$. 2perand addressing, /,/18Programming 5ith 8051 /'1. 9ata transfer instructions and 1,08'"rithmetic instructions 08(. )ogic instructions and 1,088;ontrol transfer instructions 0$/. 3 Programming ;lass Test-0

);9 8lac+board 8lac+board 8lac+board 8lac+board 8lac+board );9 8lac+board 8lac+board 8lac+board

16.$1/ 1(.$.1/ '0.$.1/ '1.$.1/ '/.$.1/ '5.$.1/ '6.$.1/ '6.$.1/ '(.$.1/

/0.$.1/

1.10.1/

T e!r* ' C)a-- : MICROPROCESSOR & MICROCONTROLLER .n/t ( : S*-tem De-/6n .-/n6 M/cr! Pr!ce--!r & M/cr!c!ntr!))er Te8t B!!9

Tar6et H!ur- : 7

: T#+ 9ouglas > &all, !Microprocessors and Interfacing, Programming and &ard5are% TM&,'006.

Page 0 of 5

S+ N!

Date

Per/!" Re:"+

T!3/c- t! be C!;ere"

Re< B!!9 ' Pa6e Number

M!"e !< teac /n6 B)ac9 B!ar"'OHP' LCD'ED.SATT ' F/e)" ;/-/t

Actua) Date !< C!m3)et/!n 0.10.1/ 5.10.1/ 5.10.1/ (.10.1/

11.10.1/ 1'.10.1/ 1(.10.1/ 18.10.1/

Remar9-

1 / 5 6 ( 8 $

$%+7+1$ 1+1%+1$ &+1%+1$ >+1%+1$ =+1%+1$ 11+1%+1$ 1#+1%+1$ 1=+1%+1$

' 1 1 1 1 1 1

Traffic )ight control Bashing machine control =T; Interfacing using I'; 4tandard Motor ;ontrol- =ela#, PBM, 9; 4tepper Motor ;ontrol "ssembl# )anguage Programming

;lass Test-5

6,'51'56. ( /,06(080. /,50(510. ','81'8/. /,0$8505.

);9 8lac+board 8lac+board );9 8lac+board 8lac+board

Facu)t* /n 4 C ar6e

HOD?ECE

Page 5 of 5

Potrebbero piacerti anche

- REF Probabilistic Gate-Level Power Estimation Using A NovelWaveform Set MethodDocumento6 pagineREF Probabilistic Gate-Level Power Estimation Using A NovelWaveform Set MethodsenthilvlNessuna valutazione finora

- Fadd ExtendedDocumento36 pagineFadd ExtendedsenthilvlNessuna valutazione finora

- Quartus Ii V7.2: The Signaltap Ii Logic Analyzer LabDocumento15 pagineQuartus Ii V7.2: The Signaltap Ii Logic Analyzer LabsenthilvlNessuna valutazione finora

- Unit 1 QuestionDocumento1 paginaUnit 1 QuestionsenthilvlNessuna valutazione finora

- Fundamentals & Link LayerDocumento38 pagineFundamentals & Link LayersenthilvlNessuna valutazione finora

- Pre Internal 1Documento2 paginePre Internal 1senthilvlNessuna valutazione finora

- Genetic Algorithm Model ExamDocumento1 paginaGenetic Algorithm Model ExamsenthilvlNessuna valutazione finora

- CNS QB 2 MK WaDocumento25 pagineCNS QB 2 MK WasenthilvlNessuna valutazione finora

- Operational Description and Message Format of PGPDocumento1 paginaOperational Description and Message Format of PGPsenthilvlNessuna valutazione finora

- Int 1Documento1 paginaInt 1senthilvlNessuna valutazione finora

- Syllabus CNSDocumento2 pagineSyllabus CNSsenthilvlNessuna valutazione finora

- Internal 1 Answer KeyDocumento2 pagineInternal 1 Answer KeysenthilvlNessuna valutazione finora

- Simulated Output: Wallace:tree MR (3..0) MD (3..0) Booth - Encoder:booth Partial:ppDocumento5 pagineSimulated Output: Wallace:tree MR (3..0) MD (3..0) Booth - Encoder:booth Partial:ppsenthilvlNessuna valutazione finora

- Data Link Layer ConceptsDocumento16 pagineData Link Layer ConceptssenthilvlNessuna valutazione finora

- Intruders, Passwords, and Intrusion DetectionDocumento41 pagineIntruders, Passwords, and Intrusion DetectionsenthilvlNessuna valutazione finora

- Course WorkDocumento7 pagineCourse WorksenthilvlNessuna valutazione finora

- Application LayerDocumento31 pagineApplication LayersenthilvlNessuna valutazione finora

- Internal Examination - 1 Internal Examination - 1Documento1 paginaInternal Examination - 1 Internal Examination - 1senthilvlNessuna valutazione finora

- Embedded SystemsDocumento2 pagineEmbedded SystemssenthilvlNessuna valutazione finora

- Model ExamDocumento1 paginaModel ExamsenthilvlNessuna valutazione finora

- Ex. No: Date: Creating Virtual Instrumentation For Simple Application AimDocumento3 pagineEx. No: Date: Creating Virtual Instrumentation For Simple Application AimsenthilvlNessuna valutazione finora

- IT 3 QuestionDocumento1 paginaIT 3 QuestionsenthilvlNessuna valutazione finora

- MEIDocumento1 paginaMEIsenthilvlNessuna valutazione finora

- Department of Electronics and CommunicationDocumento3 pagineDepartment of Electronics and CommunicationsenthilvlNessuna valutazione finora

- Cover PAGEDocumento1 paginaCover PAGEsenthilvlNessuna valutazione finora

- Analog To Digital Converters PresentationDocumento31 pagineAnalog To Digital Converters PresentationJitendra MishraNessuna valutazione finora

- MEIDocumento1 paginaMEIsenthilvlNessuna valutazione finora

- Expt No.: 2 Design and Implementation of Code Onvertor AimDocumento18 pagineExpt No.: 2 Design and Implementation of Code Onvertor AimsenthilvlNessuna valutazione finora

- Introduction To ADCs, TutorialDocumento58 pagineIntroduction To ADCs, Tutorialsenthilvl100% (1)

- Arrer List With Subject Name III Ece-NewDocumento18 pagineArrer List With Subject Name III Ece-NewsenthilvlNessuna valutazione finora

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5784)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- CSC 111 NOTE CompleteDocumento75 pagineCSC 111 NOTE CompleteJimoh QaoliyaNessuna valutazione finora

- Amd Athlon XPDocumento16 pagineAmd Athlon XPchichangNessuna valutazione finora

- Symantec DLP 15.5 System Requirements GuideDocumento67 pagineSymantec DLP 15.5 System Requirements GuideHiếu Lê VănNessuna valutazione finora

- 502 Reflection 2Documento5 pagine502 Reflection 2Brahmendra UpputuriNessuna valutazione finora

- LIC Set - 1Documento11 pagineLIC Set - 1smartkeedaNessuna valutazione finora

- Implementation of RISC Processor On FPGADocumento5 pagineImplementation of RISC Processor On FPGAObaid KhanNessuna valutazione finora

- Philips Healthcare: Field Change Order ServiceDocumento15 paginePhilips Healthcare: Field Change Order ServiceJimNessuna valutazione finora

- BSc Aircraft Maintenance Course OverviewDocumento35 pagineBSc Aircraft Maintenance Course OverviewAyem perumalNessuna valutazione finora

- Intel® Processor PricingDocumento4 pagineIntel® Processor PricingBojan ĐenićNessuna valutazione finora

- I Am The Inventor of Windows - The Hidden Truth of MicrosoftDocumento109 pagineI Am The Inventor of Windows - The Hidden Truth of MicrosoftRonald De Herrera BarreroNessuna valutazione finora

- Ashwini Patil ASIC Verification Engr 4plusDocumento3 pagineAshwini Patil ASIC Verification Engr 4plusAshwini PatilNessuna valutazione finora

- Bannari Amman Institute of Technology Sathyamangalam - 638401 Question Paper For Model Exam Department of Electronics and Communication EngineeringDocumento3 pagineBannari Amman Institute of Technology Sathyamangalam - 638401 Question Paper For Model Exam Department of Electronics and Communication EngineeringveerakumarsNessuna valutazione finora

- Zilog PDFDocumento649 pagineZilog PDFszwzNessuna valutazione finora

- C2xx DSP CPU and Instruction Set GuideDocumento43 pagineC2xx DSP CPU and Instruction Set GuideJatin Yadav100% (2)

- 1MRB520050-Uen Operating Instructions REL316-4Documento986 pagine1MRB520050-Uen Operating Instructions REL316-4Almigdad AlwsilaNessuna valutazione finora

- The 8284a Clock GeneratorDocumento32 pagineThe 8284a Clock GeneratorBETHWEL KIPROTICH100% (1)

- Global Mission International School periodic test questionsDocumento3 pagineGlobal Mission International School periodic test questionskrupa sanandiyaNessuna valutazione finora

- CAO Syllabus PDFDocumento11 pagineCAO Syllabus PDFGokul SrinathNessuna valutazione finora

- Introduction to Microprocessor in 40 CharactersDocumento15 pagineIntroduction to Microprocessor in 40 Characterskalash satypalNessuna valutazione finora

- SINAMICS G Speed Control of A G120 (Startdrive) With S7-1500Documento48 pagineSINAMICS G Speed Control of A G120 (Startdrive) With S7-1500Juan Carlos AlconNessuna valutazione finora

- Intro To C++ Programming and Computer OrganizationDocumento53 pagineIntro To C++ Programming and Computer OrganizationZzxNessuna valutazione finora

- Embedded Systems ProgrammingDocumento34 pagineEmbedded Systems ProgrammingAbdallah AdelNessuna valutazione finora

- Modicon PLC CPUS Technical Details.Documento218 pagineModicon PLC CPUS Technical Details.TrbvmNessuna valutazione finora

- EEC 117 Computer Hardware 1Documento100 pagineEEC 117 Computer Hardware 1Kalu Samuel100% (10)

- Global Digimon Online Server Error at A Time To Time BasisDocumento3 pagineGlobal Digimon Online Server Error at A Time To Time BasisEnrick Janz Avee LloretNessuna valutazione finora

- User manual for Trumpf lasers with Siemens sinumeric 840d controlDocumento13 pagineUser manual for Trumpf lasers with Siemens sinumeric 840d controlAnonymous OTmNmCLNessuna valutazione finora

- AssignmentDocumento29 pagineAssignmentBala KrishnanNessuna valutazione finora

- Microprocessor and Microcontroller Course OverviewDocumento3 pagineMicroprocessor and Microcontroller Course OverviewTarun Gupta0% (1)

- Inca 80 XPDocumento2 pagineInca 80 XPafaqueNessuna valutazione finora

- Structure and Functions of CPUDocumento18 pagineStructure and Functions of CPUEswin AngelNessuna valutazione finora