Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

DS2430

Caricato da

giulian2009Descrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

DS2430

Caricato da

giulian2009Copyright:

Formati disponibili

256-Bit 1-Wire

www.dalsemi.com

TM

DS2430A EEPROM

FEATURES

256-bit Electrically Erasable Programmable Read Only Memory (EEPROM) plus 64-bit one-time programmable application register Unique, factory-lasered and tested 64-bit registration number (8-bit family code + 48-bit serial number + 8-bit CRC tester) assures absolute identity because no two parts are alike Built-in multidrop controller ensures compatibility with other MicroLAN products EEPROM organized as one page of 32 bytes for random access Reduces control, address, data and power to a single data pin Directly connects to a single port pin of a microprocessor and communicates at up to 16.3 kbits per second 8-bit family code specifies DS2430A communication requirements to reader Presence detector acknowledges when reader first applies voltage Low cost TO-92 or 6-pin TSOC surface mount package Reads and writes over a wide voltage range of 2.8V to 6.0V from -40C to +85C

PIN ASSIGNMENT

TO-92

DALLAS DS2430A

TSOC PACKAGE

1 2 3 6 5 4

TOP VIEW 3.7 X 4.0 X 1.5 mm

1 2 3

SIDE VIEW See Mech. Drawing Section

1 2 3

BOTTOM VIEW See Mech. Drawings Section

PIN DESCRIPTION

Pin 1 Pin 2 Pin 3 Pin 4 Pin 5 Pin 6 TO-92 Ground Data NC TSOC Ground Data NC NC NC

ORDERING INFORMATION

DS2430A DS2430AP DS2430AT DS2430AV DS2430AX TO-92 package 6-pin TSOC package Tape & Reel version of DS2430A Tape & Reel version of DS2430AP Chip Scale Pkg., Tape & Reel

1 of 16

102199

DS2430A

SILICON LABEL DESCRIPTION

The DS2430A 256-bit 1-Wire EEPROM identifies and stores relevant information about the product to which it is associated. This lot or product specific information can be accessed with minimal interface, for example a single port pin of a microcontroller. The DS2430A consists of a factory-lasered registration number that includes a unique 48-bit serial number, an 8-bit CRC, and an 8-bit Family Code (14h) plus 256 bits of user-programmable EEPROM and a 64-bit one-time programmable application register. The power to read and write the DS2430A is derived entirely from the 1-Wire communication line. Data is transferred serially via the 1-Wire protocol which requires only a single data lead and a ground return. The 48-bit serial number that is factory-lasered into each DS2430A provides a guaranteed unique identity which allows for absolute traceability. The TO-92 and TSOC packages provide a compact enclosure that allows standard assembly equipment to handle the device easily for attachment to printed circuit boards or wiring. Typical applications include storage of calibration constants, board identification and product revision status.

OVERVIEW

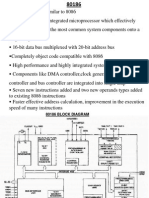

The block diagram in Figure 1 shows the relationships between the major control and memory sections of the DS2430A. The DS2430A has four main data components: 1) 64-bit lasered ROM, 2) 256-bit EEPROM data memory with scratchpad, 3) 64-bit one-time programmable application register with scratchpad and 4) 8-bit Status Memory. The hierarchical structure of the 1-Wire protocol is shown in Figure 2. The bus master must first provide one of the four ROM Function Commands: 1) Read ROM, 2) Match ROM, 3) Search ROM, 4) Skip ROM. The protocol required for these ROM Function Commands is described in Figure 8. After a ROM Function Command is successfully executed, the memory functions become accessible and the master may provide any one of the four memory function commands. The protocol for these memory function commands is described in Figure 6. All data is read and written least significant bit first.

64-BIT LASERED ROM

Each DS2430A contains a unique ROM code that is 64 bits long. The first 8 bits are a 1-Wire family code (14h). The next 48 bits are a unique serial number. The last 8 bits are a CRC of the first 56 bits. (Figure 3). The 1-Wire CRC is generated using a polynomial generator consisting of a shift register and XOR gates as shown in Figure 4. The polynomial is X8 + X5 + X4 + 1. Additional information about the Dallas 1-Wire Cyclic Redundancy Check is available in the Book of DS19xx iButton Standards. The shift register bits are initialized to 0. Then starting with the least significant bit of the family code, 1 bit at a time is shifted in. After the 8th bit of the family code has been entered, then the serial number is entered. After the 48th bit of the serial number has been entered, the shift register contains the CRC value. Shifting in the 8 bits of CRC should return the shift register to all 0s.

2 of 16

102199

DS2430A

DS2430A BLOCK DIAGRAM Figure 1

3 of 16

102199

DS2430A

HIERARCHICAL STRUCTURE FOR 1-WIRE PROTOCOL Figure 2

64-BIT LASERED ROM Figure 3

8-Bit CRC Code MSB LSB MSB 48-Bit Serial Number 8-Bit Family Code (14H) LSB MSB LSB

1-WIRE CRC GENERATOR Figure 4

Polynomial = X8 + X5 + X4 + 1

4 of 16

102199

DS2430A

MEMORY

The memory of the DS2430A consists of three separate sections, called data memory, application register and status register (Figure 5). The data memory and the application register each has its own intermediate storage area called scratchpad that acts as a buffer when writing to the device. The data memory can be read and written as often as desired. The application register, however, is one-time programmable only. Once the application register is programmed, it is automatically write protected. The status register will indicate if the application register is already locked or if it is still available for storing data. As long as the application register is unprogrammed, the status register will read FFh. Copying data from the register scratchpad to the application register will clear the 2 least significant bits of the status register, yielding a FCh the next time one reads the status register.

DS2430A MEMORY MAP Figure 5

MEMORY FUNCTION COMMANDS

The Memory Function Flow Chart (Figure 6) describes the protocols necessary for accessing the different memory sections of the DS2430A. An example is shown later in this document.

WRITE SCRATCHPAD [0Fh]

After issuing the Write Scratchpad command, the master must first provide a 1-byte address, followed by the data to be written to the scratchpad for the data memory. The DS2430A will automatically increment the address after every byte it received. After having received a data byte for address 1Fh, the address counter will wrap around to 00h for the next byte and writing continues until the master sends a reset pulse.

READ SCRATCHPAD [AAh]

This command is used to verify data previously written to the scratchpad before it is copied into the final storage EEPROM memory. After issuing the Read Scratchpad command, the master must provide the 1byte starting address from where data is to be read. The DS2430A will automatically increment the address after every byte read by the master. After the data of address 1Fh has been read, the address counter will wrap around to 00h for the next byte and reading continues until the master sends a reset pulse. 5 of 16 102199

DS2430A

MEMORY FUNCTION FLOW CHART Figure 6

COPY SCRATCHPAD [55h]

After the data stored in the scratchpad has been verified the master may send the Copy Scratchpad command followed by a validation key of A5h to transfer data from the scratchpad to the EEPROM memory. This command will always copy the data of the entire scratchpad. Therefore, if one desires to change only a few bytes of the EEPROM data, the scratchpad should contain a copy of the latest EEPROM data before the Write Scratchpad and Copy Scratchpad commands are issued. After this command is issued, the data line must be held at logic high level for at least 10 ms.

READ MEMORY [F0h]

The Read Memory command is used to read a portion or all of the EEPROM data memory and to copy the entire data memory into the scratchpad to prepare for changing a few bytes. To copy data from the data memory to the scratchpad and to read it, the master must issue the read memory command followed by the 1-byte starting address from where data is to be read from the scratchpad. The DS2430A will automatically increment the address after every byte read by the master. After the data of address 1Fh has been read, the address counter will wrap around to 00h for the next byte and reading continues until the master sends a reset pulse. If one intends to copy the entire data memory to the scratchpad without reading data, a starting address is not required; the master may send a reset pulse immediately following the command code.

6 of 16

102199

DS2430A

MEMORY FUNCTION FLOW CHART Figure 6 (cont d)

WRITE APPLICATION REGISTER [99h]

This command is essentially the same as the Write Scratchpad command, but it addresses the 64-bit register scratchpad. After issuing the command code, the master must provide a 1-byte address, followed by the data to be written. The DS2430A will automatically increment the address after every byte it received. After having received a data byte for address 07h, the address counter will wrap around to 00h for the next byte and writing continues until the master sends a reset pulse. The Write Application Register command can be used as long as the application register has not yet been locked. If issued for a device with the application register locked, the data written to the register scratchpad will be lost.

READ STATUS REGISTER [66h]

The status register is a means for the master to find out if the application register has been programmed and locked. After issuing the read status register command, the master must provide the validation key 00h before receiving status information. The two least significant bits of the 8-bit status register will be 0 if the application register was programmed and locked; all other bits will always read 1. The master may finish the read status command by sending a reset pulse at any time.

7 of 16

102199

DS2430A

MEMORY FUNCTION FLOW CHART Figure 6 (cont d)

READ APPLICATION REGISTER [C3h]

This command is used to read the application register or the register scratchpad. As long as the application register is not yet locked, one will receive data from the register scratchpad. After the application register is locked the DS2430A will transmit data from the application register, making the register scratchpad inaccessible for reading. The contents of the status register indicates where the data received with this command came from. After issuing the Read Application Register command, the master must provide the 1-byte starting address from where data is to be read. The DS2430A will automatically increment the address after every byte read by the master. After the data of address 07h has been read, the address counter will wrap around to 00h for the next byte and reading continues until the master sends a reset pulse.

COPY & LOCK APPLICATION REGISTER [5Ah]

After the data stored in the register scratchpad has been verified the master may send the Copy & Lock Application Register command followed by a validation key of A5h to transfer the contents of the entire register scratchpad to the application register and to simultaneously write-protect it. The master may cancel this command by sending a reset pulse instead of the validation key. After the validation key was transmitted, the application register will contain the data of the register scratchpad. Further write accesses to the application register will be denied. The Copy & Lock Application Register command can only be executed once.

8 of 16

102199

DS2430A

1-WIRE BUS SYSTEM

The 1-Wire bus is a system which has a single bus master and one or more slaves. In all instances, the DS2430A is a slave device. The bus master is typically a microcontroller. The discussion of this bus system is broken down into three topics: hardware configuration, transaction sequence, and 1-Wire signaling (signal type and timing). A 1-Wire protocol defines bus transactions in terms of the bus state during specified time slots that are initiated on the falling edge of sync pulses from the bus master. For a more detailed protocol description, refer to Chapter 4 of the Book of DS19xx iButton Standards.

Hardware Configuration

The 1-Wire bus has only a single line by definition; it is important that each device on the bus be able to drive it at the appropriate time. To facilitate this, each device attached to the 1-Wire bus must have open drain connection or 3-state outputs. The 1-Wire port of the DS2430A is open drain with an internal circuit equivalent to that shown in Figure 7. A multidrop bus consists of a 1-Wire bus with multiple slaves attached. The 1-Wire bus has a maximum data rate of 16.3k bits per second and requires a pullup resistor of approximately 5 k . The idle state for the 1-Wire bus is high. If for any reason a transaction needs to be suspended, the bus MUST be left in the idle state if the transaction is to resume. If this does not occur and the bus is left low for more than 120 s, one or more of the devices on the bus may be reset.

HARDWARE CONFIGURATION Figure 7

*5 k is adequate for reading the DS2430A. To write to a single device, a 2.2 k resistor and VPUP of at least 4.0V is sufficient. For writing multiple DS2430As simultaneously or operation at low VPUP, the resistor should be bypassed by a low-impedance pullup to VPUP while the device copies the scratchpad to EEPROM. 9 of 16 102199

DS2430A

ROM FUNCTIONS FLOW CHART Figure 8

10 of 16

102199

DS2430A

Transaction Sequence

The sequence for accessing the DS2430A via the 1-Wire port is as follows: Initialization ROM Function Command Memory Function Command Transaction/Data

INITIALIZATION

All transactions on the 1-Wire bus begin with an initialization sequence. The initialization sequence consists of a reset pulse transmitted by the bus master followed by a presence pulse(s) transmitted by the slave(s). The presence pulse lets the bus master know that the DS2430A is on the bus and is ready to operate. For more details, see the 1-Wire Signaling section.

ROM FUNCTION COMMANDS

Once the bus master has detected a presence, it can issue one of the four ROM function commands. All ROM function commands are 8 bits long. A list of these commands follows (refer to flowchart in Figure 8):

Read ROM [33h]

This command allows the bus master to read the DS2430A s 8-bit family code, unique 48-bit serial number, and 8-bit CRC. This command can be used only if there is a single DS2430A on the bus. If more than one slave is present on the bus, a data collision will occur when all slaves try to transmit at the same time (open drain will produce a wired-AND result). The resultant family code and 48-bit serial number will usually result in a mismatch of the CRC.

Match ROM [55h]

The Match ROM command, followed by a 64-bit ROM sequence, allows the bus master to address a specific DS2430A on a multidrop bus. Only the DS2430A that exactly matches the 64-bit ROM sequence will respond to the subsequent memory function command. All slaves that do not match the 64-bit ROM sequence will wait for a reset pulse. This command can be used with a single or multiple devices on the bus.

Skip ROM [CCh]

This command can save time in a single-drop bus system by allowing the bus master to access the memory functions without providing the 64-bit ROM code. If more than one slave is present on the bus and a read command is issued following the Skip ROM command, data collision will occur on the bus as multiple slaves transmit simultaneously (open drain pulldowns will produce a wired-AND result).

Search ROM [F0h]

When a system is initially brought up, the bus master might not know the number of devices on the 1Wire bus or their 64-bit ROM codes. The Search ROM command allows the bus master to use a process of elimination to identify the 64-bit ROM codes of all slave devices on the bus. The Search ROM process is the repetition of a simple, three-step routine: read a bit, read the complement of the bit, then write the desired value of that bit. The bus master performs this simple, three-step routine on each bit of the ROM. 11 of 16 102199

DS2430A

After one complete pass, the bus master knows the contents of the ROM in one device. The remaining number of devices and their ROM codes may be identified by additional passes. See Chapter 5 of the Book of DS19xx iButton Standards for a comprehensive discussion of a search ROM, including an actual example.

1-Wire Signaling

The DS2430A requires strict protocols to insure data integrity. The protocol consists of four types of signaling on one line: Reset Sequence with Reset Pulse and Presence Pulse, Write 0, Write 1 and Read Data. All these signals except presence pulse are initiated by the bus master. The initialization sequence required to begin any communication with the DS2430A is shown in Figure 9. A reset pulse followed by a presence pulse indicates the DS2430A is ready to accept a ROM command. The bus master transmits (TX) a reset pulse (tRSTL, minimum 480 s). The bus master then releases the line and goes into receive mode (RX). The 1-Wire bus is pulled to a high state via the pullup resistor. After detecting the rising edge on the data pin, the DS2430A waits (tPDH, 15-60 s) and then transmits the presence pulse (tPDL, 60-240 s).

INITIALIZATION PROCEDURE RESET AND PRESENCE PULSES Figure 9

In order not to mask interrupt signaling by other devices on the 1-Wire bus, tRSTL + tR should always be less than 960 s.

Read/Write Time Slots

The definitions of write and read time slots are illustrated in Figure 10. All time slots are initiated by the master driving the data line low. The falling edge of the data line synchronizes the DS2430A to the master by triggering a delay circuit in the DS2430A. During write time slots, the delay circuit determines when the DS2430A will sample the data line. For a read data time slot, if a 0 is to be transmitted, the delay circuit determines how long the DS2430A will hold the data line low overriding the 1 generated by the master. If the data bit is a 1, the DS2430A will leave the read data time slot unchanged.

12 of 16

102199

DS2430A

READ/WRITE TIMING DIAGRAM Figure 10

Write-1 Time Slot

Write-0 Time Slot

Read-data Time Slot

13 of 16

102199

DS2430A

MEMORY FUNCTION EXAMPLE

Example: Write 2 data bytes to data memory location 0006 and 0007. Read entire data memory. MASTER MODE TX RX TX TX TX RX TX TX TX TX TX RX TX TX TX RX TX RX TX TX TX TX TX RX TX TX TX RX TX RX DATA (LSB FIRST) Reset Presence CCh F0h Reset Presence CCh 0Fh 06h <2 data bytes> Reset Presence CCh AAh 06h <2 data bytes> Reset Presence CCh 55h A5h <data line high> Reset Presence CCh F0h 00h <32 bytes> Reset Presence COMMENTS Reset pulse (480-960 s) Presence pulse Issue Skip ROM command Issue Read Memory command Reset pulse (480-960 s) Presence pulse Issue Skip ROM command Issue Write Scratchpad command Start address = 06h Write 2 bytes of data to scratchpad Reset pulse Presence pulse Issue Skip ROM command Issue Read Scratchpad command Start address = 06h Read scratchpad data and verify Reset pulse Presence pulse Issue Skip ROM command Issue Copy Scratchpad command Validation key Data line is held high for 10 ms by the bus master to provide energy for copying data from the scratchpad to EEPROM Reset pulse Presence pulse Issue Skip ROM command Issue Read Memory command Start address = 00h Read EEPROM data page Reset pulse Presence pulse

14 of 16

102199

DS2430A

ABSOLUTE MAXIMUM RATINGS*

Voltage on DATA to Ground Operating Temperature Storage Temperature Soldering Temperature * -0.5V to +7.0V -40C to +85C -55C to +125C 260C for 10 seconds

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

DC ELECTRICAL CHARACTERISTICS

PARAMETER Logic 1 Logic 0 Output Logic Low @ 4 mA Output Logic High Input Load Current (DATA pin) Programming Current SYMBOL VIH VIL VOL VOH IL IP MIN 2.2 -0.3

(-40C to +85C; VPUP=2.8V to 6.0V)

TYP MAX +0.8 0.4 6.0 500 UNITS V V V V A A NOTES 1, 6 1, 9 1 1, 2 3

VPUP 5

CAPACITANCE

PARAMETER Capacitance SYMBOL CD MIN TYP MAX 800 UNITS pF

(tA =25C)

NOTES 7

ENDURANCE

PARAMETER Write/Erase Cycles SYMBOL NCYCLE MIN 100k TYP

(VPUP=5.0V; tA =25C)

MAX UNITS NOTES 10

AC ELECTRICAL CHARACTERISTICS

PARAMETER Time Slot Write 1 Low Time Write 0 Low Time Read Low Time Read Data Valid Release Time Read Data Setup Recovery Time Reset Time High Reset Time Low Presence Detect High Presence Detect Low Programming Time SYMBOL tSLOT tLOW1 tLOW0 tLOWR tRDV tRELEASE tSU tREC tRSTH tRSTL tPDH tPDL tPROG MIN 60 1 60 1 0 1 480 480 15 60

(-40C to +85C; VPUP=2.8V to 6.0V)

TYP MAX 120 15 120 15 45 1 UNITS s s s s s s s s s s s s ms NOTES

exactly 15 15

5 4 8

5000 60 240 10

15 of 16

102199

DS2430A

NOTES:

1. All voltages are referenced to ground. 2. VPUP=external pullup voltage. 3. Input load is to ground. 4. An additional reset or communication sequence cannot begin until the reset high time has expired. 5. Read data setup time refers to the time the host must pull the 1-Wire bus low to read a bit. Data is guaranteed to be valid within 1 s of this falling edge. 6. VIH is a function of the external pullup resistor and VPUP. 7. Capacitance on the data pin could be 800 pF when power is first applied. If a 5 k resistor is used to pull up the data line to VPUP, 5 s after power has been applied the parasite capacitance will not affect normal communications. 8. tRSTL should be limited to maximum 5 ms. Otherwise the DS2430A may perform a power-on reset. 9. Under certain low voltage conditions VILMAX may have to be reduced to as much as 0.5V to always guarantee a presence pulse. 10. The Copy Scratchpad takes 10 ms maximum, during which the voltage on the 1-Wire bus must not fall below 2.8V.

16 of 16

102199

Potrebbero piacerti anche

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDa EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNessuna valutazione finora

- DS2430A 256-Bit 1-Wire Eeprom: Features Pin AssignmentDocumento16 pagineDS2430A 256-Bit 1-Wire Eeprom: Features Pin Assignmentjose ambiorixNessuna valutazione finora

- Micro ControllersDocumento141 pagineMicro ControllersBiswajit SarkarNessuna valutazione finora

- L24C32Documento14 pagineL24C32mpapamicNessuna valutazione finora

- DS2506 64Kb Add-Only Memory: Features Pin AssignmentDocumento25 pagineDS2506 64Kb Add-Only Memory: Features Pin AssignmentFariasNessuna valutazione finora

- OBJECT COUNTING CONVEYORDocumento42 pagineOBJECT COUNTING CONVEYORMayilai AshokNessuna valutazione finora

- Interfacing Devices Memory Devices and Interfacing Interfacing DevicesDocumento14 pagineInterfacing Devices Memory Devices and Interfacing Interfacing DevicesShilpa ShettyNessuna valutazione finora

- 24C 04Documento15 pagine24C 04Diego AsiconaNessuna valutazione finora

- Atmega ArchitectureDocumento18 pagineAtmega ArchitecturevigneshthegreatNessuna valutazione finora

- TMS320C4X Digital Signal ProcessingDocumento12 pagineTMS320C4X Digital Signal ProcessingRamasubramanian Subramanian100% (1)

- NotesDocumento21 pagineNotesShinisg Vava50% (2)

- 1 Wire Command SetDocumento46 pagine1 Wire Command SetAmarjith ValancheryNessuna valutazione finora

- Computer Architecture: Assignment: 80X86 FamilyDocumento17 pagineComputer Architecture: Assignment: 80X86 FamilyAnjan KumarNessuna valutazione finora

- Datasheet Eeprom Mototrbo Impres Ds2433Documento19 pagineDatasheet Eeprom Mototrbo Impres Ds2433py5rcbNessuna valutazione finora

- Microprocessor AnswerDocumento4 pagineMicroprocessor AnswerHacker hai kya BhosdikeNessuna valutazione finora

- Control Unit - 89C52: Introduction About Micro ControllerDocumento20 pagineControl Unit - 89C52: Introduction About Micro ControllerSubhashini AruchamyNessuna valutazione finora

- The Microprocessor & Its Architecture: by Engr: Shah Rehan AliDocumento39 pagineThe Microprocessor & Its Architecture: by Engr: Shah Rehan AliUsman SaeedNessuna valutazione finora

- G MPMC U4 Rit 150 CopiesDocumento19 pagineG MPMC U4 Rit 150 CopiesBobby SatyaNessuna valutazione finora

- Amm Cheet PrintDocumento7 pagineAmm Cheet PrintjokerNessuna valutazione finora

- Microprocessor 80386Documento40 pagineMicroprocessor 80386eshwar_worldNessuna valutazione finora

- Lecture#2 Fut Microprocessor PDFDocumento81 pagineLecture#2 Fut Microprocessor PDFAhmedGamalNessuna valutazione finora

- Microprocessor ArchitectureDocumento23 pagineMicroprocessor Architectureganesh6583Nessuna valutazione finora

- The M68000 Educational Computer BoardDocumento13 pagineThe M68000 Educational Computer BoardPanos BriniasNessuna valutazione finora

- Memory Interfacing 8086 Good and UsefulDocumento39 pagineMemory Interfacing 8086 Good and UsefulSatish GuptaNessuna valutazione finora

- Mic ProjectDocumento15 pagineMic Projectsudarshan sonawaneNessuna valutazione finora

- Introduction of Moving Message Display Using Liquid Crystal Display and Micro Controller 8051 FamilyDocumento13 pagineIntroduction of Moving Message Display Using Liquid Crystal Display and Micro Controller 8051 Familyishu58643Nessuna valutazione finora

- 8086 Third Term TopicsDocumento46 pagine8086 Third Term TopicsgandharvsikriNessuna valutazione finora

- Unit 3 MicroprocessorDocumento155 pagineUnit 3 MicroprocessorHUISCINessuna valutazione finora

- Doc-A.14-Text Editor On A LCD Using At89c51 Micro Controller and KeyboardDocumento48 pagineDoc-A.14-Text Editor On A LCD Using At89c51 Micro Controller and KeyboardRockson Kwame AgyemanNessuna valutazione finora

- Advanced Microprocessors: 80386 FeaturesDocumento14 pagineAdvanced Microprocessors: 80386 FeaturesSwamy NallabelliNessuna valutazione finora

- 8051 NotesDocumento24 pagine8051 Notessreedhar_vkNessuna valutazione finora

- Unit-I: - 80386 IntroductionDocumento74 pagineUnit-I: - 80386 IntroductionOmkar MarkadNessuna valutazione finora

- CS18303 Microprocessor and Microcontroller Lecture NotesDocumento160 pagineCS18303 Microprocessor and Microcontroller Lecture NotesDeepak SrinivasNessuna valutazione finora

- Microprocessor NotesDocumento140 pagineMicroprocessor NotesSaquibh ShaikhNessuna valutazione finora

- 80386Documento89 pagine80386chandanayadav849050% (2)

- 184 Pin 512mb 1g Unbuffered DDR Dimm Pc3200 DsDocumento9 pagine184 Pin 512mb 1g Unbuffered DDR Dimm Pc3200 DsKiran VeesamNessuna valutazione finora

- AMI CHP 1 32bit 80386 FinalDocumento59 pagineAMI CHP 1 32bit 80386 FinalAliNessuna valutazione finora

- MicroprocessorDocumento103 pagineMicroprocessorUbaid SaudagarNessuna valutazione finora

- 80486Documento34 pagine80486Manoj RayNessuna valutazione finora

- Lecture 4Documento22 pagineLecture 4qasimNessuna valutazione finora

- 2.1 LPC2129 Microcontroller: 2.1.1 FeaturesDocumento14 pagine2.1 LPC2129 Microcontroller: 2.1.1 FeaturesBhaskar Rao PNessuna valutazione finora

- Chapter-6 Data MemoryDocumento9 pagineChapter-6 Data MemoryPrathyusha ReddyNessuna valutazione finora

- Architecture of 80386Documento39 pagineArchitecture of 80386Jaimon JacobNessuna valutazione finora

- The Complete Understanding of Microprocessors and Intro To ARMDocumento56 pagineThe Complete Understanding of Microprocessors and Intro To ARMasimNessuna valutazione finora

- Pic MicrocontrollerDocumento14 paginePic Microcontrollermsubashece001Nessuna valutazione finora

- FEATURES OF 80386:: 2) Address 4GB of Memory 2) 16 MB ofDocumento39 pagineFEATURES OF 80386:: 2) Address 4GB of Memory 2) 16 MB ofJ VNessuna valutazione finora

- 32 - Bit Microprocessor-Intel 80386Documento71 pagine32 - Bit Microprocessor-Intel 80386Ibtisam Anwar KhattakNessuna valutazione finora

- 80486 Microprocessor: 32-Bit CPU with Integrated Math CoprocessorDocumento34 pagine80486 Microprocessor: 32-Bit CPU with Integrated Math CoprocessorlashmaNessuna valutazione finora

- Direct Memory Access (DMA) and The DMA Controller (DMAC) 8237Documento24 pagineDirect Memory Access (DMA) and The DMA Controller (DMAC) 8237abu sayedNessuna valutazione finora

- University Institute of EnggDocumento28 pagineUniversity Institute of EnggMeghna ChatterjeeNessuna valutazione finora

- UNIT-V-TMS320C54x-DSP ProcessorDocumento47 pagineUNIT-V-TMS320C54x-DSP ProcessorVasant DivekarNessuna valutazione finora

- MP-MC R16 - Unit-4Documento14 pagineMP-MC R16 - Unit-4satyanarayana12Nessuna valutazione finora

- Introdution To The DsPIC30FDocumento17 pagineIntrodution To The DsPIC30Fboyluca100% (1)

- Microprocessor Short Question AnswersDocumento50 pagineMicroprocessor Short Question AnswersHamza IqbalNessuna valutazione finora

- 8086 Min Max Mode Operations ModifiedDocumento78 pagine8086 Min Max Mode Operations ModifiedRitu RathiNessuna valutazione finora

- Pentium ArchitectureDocumento18 paginePentium ArchitectureMary HarrisonNessuna valutazione finora

- Operation Manual Modbus MasterDocumento17 pagineOperation Manual Modbus MasterMiguel PozoNessuna valutazione finora

- The Programmable Keyboard Display Interface - 8279Documento23 pagineThe Programmable Keyboard Display Interface - 8279Pranav MpNessuna valutazione finora

- Protected Address Mode Software Architecture of 80386dxDocumento29 pagineProtected Address Mode Software Architecture of 80386dxSanjivanee KumbharNessuna valutazione finora

- Read Me Slave 2.1Documento7 pagineRead Me Slave 2.1Prasad VylaleNessuna valutazione finora

- Autoclav Sterivap BMT Operating InstructionsDocumento9 pagineAutoclav Sterivap BMT Operating Instructionsgiulian2009Nessuna valutazione finora

- Weinmann Oxymat 3 Oxygen Concentrator - Service ManualDocumento84 pagineWeinmann Oxymat 3 Oxygen Concentrator - Service Manualgiulian2009100% (5)

- Care and Safe Use of Hospital EquipmentDocumento200 pagineCare and Safe Use of Hospital Equipmentgiulian2009Nessuna valutazione finora

- Iwaki BrochureDocumento2 pagineIwaki Brochuregiulian2009Nessuna valutazione finora

- 1500mAh lithium-ion cell specificationsDocumento1 pagina1500mAh lithium-ion cell specificationsgiulian2009Nessuna valutazione finora

- 123456 positivity guideDocumento1 pagina123456 positivity guidegiulian2009Nessuna valutazione finora

- Hill-Rom Evolution Bed - User ManualDocumento60 pagineHill-Rom Evolution Bed - User Manualgiulian2009Nessuna valutazione finora

- Hill-Rom TotalCare - User ManualDocumento50 pagineHill-Rom TotalCare - User Manualgiulian2009Nessuna valutazione finora

- Toshiba Satellite l300d (Inventec Ps10a - 6050a2174501)Documento54 pagineToshiba Satellite l300d (Inventec Ps10a - 6050a2174501)drop9721100% (1)

- 123456 positivity guideDocumento1 pagina123456 positivity guidegiulian2009Nessuna valutazione finora

- Operators Manual Dms Holter Recorder 300-3 and 300-4: October 2005Documento17 pagineOperators Manual Dms Holter Recorder 300-3 and 300-4: October 2005giulian2009Nessuna valutazione finora

- IWAKI Bellows Pump Instruction ManualDocumento12 pagineIWAKI Bellows Pump Instruction Manualgiulian2009Nessuna valutazione finora

- Digital Holter Recorder Service Manual and Troubleshooting GuideDocumento15 pagineDigital Holter Recorder Service Manual and Troubleshooting Guidegiulian2009Nessuna valutazione finora

- Lifepak CR Plus Lifepak Express: Operating InstructionsDocumento78 pagineLifepak CR Plus Lifepak Express: Operating InstructionsMattNessuna valutazione finora

- Erbe Erbotom ACC450 - ServicemanualDocumento220 pagineErbe Erbotom ACC450 - Servicemanualgiulian2009100% (2)

- Power Supply PC ©Documento35 paginePower Supply PC ©salbog333roNessuna valutazione finora

- DC-6 Operation Manual Basic CE V1.1Documento149 pagineDC-6 Operation Manual Basic CE V1.1giulian2009100% (1)

- DC-6 Operation Manual Basic CE V1.1Documento149 pagineDC-6 Operation Manual Basic CE V1.1giulian2009100% (1)

- Cars Refrigerant Oil Filling QuantitiesDocumento92 pagineCars Refrigerant Oil Filling QuantitiesMahmoud MohamedNessuna valutazione finora

- Cosmed Pony Graphic - User ManualDocumento110 pagineCosmed Pony Graphic - User Manualgiulian2009Nessuna valutazione finora

- Sonosite c1.99 Elite Service ManDocumento0 pagineSonosite c1.99 Elite Service Mangiulian2009Nessuna valutazione finora

- Cars Refrigerant Oil Filling QuantitiesDocumento92 pagineCars Refrigerant Oil Filling QuantitiesMahmoud MohamedNessuna valutazione finora

- User & Service Manual: QA-90 Electrical Safety AnalyzerDocumento82 pagineUser & Service Manual: QA-90 Electrical Safety Analyzerjose_barradas_1Nessuna valutazione finora

- Microscopy From The Very Beginning (Zeiss)Documento48 pagineMicroscopy From The Very Beginning (Zeiss)Eric LaloumNessuna valutazione finora

- Stunning Photoshop WorksDocumento23 pagineStunning Photoshop Worksgiulian2009Nessuna valutazione finora

- SCX-4x21 EnglishDocumento120 pagineSCX-4x21 Englishvladimir100% (2)

- Requesting A Query in Zemanta Using PHPDocumento10 pagineRequesting A Query in Zemanta Using PHPAther SajjadNessuna valutazione finora

- Trading As A BusinessDocumento169 pagineTrading As A Businesspetefader100% (1)

- Exercises 6 Workshops 9001 - WBP1Documento1 paginaExercises 6 Workshops 9001 - WBP1rameshqcNessuna valutazione finora

- CR Vs MarubeniDocumento15 pagineCR Vs MarubeniSudan TambiacNessuna valutazione finora

- Krok2 - Medicine - 2010Documento27 pagineKrok2 - Medicine - 2010Badriya YussufNessuna valutazione finora

- Evolution of Bluetooth PDFDocumento2 pagineEvolution of Bluetooth PDFJuzerNessuna valutazione finora

- Panel Data Econometrics: Manuel ArellanoDocumento5 paginePanel Data Econometrics: Manuel Arellanoeliasem2014Nessuna valutazione finora

- Case Study Hotel The OrchidDocumento5 pagineCase Study Hotel The Orchidkkarankapoor100% (4)

- Traffic LightDocumento19 pagineTraffic LightDianne ParNessuna valutazione finora

- Decision Maths 1 AlgorithmsDocumento7 pagineDecision Maths 1 AlgorithmsNurul HafiqahNessuna valutazione finora

- Maverick Brochure SMLDocumento16 pagineMaverick Brochure SMLmalaoui44Nessuna valutazione finora

- Interpretation of Arterial Blood Gases (ABGs)Documento6 pagineInterpretation of Arterial Blood Gases (ABGs)afalfitraNessuna valutazione finora

- Simply Put - ENT EAR LECTURE NOTESDocumento48 pagineSimply Put - ENT EAR LECTURE NOTESCedric KyekyeNessuna valutazione finora

- Lifespan Development Canadian 6th Edition Boyd Test BankDocumento57 pagineLifespan Development Canadian 6th Edition Boyd Test Bankshamekascoles2528zNessuna valutazione finora

- GROSS DOMESTIC PRODUCT STATISTICS (Report) - Powerpoint PresentationDocumento37 pagineGROSS DOMESTIC PRODUCT STATISTICS (Report) - Powerpoint PresentationCyryhl GutlayNessuna valutazione finora

- Zelev 1Documento2 pagineZelev 1evansparrowNessuna valutazione finora

- Marine Engineering 1921Documento908 pagineMarine Engineering 1921Samuel Sneddon-Nelmes0% (1)

- Android software download guideDocumento60 pagineAndroid software download guideRizky PradaniNessuna valutazione finora

- Sri S T Kalairaj, Chairman: Income Tax TaxesDocumento3 pagineSri S T Kalairaj, Chairman: Income Tax TaxesvikramkkNessuna valutazione finora

- IGCSE Chemistry Section 5 Lesson 3Documento43 pagineIGCSE Chemistry Section 5 Lesson 3Bhawana SinghNessuna valutazione finora

- #### # ## E232 0010 Qba - 0Documento9 pagine#### # ## E232 0010 Qba - 0MARCONessuna valutazione finora

- C6030 BrochureDocumento2 pagineC6030 Brochureibraheem aboyadakNessuna valutazione finora

- Coffee Table Book Design With Community ParticipationDocumento12 pagineCoffee Table Book Design With Community ParticipationAJHSSR JournalNessuna valutazione finora

- Estimation of Working CapitalDocumento12 pagineEstimation of Working CapitalsnehalgaikwadNessuna valutazione finora

- 5054 w11 QP 11Documento20 pagine5054 w11 QP 11mstudy123456Nessuna valutazione finora

- GIS Multi-Criteria Analysis by Ordered Weighted Averaging (OWA) : Toward An Integrated Citrus Management StrategyDocumento17 pagineGIS Multi-Criteria Analysis by Ordered Weighted Averaging (OWA) : Toward An Integrated Citrus Management StrategyJames DeanNessuna valutazione finora

- Site Visit Risk Assessment FormDocumento3 pagineSite Visit Risk Assessment FormAmanuelGirmaNessuna valutazione finora

- Evaluating Sources IB Style: Social 20ib Opvl NotesDocumento7 pagineEvaluating Sources IB Style: Social 20ib Opvl NotesRobert ZhangNessuna valutazione finora

- Bluetooth TutorialDocumento349 pagineBluetooth Tutorialjohn bougsNessuna valutazione finora

- Progressive Myoclonic Epilepsies - Practical Neurology 2015. MalekDocumento8 pagineProgressive Myoclonic Epilepsies - Practical Neurology 2015. MalekchintanNessuna valutazione finora