Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

CD4040BCN

Caricato da

auto1265Descrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

CD4040BCN

Caricato da

auto1265Copyright:

Formati disponibili

CD4020BC CD4040BC CD4060BC 14-Stage Ripple Carry Binary Counters 12-Stage Ripple Carry Binary Counters 14-Stage Ripple

pple Carry Binary Counters

October 1987 Revised January 2004

CD4020BC CD4040BC CD4060BC 14-Stage Ripple Carry Binary Counters 12-Stage Ripple Carry Binary Counters 14-Stage Ripple Carry Binary Counters

General Description

The CD4020BC, CD4060BC are 14-stage ripple carry binary counters, and the CD4040BC is a 12-stage ripple carry binary counter. The counters are advanced one count on the negative transition of each clock pulse. The counters are reset to the zero state by a logical 1 at the reset input independent of clock.

Features

I Wide supply voltage range: 3.0V to 15V I High noise immunity: 0.45 VDD (typ.) I Low power TTL compatibility: or 1 driving 74LS I Schmitt trigger clock input Fan out of 2 driving 74L

I Medium speed operation: 8 MHz typ. at VDD = 10V

Ordering Code:

Order Number CD4020BCM CD4020BCN CD4040BCM CD4040BCN CD4060BCM CD4060BCN Package Number M16A N16E M16A N16E M16A N16E Package Description 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter X to the ordering code.

Connection Diagrams

Pin Assignments for DIP and SOIC CD4020BC Pin Assignments for DIP and SOIC CD4040BC

Top View

Top View

2004 Fairchild Semiconductor Corporation

DS005953

www.fairchildsemi.com

CD4020BC CD4040BC CD4060BC

Connection Diagrams

(Continued) Pin Assignments for DIP and SOIC CD4060BC

Top View

Schematic Diagrams

CD4020BC

CD4040BC

www.fairchildsemi.com

CD4020BC CD4040BC CD4060BC

Schematic Diagrams

(Continued) CD4060BC

CD4060B Typical Oscillator Connections

RC Oscillator

Crystal Oscillator

www.fairchildsemi.com

CD4020BC CD4040BC CD4060BC

Absolute Maximum Ratings(Note 1)

(Note 2) Supply Voltage (VDD ) Input Voltage (VIN) Storage Temperature Range (TS) Package Dissipation (PD) Dual-In-Line Small Outline Lead Temperature (TL) (Soldering, 10 seconds) 260 C 700 mW 500 mW

Recommended Operating Conditions

Supply Voltage (VDD) Input Voltage (VIN) Operating Temperature Range (TA)

0.5V to +18V 0.5V to VDD +0.5V 65C to +150 C

+3V to +15V

0V to VDD

55C to +125C

Note 1: Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The tables of Recommended Operating Conditions and Electrical Characteristics provide conditions for actual device operation. Note 2: VSS = 0V unless otherwise specified.

DC Electrical Characteristics (Note 2)

Symbol IDD Parameter Quiescent Device Current Conditions VDD = 5V, VIN = VDD or VSS VDD = 10V, VIN = V DD or VSS VDD = 15V, VIN = V DD or VSS VOL LOW Level Output Voltage VDD = 5V VDD = 10V VDD = 15V VOH HIGH Level Output Voltage VDD = 5V VDD = 10V VDD = 15V VIL LOW Level Input Voltage VDD = 5V, VO = 0.5V or 4.5V VDD = 10V, VO = 1.0V or 9.0V VDD = 15V, VO = 1.5V or 13.5V VIH HIGH Level Input Voltage VDD = 5V, VO = 0.5V or 4.5V VDD = 10V, VO = 1.0V or 9.0V VDD = 15V, VO = 1.5V or 13.5V IOL LOW Level Output Current (Note 3) IOH HIGH Level Output Current (Note 3) IIN Input Current VDD = 5V, VO = 0.4V VDD = 10V, VO = 0.5V VDD = 15V, VO = 1.5V VDD = 5V, VO = 4.6V VDD = 10V, VO = 9.5V VDD = 15V, VO = 13.5V VDD = 15V, VIN = 0V VDD = 15V, VIN = 15V 3.5 7.0 11.0 0.64 1.6 4.2 0.64 1.6 4.2 0.1 0.1 4.95 9.95 14.95 1.5 3.0 4.0 3.5 7.0 11.0 0.51 1.3 3.4 0.51 1.3 3.4 55C Min Max 5 10 20 0.05 0.05 0.05 4.95 9.95 14.95 0 0 0 5 10 15 2 4 6 3 6 9 0.88 2.25 8.8 0.88 2.25 8.8 105 105 0.1 0.1 1.5 3.0 4.0 3.5 7.0 11.0 0.36 0.9 2.4 0.36 0.9 2.4 1.0 1.0 A mA mA V Min +25C Typ Max 5 10 20 0.05 0.05 0.05 4.95 9.95 14.95 1.5 3.0 4.0 V V +125C Min Max 150 300 600 0.05 0.05 0.05 V A Units

Note 3: Data does not apply to oscillator points 0 and 0 of CD4060BC. I OH and IOL are tested one output at a time.

www.fairchildsemi.com

CD4020BC CD4040BC CD4060BC

AC Electrical Characteristics

Symbol tPHL1, tPLH1 Parameter Propagation Delay Time to Q1

(Note 4)

Conditions Min Typ 250 100 75 150 60 45 100 50 40 125 50 40 Max 550 210 150 330 125 90 200 100 80 335 125 100 No Limit No Limit No Limit 1.5 4 5 4 10 12 200 100 80 200 100 80 5 50 450 210 170 450 210 170 7.5 pF pF ns ns MHz ns ns ns ns ns Units

CD4020BC, CD4040BC TA = 25C, CL = 50 pF, RL = 200k, tr = tf = 20 ns, unless otherwise noted VDD = 5V VDD = 10V VDD = 15V tPHL, tPLH Interstage Propagation Delay Time from Qn to Qn+1 tTHL, tTLH Transition Time VDD = 5V VDD = 10V VDD = 15V VDD = 5V VDD = 10V VDD = 15V tWL, tWH Minimum Clock Pulse Width VDD = 5V VDD = 10V VDD = 15V trCL, tfCL Maximum Clock Rise and Fall Time VDD = 5V VDD = 10V VDD = 15V fCL Maximum Clock Frequency VDD = 5V VDD = 10V VDD = 15V tPHL(R) Reset Propagation Delay VDD = 5V VDD = 10V VDD = 15V tWH(R) Minimum Reset Pulse Width VDD = 5V VDD = 10V VDD = 15V CIN CPD Average Input Capacitance Power Dissipation Capacitance Any Input

Note 4: AC Parameters are guaranteed by DC correlated testing.

www.fairchildsemi.com

CD4020BC CD4040BC CD4060BC

AC Electrical Characteristics

Symbol tPHL4, tPLH4 Parameter Propagation Delay Time to Q4

(Note 5)

Conditions Min Typ 550 250 200 150 60 45 100 50 40 170 65 50 Max 1300 525 400 330 125 90 200 100 80 500 170 125 No Limit No Limit No Limit 1 3 4 3 8 10 200 100 80 200 100 80 5 50 450 210 170 450 210 170 7.5 pF pF ns ns MHz ns ns ns ns ns Units

CD4060BC TA = 25C, CL = 50 pF, RL = 200k, tr = tf = 20 ns, unless otherwise noted VDD = 5V VDD = 10V VDD = 15V tPHL, tPLH Interstage Propagation Delay Time from Qn to Qn+1 tTHL, tTLH Transition Time VDD = 5V VDD = 10V VDD = 15V VDD = 5V VDD = 10V VDD = 15V tWL, tWH Minimum Clock Pulse Width VDD = 5V VDD = 10V VDD = 15V trCL, tfCL Maximum Clock Rise and Fall Time VDD = 5V VDD = 10V VDD = 15V fCL Maximum Clock Frequency VDD = 5V VDD = 10V VDD = 15V tPHL(R) Reset Propagation Delay VDD = 5V VDD = 10V VDD = 15V tWH(R) Minimum Reset Pulse Width VDD = 5V VDD = 10V VDD = 15V CIN CPD Average Input Capacitance Power Dissipation Capacitance Any Input

Note 5: AC Parameters are guaranteed by DC correlated testing.

RC Oscillator Notes: 1. R2 = 2 R1 to 10 R1 2. RC Oscillator applications are not recommended at supply voltages below 7.0V for R1 < 50 k 3. f 1 2.2 R1 CX at VCC = 10V

www.fairchildsemi.com

CD4020BC CD4040BC CD4060BC

Physical Dimensions inches (millimeters) unless otherwise noted

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Package Number M16A

www.fairchildsemi.com

CD4020BC CD4040BC CD4060BC 14-Stage Ripple Carry Binary Counters 12-Stage Ripple Carry Binary Counters 14-Stage Ripple Carry Binary Counters

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N16E

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. www.fairchildsemi.com 8 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. www.fairchildsemi.com

Potrebbero piacerti anche

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDa EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNessuna valutazione finora

- CD 4050Documento7 pagineCD 4050nicolaunmNessuna valutazione finora

- CD 4528Documento9 pagineCD 4528L30N1Nessuna valutazione finora

- 4094BCDocumento7 pagine4094BCNelson RodriguezNessuna valutazione finora

- NewDocumento8 pagineNewxuankien181991Nessuna valutazione finora

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDa EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsValutazione: 3.5 su 5 stelle3.5/5 (6)

- CD4015BC Dual 4-Bit Static Shift Register: General Description FeaturesDocumento6 pagineCD4015BC Dual 4-Bit Static Shift Register: General Description FeaturesMerényi OszkárNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- HEF40106B: 1. General DescriptionDocumento15 pagineHEF40106B: 1. General DescriptionyajujotosNessuna valutazione finora

- Switching in Electrical Transmission and Distribution SystemsDa EverandSwitching in Electrical Transmission and Distribution SystemsNessuna valutazione finora

- CD4094BCDocumento7 pagineCD4094BCEdgar MendezNessuna valutazione finora

- Beginning Digital Electronics through ProjectsDa EverandBeginning Digital Electronics through ProjectsValutazione: 5 su 5 stelle5/5 (1)

- CD4020BM/CD4020BC 14-Stage Ripple Carry Binary Counters CD4040BM/CD4040BC 12-Stage Ripple Carry Binary Counters CD4060BM/CD4060BC 14-Stage Ripple Carry Binary CountersDocumento6 pagineCD4020BM/CD4020BC 14-Stage Ripple Carry Binary Counters CD4040BM/CD4040BC 12-Stage Ripple Carry Binary Counters CD4060BM/CD4060BC 14-Stage Ripple Carry Binary CountersZoltán HalászNessuna valutazione finora

- 110 Waveform Generator Projects for the Home ConstructorDa Everand110 Waveform Generator Projects for the Home ConstructorValutazione: 4 su 5 stelle4/5 (1)

- CD4047Documento9 pagineCD4047Haryadi VjNessuna valutazione finora

- CD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S LatchesDocumento6 pagineCD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S LatchesDouglas CorderoNessuna valutazione finora

- CD40174 40175Documento6 pagineCD40174 40175scooby_maximoNessuna valutazione finora

- CD4011BCDocumento10 pagineCD4011BCKike DavilaNessuna valutazione finora

- CD4093 PDFDocumento8 pagineCD4093 PDFIván IvanovNessuna valutazione finora

- cd4066 DatasheetDocumento9 paginecd4066 DatasheetAbubakar SidikNessuna valutazione finora

- 74AC74Documento9 pagine74AC74ciernesNessuna valutazione finora

- CD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S LatchesDocumento7 pagineCD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S LatchesNarendra BholeNessuna valutazione finora

- MC 14521Documento12 pagineMC 14521rrebollarNessuna valutazione finora

- CD4017BC, CD4017BM, CD4022BC, CD4022BMDocumento10 pagineCD4017BC, CD4017BM, CD4022BC, CD4022BMRajkumar DommetiNessuna valutazione finora

- CD54HC14, CD74HC14, CD54HCT14, CD74HCT14: Features DescriptionDocumento16 pagineCD54HC14, CD74HC14, CD54HCT14, CD74HCT14: Features DescriptionAndrea DispoNessuna valutazione finora

- CD4029BC Presettable Binary/Decade Up/Down CounterDocumento10 pagineCD4029BC Presettable Binary/Decade Up/Down CounterIbrahimEssamNessuna valutazione finora

- CD4093BC Quad 2-Input NAND Schmitt Trigger: General Description FeaturesDocumento8 pagineCD4093BC Quad 2-Input NAND Schmitt Trigger: General Description FeaturesbanoluNessuna valutazione finora

- CD4008BMS - Full AdderDocumento8 pagineCD4008BMS - Full AdderTony TohNessuna valutazione finora

- CD40106BC Hex Schmitt Trigger: General Description FeaturesDocumento6 pagineCD40106BC Hex Schmitt Trigger: General Description FeaturesRoozbeh BahmanyarNessuna valutazione finora

- CD4029BM/CD4029BC Presettable Binary/Decade Up/Down Counter: General DescriptionDocumento8 pagineCD4029BM/CD4029BC Presettable Binary/Decade Up/Down Counter: General DescriptionMerényi OszkárNessuna valutazione finora

- CD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionDocumento10 pagineCD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionWillianNessuna valutazione finora

- CD4027BM/CD4027BC Dual J-K Master/Slave Flip-Flop With Set and ResetDocumento7 pagineCD4027BM/CD4027BC Dual J-K Master/Slave Flip-Flop With Set and ResetluckpoloNessuna valutazione finora

- 02 B - CD4001BCDocumento6 pagine02 B - CD4001BCtati_g10Nessuna valutazione finora

- Nte 4013Documento4 pagineNte 4013Codinasound CaNessuna valutazione finora

- Contador A Decadas HEF4040B PDFDocumento14 pagineContador A Decadas HEF4040B PDFAnonymous hp6KDLIxENessuna valutazione finora

- National Semiconductor CD40106BCN DatasheetDocumento7 pagineNational Semiconductor CD40106BCN DatasheetAlan CienfuegosNessuna valutazione finora

- CD 4060Documento10 pagineCD 4060ahocine2011Nessuna valutazione finora

- 7473Documento8 pagine7473Merényi OszkárNessuna valutazione finora

- CD4049 CD4050 Hoja de DatosDocumento6 pagineCD4049 CD4050 Hoja de Datoscemtech06Nessuna valutazione finora

- CD 74 HC 194Documento18 pagineCD 74 HC 194rrebollarNessuna valutazione finora

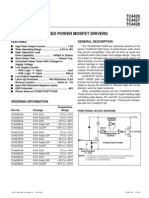

- TC4426 TC4427 TC4428 1.5A Dual High-Speed Power Mosfet DriversDocumento9 pagineTC4426 TC4427 TC4428 1.5A Dual High-Speed Power Mosfet DriversroozbehxoxNessuna valutazione finora

- CD22100 - DataSheetDocumento10 pagineCD22100 - DataSheetHao ChungNessuna valutazione finora

- CD4028BC BCD-to-Decimal Decoder: General Description FeaturesDocumento6 pagineCD4028BC BCD-to-Decimal Decoder: General Description Featuresmalirezazadeh5549Nessuna valutazione finora

- CD4094BMS: Pinout FeaturesDocumento12 pagineCD4094BMS: Pinout FeatureswertenoNessuna valutazione finora

- El5120 - El5220 - El5420Documento13 pagineEl5120 - El5220 - El5420Cristina NistorNessuna valutazione finora

- Device Datasheet For CD4021Documento7 pagineDevice Datasheet For CD4021bdfbNessuna valutazione finora

- cd4007 Intersil DatasheetDocumento9 paginecd4007 Intersil DatasheetMarie HayesNessuna valutazione finora

- CD 4052 BDocumento28 pagineCD 4052 BGeovanny AshquiNessuna valutazione finora

- CD4051B, CD4052B, CD4053B: FeaturesDocumento29 pagineCD4051B, CD4052B, CD4053B: Featuresdeec75Nessuna valutazione finora

- CD4538BCDocumento11 pagineCD4538BCImtiaz HussainNessuna valutazione finora

- Ad7524 Ep PDFDocumento8 pagineAd7524 Ep PDFjlfepeNessuna valutazione finora

- 0 Ti 4 Kki 3 L 0243 Iulijdp 7 A 7 TapfyDocumento8 pagine0 Ti 4 Kki 3 L 0243 Iulijdp 7 A 7 TapfyjuenkkoNessuna valutazione finora

- CD 4069Documento6 pagineCD 4069shaniimranNessuna valutazione finora

- 4051 PDFDocumento6 pagine4051 PDFyamaha640Nessuna valutazione finora

- 7 M 0880Documento18 pagine7 M 0880Mahmoued YasinNessuna valutazione finora