Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

An 6003

Caricato da

jesse_w_petersDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

An 6003

Caricato da

jesse_w_petersCopyright:

Formati disponibili

www.fairchildsemi.

com

AN-6003

Shoot-through in Synchronous Buck Converters

Jon Klein Power Management Applications

Abstract

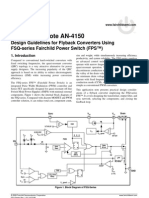

The synchronous buck circuit is in widespread use to provide point of use high current, low voltage power for CPUs, chipsets, peripherals etc. In the synchronous buck converter, the power stage has a high-side (Q1 below) MOSFET to charge the inductor, and a Low-side MOSFET which replaces a conventional buck regulators catch diode to provide a low-loss recirculation path for the inductor current.

V IN

PWM CONTROLLER

2.

Adaptive gate drive: This circuit looks at the VGS of the MOSFET thats being driven off to determine when to turn on the complementary MOSFET. Theoretically, adaptive gate drives produce the shortest possible dead-time for a given MOSFET without producing shootthrough.

H igh-S ide Q1 VO U T

L1

In practice, a combination of adaptive and fixed produces the best results, and is typically what is in todays PWM controllers and gate drivers as shown in Figure 2

D1 BOOT RG V IN +5 C BO O T

D C GD PW M 1V + D elay SW H D RV R G A TE G C GS S D C GD LDR V PW M R G A TE G C GS S D elay + 1V PG ND

Low -S ide Q2

Figure 1. Synchronous Buck output stage

Q1

Shoot-through is defined as the condition when both MOSFETs are either fully or partially turned on, providing a path for current to shoot through from VIN to GND. To minimize shoot-through, synchronous buck regulator ICs employ one of two techniques to ensure break before make operation of Q1 and Q2 to minimize shoot-through: 1. Fixed dead-time: A MOSFET is turned off, then a fixed delay is provided before the lowside is turned on. This circuit is simple and usually effective, but suffers from its lack of flexibility if a wide range of MOSFET gate capacitances are to be used with a given controller. Too long a dead-time means high conduction losses. Too short a dead time can cause shoot-through. A fixed dead-time typically must err on the too long side to allow high CGS MOSFETs to fully discharge before turning on the complementary MOSFET.

Q2

Figure 2. Typical Adaptive Gate drive

Even though there apparently is a break before make action by the controller, shoot-through can still occur when the High-side MOSFET turns on, due to Gate Step. Shoot-through is very difficult to measure directly. Shoot-through currents persist for only a few nS, hence the added inductance in a current probe drastically affects the shoot-through waveform. Shoot-through manifests itself typically as increased ringing, reduced efficiency, higher MOSFET temperatures (especially in Q1) and higher EMI. This paper will provide analytical techniques to predict shoot-through, and methods to reduce it.

04/25/2003

Shoot-through in Synchronous Buck Regulators

AN-6003

Gate Step The shootthrough culprit

VGS

6 5

SW NODE VOLTAGE

25 20 15

LS MOSFET GATE

Not exactly. Most shoot-through occurs when the high-side MOSFET is turned on. The high dv/dT on the SW node (Drain of the low-side MOSFET) couples charge through CGD. This drives the gate positive at the very moment when the driver is trying to hold the gate low. CGD and CGS form a capacitive voltage divider, which attenuates the gate step such that the worst case peak amplitude of the gate step (VSTEP) seen is:

TR

2 1 0

0 20 40

t (nS)

5 0 -5 60 80

Figure 4. Gate Step for VIN .=20V

V R (C + C ) VSTEP(PK ) RT CGD IN 1 e T GD GS TR

(1a)

Where RT = RDRIVER + RGATE + RDAMPING (see Figure 5), and TR is the rise-time of the SW node. The limiting case is when TR = 0. Then

VSTEP(MAX ) VIN CGD CGD + CGS

(1b)

This expression only illustrates the AC portion of the gate step. The gate step is injected onto whatever voltage the MOSFETs gate has discharged to. For example, if the switch node rises when VGS = 1V, and the gate step amplitude is 2V, instantaneously there will be 3 VGS which is more than enough to have a high instantaneous current through both MOSFETs. Its important, therefore that adaptive gate drive circuits allow sufficient delay to prevent the high side from turning on before the low-side VGS is discharged down to a few hundred mV. An illustration of gate step is seen below.

6 5

SW NODE VOLTAGE

Further exacerbating the problem for adaptive circuits is the fact that the adaptive comparator is not actually sensing the voltage at the internal gate junction of the MOSFET. As seen in Figure 5, the internal MOSFETs gate voltage has an unavoidable internal RGATE resistance. In addition, some designers like to have a damping resistor in series with the gates of MOSFETs that are located physically far away from their gate drives. This creates a bigger problem for the adaptive gate drive circuit. These series resistances form a voltage divider with the internal pull-down resistance of the low-side gate drive of the IC, causing it to think the gate voltage is lower than it really is when it decides to release the High-side driver.

HDRV H.S. MOSFET

D Delay 1V LDRV G RDamping RDRIVER CGS S CGD RGATE

Q2

14 12 10 8

LS MOSFET GATE

Figure 5. Resistance in the gate drive path attenuates the voltage at the MOSFET gate node.

4 VGS 3 2 1 0

0 20 40

t (nS)

6 4 2 0 -2 60 80

When there is 1V at the pin of the IC, the internal MOSFET VGS is:

VGS(I) = 1V RDRIVER RDRIVER + R GATE + RDamping

If the adaptive circuits are working, then we shouldnt see any shoot-through, right?

4 3

10

Consider an example where: RDRIVER = 2 , RDAMPING = 5 RGATE = 1.2

Figure 3. Gate Step for VIN .=12V.

04/25/2003

Shoot-through in Synchronous Buck Regulators

AN-6003

When the adaptive gate circuit switches, the internal MOSFET gate voltage will be:

1V (2 + 1.2 + 5) = 4.1V 2

MOSFET Choices

MOSFET characteristics can have a dramatic effect on how much shoot-through current can be induced by the gate step. The worst case for shoot-through is an infinitely fast (0 rise time) on the drain node. The amount of gate step is largely determined by the ration of CGS and CGD . Once the size of the gate step is determined (eq. 1 above), the peak magnitude of the shoot-through current can be calculated as :

IPEAK (MAX) K GM VSTEP(MAX) VTH(MIN)

In this example, if there were no delay in the circuit, the HDRV would turn on when the low-side MOSFET has just begun to discharge, causing a very high shoot-through current. Much of the problem in the above circuit is the damping resistor. If a damping resistance is necessary, place a Schottky diode across the resistor (as shown below) to reduce the effect the damping resistor will have on the adaptive gate drive.

HDRV H.S. MOSFET

D Delay 1V LDRV RDamping G CGS RDRIVER S CGD RGATE

(2)

where GM is the transconductance (in S, or A/V) given in the datasheet. While only a small percentage of MOSFETs exhibit VTH(MIN) at room temperature, VTH goes down with increasing junction temperature, therefore VTH(MIN) is a good proxy for the VTH at the operating junction temperature of the MOSFET. Subsequent calculations use VTH(MIN) for this reason. GM is not really a contstant, however, and its value is greatly reduced low enhancement voltages (VGS-VTH). In these calculations we use a factor "K" from the graph below, which is typical of GM with low values of enhancement. The X axis of Figure 7 is calculated as

VGS VTH(MIN) VTH(MIN)

1.0 0.8 K (GM Multipler) 0.6 0.4 0.2 0.0 0% 50% 100% 150% 200% 250% 300% Normalized Enhancement Voltage

Q2

Figure 6. Schottky diode reduces damping resistor error in adaptive gate drive

When using the schottky, the internal gate node will be at:

VGS(I) = 0.5 + 1V RDRIVER (RDRIVER + R GATE )

or 2.1V for our example. A dramatic improvement. Furthermore, the Schottky reduces the duration of the shoot-through step, since only RGATE + RDRIVER will be discharging CGS, rather than the sum of RGATE + RDAMPING + RDRIVER . Table 1 below illustrates the performance improvement in our example with and without the Schottky diode:

No Schottky 4.1 2.23 2.50 36 1100 With Schottky 2.1 1.14 1.25 0.29 20

Figure 7 GM factor (K)

V V V A mW

Comparator Flips @ VGS(INT) = VGS(INT) after 20nS delay VSTEP Peak Peak current Power Loss @ FSW=300KHz

Table 2 shows the relevant MOSFET characteristics which determine the maximum shoot-through current.

MOSFET MOSFET1 MOSFET2 MOSFET3 MOSFET4 MOSFET5 CGS 3,514 5,070 4,942 3,888 6,324 CGD 307 230 315 401 281 Typical Min VTH VTH 1.6 1.2 1.6 1.6 1.15 1 0.8 1 1 0.6 GM 86 97 80 135 90

Conditions: Typical low-side MOSFET, 25nS delay from comparator sense to beginning of SW node rise, 19VIN, 10nS SW node rise time.

Table 1 . Peak Currents with and without Schottky with RDAMPING = 5 .

Table 2 . Low-Side MOSFET Characteristics

04/25/2003

Shoot-through in Synchronous Buck Regulators

AN-6003

Each of the MOSFETs represented is from a different process and has different ratios of internal capacitance.

MOSFET MOSFET1 MOSFET2 MOSFET3 MOSFET4 MOSFET5 VSTEP(MAX) VTH(MIN) 1.53 0.82 1.14 1.78 0.81 1 0.8 1 1 0.6 VSTEP VTH(MIN) 0.53 0.02 0.14 0.78 0.21 IPEAK (max) 0.31 0.02 0.07 16.37 0.13

Reducing gate step by slowing down Q1 rise time

Usually, designers attempt to achieve the fastest risetime possible on the High-Side MOSFET in order to minimize switching losses. A simplified expression for turn-on losses (P(TURN-ON)) for the high-side MOSFET is:

PTURN ON FSW TR VIN IOUT 2

(3)

Table 3. Maximum VSTEP and ISHOOTTHROUGH @ VIN = 19V and VGS(START) = 0V.

Table 3 assumes that the VGS has dropped to 0 before the SW node rises when HDRV turns on. As demonstrated above, the smallest amplitude of VSTEP comes from MOSFET2 and MOSFET5, which are low-threshold devices. Low threshold in large part is due to a thin gate oxide, giving the MOSFET a high CGS ratio, which attenuates VSTEP. more than other CGD MOSFETs. Also, Table 3 only shows the theoretical peak current in Q2 due to the gate step. In a real converter, parasitic inductance limits the rise in current to 4A/nS. Even for the MOSFET4, the gate pulse only stays above threshold for about 5nS, so the shootthrough current would be further limited. An additional shortcoming of the simplified calculations of Table 3 is the assumption that SW node turn-on begins when VGS of the low-side is at 0. As we saw from the earlier discussion, this may not be the case.

where TR is the rise-time of the MOSFET. A very dV on SW) is desirable to fast rise-time (high dt minimize high-side power dissipation, but if it results in a large gate-step, causing shoot-through, the dissipation effect can be greater than the dissipation induced by slowing the rise time. In some situations this is the only practical approach to eliminate shootthrough. As can be seen in Figure 8, slowing down the rise time has a dramatic effect on the amplitude of VSTEP that is coupled into the Low-side MOSFET gate. TR slowdown has the added benefit of reducing EMI, but comes at a cost of efficiency loss . Figure 8 and subsequent tables were simulated with MOSFETs typical of those used in notebook PCs (2 in parallel) with 15A output current and 19VIN. Figure 8 assumes that the SW node begins to rise when the internal gate node has discharged down to 0.5V.

04/25/2003

Shoot-through in Synchronous Buck Regulators

AN-6003

2.0 1.8 1.6 1.4

V(STEP) Peak

MOSFET4 MOSFET1 MOSFET3 MOSFET5 MOSFET2

1.2 1.0 0.8 0.6 0.4 0.2 0.0

0 5 10 15 20 25 30 35

19V RiseTime(nS)

Figure 8 . Effect of SW node rise-time on VSTEP VIN=19V, SW rise starts @ VGS(Q2) = 0.5V

Table 4 shows the power loss due to shoot-through for each MOSFET. The major component of switching loss during Q1 turn-on is:

PTURNON t R FSW VIN IOUT 2

SW will rise when there is still a substantial VGS on Q2 as shown is Table 5. Slowing down Q1 can then be an effective strategy to reduce shoot-through losses.

(3)

TR(SW) 5 10 15 20 25 30 FET1 90 30 23 16 8 0 FET2 62 31 26 21 16 11 FET3 29 24 18 13 7 1 FET4 380 127 61 50 39 25 FET5 551 266 58 54 51 47 Q1 tR Loss 214 428 641 855 1,069 1,283

and is computed in the right-most column for each rise-time in Table 4 for IOUT = 15A.

TR(SW) 5 10 15 20 25 30 FET1 18 12 7 3 0 0 FET2 10 6 3 0 0 0 FET3 10 6 3 0 0 0 FET4 56 39 28 19 11 4 FET5 27 24 19 16 12 8 Q1 tR Loss 214 428 641 855 1,069 1,283

Table 5. Worst case (Min VTH) shoot-through power loss (mW) SW rise starts @ VGS(Q2) = 1V

Table 4. Worst case (Min VTH) shoot-through power loss (mW) SW rise starts @ VGS(Q2) = 0.5V

This is typically achieved by adding resistance (RG in Figure 2) in series with CBOOT . An approximation for TR provides a good starting point for choosing a value of RG:

TR C GS RDRIVE(L H) + RG

In most cases, the shoot-through is negligble, so slowing down high-side rise-time would not be a prudent choice, since the more power would be lost in slowing down the rise time than power saved by eliminating shoot-through. If, the controller's gate drive starts to turn Q1 on before allowing the internal node of Q2 to discharge,

(4)

where RDRIVE(L-H) is the resistance of the ICs high-side MOSFET gate driver when driving from low to high.

04/25/2003

Shoot-through in Synchronous Buck Regulators

AN-6003

DISCLAIMER FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user. 2. A critical component in any component of a life support, device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

04/25/2003

Potrebbero piacerti anche

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- IRF7807VD2: Fetky™ Mosfet / Schottky DiodeDocumento9 pagineIRF7807VD2: Fetky™ Mosfet / Schottky DiodeMartin TorresNessuna valutazione finora

- 4-5 EE462L MOSFET Firing CircuitDocumento44 pagine4-5 EE462L MOSFET Firing Circuitbal3xNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Valutazione: 2.5 su 5 stelle2.5/5 (3)

- Properly Sizing Mosfets For PWM ControllersDocumento15 pagineProperly Sizing Mosfets For PWM ControllersTaqi SyedNessuna valutazione finora

- LMC555 CMOS Timer: General Description FeaturesDocumento10 pagineLMC555 CMOS Timer: General Description FeaturesJeremy ObriotNessuna valutazione finora

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDa EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNessuna valutazione finora

- Datasheet PDFDocumento10 pagineDatasheet PDFVenkatesh VakamulluNessuna valutazione finora

- LMC555 CMOS Timer: General Description FeaturesDocumento12 pagineLMC555 CMOS Timer: General Description FeaturesNicolas FontanaNessuna valutazione finora

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDa EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsValutazione: 3.5 su 5 stelle3.5/5 (6)

- RT9202Documento16 pagineRT9202bachet56Nessuna valutazione finora

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocumento8 pagineN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical Datameroka2000Nessuna valutazione finora

- Irf7811Avpbf Irf7811Avpbf: Absolute Maximum RatingsDocumento6 pagineIrf7811Avpbf Irf7811Avpbf: Absolute Maximum RatingsnewmailsNessuna valutazione finora

- NTMD6N03R2 Power MOSFET: 30 V, 6 A, Dual N Channel SOIC 8Documento8 pagineNTMD6N03R2 Power MOSFET: 30 V, 6 A, Dual N Channel SOIC 8RjibNessuna valutazione finora

- Mosfet Gate DriveDocumento6 pagineMosfet Gate DrivegubiliNessuna valutazione finora

- MTP3055Documento9 pagineMTP3055lisandroantonNessuna valutazione finora

- Linear Technology LTC3728EG28400Documento37 pagineLinear Technology LTC3728EG28400Rickz2k8Nessuna valutazione finora

- MTP52N06V Datasheet - 2 PDFDocumento7 pagineMTP52N06V Datasheet - 2 PDFLeonel ValençaNessuna valutazione finora

- Stp7Nk80Z - Stp7Nk80Zfp STB7NK80Z - STB7NK80Z-1Documento18 pagineStp7Nk80Z - Stp7Nk80Zfp STB7NK80Z - STB7NK80Z-1queequeg73Nessuna valutazione finora

- Application Note 9017 Manufacturing Technology of A Small Capacity Inverter Using A Fairchild IGBTDocumento28 pagineApplication Note 9017 Manufacturing Technology of A Small Capacity Inverter Using A Fairchild IGBTRajesh VyasNessuna valutazione finora

- Infineon-Application Note Applications For Depletion MOSFETs-An-V01 00-EnDocumento13 pagineInfineon-Application Note Applications For Depletion MOSFETs-An-V01 00-EnP.r. Nuwan TharakaNessuna valutazione finora

- FSDM07652R DatasheetDocumento16 pagineFSDM07652R Datasheetmarianos67Nessuna valutazione finora

- Irf7832Pbf: V R Max QGDocumento10 pagineIrf7832Pbf: V R Max QGdreyes3773Nessuna valutazione finora

- An-978 HV Floating MOS Gate DriversDocumento21 pagineAn-978 HV Floating MOS Gate DriversPeter RueNessuna valutazione finora

- I GB T ApplicationDocumento17 pagineI GB T ApplicationSachin ThomasNessuna valutazione finora

- Mtw8n60e DDocumento9 pagineMtw8n60e DAtiqurrehman UmairNessuna valutazione finora

- 161 20551 0 FS7M0880Documento16 pagine161 20551 0 FS7M0880Edwin Vitovis TorresNessuna valutazione finora

- L6 - Gate Drive and SnubbersDocumento66 pagineL6 - Gate Drive and SnubberssrnankitNessuna valutazione finora

- Irf 7832Documento10 pagineIrf 7832Nguyễn Minh TúNessuna valutazione finora

- SG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorDocumento10 pagineSG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorJayesh SuryavanshiNessuna valutazione finora

- Infineon-Application Note Applications For Depletion MOSFETs-AN-v01 00-ENDocumento10 pagineInfineon-Application Note Applications For Depletion MOSFETs-AN-v01 00-ENvictorhugoseNessuna valutazione finora

- Float DriveDocumento24 pagineFloat DriveEdy AchalmaNessuna valutazione finora

- LMC555 CMOS Timer: Literature Number: SNAS558HDocumento14 pagineLMC555 CMOS Timer: Literature Number: SNAS558HIvr FloresNessuna valutazione finora

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocumento8 pagineN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical Datauim0% (1)

- Datasheet MC3334Documento6 pagineDatasheet MC3334odipasNessuna valutazione finora

- 1 To 5 ManualDocumento30 pagine1 To 5 ManualRoshan DodiyaNessuna valutazione finora

- An-990 Application Characterization of IGBT'sDocumento31 pagineAn-990 Application Characterization of IGBT'sVasco RodriguesNessuna valutazione finora

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDocumento10 pagineNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânNessuna valutazione finora

- Isolated Mosfet Gate Driver PaperDocumento6 pagineIsolated Mosfet Gate Driver PapergenwittsNessuna valutazione finora

- IGBT BasicsDocumento20 pagineIGBT Basicsscrewyou2222Nessuna valutazione finora

- STR W6753 DatasheetDocumento8 pagineSTR W6753 DatasheetjgerabmNessuna valutazione finora

- An786 (Driving Power Mosfet)Documento8 pagineAn786 (Driving Power Mosfet)Rody GCNessuna valutazione finora

- MLP2N06CL Smartdiscretes Mosfet 2 Amps, 62 Volts, Logic LevelDocumento9 pagineMLP2N06CL Smartdiscretes Mosfet 2 Amps, 62 Volts, Logic LevelEcurepair BrasilNessuna valutazione finora

- An 6069 PDFDocumento12 pagineAn 6069 PDFprasannaNessuna valutazione finora

- Parasitic Turn On of Sic Mosfets Turning A Bug Into FeatureDocumento9 pagineParasitic Turn On of Sic Mosfets Turning A Bug Into Featureelmarvin22Nessuna valutazione finora

- 2A, 2Mhz, Synchronous Step-Down Converter: General Description FeaturesDocumento13 pagine2A, 2Mhz, Synchronous Step-Down Converter: General Description FeaturesCesar TemocheNessuna valutazione finora

- Low-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationDocumento4 pagineLow-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationwhamcNessuna valutazione finora

- Massachusetts Institute of Technology Department of Electrical Engineering and Computer ScienceDocumento7 pagineMassachusetts Institute of Technology Department of Electrical Engineering and Computer ScienceFernando Sánchez HernándezNessuna valutazione finora

- IGBT/MOSFET Gate Drive Optocoupler: Optocouplers and Solid-State RelaysDocumento9 pagineIGBT/MOSFET Gate Drive Optocoupler: Optocouplers and Solid-State Relaysme1816Nessuna valutazione finora

- Bit 3713Documento24 pagineBit 3713neckoprvak5Nessuna valutazione finora

- Application Note AN-6027: Design of Power Factor Correction Circuit Using FAN7530Documento16 pagineApplication Note AN-6027: Design of Power Factor Correction Circuit Using FAN7530Malanie Sriya De SilvaNessuna valutazione finora

- DatasheetDocumento8 pagineDatasheetAri PutraNessuna valutazione finora

- Application Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Documento16 pagineApplication Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Nagendra ChaitanyaNessuna valutazione finora

- Power Electronics LabDocumento51 paginePower Electronics LabManoharan ManuNessuna valutazione finora

- Datasheet L6229Documento25 pagineDatasheet L6229Raul Sense MejiaNessuna valutazione finora

- RT9214Documento17 pagineRT9214levimolnarNessuna valutazione finora

- IGBT Characteristic CurveDocumento17 pagineIGBT Characteristic CurveSanaKayaniNessuna valutazione finora

- Only Fools and Horses - Season 1Documento1 paginaOnly Fools and Horses - Season 1jesse_w_peters100% (1)

- 0024 Tdp2 FMTV ModelingDocumento175 pagine0024 Tdp2 FMTV Modelingjesse_w_petersNessuna valutazione finora

- Homework 1 2014Documento1 paginaHomework 1 2014jesse_w_petersNessuna valutazione finora

- Table Thread ReferenceDocumento40 pagineTable Thread Referencejesse_w_petersNessuna valutazione finora

- Tim Keller Knowing GodDocumento4 pagineTim Keller Knowing Godjesse_w_petersNessuna valutazione finora

- Tim Keller Knowing GodDocumento4 pagineTim Keller Knowing Godjesse_w_petersNessuna valutazione finora

- Modern Residential Housing in UAEDocumento15 pagineModern Residential Housing in UAEBee Dan BudhachettriNessuna valutazione finora

- Kia September 2020 Price List: Picanto ProceedDocumento2 pagineKia September 2020 Price List: Picanto ProceedCaminito MallorcaNessuna valutazione finora

- Agricultural Extension and CommunicationDocumento173 pagineAgricultural Extension and CommunicationAlfredo Conde100% (1)

- AS-Interface Devices: (Slave Modules)Documento48 pagineAS-Interface Devices: (Slave Modules)Muhamad PriyatnaNessuna valutazione finora

- MS 005 For DUCT FABRICATION - INSULATION & INSTALLATION REV-1Documento21 pagineMS 005 For DUCT FABRICATION - INSULATION & INSTALLATION REV-1vusal huseynli100% (2)

- Exact Solution Tank DrainageDocumento8 pagineExact Solution Tank DrainageFelipe CastNessuna valutazione finora

- P eDocumento22 pagineP eKiks AshNessuna valutazione finora

- Agricultural Machinery in PakistanDocumento19 pagineAgricultural Machinery in PakistanBadar NiaziNessuna valutazione finora

- Bryophytes MorphologyDocumento9 pagineBryophytes Morphologyrachna singh0% (1)

- Https - Threejs - Org - Examples - Webgl - Fire - HTMLDocumento9 pagineHttps - Threejs - Org - Examples - Webgl - Fire - HTMLMara NdirNessuna valutazione finora

- EclipseDocumento6 pagineEclipsetoncipNessuna valutazione finora

- (Rect-15) Experimental Study On Partial Replacement of Cement With Coconut Shell Ash in ConcreteDocumento3 pagine(Rect-15) Experimental Study On Partial Replacement of Cement With Coconut Shell Ash in Concretefrancis dimakilingNessuna valutazione finora

- SCM 025-108 M2Documento8 pagineSCM 025-108 M2kazdanoNessuna valutazione finora

- AD&D - Forgotten Realms - Menzoberranzan - EXTRAS - House Do'Urden RestrospectiveDocumento16 pagineAD&D - Forgotten Realms - Menzoberranzan - EXTRAS - House Do'Urden RestrospectiveThiago RaulinoNessuna valutazione finora

- Flap Designs For Flap Advancement During Implant Therapy A Systematic Review 2016 PDFDocumento8 pagineFlap Designs For Flap Advancement During Implant Therapy A Systematic Review 2016 PDFRohit ShahNessuna valutazione finora

- University of LeedsDocumento20 pagineUniversity of LeedsYasir KhanNessuna valutazione finora

- Anti-Cellulite: Endermologie TreatmentDocumento8 pagineAnti-Cellulite: Endermologie TreatmentMinu CatalinNessuna valutazione finora

- UNDP NP Dhangadhi SWM TOR FinalDocumento4 pagineUNDP NP Dhangadhi SWM TOR FinalNirmal K.c.Nessuna valutazione finora

- L23 - Axial Flow CompressorDocumento17 pagineL23 - Axial Flow CompressorRohan GuptaNessuna valutazione finora

- Tyre Industry in IndiaDocumento14 pagineTyre Industry in IndiaH Janardan PrabhuNessuna valutazione finora

- Flooding Deagon Flood Flag MapDocumento1 paginaFlooding Deagon Flood Flag MapNgaire TaylorNessuna valutazione finora

- Modeling of Conducted EMI (Model Motor Simulink Bun)Documento8 pagineModeling of Conducted EMI (Model Motor Simulink Bun)Ioan ŢileaNessuna valutazione finora

- 8Documento3 pagine8Anirban Dasgupta100% (1)

- IbnTaymiyyah Theological EthicsDocumento361 pagineIbnTaymiyyah Theological EthicsDado Daki100% (1)

- Chapter 1 Cumulative Review: Multiple ChoiceDocumento2 pagineChapter 1 Cumulative Review: Multiple ChoiceJ. LeeNessuna valutazione finora

- EOCR 종합 EN 2015 PDFDocumento228 pagineEOCR 종합 EN 2015 PDFShubhankar KunduNessuna valutazione finora

- 510 1453 1 PB Tiang ReklameDocumento6 pagine510 1453 1 PB Tiang ReklameGunaedy UtomoNessuna valutazione finora

- Genesis of KupferschieferDocumento15 pagineGenesis of KupferschieferMaricela GarciaNessuna valutazione finora

- Evaluation of Global Research Trends in The Area of Food Waste D - 2020 - Food CDocumento10 pagineEvaluation of Global Research Trends in The Area of Food Waste D - 2020 - Food CAliNessuna valutazione finora

- Module 1 Hvac Basics Chapter-1Documento5 pagineModule 1 Hvac Basics Chapter-1KHUSHBOONessuna valutazione finora

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsDa EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsValutazione: 5 su 5 stelle5/5 (3)

- Chip War: The Fight for the World's Most Critical TechnologyDa EverandChip War: The Fight for the World's Most Critical TechnologyValutazione: 4.5 su 5 stelle4.5/5 (82)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyDa EverandChip War: The Quest to Dominate the World's Most Critical TechnologyValutazione: 4.5 su 5 stelle4.5/5 (229)

- Cyber-Physical Systems: Foundations, Principles and ApplicationsDa EverandCyber-Physical Systems: Foundations, Principles and ApplicationsHoubing H. SongNessuna valutazione finora

- CompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Da EverandCompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Valutazione: 5 su 5 stelle5/5 (2)

- Samsung Galaxy S22 Ultra User Guide For Beginners: The Complete User Manual For Getting Started And Mastering The Galaxy S22 Ultra Android PhoneDa EverandSamsung Galaxy S22 Ultra User Guide For Beginners: The Complete User Manual For Getting Started And Mastering The Galaxy S22 Ultra Android PhoneNessuna valutazione finora

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Da EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Valutazione: 5 su 5 stelle5/5 (2)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Da EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Valutazione: 5 su 5 stelle5/5 (3)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Da EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Valutazione: 5 su 5 stelle5/5 (1)

- CompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Da EverandCompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Nessuna valutazione finora

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XDa EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XValutazione: 3 su 5 stelle3/5 (2)

- Computer Science: A Concise IntroductionDa EverandComputer Science: A Concise IntroductionValutazione: 4.5 su 5 stelle4.5/5 (14)

- Cancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionDa EverandCancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionValutazione: 5 su 5 stelle5/5 (2)

- Jensen Huang's Nvidia: Processing the Mind of Artificial IntelligenceDa EverandJensen Huang's Nvidia: Processing the Mind of Artificial IntelligenceNessuna valutazione finora

- Raspberry PI: Learn Rasberry Pi Programming the Easy Way, A Beginner Friendly User GuideDa EverandRaspberry PI: Learn Rasberry Pi Programming the Easy Way, A Beginner Friendly User GuideNessuna valutazione finora

- Arduino and Raspberry Pi Sensor Projects for the Evil GeniusDa EverandArduino and Raspberry Pi Sensor Projects for the Evil GeniusNessuna valutazione finora

- A Beginner's Guide To IPhone 14 Pro Max Mastering: The Comprehensive User Guide And Illustrated Owner's Manual With Tips And Advanced Tricks For New BeDa EverandA Beginner's Guide To IPhone 14 Pro Max Mastering: The Comprehensive User Guide And Illustrated Owner's Manual With Tips And Advanced Tricks For New BeNessuna valutazione finora

- The comprehensive guide to build Raspberry Pi 5 RoboticsDa EverandThe comprehensive guide to build Raspberry Pi 5 RoboticsNessuna valutazione finora

- iPhone Photography: A Ridiculously Simple Guide To Taking Photos With Your iPhoneDa EverandiPhone Photography: A Ridiculously Simple Guide To Taking Photos With Your iPhoneNessuna valutazione finora

- Debugging Embedded and Real-Time Systems: The Art, Science, Technology, and Tools of Real-Time System DebuggingDa EverandDebugging Embedded and Real-Time Systems: The Art, Science, Technology, and Tools of Real-Time System DebuggingValutazione: 5 su 5 stelle5/5 (1)

- The User's Directory of Computer NetworksDa EverandThe User's Directory of Computer NetworksTracy LaqueyNessuna valutazione finora

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1715193157?v=1)