Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Coguia

Caricato da

Zapata JohnTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Coguia

Caricato da

Zapata JohnCopyright:

Formati disponibili

Gua visual y dinmica del funcionamiento de un procesador didctico sencillo

Jon Corts Ayala, Txelo Ruiz Vzquez, Izaskun Etxeberria Uztarroz

Dpto. de Arquitectura y Tecnologa de Computadores Facultad de Informtica, Universidad del Pas Vasco UPV-EHU 20018 Donostia - San Sebastin e-mail: jon@sc.ehu.es, txelo.ruiz@ehu.es, izaskun@si.ehu.es

Resumen

En este trabajo se presenta una aplicacin grfica cuyo objetivo es proporcionar una gua visual y dinmica del funcionamiento, a nivel de los componentes hardware, de un procesador didctico muy sencillo. Dicha aplicacin puede ser utilizada tanto por el profesor en el aula, en lecciones magistrales, como por los alumnos de manera autnoma, para profundizar en la comprensin del funcionamiento del procesador. Por ello, cuenta con una interfaz visual atrayente y su utilizacin es fcil e intuitiva. Dispone tambin de ayuda online para resolucin de dudas.

1. Motivacin

Dentro de los tpicos que habitualmente se imparten dentro de una asignatura introductoria de Arquitectura de Computadores est el de la unidad de proceso o ruta de datos de un procesador relativamente sencillo [4] [5] [6]. La comprensin de su funcionamiento por parte del alumnado es fundamental para la adquisicin posterior de conceptos ms avanzados de Arquitectura de Computadores, como puede ser la segmentacin de la ruta de datos. En nuestra Facultad, en una asignatura introductoria de primer curso, denominada Diseo de Sistemas Digitales e impartida en el primer semestre, se presenta una versin reducida de un procesador sencillo [1] diseado por miembros de esta Facultad en base al procesador MIPS [4] que es utilizado en asignaturas posteriores para introducir ms conceptos de Arquitectura de Computadores. En dicha asignatura, planteada segn un enfoque bottom-up [2], inicialmente se exponen los componentes bsicos de un sistema digital, trabajndose exhaustivamente tanto el anlisis como la sntesis de sistemas sencillos, y se con-

tina con una introduccin al diseo de sistemas sncronos con unidades de control cableadas basadas en mquinas de estados finitas (algoritmos ASM). Como colofn de la misma, se realiza el diseo (guiado por el profesor) de un procesador sencillo, tipo RISC, con un reducidsimo conjunto de instrucciones (concretamente, cuatro) y slo dos modos de direccionamiento: absoluto y directo de registro. Se disean tanto la Unidad de Proceso como la Unidad de Control cableada (mediante su especificacin ASM). El objetivo fundamental de dicho proceso de diseo contempla dos facetas: por una parte, que los alumnos sean capaces de analizar exhaustivamente el funcionamiento del procesador, distinguiendo todas las fases de ejecucin de las instrucciones y dndose cuenta del funcionamiento concurrente de los componentes hardware; por otra parte, que adquieran la visin de conjunto necesaria para deducir qu componentes habra que aadir o modificar en la Unidad de Proceso para poder ampliar el conjunto de instrucciones del procesador con una instruccin determinada, as como cules seran los pasos de ejecucin que debera realizar la Unidad de Control para obtener un funcionamiento correcto de la nueva instruccin aadida. Es obvio que la segunda faceta depende de la primera: si no se alcanza un conocimiento satisfactorio del funcionamiento del procesador, difcil ser modificar correctamente el diseo dado para ampliar su funcionamiento. Para evaluar la adquisicin de ambas competencias, en el examen de la asignatura se plantea un ejercicio (habitualmente, con un peso de 2,5 puntos sobre 10) sobre el procesador sencillo, que recoge ambas facetas de manera independiente: por un lado, preguntas muy concisas y concretas sobre el funcionamiento del procesador, y, por otro, la realizacin de una nueva instruccin. Dada la falta de costumbre del alumnado de primer curso a la hora de comprender en profun-

498

Recursos docentes

didad el funcionamiento a nivel hardware de un sistema digital de cierta complejidad, como es el sencillo procesador diseado, surga el problema de que un elevado nmero de alumnos no llegaba a alcanzar el nivel mnimo deseado, lo cual era un inconveniente en asignaturas posteriores. Dada la amplia utilizacin de simuladores en la enseanza de materias de Arquitectura y Organizacin de Computadores [8] [9] [3] y las ventajas que en el proceso de enseanza/aprendizaje reportan [7], en el momento en que se dise el procesador sencillo, se realiz tambin su simulador correspondiente [1]. Dicho simulador es utilizado en la asignatura de primer curso Lenguaje Mquina, impartida en el segundo semestre, y es muy adecuado para trabajar los aspectos relacionados con la programacin en lenguaje ensamblador, permitiendo visualizar los resultados obtenidos en cada paso de ejecucin contenido del conjunto de registros y de memoria principal, pero sin hacer hincapi en el funcionamiento del hardware, que es el aspecto que interesa recalcar en la asignatura de Diseo de Sistemas Digitales. Por ello, con el objetivo de paliar las deficiencias observadas, y con la idea de obtener mejores resultados, se pens que sera de gran ayuda didctica el contar con un simulador especfico del procesador sencillo, que hiciera hincapi en el funcionamiento de los componentes hardware (PC, IR, UAL, conjunto de registros,...) y que presentara una interfaz grfica amistosa y sencilla, de manera que pudiera ser utilizado tanto por

el profesor en el aula durante sus lecciones magistrales, como por los alumnos de manera autnoma, lo que les permitira profundizar a su ritmo en la comprensin del funcionamiento del procesador, sin presiones. Al tratarse de un procesador especfico, no era viable la utilizacin de simuladores ya existentes, sino que exiga el desarrollo de un simulador especfico, para lo que se recurri a plantear un proyecto fin de carrera (PFC). Dada la limitacin de tiempo, inherente al PFC, para el desarrollo de un simulador completo, que permitiera la posibilidad de ejecucin de diferentes programas, se decidi reducirlo, de manera que lo que se ha obtenido es la gua visual dinmica del funcionamiento del procesador sencillo que aqu se presenta.

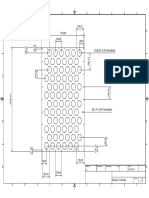

2. Estructura del procesador sencillo

La unidad de proceso del procesador sencillo (figura 1) consta de un conjunto de 32 registros de propsito general (CR), una unidad aritmticolgica sencilla (UAL), el contador de programa (PC), el registro de instruccin (IR), y una serie de registros y circuitera auxiliar (bsicamente multiplexores). Se considera una memoria principal de 64K x 16 bits. Los datos son de 16 bits, mientras que las instrucciones son de 32 bits (de ah la divisin del registro de instruccin, IR, en dos partes, IR1 e IR2, ya que se necesitan dos lecturas en memoria).

Figura 1. Estructura de la unidad de proceso del procesador sencillo (pantalla principal de la aplicacin).

XI Jornadas de Enseanza Universitaria de la Informtica

499

Figura 2. Resultado de hacer zoom sobre el algoritmo de control ASM.

En la figura 2 se puede ver el algoritmo ASM que refleja el funcionamiento de la unidad de control del procesador, tal como lo muestra el programa al hacer zoom sobre el recuadro de la parte inferior izquierda de la pantalla principal.

3.

Caractersticas de la aplicacin

La aplicacin se ha desarrollado en el entorno Microsoft Visual Basic 6.0, sobre una plataforma PC

y el sistema operativo Windows XP. Se puede ejecutar en plataformas PC Pentium y en los sistemas operativos: Windows 9x, Milenium, NT 3.5 o superiores, 2000/ XP. La pantalla principal (figura 3), permite ver el estado de cada componente de la unidad de proceso mediante una interfaz grfica intuitiva, proporcionando toda la informacin necesaria para comprender el funcionamiento de la misma: seales de control que se activan en un momento dado; esta-

Figura 3. Evolucin de la informacin a travs de la unidad de proceso en un instante dado.

500

Recursos docentes

Figura 4. Resultado de hacer zoom sobre la memoria principal.

do en el que se encuentra el algoritmo ASM de control; y el camino seguido por la informacin al circular entre diferentes componentes. Dicha informacin se va mostrando de manera dinmica, de forma que el usuario puede seguir intuitivamente todo el proceso de ejecucin de cada instruccin y su efecto sobre la unidad de proceso. Adems, haciendo zoom bien sobre la memoria principal o bien sobre el conjunto de registros, se puede ver su contenido en cualquier instante de la ejecucin del programa (figuras 4 y 5).

En cuanto a su funcionamiento, se toma como base un programa ejemplo que multiplica dos nmeros, escrito usando nicamente las cuatro instrucciones del conjunto de instrucciones. El usuario puede elegir entre tres modos de simulacin: continua, ciclo a ciclo, o una instruccin completa. As, puede optar por el modo de simulacin que mejor se adapta a su nivel de comprensin. En esta lnea, se ofrece la posibilidad de modificar la velocidad a la que evoluciona la informacin en la pantalla durante la simulacin, as como

Figura 5. Resultado de hacer zoom sobre el conjunto de registros.

XI Jornadas de Enseanza Universitaria de la Informtica

501

detenerla, para poder analizar detenidamente el resultado de alguna de las fases de ejecucin, y posteriormente continuar con la simulacin. En www.ehu.es/acwruvac/SIM/simc.htm se puede obtener la apicacin (2,72 MB).

4. Conclusin

En este trabajo se ha presentado un programa que proporciona una gua visual dinmica de la unidad de proceso de un procesador didctico muy sencillo. Este programa ha sido realizado como proyecto fin de carrera por un alumno de la titulacin de Ingeniera Informtica. La experiencia adquirida por el alumno al realizar esta aplicacin ha sido muy enriquecedora, ya que no slo se ha tenido que enfrentar al desarrollo de un programa de cierta envergadura, sino que tambin ha tenido que tener en cuenta las caractersticas de los posibles usuarios. Adems, el ndice de satisfaccin del alumno ha sido alto, ya que ha comprobado que su trabajo es de utilidad para ayudar a otros alumnos y facilitar su aprendizaje. Por otra parte, la experiencia ha confirmado la validez de utilizar los proyectos fin de carrera como generadores de recursos docentes ad hoc, totalmente adaptados a las necesidades concretas de cada centro/asignatura/profesor, ya que se pueden tener en cuenta un sinfn de particularidades; en concreto, una de ellas es la posibilidad de que los recursos docentes estn en los idiomas utilizados por los alumnos (en el caso de la aplicacin aqu presentada, est en castellano y en euskara). La aplicacin se utiliz por primera vez en la asignatura de Diseo de Sistemas Digitales durante el segundo semestre del curso 2003-04 y tambin en el primer semestre del curso 2004-05. El nivel de aceptacin tanto del profesorado como del alumnado ha sido alto. Su utilizacin en el aula por parte del profesor se ha revelado como una potente ayuda de cara a la explicacin detenida del funcionamiento del procesador, ya que permite hacer hincapi en los conceptos deseados: fases de ejecucin de las instrucciones, funcionamiento concurrente de los componentes hardware, etc., pudiendo el profesor detener la simulacin en cualquier instante y continuar cuando desee. Antes de la utilizacin del simulador, se recurra a la realizacin manual, sobre transpa-

rencias, de cronogramas explicativos, lo que sola ser bastante engorroso, tanto desde el punto de vista del profesor, como desde el de seguimiento del alumnado. En cuanto a resultados acerca de su influencia en el nivel de comprensin de los alumnos medido en una prueba objetiva, como es el examen, en comparacin con los resultados del curso anterior cabe destacar que la nota media obtenida en el ejercicio correspondiente ha mejorado en un 30% aproximadamente. Por otra parte, se ha reducido en un 15% el nmero de alumnos que obtenan en dicho ejercicio una puntuacin inferior a 0,5 puntos (sobre los 2,5 que vale el ejercicio).

Referencias

[1] Arbelaitz, O, Arregi, O., et alter. Nivel de lenguaje mquina: una aproximacin. ATCFISS. ISBN: 84-600-9519-3, 1999. [2] Clements, A. The Undergraduate Curriculum in Computer Architecture. IEEE Micro Special Issue on Computer Architecture Education, Vol. 20, No. 3, pp. 13-22, May/June 2000. [3] Djordjevic, J., et alter. An Integrated Environment for Teaching Computer Architecture. IEEE Micro Special Issue on Computer Architecture Education, Vol. 20, No. 3, pp. 66-74, May/June 2000. [4] Patterson, D.A., Hennesy, J.L. Estructura y diseo de computadores. Interficie circuitera/ programacin, Editorial Revert, 2000. [5] Stallings, W. Organizacin y Arquitectura de computadores, 5 edicin, Prentice Hall, 2000. [6] Tanenbaum, A.S. Organizacin de computadoras. Un enfoque estructurado, 4 edicin. Pearson Educacin, 2000. [7] Tangorra, F. The Role of the Computer Architecture Simulator in the Laboratory. SIGCSE Bulletin, Vol. 22, June 1990. [8] Wolffe, G., et alter. Teaching Computer Organization/Architecture With Limited Resources Using Simulators. Proc. of SIGCSE 2002. [9] Yurcik, W., et alter. A Survey of Simulators Used in Computer Organization/Architecture Courses. Proc. of the Summer Computer Simulation Conference (SCSC), July 2001.

Potrebbero piacerti anche

- Practicas de Soporte Tecnico A DistanciaDocumento88 paginePracticas de Soporte Tecnico A DistanciaErnesto Fernando Fernandez Farias75% (4)

- PudeosDocumento1 paginaPudeosZapata JohnNessuna valutazione finora

- SdfafDocumento1 paginaSdfafZapata JohnNessuna valutazione finora

- DFSFAFSDFFDocumento1 paginaDFSFAFSDFFZapata JohnNessuna valutazione finora

- PudeosDocumento1 paginaPudeosZapata JohnNessuna valutazione finora

- ZCZCDocumento1 paginaZCZCZapata JohnNessuna valutazione finora

- UrurtuDocumento2 pagineUrurtuZapata JohnNessuna valutazione finora

- Factura: No IVADocumento1 paginaFactura: No IVAZapata JohnNessuna valutazione finora

- CXCVZVCVDocumento1 paginaCXCVZVCVZapata JohnNessuna valutazione finora

- VXZXCVXVXDocumento1 paginaVXZXCVXVXZapata JohnNessuna valutazione finora

- Resultados Producto Marmolera La PalmaDocumento1 paginaResultados Producto Marmolera La PalmaZapata JohnNessuna valutazione finora

- ZdzasxfasDocumento1 paginaZdzasxfasZapata JohnNessuna valutazione finora

- Gastos Tarjeta de CreditoDocumento1 paginaGastos Tarjeta de CreditoZapata JohnNessuna valutazione finora

- CXZCCXDocumento1 paginaCXZCCXZapata JohnNessuna valutazione finora

- Nuevo DocmmDocumento2 pagineNuevo DocmmZapata JohnNessuna valutazione finora

- Nuevo DocmmDocumento2 pagineNuevo DocmmZapata JohnNessuna valutazione finora

- Relación de Gastos Salida BogotáDocumento1 paginaRelación de Gastos Salida BogotáZapata JohnNessuna valutazione finora

- Cotizaciones EstucoDocumento2 pagineCotizaciones EstucoZapata JohnNessuna valutazione finora

- Historial de Pegantes Cerámicos PDFDocumento1 paginaHistorial de Pegantes Cerámicos PDFZapata JohnNessuna valutazione finora

- Historial de Pegantes CerámicosDocumento1 paginaHistorial de Pegantes CerámicosZapata JohnNessuna valutazione finora

- Historial Sad ASDocumento2 pagineHistorial Sad ASZapata JohnNessuna valutazione finora

- Manual de FuncionesDocumento2 pagineManual de FuncionesZapata JohnNessuna valutazione finora

- Proyectos MMPDocumento1 paginaProyectos MMPZapata JohnNessuna valutazione finora

- Rut CaldeaDocumento1 paginaRut CaldeaZapata JohnNessuna valutazione finora

- Nitrwdadato de Calcio PDFDocumento1 paginaNitrwdadato de Calcio PDFZapata JohnNessuna valutazione finora

- Nitrato de CalcioDocumento2 pagineNitrato de CalcioZapata JohnNessuna valutazione finora

- Formato Afil EstadoDocumento1 paginaFormato Afil EstadoZapata JohnNessuna valutazione finora

- Plano MontajeDocumento1 paginaPlano MontajeZapata JohnNessuna valutazione finora

- Balance PDFDocumento1 paginaBalance PDFZapata JohnNessuna valutazione finora

- Espejo 16 ValvulasDocumento1 paginaEspejo 16 ValvulasZapata JohnNessuna valutazione finora

- Visitas Clientes PDFDocumento10 pagineVisitas Clientes PDFZapata JohnNessuna valutazione finora

- Caderno Completo - Simulado 2 Fase Administrativo - XXVDocumento16 pagineCaderno Completo - Simulado 2 Fase Administrativo - XXVPaulo César Rodrigues0% (1)

- Manual PBX Electrofon Pbx308-06Documento41 pagineManual PBX Electrofon Pbx308-06Javi KatzNessuna valutazione finora

- Tutorial - Cómo Eliminar La Contraseña - Password de La Bios (Método 1) - Descargar GratisDocumento11 pagineTutorial - Cómo Eliminar La Contraseña - Password de La Bios (Método 1) - Descargar GratismargierNessuna valutazione finora

- Admin IngfraestructuraDocumento3 pagineAdmin IngfraestructurashadiaNessuna valutazione finora

- Curso Reparacion de Computadoras Leccion 12 PDFDocumento12 pagineCurso Reparacion de Computadoras Leccion 12 PDFjuancarlos3927Nessuna valutazione finora

- Actividad 10, Sistemas OperativosDocumento10 pagineActividad 10, Sistemas OperativosCoraNessuna valutazione finora

- Test MantenimeintoDocumento2 pagineTest MantenimeintoLeonidParedesNessuna valutazione finora

- Direccion Estrategica Como DisciplinaDocumento2 pagineDireccion Estrategica Como DisciplinaViendall Rafael ZerónNessuna valutazione finora

- Informe 3 - Mantenimiento y Ensamble de ComputadoresDocumento26 pagineInforme 3 - Mantenimiento y Ensamble de Computadoresjohan100% (1)

- Práctica de Laboratorio-WiressharkDocumento7 paginePráctica de Laboratorio-WiressharkWilliam MolinaNessuna valutazione finora

- Administracion de ProyectoDocumento15 pagineAdministracion de ProyectoMarcelo Ignacio Cuyul Campos0% (1)

- 10 Trucos para Acelerar Windows XP - Blog de Jack MorenoDocumento9 pagine10 Trucos para Acelerar Windows XP - Blog de Jack Morenovarelator2007Nessuna valutazione finora

- Computador ClonDocumento2 pagineComputador Clonkisss_honey25% (4)

- Sistemas OperativosDocumento106 pagineSistemas OperativosYAQUELIN100% (1)

- ManualDocumento81 pagineManualPableins Francisco0% (2)

- Materiales Didácticos FESTODocumento15 pagineMateriales Didácticos FESTOLuciano Noé MatiasNessuna valutazione finora

- PIC-600 Actualización de DriverDocumento3 paginePIC-600 Actualización de Driverdaniel9797Nessuna valutazione finora

- PLC Pid PCDocumento5 paginePLC Pid PCArnol MurilloNessuna valutazione finora

- VOD MicrotrapDocumento12 pagineVOD MicrotrapFavian Silva ArayaNessuna valutazione finora

- InfografiaDocumento3 pagineInfografiaAna RaudalesNessuna valutazione finora

- Neurorazer2, Online - Juego Multitarea - Multitasking GameDocumento10 pagineNeurorazer2, Online - Juego Multitarea - Multitasking GameTijuíNessuna valutazione finora

- 11.7.3.2 Lab - Troubleshoot Operating System ProblemsDocumento3 pagine11.7.3.2 Lab - Troubleshoot Operating System ProblemsELVIS EMANUEL SANDOVAL SUAREZNessuna valutazione finora

- Portafolio de Evidencias Ingles TecnicoDocumento78 paginePortafolio de Evidencias Ingles TecnicoSergio García JiménezNessuna valutazione finora

- Póngase Frente A Su Computador y Observe Detenidamente Cada Una de Sus PartesDocumento4 paginePóngase Frente A Su Computador y Observe Detenidamente Cada Una de Sus PartesAura helenaNessuna valutazione finora

- Historia de La Computadora 2020Documento24 pagineHistoria de La Computadora 2020marcoNessuna valutazione finora

- OFIMATICADocumento18 pagineOFIMATICAAna Maria ValbuenaNessuna valutazione finora

- Manual Del Usuario NOKIA X3-00 RM-540Documento64 pagineManual Del Usuario NOKIA X3-00 RM-540Luis Alberto Diaz DiazNessuna valutazione finora

- Tutorial Word PDFDocumento87 pagineTutorial Word PDFJOSE ENRIQUE FERNANDEZ DIAZNessuna valutazione finora

- ExpertsoftDocumento34 pagineExpertsoftArianaObregonNessuna valutazione finora