Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Practica 3 Sumador y Restador

Caricato da

Gastón SolisCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Practica 3 Sumador y Restador

Caricato da

Gastón SolisCopyright:

Formati disponibili

PRACTICA 3. SUMADOR Y RESTADOR MATERIAL: Una fuente de voltaje de 5V LEDS (no importa el color) Alambre para conexiones.

iones. Resistencias de 330 ohms 1 tablilla de conexiones (protoboard) Circuitos integrados o equivalentes: o Dos 74FS08 o Dos 74LS32 o Un 74LS04.

SEMISUMADOR. Contiene un bit para el consumado, otro para el sumado y se puede tener un bit de acarreo C. El diagrama a bloques del semisumador se presenta en la siguiente figura:

Donde X e Y son los sumandos, C el acarreo y S la suma.

La tabla funcional del semisumador es: DEC X Y C S 0 1 2 3 0 0 1 1 0 1 0 1 0 0 0 1 0 1 1 0

De la tabla funcional, los mapas K para S y C, son:

Resumiendo: C=XY y S = X O EXC Y

Es decir, C se genera con una compuerta Y y S con una compuerta O EXC, como se muestra en el circuito correspondiente al semisumador:

Y el circuito topolgico es:

Donde S se representa por D1 y C por D2.

SUMADOR COMPLETO: Cuando adems de tener los 2 bits correspondientes al cosumado y al sumado, se tiene un acarreo inicial C0, con acarreo final C. Su diagrama a bloques se muestra en la figura siguiente:

Donde C0 es el acarreo posterior y C el acarreo final.

La tabla funcional del sumador completo es: DEC X Y C0 C S 0 1 2 3 4 5 6 7 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 0 1 0 1 1 1 0 1 1 0 1 0 0 1

De la definicin de Or EXC (cuando el nmero de entradas con valor 1 es impar, la funcin es igual a 1, en caso contrario es igual a 0), la suma S es igual a: S = X OEXC Y OEXC C0 El acarreo final C, en forma cannica es: C = SUMAminitrminos (3,5,6,7)

Los mapas K para S y C son.

La funcin reducida es: C = XY + YC0 + XC0

El circuito de S y C es:

Donde la compuerta Or de 3 entradas de 2 compuertas Or de 2 entradas. El circuito topolgico del sumador completo es:

se

obtuvo

partir

Donde S se representa por D1 y C por D2.

Obtencin de un SUMADOR COMPLETO a partir de dos SEMISUMADORES Partiendo de la expresin del acarreo final C del sumador completo, se hacen cannicos los dos trminos que contienen a C0: C = XY + YC0 + XC0 = XY + Y(X + X')C0 + X(Y +Y')C0 = = XY + XYC0 + X'YC0 + XYC0 + XY'C0 = XY + XYC0 +X'YC0 + XY'C0 = = XY (1 + C0) + C0 (X'Y + XY') = XY + C0 (X OEXC Y)

La siguiente figura muestra el circuito de un sumador completo a partir de dos semisumadores:

Donde la compuerta Or de 3 entradas se obtuvo a partir de dos compuertas Or de 2 entradas.

El circuito topolgico es:

Donde S se representa por D1 y C por D2.

SEMIRESTADOR: Es aquel que tiene un bit para el minuendo y otro para el sustraendo. Para el caso de que un bit del minuendo sea menor que el bit del sustraendo, se tendr un prstamo P. El diagrama a bloques se presenta en la figura adjunta.

La tabla funcional para el semirestador es: DEC X Y P R 0 1 2 3 Los mapas K para R y P son: 0 0 1 1 0 1 0 1 0 1 0 0 0 1 1 0

Resumiendo: P = X' Y y R = X O EXC Y

El circuito del semirestador es:

El circuito topolgico del semirestador es:

Donde R se representa por D1 y P por D2.

RESTADOR COMPLETO: Es aquel que considera un prstamo inicial P0, aunado a los bits del minuendo y el sustraendo. Su diagrama a bloques se presenta en la figura adjunta.

La tabla funcional del restador completo es: DEC X Y P0 P R 0 1 2 0 0 0 0 0 0 0 1 1 1 0 1 0 1 1

3 4 5 6 7

0 1 1 1 1

1 0 0 1 1

1 0 1 0 1

1 0 0 0 1

0 1 0 0 1

El prstamo final P, en forma cannica es: P = SUMAminitrminos (1,2,3,7) Los mapas K para R y P son:

De la definicin de OEXC (cuando el nmero de entradas con valor 1 es impar, la funcin es igual a 1, en caso contrario es igual a 0), la resta Res igual a: R = X OEXC Y OEXC C0

La funcin reducida del prstamo final P es: P = X'Y + YP0 +X'P0

La siguiente figura presenta el logigrama del restador completo:

Circuito topolgico del restador completo:

Donde R se representa por D1 y P por D2. Nuevamente, la compuerta O de 3 entradas se puede obtener a partir de dos compuertas O de 2 entradas.

Obtencin de un RESTADOR COMPLETO a partir de dos SEMIRESTADORES Partiendo de la expresin del prstamo final P del restador completo, se hacen cannicos los dos trminos que contienen a P0: C = X'Y + YP0 + X'P0 = XY + Y(X + X')P0 + X'(Y +Y')P0 = = X'Y + XYP0 + X'YP0 + X'YP0 + X'Y'P0 = X'Y + XYP0 +X'YP0 + X'Y'P0 = = X'Y (1 + P0) + P0 (XY + X'Y') = X'Y + P0 (X OEXC Y)'

El logigrama del restador completo en base a dos semirestadores es:

La siguiente figura presenta el circuito topolgico del restador completo a partir de 2 semirestadores:

Donde R se representa por D1 y P por D2.

PROCEDIMIENTO EXPERIMENTAL Armar los siguientes circuitos y comprobar sus seales de salida, sus acarreos y sus prstamos, segn sea el caso, basndose en las tablas funcionales desarrolladas.

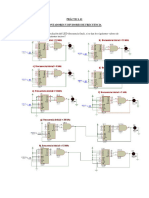

Circuito topolgico 1: Resume los 3 circuitos relativos a los sumadores.

Los LED (diodos emisores de luz) 1 y 2, representan las seales de salida S y C del semisumador, respectivamente; los LED 3 y 4, las seales de salida S y C del sumador completo, respectivamente; y los LED 5 y 6, las seales de salida S y C del sumador completo, hecho a base de dos semisumadores, respectivamente.

Circuito topolgico 1: Resume los 3 circuitos relativos a los restadores.

Los LED 1 y 2, representan las seales de salida R y P del semirestador, respectivamente; los LED 3 y 4, representan R y P, seales de salida del restador completo, respectivamente; los LED 5 y 6 representan las seales de salida R y P del restador completo formado a base de dos semirestadores, respectivamente.

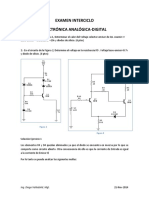

7. Realizar la tabla de verdad para el siguiente circuito MSI (mediana escala de integracin):

Polarizar el circuito integrado con VCC en la pata 16 y aterrizar la pata 8. A, B, C, D y C0 son entradas; S0, S1, S2, S3 y C4 son salidas.

Potrebbero piacerti anche

- Articulo IEEE Curvas Del DiodoDocumento4 pagineArticulo IEEE Curvas Del DiodoEveth De la CruzNessuna valutazione finora

- Sumadorrestador - Contador 0 99Documento24 pagineSumadorrestador - Contador 0 99Jose Ignacio Fajardo AguirreNessuna valutazione finora

- Contador Fotoeléctrico de Personas y ObjetosDocumento3 pagineContador Fotoeléctrico de Personas y ObjetosAndres Felipe Jaimes AlvarezNessuna valutazione finora

- Aplicaciones Flip Flop Tipo DDocumento8 pagineAplicaciones Flip Flop Tipo DherguamuNessuna valutazione finora

- Ejercicios Redes de Dos Puertos y Estabilidad de Funciones.Documento3 pagineEjercicios Redes de Dos Puertos y Estabilidad de Funciones.Santiago Fabian Valarezo TorresNessuna valutazione finora

- Contador de Visitantes Usando Led IR y FototransistorDocumento5 pagineContador de Visitantes Usando Led IR y FototransistorJuan Chaug SánchezNessuna valutazione finora

- Informe de Laboratorio de Transistor BJT Configuración Emisor ComúnDocumento4 pagineInforme de Laboratorio de Transistor BJT Configuración Emisor ComúnLaura Camila Murcia LaitonNessuna valutazione finora

- Control de teclado matricial 4x4 con Arduino y PythonDocumento3 pagineControl de teclado matricial 4x4 con Arduino y PythonJuan David SolarteNessuna valutazione finora

- Eedi U1 A3 CecaDocumento7 pagineEedi U1 A3 CecaCESAR CASTLE100% (1)

- Términos máximos y mínimos en sistemas digitalesDocumento3 pagineTérminos máximos y mínimos en sistemas digitalesLuigi OrtiɀNessuna valutazione finora

- Guía electrónica digitalDocumento61 pagineGuía electrónica digitalAlejandro hernadez de la rosa100% (1)

- Transistor IdealDocumento2 pagineTransistor IdealRaul PaguayNessuna valutazione finora

- Ejercicios Resueltos TransistoresDocumento4 pagineEjercicios Resueltos TransistoresMateo DomínguezNessuna valutazione finora

- Densidad de flujo magnético en un solenoide de 20 cmDocumento3 pagineDensidad de flujo magnético en un solenoide de 20 cmVenegas ChioNessuna valutazione finora

- Informe 1Documento17 pagineInforme 1Jhon Cerna F.Nessuna valutazione finora

- Práctica 4 TermocuplaDocumento6 paginePráctica 4 TermocuplaFreddy TamayoNessuna valutazione finora

- Ejercicios de Campos Eléctricos y PotencialesDocumento7 pagineEjercicios de Campos Eléctricos y PotencialesJhon D'LozxoNessuna valutazione finora

- Práctica 1. Funcionamiento Del Diodo SemiconductorDocumento11 paginePráctica 1. Funcionamiento Del Diodo SemiconductorBayron A. Pérez AyalaNessuna valutazione finora

- Informe 2 Repaso Teorema de MorganDocumento5 pagineInforme 2 Repaso Teorema de MorganGüerrëröYöylëNessuna valutazione finora

- PDF Contador Digital Informe Proyecto Final - Compress PDFDocumento12 paginePDF Contador Digital Informe Proyecto Final - Compress PDFLEYDA ORIANA CAYRO FLORESNessuna valutazione finora

- Diseño de teclado matricial 4x4 con codificador, decodificador y registrosDocumento13 pagineDiseño de teclado matricial 4x4 con codificador, decodificador y registrosDavid EstrellaNessuna valutazione finora

- Taller 1 F Sica El CtricaDocumento4 pagineTaller 1 F Sica El CtricaElena Jiménez BohórquezNessuna valutazione finora

- Morris Mano EjerciciosDocumento12 pagineMorris Mano EjerciciosMaura SichaNessuna valutazione finora

- Practica 10 Registro UniversalDocumento7 paginePractica 10 Registro UniversalJonathan DominguezNessuna valutazione finora

- Diseño de un multiplicador 2x2 bits con compuertas lógicasDocumento3 pagineDiseño de un multiplicador 2x2 bits con compuertas lógicasLalo SanttyNessuna valutazione finora

- Práctica 4 Circuitos DigitalesDocumento2 paginePráctica 4 Circuitos DigitalesalfredocorNessuna valutazione finora

- Variable Aleatoria Bi Dimensional DiscretaDocumento5 pagineVariable Aleatoria Bi Dimensional DiscretaSistemasUCHNessuna valutazione finora

- Electronica DigitalDocumento200 pagineElectronica Digitaldescargerfm1415Nessuna valutazione finora

- Taller II CorteDocumento2 pagineTaller II Cortemauro ibarraNessuna valutazione finora

- Practica 5 Codificadores y DecodificadoresDocumento3 paginePractica 5 Codificadores y DecodificadoresIván ChambiNessuna valutazione finora

- Problemas Resueltos de DieléctricosDocumento6 pagineProblemas Resueltos de Dieléctricosjim_crane10Nessuna valutazione finora

- Compuertas Practica 01 PDFDocumento17 pagineCompuertas Practica 01 PDFWilson TarrifaNessuna valutazione finora

- CapacitanciaDocumento5 pagineCapacitanciaXavi MayénNessuna valutazione finora

- Ejercicios Resueltos de Dispositivos Electrónicos I Examen de Junio de 2001 - Ejercicio 2Documento3 pagineEjercicios Resueltos de Dispositivos Electrónicos I Examen de Junio de 2001 - Ejercicio 2Jimmie Valverde MontalvoNessuna valutazione finora

- Practica - 1 Sis Digis 2Documento7 paginePractica - 1 Sis Digis 2Mathy MerinoNessuna valutazione finora

- Potencial de Esfera Cargada, Por Dentro y Por Fuera.Documento1 paginaPotencial de Esfera Cargada, Por Dentro y Por Fuera.Anuar HernándezNessuna valutazione finora

- Diodo Schottky: Características y AplicacionesDocumento13 pagineDiodo Schottky: Características y AplicacionesAbel JmcNessuna valutazione finora

- Informe 5 Electricidad y Magnetismo JAARADocumento19 pagineInforme 5 Electricidad y Magnetismo JAARAC Geramias MoralesNessuna valutazione finora

- Simulación #5 Motor A PasosDocumento2 pagineSimulación #5 Motor A PasosThelma MoralesNessuna valutazione finora

- Numeros Primos VHDL PDFDocumento2 pagineNumeros Primos VHDL PDFLeonardo MoraNessuna valutazione finora

- Exámen 1 Circuitos DigitalesDocumento2 pagineExámen 1 Circuitos DigitalesalfredocorNessuna valutazione finora

- Practica 5Documento10 paginePractica 5Diana ObandoNessuna valutazione finora

- p7 - Multiplexores y DemultiplexoresDocumento7 paginep7 - Multiplexores y DemultiplexoresalexNessuna valutazione finora

- Grupo7 - Materiales Dieléctricos y Capacitancia PDFDocumento46 pagineGrupo7 - Materiales Dieléctricos y Capacitancia PDFLuisNessuna valutazione finora

- Monitoreo potencia antena 4 bitsDocumento16 pagineMonitoreo potencia antena 4 bitsCarlos De Los SantosNessuna valutazione finora

- Caracterización de Conversores ADCDocumento4 pagineCaracterización de Conversores ADCJonathanNessuna valutazione finora

- Fundamentos de Diseño Digital LecturaDocumento316 pagineFundamentos de Diseño Digital LecturaJuan PerezNessuna valutazione finora

- Programación lógicaDocumento4 pagineProgramación lógicaAldo CamPzNessuna valutazione finora

- Entorno PythonDocumento11 pagineEntorno PythonLuchinEQNessuna valutazione finora

- Circuito Lógicos Con TransistoresDocumento3 pagineCircuito Lógicos Con TransistoresDiana Catalina JaimesNessuna valutazione finora

- Análisis Senoidal Permanente de Circuitos Trifásicos Balanceados y DesbalanceadosDocumento12 pagineAnálisis Senoidal Permanente de Circuitos Trifásicos Balanceados y DesbalanceadosHugo98Nessuna valutazione finora

- Práctica 1Documento5 paginePráctica 1danielNessuna valutazione finora

- Código Gray a 7 segmentoDocumento8 pagineCódigo Gray a 7 segmentoValentina RoyeroNessuna valutazione finora

- Oscilador de CuadraturaDocumento31 pagineOscilador de CuadraturaCristian Figueroa100% (1)

- Polarización de Los FETDocumento27 paginePolarización de Los FETEbert Gabriel San Román CastilloNessuna valutazione finora

- 7448Documento4 pagine7448Juan VazquezNessuna valutazione finora

- Práctica 4 DigitalesDocumento13 paginePráctica 4 DigitalesElizabeth Flores MancillaNessuna valutazione finora

- Lab Cir Digitales 04Documento12 pagineLab Cir Digitales 04Christian RiveraNessuna valutazione finora

- Diseño de Circuitos LogicosDocumento36 pagineDiseño de Circuitos LogicosFabian CasteloNessuna valutazione finora

- Recolección de datos para sistemas de información indígenaDocumento7 pagineRecolección de datos para sistemas de información indígenaClaudino ChaconNessuna valutazione finora

- Certificado de Registro de Multas de Transito No PagadasDocumento2 pagineCertificado de Registro de Multas de Transito No PagadaspoloNessuna valutazione finora

- M3-Tg-Gestión de Inventarios y AlmacenamientoDocumento3 pagineM3-Tg-Gestión de Inventarios y Almacenamientocamipiza88Nessuna valutazione finora

- Mariela Burghardt y Otros - Trabajador 4.0 PDFDocumento8 pagineMariela Burghardt y Otros - Trabajador 4.0 PDFomtrilloNessuna valutazione finora

- CVCarlos Eduardo Ludeña MerinoDocumento9 pagineCVCarlos Eduardo Ludeña MerinoGiancarloNessuna valutazione finora

- b5 b50 13 Analista ProgramadorDocumento6 pagineb5 b50 13 Analista Programadorge reNessuna valutazione finora

- TrabajoGrupal ActividadInvestigaciónFormativaCatálogoTesisDocumento4 pagineTrabajoGrupal ActividadInvestigaciónFormativaCatálogoTesisterreros molinaNessuna valutazione finora

- 19-3-20071239guia01 Eb Sta200Documento11 pagine19-3-20071239guia01 Eb Sta200Laura Francisca Carril CancinoNessuna valutazione finora

- Catalogo Guinaz 2015 TarifaDocumento36 pagineCatalogo Guinaz 2015 Tarifat.m lauraNessuna valutazione finora

- Células de McCulloch-Pitts en MatlabDocumento7 pagineCélulas de McCulloch-Pitts en MatlabAdrian Sanchez CarriloNessuna valutazione finora

- Actividad 3 Habilidades Gerenciales Entrega 3Documento5 pagineActividad 3 Habilidades Gerenciales Entrega 3Jorge LozanoNessuna valutazione finora

- Monografia Marketing MovilDocumento25 pagineMonografia Marketing MovilJoel Puma ChampiNessuna valutazione finora

- TFM - Cambio OrganizacionalsDocumento16 pagineTFM - Cambio OrganizacionalsJobPlazaRieraNessuna valutazione finora

- Aos 3Documento44 pagineAos 3Whispy Piniwini100% (1)

- Simbologia y Ejemplos Gráficos Diagramas de ProcesosDocumento5 pagineSimbologia y Ejemplos Gráficos Diagramas de ProcesosLuisa FernandaNessuna valutazione finora

- Informe InstalacionesDocumento19 pagineInforme InstalacionesCarLz89100% (1)

- Campos CorreoDocumento3 pagineCampos CorreoReineiry GironNessuna valutazione finora

- Actividad 3 - Derechos de AutorDocumento9 pagineActividad 3 - Derechos de AutorDiegoNessuna valutazione finora

- Pluma de EstacionamientoDocumento7 paginePluma de Estacionamientoeags4343_136495528Nessuna valutazione finora

- Ex Recuperacion LFADocumento3 pagineEx Recuperacion LFAJose Fernando Villacorta TafurNessuna valutazione finora

- CENTRAL MONITORIZACION Nihon Kodhen CNS-9601K PDFDocumento412 pagineCENTRAL MONITORIZACION Nihon Kodhen CNS-9601K PDFJ VkNessuna valutazione finora

- TEMA 16 MacrosDocumento10 pagineTEMA 16 MacrosJhon Alexis Vera RamosNessuna valutazione finora

- Exposición_ Norma Británica BS 3811Documento2 pagineExposición_ Norma Británica BS 3811jesusx7422Nessuna valutazione finora

- Imforme 08 Topo Perfil Longt (Kent) (Oficial)Documento12 pagineImforme 08 Topo Perfil Longt (Kent) (Oficial)Flor de Maria Flores TaparaNessuna valutazione finora

- MONT FrecuencimetroDocumento3 pagineMONT FrecuencimetroConde JuanjoNessuna valutazione finora

- Taller 1 Estilos y Tabla de ContenidoDocumento4 pagineTaller 1 Estilos y Tabla de ContenidoValeryPicoNessuna valutazione finora

- Características de Un Instrumento de MedidaDocumento2 pagineCaracterísticas de Un Instrumento de MedidaOscar OchoaNessuna valutazione finora

- Guía de Servicio SocialDocumento21 pagineGuía de Servicio SocialIvan MayoNessuna valutazione finora

- Aplicar La 4FN y 5FN PDFDocumento5 pagineAplicar La 4FN y 5FN PDFEdgar Ismael Rodriguez MendozaNessuna valutazione finora

- Preguntas y Respuestas Defensa FinalDocumento20 paginePreguntas y Respuestas Defensa FinalIsabel GrandeNessuna valutazione finora