Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

VN750 / VN750S VN750PT / VN750-B5: High Side Driver

Caricato da

Dan EsentherTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

VN750 / VN750S VN750PT / VN750-B5: High Side Driver

Caricato da

Dan EsentherCopyright:

Formati disponibili

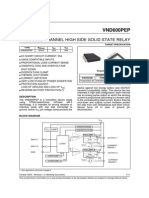

VN750 / VN750S / VN750PT / VN750-B5

HIGH SIDE DRIVER

TYPE VN750 VN750S VN750PT VN750-B5

RDS(on) 60 m

IOUT

VCC

6A

36 V

SO-8

PENTAWATT

CMOS COMPATIBLE INPUT I ON STATE OPEN LOAD DETECTION I OFF STATE OPEN LOAD DETECTION I SHORTED LOAD PROTECTION I UNDERVOLTAGE AND OVERVOLTAGE SHUTDOWN I PROTECTION AGAINST LOSS OF GROUND I VERY LOW STAND-BY CURRENT

I I

P2PAK

PPAK ORDER CODES

REVERSE BATTERY PROTECTION (*)

PACKAGE PENTAWATT SO-8 P2PAK PPAK

TUBE VN750 VN750S VN750-B5 VN750PT

T&R VN750S13TR VN750-B513TR VN750PT13TR

DESCRIPTION The VN750, VN750S, VN750PT, VN750-B5 are a monolithic device designed in STMicroelectronics VIPower M0-3 Technology, intended for driving any kind of load with one side connected to ground. Active V CC pin voltage clamp protects the device against low energy spikes (see ISO7637 transient BLOCK DIAGRAM

compatibility table). Active current limitation combined with thermal shutdown and automatic restart protect the device against overload. The device detects open load condition both is on and off state. Output shorted to VCC is detected in the off state. Device automatically turns off in case of ground pin disconnection.

VCC

VCC CLAMP

OVERVOLTAGE DETECTION UNDERVOLTAGE DETECTION

GND Power CLAMP

INPUT LOGIC

DRIVER OUTPUT CURRENT LIMITER

STATUS

ON STATE OPENLOAD DETECTION OVERTEMPERATURE DETECTION

OFF STATE OPENLOAD AND OUTPUT SHORTED TO V CC DETECTION

(*) See application schematic at page 8

Rev. 1 1/31

June 2004

VN750 / VN750S / VN750PT / VN750-B5

ABSOLUTE MAXIMUM RATING

Symbol VCC - VCC - Ignd IOUT - IOUT IIN ISTAT Parameter DC Supply Voltage Reverse DC Supply Voltage DC Reverse Ground Pin Current DC Output Current Reverse DC Output Current DC Input Current DC Status Current Electrostatic Discharge (Human Body Model: R=1.5K; C=100pF) VESD - INPUT - STATUS - OUTPUT - VCC Maximum Switching Energy (L=1.8mH; RL=0; Vbat=13.5V; Tjstart=150C; IL=9A) Maximum Switching Energy (L=2.46mH; RL=0; Vbat=13.5V; Tjstart=150C; IL=9A) Power Dissipation TC=25C Junction Operating Temperature Case Operating Temperature Storage Temperature 4000 4000 5000 5000 100 138 4.2 60 60 Internally Limited - 40 to 150 - 55 to 150 138 60 V V V V mJ mJ W C C C SO-8 Value PENTAWATT P2PAK 41 - 0.3 - 200 Internally Limited -6 +/- 10 +/- 10 PPAK Unit V V mA A A mA mA

EMAX EMAX Ptot Tj Tc Tstg

CONFIGURATION DIAGRAM (TOP VIEW) & SUGGESTED CONNECTIONS FOR UNUSED AND N.C. PINS

VCC OUTPUT OUTPUT VCC

5 4

N.C. STATUS INPUT GND

5 4 3 2 1

OUTPUT STATUS VCC INPUT GND

SO-8 Connection / Pin Floating To Ground

PPAK / P2PAK Status X N.C. X X Output X

PENTAWATT

Input X Through 10K resistor

CURRENT AND VOLTAGE CONVENTIONS

IS VF

IIN INPUT ISTAT STATUS

VCC

IOUT OUTPUT GND VCC

VIN VSTAT IGND

VOUT

2/31

VN750 / VN750S / VN750PT / VN750-B5

THERMAL DATA

Symbol Rthj-case Rthj-lead Rthj-amb Parameter Thermal Resistance Junction-case Thermal Resistance Junction-lead Max Max S0-8 30 93 (1) 82 (2) Value PENTAWATT P2PAK 2.1 2.1 62.1 52.1 (3) 62.1 37 (4) PPAK 2.1 77.1 (3) 44 (4) Unit C/W C/W C/W C/W

Thermal Resistance Junction-ambient Max

(1) When mounted on a standard single-sided FR-4 board with 0.5cm2 of Cu (at least 35m thick) connected to all VCC pins. Horizontal mounting and no artificial air flow. (2) When mounted on a standard single-sided FR-4 board with 2cm2 of Cu (at least 35m thick) connected to all VCC pins. Horizontal mounting and no artificial air flow. (3) When mounted on a standard single-sided FR-4 board with 0.5cm2 of Cu (at least 35m thick). Horizontal mounting and no artificial air flow. (4) When mounted on a standard single-sided FR-4 board with 6cm2 of Cu (at least 35m thick). Horizontal mounting and no artificial air flow.

ELECTRICAL CHARACTERISTICS (8V<VCC<36V; -40C<Tj<150C unless otherwise specified) POWER

Symbol VCC VUSD VUSDhyst VOV RON Parameter Operating Supply Voltage Undervoltage Shut-down Undervoltage Shut-down Hysteresis Overvoltage Shut-down On State Resistance Test Conditions Min 5.5 3 Typ 13 4 0.5 36 IOUT=2A; Tj=25C; VCC>8V IOUT=2A; VCC>8V Off State; VCC=13V; VIN=VOUT =0V IS Supply Current Off State; VCC=13V; VIN=VOUT=0V; Tj=25C On State; VCC=13V; VIN=5V; IOUT=0A IL(off1) IL(off2) IL(off3) IL(off4) Off State Off State Off State Off State Output Current Output Current Output Current Output Current VIN=VOUT=0V VIN=0V; VOUT =3.5V VIN=VOUT=0V; Vcc=13V; Tj =125C VIN=VOUT=0V; Vcc=13V; Tj =25C 0 -75 (#) 10 10 2 (#) 60 120 25 20 3.5 50 0 5 3 Max 36 5.5 Unit V V V V m m A A mA A A A A

SWITCHING (V CC=13V)

Symbol td(on) td(off) dVOUT/dt(on) dVOUT/dt(off) Parameter Turn-on Delay Time Turn-off Delay Time Turn-on Voltage Slope Turn-off Voltage Slope Test Conditions RL=6.5 from VIN rising edge to VOUT=1.3V RL=6.5 from VIN falling edge to VOUT =11.7V RL=6.5 from VOUT=1.3V to VOUT=10.4V RL=6.5 from VOUT=11.7V to VOUT =1.3V Min Typ 40 30 (#) (#) Max Unit s s V/s V/s

INPUT PIN

Symbol VIL IIL VIH IIH Vhyst VICL Parameter Input Low Level Low Level Input Current Input High Level High Level Input Current Input Hysteresis Voltage Input Clamp Voltage Test Conditions VIN=1.25V VIN=3.25V IIN=1mA IIN=-1mA 0.5 6 Min 1 3.25 Typ (#) (#) (#) (#) (#) 6.8 -0.7 Max 1.25 Unit V A V A V V V

10 8

(#) See relative diagram

3/31

VN750 / VN750S / VN750PT / VN750-B5

ELECTRICAL CHARACTERISTICS (continued) VCC - OUTPUT DIODE

Symbol VF Parameter Forward on Voltage Test Conditions -IOUT=1.3A; Tj=150C Min Typ Max 0.6 Unit V

STATUS PIN

Symbol VSTAT ILSTAT CSTAT VSCL Parameter Status Low Output Voltage Status Leakage Current Status Pin Input Capacitance Status Clamp Voltage Test Conditions ISTAT =1.6mA Normal Operation; VSTAT=5V Normal Operation; VSTAT=5V ISTAT =1mA ISTAT =-1mA 6 6.8 -0.7 Min Typ (#) (#) Max 0.5 10 100 8 Unit V A pF V V

PROTECTIONS (See note 1)

Symbol TTSD TR Thyst tSDL Ilim Vdemag Parameter Shut-down Temperature Reset Temperature Thermal Hysteresis Status delay in overload condition Current limitation Turn-off Output Clamp Voltage Test Conditions Min 150 135 7 Typ 175 15 20 6 9 15 15 VCC-41 VCC-48 VCC-55 Max 200 Unit C C C s A A V

Tj>Tjsh 9V<VCC<36V 5V<VCC<36V IOUT=2A; VIN=0V; L=6mH

Note 1: To ensure long term reliability under heavy overload or short circuit conditions, protection and related diagnostic signals must be used together with a proper software strategy. If the device operates under abnormal conditions this software must limit the duration and number of activation cycles. (#) See relative diagram

4/31

VN750 / VN750S / VN750PT / VN750-B5

ELECTRICAL CHARACTERISTICS (continued) OPENLOAD DETECTION

Symbol IOL tDOL(on) Parameter Openload ON State Detection Threshold Openload ON State Detection Delay Openload OFF State Voltage Detection Threshold Openload Detection Delay at Turn Off Test Conditions VIN=5V IOUT =0A Min 50 Typ (#) Max 200 200 Unit mA s

VOL tDOL(off)

VIN=0V

1.5

(#)

3.5

V s

1000

OPEN LOAD STATUS TIMING (with external pull-up) IOUT< IOL VOUT > VOL VIN VIN

OVERTEMP STATUS TIMING Tj > Tjsh

VSTAT

VSTAT

tDOL(off)

tDOL(on)

tSDL

tSDL

5/31

VN750 / VN750S / VN750PT / VN750-B5

Switching time Waveforms

VOUT 90% 80%

dVOUT/dt(on)

dVOUT/dt(off)

10%

t

VIN td(on)

td(off)

TRUTH TABLE

CONDITIONS Normal Operation Current Limitation Overtemperature Undervoltage Overvoltage Output Voltage > VOL Output Current < IOL INPUT L H L H H L H L H L H L H L H OUTPUT L H L X X L L L L L L H H L H STATUS H H H (Tj < TTSD) H (Tj > TTSD) L H L X X H H L H H L

6/31

VN750 / VN750S / VN750PT / VN750-B5

ELECTRICAL TRANSIENT REQUIREMENTS ON VCC PIN

ISO T/R 7637/1 Test Pulse 1 2 3a 3b 4 5 ISO T/R 7637/1 Test Pulse 1 2 3a 3b 4 5 CLASS C E I C C C C C C I -25 V +25 V -25 V +25 V -4 V +26.5 V II -50 V +50 V -50 V +50 V -5 V +46.5 V TEST LEVELS III -75 V +75 V -100 V +75 V -6 V +66.5 V TEST LEVELS RESULTS II III C C C C C E C C C C C E IV -100 V +100 V -150 V +100 V -7 V +86.5 V Delays and Impedance 2 ms 10 0.2 ms 10 0.1 s 50 0.1 s 50 100 ms, 0.01 400 ms, 2

IV C C C C C E

CONTENTS All functions of the device are performed as designed after exposure to disturbance. One or more functions of the device is not performed as designed after exposure to disturbance and cannot be returned to proper operation without replacing the device.

7/31

VN750 / VN750S / VN750PT / VN750-B5

Figure 1: Waveforms

NORMAL OPERATION INPUT LOAD VOLTAGE STATUS UNDERVOLTAGE VCC VUSD INPUT LOAD VOLTAGE STATUS undefined VUSDhyst

OVERVOLTAGE VCC<VOV VCC INPUT LOAD VOLTAGE STATUS OPEN LOAD with external pull-up INPUT LOAD VOLTAGE STATUS VOUT >VOL VOL VCC>VOV

OPEN LOAD without external pull-up INPUT LOAD VOLTAGE STATUS

Tj INPUT LOAD CURRENT STATUS

TTSD TR

OVERTEMPERATURE

8/31

1 1

VN750 / VN750S / VN750PT / VN750-B5

APPLICATION SCHEMATIC

+5V

+5V

Rprot STATUS

VCC

Dld C Rprot INPUT OUTPUT

GND

VGND

RGND

DGND

GND PROTECTION REVERSE BATTERY

NETWORK

AGAINST

Solution 1: Resistor in the ground line (RGND only). This can be used with any type of load. The following is an indication on how to dimension the RGND resistor. 1) RGND 600mV / (IS(on)max). 2) RGND (VCC) / (-IGND) where -IGND is the DC reverse ground pin current and can be found in the absolute maximum rating section of the devices datasheet. Power Dissipation in RGND (when VCC<0: during reverse battery situations) is: PD= (-VCC)2/RGND This resistor can be shared amongst several different HSD. Please note that the value of this resistor should be calculated with formula (1) where IS(on)max becomes the sum of the maximum on-state currents of the different devices. Please note that if the microprocessor ground is not common with the device ground then the RGND will produce a shift (IS(on)max * RGND) in the input thresholds and the status output values. This shift will vary depending on many devices are ON in the case of several high side drivers sharing the same RGND. If the calculated power dissipation leads to a large resistor or several devices have to share the same resistor then the ST suggests to utilize Solution 2 (see below). Solution 2: A diode (DGND) in the ground line. A resistor (RGND=1k) should be inserted in parallel to DGND if the device will be driving an inductive load.

This small signal diode can be safely shared amongst several different HSD. Also in this case, the presence of the ground network will produce a shift (j600mV) in the input threshold and the status output values if the microprocessor ground is not common with the device ground. This shift will not vary if more than one HSD shares the same diode/resistor network. Series resistor in INPUT and STATUS lines are also required to prevent that, during battery voltage transient, the current exceeds the Absolute Maximum Rating. Safest configuration for unused INPUT and STATUS pin is to leave them unconnected.

LOAD DUMP PROTECTION

Dld is necessary (Voltage Transient Suppressor) if the load dump peak voltage exceeds VCC max DC rating. The same applies if the device will be subject to transients on the VCC line that are greater than the ones shown in the ISO T/R 7637/1 table.

C I/Os PROTECTION:

If a ground protection network is used and negative transients are present on the VCC line, the control pins will be pulled negative. ST suggests to insert a resistor (Rprot) in line to prevent the C I/Os pins to latch-up. The value of these resistors is a compromise between the leakage current of C and the current required by the HSD I/Os (Input levels compatibility) with the latch-up limit of C I/Os. -VCCpeak/Ilatchup Rprot (VOHC-VIH-VGND) / IIHmax Calculation example: For VCCpeak= - 100V and Ilatchup 20mA; VOHC 4.5V 5k Rprot 65k. Recommended Rprot value is 10k. 9/31

VN750 / VN750S / VN750PT / VN750-B5

OPEN LOAD DETECTION IN OFF STATE

Off state open load detection requires an external pull-up resistor (RPU) connected between OUTPUT pin and a positive supply voltage (VPU) like the +5V line used to supply the microprocessor. The external resistor has to be selected according to the following requirements: 1) no false open load indication when load is connected: in this case we have to avoid VOUT to be higher than VOlmin; this results in the following condition VOUT=(VPU/(RL+RPU))RL<VOlmin. 2) no misdetection when load is disconnected: in this case the VOUT has to be higher than VOLmax; this results in the following condition RPU<(VPUVOLmax)/ IL(off2). Because Is(OFF) may significantly increase if Vout is pulled high (up to several mA), the pull-up resistor RPU should be connected to a supply that is switched OFF when the module is in standby. The values of VOLmin, VOLmax and IL(off2) are available in the Electrical Characteristics section.

Open Load detection in off state

V batt.

VPU

VCC RPU INPUT DRIVER + LOGIC OUT + R STATUS VOL RL IL(off2)

GROUND

10/31

VN750 / VN750S / VN750PT / VN750-B5

Off State Output Current

IL(off1) (uA)

3 2.5 2 1.5 4 1 3 0.5 0 -0.5 -1 -50 -25 0 25 50 75 100 125 150 175 2

High Level Input Current

Iih (uA)

7

Off state Vcc=36V Vin=Vout=0V

Vin=3.25V

5

0 -50 -25 0 25 50 75 100 125 150 175

Tc (C)

Tc (C)

Input Clamp Voltage

Vicl (V)

8 7.8

Status Leakage Current

Ilstat (uA)

0.05

Iin=1mA

7.6 7.4 7.2 7 6.8 6.6 6.4 6.2 6 -50 -25 0 25 50 75 100 125 150 175 0 -50 -25 0 25 50 75 100 125 150 175 0.01 0.02 0.03 0.04

Vstat=5V

Tc (C)

Tc (C)

Status Low Output Voltage

Vstat (V)

0.6

Status Clamp Voltage

Vscl (V)

8 7.8

0.5

Istat=1mA

7.6

Istat=1.6mA

0.4 7.4 7.2 0.3 7 6.8 0.2 6.6 6.4 6.2 0 -50 -25 0 25 50 75 100 125 150 175 6 -50 -25 0 25 50 75 100 125 150 175

0.1

Tc (C)

Tc (C)

11/31

VN750 / VN750S / VN750PT / VN750-B5

On State Resistance Vs Tcase

Ron (mOhm)

140

On State Resistance Vs VCC

Ron (mOhm)

120 110

120

100

Iout=2A Vcc=8V; 13V; 36V

Iout=2A

100

Tc= 150C

90 80

80

Tc= 125C

70 60 50

60

40

Tc= 25C

40

20 30 0 -50 -25 0 25 50 75 100 125 150 175 20 5 10 15 20 25

Tc= - 40C

30

35

40

Tc (C)

Vcc (V)

Openload On State Detection Threshold

Iol (mA)

220 200 180 160 140 120

Input High Level

Vih (V)

3.6 3.4 3.2 3 2.8

Vcc=13V Vin=5V

100 80 60 40 20 0 -50 -25 0 25 50 75 100 125 150 175 2.2 2 -50 -25 0 25 50 75 100 125 150 175 2.6 2.4

Tc (C)

Tc (C)

Input Low Level

Vil (V)

2.8 2.6 2.4 2.2 2

Input Hysteresis Voltage

Vhyst (V)

1.5 1.4 1.3 1.2 1.1 1

1.8 0.9 1.6 1.4 1.2 1 -50 -25 0 25 50 75 100 125 150 175 0.8 0.7 0.6 0.5 -50 -25 0 25 50 75 100 125 150 175

Tc (C)

Tc (C)

12/31

VN750 / VN750S / VN750PT / VN750-B5

Overvoltage Shutdown

Vov (V)

50 48 46 4 44 42 40 38 36 2 34 32 30 -50 -25 0 25 50 75 100 125 150 175 1.5 1 -50 -25 0 25 50 75 100 125 150 175 3.5 3 2.5

Openload Off State Voltage Detection Threshold

Vol (V)

5 4.5

Vin=0V

Tc (C)

Tc (C)

Turn-on Voltage Slope

dVout/dt/(on) (V/ms)

1000 900 800 700 600 500 400 300 200 100 0 -50 -25 0 25 50 75 100 125 150 175

Turn-off Voltage Slope

dVout/dt(off) (V/ms)

500 450

Vcc=13V Rl=6.5Ohm

400 350 300 250 200 150 100 50 0 -50 -25

Vcc=13V Rl=6.5Ohm

25

50

75

100

125

150

175

Tc (C)

Tc (C)

Ilim Vs T case

Ilim (A)

20 18

Vcc=13V

16 14 12 10 8 6 4 2 0 -50 -25 0 25 50 75 100 125 150 175

Tc (C)

13/31

VN750 / VN750S / VN750PT / VN750-B5

SO-8 Maximum turn off current versus load inductance

ILMAX (A) 100

10

A B C

1 0.1

A = Single Pulse at TJstart=150C B= Repetitive pulse at T Jstart=100C C= Repetitive Pulse at T Jstart=125C Conditions: VCC=13.5V Values are generated with R L=0 In case of repetitive pulses, Tjstart (at beginning of each demagnetization) of every pulse must not exceed the temperature specified above for curves B and C. VIN, IL Demagnetization Demagnetization Demagnetization

1 L(mH)

10

100

14/31

VN750 / VN750S / VN750PT / VN750-B5

PPAK, P 2PAK Maximum turn off current versus load inductance

ILMAX (A) 100

10

A B C

1 0.1

A = Single Pulse at TJstart=150C B= Repetitive pulse at T Jstart=100C C= Repetitive Pulse at T Jstart=125C Conditions: VCC=13.5V Values are generated with R L=0 In case of repetitive pulses, Tjstart (at beginning of each demagnetization) of every pulse must not exceed the temperature specified above for curves B and C. VIN, IL Demagnetization Demagnetization Demagnetization

1 L(mH)

10

100

15/31

VN750 / VN750S / VN750PT / VN750-B5

SO-8 THERMAL DATA

SO-8 PC Board

Layout condition of Rth and Zth measurements (PCB FR4 area= 58mm x 58mm, PCB thickness=2mm, Cu thickness=35m, Copper areas: 0.14cm2, 0.8cm2, 2cm2).

Rthj-amb Vs PCB copper area in open box free air condition

RTHj_amb (C/W)

SO-8 at 2 pins connected to TAB

110 105 100 95 90 85 80 75 70 0 0.5 1 1.5 2 2.5

PCB Cu heatsink area (cm^2)

16/31

VN750 / VN750S / VN750PT / VN750-B5

P2PAK THERMAL DATA

P2PAK PC Board

Layout condition of Rth and Zth measurements (PCB FR4 area= 60mm x 60mm, PCB thickness=2mm, Cu thickness=35m, Copper areas: 0.97cm2, 8cm2).

Rthj-amb Vs PCB copper area in open box free air condition

RTHj_amb (C/W)

55

Tj-Tamb=50C

50 45 40 35 30

0 2 4 6 8 10

PCB Cu heatsink area (cm^2)

17/31

VN750 / VN750S / VN750PT / VN750-B5

PPAK THERMAL DATA

PPAK PC Board

Layout condition of Rth and Zth measurements (PCB FR4 area= 60mm x 60mm, PCB thickness=2mm, Cu thickness=35m, Copper areas: 0.44cm2, 8cm2).

Rthj-amb Vs PCB copper area in open box free air condition

RTHj_amb (C/W)

90 80 70 60 50 40 30 20 10 0 0 2 4 6 8 10

PCB Cu heatsink area (cm^2)

18/31

VN750 / VN750S / VN750PT / VN750-B5

SO-8 Thermal Impedance Junction Ambient Single Pulse

ZTH (C/W) 1000

100

0.5 cm2 2 cm2

10

0.1

0.01 0.0001 0.001 0.01 0.1 1 Time (s) 10 100 1000

Thermal fitting model of a single channel HSD in SO-8

Pulse calculation formula

Z TH = R TH + Z THtp ( 1 )

where

= tp T

0.5 0.05 0.8 3.5 21 16 58 0.006 2.60E-03 0.0075 0.045 0.35 1.05 2

Thermal Parameter

Area/island (cm2) R1 (C/W) R2 (C/W) R3 ( C/W) R4 (C/W) R5 (C/W) R6 (C/W) C1 (W.s/C) C2 (W.s/C) C3 (W.s/C) C4 (W.s/C) C5 (W.s/C) C6 (W.s/C)

Tj

C1

C2

C3

C4

C5

C6

R1

R2

R3

R4

R5

R6

Pd

28

T_amb

19/31

VN750 / VN750S / VN750PT / VN750-B5

PPAK Thermal Impedance Junction Ambient Single Pulse

ZTH (C/W) 1000

100

0.44 cm2 6 cm2

10

0.1 0.0001 0.001 0.01 0.1 1 T ime (s) 10 100 1000

Thermal fitting model of a single channel HSD in PPAK

Pulse calculation formula

Z TH = R TH + Z THtp ( 1 )

where

= tp T

0.5 0.15 0.7 1.6 2 15 61 0.0006 0.0025 0.08 0.3 0.45 0.8 6

Thermal Parameter

Area/island (cm2) R1 (C/W) R2 (C/W) R3 ( C/W) R4 (C/W) R5 (C/W) R6 (C/W) C1 (W.s/C) C2 (W.s/C) C3 (W.s/C) C4 (W.s/C) C5 (W.s/C) C6 (W.s/C)

Tj

C1

C2

C3

C4

C5

C6

R1

R2

R3

R4

R5

R6

Pd

24

T_amb

20/31

VN750 / VN750S / VN750PT / VN750-B5

P2PAK Thermal Impedance Junction Ambient Single Pulse

ZTH (C/W) 1000

100

0.5 cm 2 6 cm2

10

0.1 0.0001 0.001 0.01 0.1 1 Time (s) 10 100 1000

Thermal fitting model of a single channel HSD in P 2PAK

Pulse calculation formula

Z TH = R T H + Z THtp ( 1 )

where

= tp T

0.5 0.15 0.7 0.7 4 9 37 0.0006 0.0025 0.055 0.4 2 3 6

Thermal Parameter

Area/island (cm2) R1 (C/W) R2 (C/W) R3 ( C/W) R4 (C/W) R5 (C/W) R6 (C/W) C1 (W.s/C) C2 (W.s/C) C3 (W.s/C) C4 (W.s/C) C5 (W.s/C) C6 (W.s/C)

Tj

C1

C2

C3

C4

C5

C6

R1

R2

R3

R4

R5

R6

Pd

22

T_amb

21/31

VN750 / VN750S / VN750PT / VN750-B5

SO-8 MECHANICAL DATA

mm. MIN. 0.1 0.65 0.35 0.19 0.25 4.8 5.8 1.27 3.81 3.8 0.4 4 1.27 0.6 8 (max.) 0.8 1.2 0.031 0.047 0.14 0.015 TYP MAX. 1.75 0.25 1.65 0.85 0.48 0.25 0.5 45 (typ.) 5 6.2 0.188 0.228 0.050 0.150 0.157 0.050 0.023 0.196 0.244 0.025 0.013 0.007 0.010 0.003 MIN. inch TYP. MAX. 0.068 0.009 0.064 0.033 0.018 0.010 0.019

DIM. A a1 a2 a3 b b1 C c1 D E e e3 F L M S L1

22/31

VN750 / VN750S / VN750PT / VN750-B5

PENTAWATT (VERTICAL) MECHANICAL DATA

DIM. A C D D1 E F F1 G G1 H2 H3 L L1 L2 L3 L5 L6 L7 M M1 Diam. 3.65 2.6 15.1 6 4.5 4 3.85 0.144 10.05 17.85 15.75 21.4 22.5 3 15.8 6.6 0.102 0.594 0.236 0.177 0.157 0.152 2.4 1.2 0.35 0.8 1 3.2 6.6 3.4 6.8 mm. MIN. TYP MAX. 4.8 1.37 2.8 1.35 0.55 1.05 1.4 3.6 7 10.4 10.4 0.396 0.703 0.620 0.843 0.886 0.118 0.622 0.260 0.094 0.047 0.014 0.031 0.039 0.126 0.260 0.134 0.268 MIN. inch TYP. MAX. 0.189 0.054 0.110 0.053 0.022 0.041 0.055 0.142 0.276 0.409 0.409

23/31

VN750 / VN750S / VN750PT / VN750-B5

P2PAK MECHANICAL DATA

DIM. A A1 A2 b c c2 D D2 E E1 e e1 L L2 L3 L5 R V2 Package Weight 0 1.40 Gr (typ) 3.20 6.60 13.70 1.25 0.90 1.55 0.40 8 10.00 8.50 3.60 7.00 14.50 1.40 1.70 2.40 mm. MIN. 4.30 2.40 0.03 0.80 0.45 1.17 8.95 8.00 10.40 TYP MAX. 4.80 2.80 0.23 1.05 0.60 1.37 9.35

P010R

24/31

VN750 / VN750S / VN750PT / VN750-B5

PPAK MECHANICAL DATA

DIM. A A1 A2 B B2 C C2 D1 D E E1 e G G1 H L2 L4 R V2 Package Weight 0 Gr. 0.3 0.60 0.2 8 4.90 2.38 9.35 0.8 6.00 6.40 4.7 1.27 5.25 2.70 10.10 1.00 1.00 MIN. 2.20 0.90 0.03 0.40 5.20 0.45 0.48 5.1 6.20 6.60 TYP MAX. 2.40 1.10 0.23 0.60 5.40 0.60 0.60

P032T1

25/31

VN750 / VN750S / VN750PT / VN750-B5

SO-8 TUBE SHIPMENT (no suffix)

Base Q.ty Bulk Q.ty Tube length ( 0.5) A B C ( 0.1)

All dimensions are in mm.

100 2000 532 3.2 6 0.6

TAPE AND REEL SHIPMENT (suffix 13TR) REEL DIMENSIONS

Base Q.ty Bulk Q.ty A (max) B (min) C ( 0.2) F G (+ 2 / -0) N (min) T (max) 2500 2500 330 1.5 13 20.2 12.4 60 18.4

All dimensions are in mm.

TAPE DIMENSIONS

According to Electronic Industries Association (EIA) Standard 481 rev. A, Feb 1986 Tape width Tape Hole Spacing Component Spacing Hole Diameter Hole Diameter Hole Position Compartment Depth Hole Spacing W P0 ( 0.1) P D ( 0.1/-0) D1 (min) F ( 0.05) K (max) P1 ( 0.1) 12 4 8 1.5 1.5 5.5 4.5 2

End

All dimensions are in mm.

Start Top cover tape 500mm min Empty components pockets saled with cover tape. User direction of feed 500mm min No components Components No components

26/31

VN750 / VN750S / VN750PT / VN750-B5

PENTAWATT TUBE SHIPMENT (no suffix)

Base Q.ty Bulk Q.ty Tube length ( 0.5) A B C ( 0.1)

All dimensions are in mm.

50 1000 532 18 33.1 1

27/31

VN750 / VN750S / VN750PT / VN750-B5

P2PAK TUBE SHIPMENT (no suffix)

Base Q.ty Bulk Q.ty Tube length ( 0.5) A B C ( 0.1)

All dimensions are in mm.

50 1000 532 18 33.1 1

TAPE AND REEL SHIPMENT (suffix 13TR) REEL DIMENSIONS

Base Q.ty Bulk Q.ty A (max) B (min) C ( 0.2) F G (+ 2 / -0) N (min) T (max) 1000 1000 330 1.5 13 20.2 24.4 60 30.4

All dimensions are in mm.

TAPE DIMENSIONS

According to Electronic Industries Association (EIA) Standard 481 rev. A, Feb 1986 Tape width Tape Hole Spacing Component Spacing Hole Diameter Hole Diameter Hole Position Compartment Depth Hole Spacing W P0 ( 0.1) P D ( 0.1/-0) D1 (min) F ( 0.05) K (max) P1 ( 0.1) 24 4 16 1.5 1.5 11.5 6.5 2

End

All dimensions are in mm.

Start Top cover tape No components 500mm min Empty components pockets saled with cover tape. User direction of feed 500mm min Components No components

28/31

VN750 / VN750S / VN750PT / VN750-B5

PPAK SUGGESTED PAD LAYOUT

A C

PPAK TUBE SHIPMENT (no suffix)

Base Q.ty Bulk Q.ty Tube length ( 0.5) A B C ( 0.1)

All dimensions are in mm.

75 3000 532 6 21.3 0.6

1.8

6.7

TAPE AND REEL SHIPMENT (suffix 13TR) REEL DIMENSIONS

Base Q.ty Bulk Q.ty A (max) B (min) C ( 0.2) F G (+ 2 / -0) N (min) T (max) 2500 2500 330 1.5 13 20.2 16.4 60 22.4

All dimensions are in mm.

TAPE DIMENSIONS

According to Electronic Industries Association (EIA) Standard 481 rev. A, Feb 1986 Tape width Tape Hole Spacing Component Spacing Hole Diameter Hole Diameter Hole Position Compartment Depth Hole Spacing W P0 ( 0.1) P D ( 0.1/-0) D1 (min) F ( 0.05) K (max) P1 ( 0.1) 16 4 8 1.5 1.5 7.5 2.75 2

End

All dimensions are in mm.

Start Top cover tape No components 500mm min Empty components pockets saled with cover tape. User direction of feed 500mm min Components No components

29/31

VN750 / VN750S / VN750PT / VN750-B5

REVISION HISTORY

Date Revision Description of Changes - Current and voltage convention update (page 2). - Configuration diagram (top view) & suggested connections for unused and n.c. pins insertion (page 2). May 2004 1 - 6cm2 Cu condition insertion in Thermal Data table (page 3). - VCC - OUTPUT DIODE section update (page 4). - Revision History table insertion (page 30). - Disclaimers update (page 31).

30/31

VN750 / VN750S / VN750PT / VN750-B5

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics. The ST logo is a trademark of STMicroelectronics. All other names are the property of their respective owners 2004 STMicroelectronics - Printed in ITALY- All Rights Reserved. STMicroelectronics GROUP OF COMPANIES Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States http://www.st.com

31/31

Potrebbero piacerti anche

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (120)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- Frequency Measurement and Switching Instruments: Operating InstructionsDocumento26 pagineFrequency Measurement and Switching Instruments: Operating Instructionsdylan_dearing@hotmail.comNessuna valutazione finora

- VMM1615 Instruction BookDocumento77 pagineVMM1615 Instruction BookYASIN100% (1)

- Powerso16: Outline and Mechanical DataDocumento1 paginaPowerso16: Outline and Mechanical DataDan EsentherNessuna valutazione finora

- Powersso-24 Mechanical Data: Dim. Mm. Min. Typ MaxDocumento1 paginaPowersso-24 Mechanical Data: Dim. Mm. Min. Typ MaxDan EsentherNessuna valutazione finora

- Pso 36Documento1 paginaPso 36Dan EsentherNessuna valutazione finora

- Powerso-20 Mechanical Data: Dim. Mm. Inch Min. TYP Max. Min. Typ. MaxDocumento1 paginaPowerso-20 Mechanical Data: Dim. Mm. Inch Min. TYP Max. Min. Typ. MaxDan EsentherNessuna valutazione finora

- PSSO-12 Mechanical Data: Dim. Mm. Min. TYP MaxDocumento1 paginaPSSO-12 Mechanical Data: Dim. Mm. Min. TYP MaxDan EsentherNessuna valutazione finora

- Hiquad 64Documento1 paginaHiquad 64Dan EsentherNessuna valutazione finora

- Powerso-10 Mechanical Data: Dim. Mm. Inch Min. Typ Max. Min. Typ. MaxDocumento1 paginaPowerso-10 Mechanical Data: Dim. Mm. Inch Min. Typ Max. Min. Typ. MaxDan EsentherNessuna valutazione finora

- 10833Documento18 pagine10833Dan EsentherNessuna valutazione finora

- Ppak Mechanical Data: Dim. Min. TYP MaxDocumento1 paginaPpak Mechanical Data: Dim. Min. TYP MaxDan EsentherNessuna valutazione finora

- Multipowerso-30 Mechanical Data: Dim. Mm. Min. Typ MaxDocumento1 paginaMultipowerso-30 Mechanical Data: Dim. Mm. Min. Typ MaxDan EsentherNessuna valutazione finora

- L9929Documento3 pagineL9929Dan EsentherNessuna valutazione finora

- Fully Integrated H-Bridge Motor Driver: VNH3SP30Documento26 pagineFully Integrated H-Bridge Motor Driver: VNH3SP30Dan EsentherNessuna valutazione finora

- 10832Documento26 pagine10832Dan EsentherNessuna valutazione finora

- 10831Documento21 pagine10831Dan EsentherNessuna valutazione finora

- VNQ830A-E: Quad Channel High Side DriverDocumento17 pagineVNQ830A-E: Quad Channel High Side DriverDan EsentherNessuna valutazione finora

- 10302Documento4 pagine10302Dan EsentherNessuna valutazione finora

- 10830Documento21 pagine10830Dan EsentherNessuna valutazione finora

- 10640Documento22 pagine10640Dan EsentherNessuna valutazione finora

- VND830PEP-E: Double Channel High Side DriverDocumento13 pagineVND830PEP-E: Double Channel High Side DriverDan EsentherNessuna valutazione finora

- 10683Documento19 pagine10683Dan EsentherNessuna valutazione finora

- 10311Documento23 pagine10311Dan Esenther100% (1)

- Uh 30Documento10 pagineUh 30Dan EsentherNessuna valutazione finora

- 9927Documento11 pagine9927Dan EsentherNessuna valutazione finora

- 10022Documento262 pagine10022Dan EsentherNessuna valutazione finora

- 10303Documento5 pagine10303Dan EsentherNessuna valutazione finora

- 9696Documento17 pagine9696Dan EsentherNessuna valutazione finora

- 9792Documento21 pagine9792Dan EsentherNessuna valutazione finora

- 9933Documento11 pagine9933Dan EsentherNessuna valutazione finora

- 10261Documento10 pagine10261Dan EsentherNessuna valutazione finora

- 9934Documento11 pagine9934Dan EsentherNessuna valutazione finora

- Din Dual Colour Display Temperature Indicator Product ManualDocumento40 pagineDin Dual Colour Display Temperature Indicator Product ManualRicardo CarrascoNessuna valutazione finora

- Unit - I Difference Between Microprocessor and MicrocontrollerDocumento30 pagineUnit - I Difference Between Microprocessor and MicrocontrollerGopinathan MNessuna valutazione finora

- Signet 9900 Manual InstructionDocumento64 pagineSignet 9900 Manual InstructionHearnfar99Nessuna valutazione finora

- PIC - IO PortsDocumento43 paginePIC - IO PortsElena Gilbert100% (2)

- Liebherr Liccon System: Microtec Mkii Light Control Module Input ConnectionDocumento4 pagineLiebherr Liccon System: Microtec Mkii Light Control Module Input ConnectionАлександр АндреевNessuna valutazione finora

- AD420Documento16 pagineAD420Hasan MoradiNessuna valutazione finora

- Main Features: - Set-Top-Boxes - White Goods - Home Appliances - DVD Players and VcrsDocumento25 pagineMain Features: - Set-Top-Boxes - White Goods - Home Appliances - DVD Players and VcrsDhivya NNessuna valutazione finora

- Resistors: Take A Stance, The Resist StanceDocumento35 pagineResistors: Take A Stance, The Resist Stancepavan pujarNessuna valutazione finora

- Ds191 XC7Z030 XC7Z045 Data SheetDocumento67 pagineDs191 XC7Z030 XC7Z045 Data SheetApurv SinghNessuna valutazione finora

- Infineon-Component - PSoC - 4 - SCB - V4.0-Software Module Datasheets-V04 - 00-ENDocumento217 pagineInfineon-Component - PSoC - 4 - SCB - V4.0-Software Module Datasheets-V04 - 00-ENPiyush Kumar SahooNessuna valutazione finora

- An 97055Documento16 pagineAn 97055marioAC2Nessuna valutazione finora

- A Micocotroller Based Digital Thermometer With Timer DigithermoDocumento10 pagineA Micocotroller Based Digital Thermometer With Timer DigithermoKarthik MohanNessuna valutazione finora

- nb868 User Guide v2.2.3Documento25 paginenb868 User Guide v2.2.3BENTABET AKILANessuna valutazione finora

- Tda9874ah PDFDocumento69 pagineTda9874ah PDFMiszcsi MiszcsiNessuna valutazione finora

- LC863224ADocumento21 pagineLC863224AJose SintuNessuna valutazione finora

- A Study On Adiabatic Logic Circuits For Low Power ApplicationsDocumento7 pagineA Study On Adiabatic Logic Circuits For Low Power ApplicationsNoReply ProgramNessuna valutazione finora

- Glow Plug System Control IC: FeaturesDocumento27 pagineGlow Plug System Control IC: FeaturesPiotr PodkowaNessuna valutazione finora

- Bimos Ii 8-Bit Serial-Input, Latched Drivers: Absolute Maximum Ratings at 25 C Free-Air TemperatureDocumento7 pagineBimos Ii 8-Bit Serial-Input, Latched Drivers: Absolute Maximum Ratings at 25 C Free-Air TemperatureAlexNessuna valutazione finora

- 6500Documento1.118 pagine6500apeksha_837Nessuna valutazione finora

- LM339, LM393, TL331Documento16 pagineLM339, LM393, TL331Adi PopaNessuna valutazione finora

- Avr Atmega8535Documento277 pagineAvr Atmega8535Faisal Rahman0% (1)

- Dell N5050 DV15 UMA Caruso15 HR H00RX Rev A00 MB 10316-1 Schematics PDFDocumento104 pagineDell N5050 DV15 UMA Caruso15 HR H00RX Rev A00 MB 10316-1 Schematics PDFSk SaroheNessuna valutazione finora

- HMC 7044Documento71 pagineHMC 7044Sid areNessuna valutazione finora

- LAB 4: A L F: Rithmetic Ogic UnctionsDocumento5 pagineLAB 4: A L F: Rithmetic Ogic UnctionsAhmed SajidNessuna valutazione finora

- Vlsi Lab Manual: Department of Information TechnologyDocumento135 pagineVlsi Lab Manual: Department of Information TechnologyVijay MythryNessuna valutazione finora

- Datasheet I2 C1Documento200 pagineDatasheet I2 C1HồngHàNessuna valutazione finora

- Static CMOS and Dynamic CircuitsDocumento19 pagineStatic CMOS and Dynamic CircuitsAbhijna MaiyaNessuna valutazione finora

- Zebra S-Series Parts & ServiceDocumento173 pagineZebra S-Series Parts & ServiceDusty BretchesNessuna valutazione finora