Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

EC2207 Digital Lab Manual

Caricato da

muthubeCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

EC2207 Digital Lab Manual

Caricato da

muthubeCopyright:

Formati disponibili

Sri Subramanya college of Engineering and Technology Department of ECE EC2207 - DIGITAL ELECTRONICS LAB MANUAL

SYLLABUS

1. Design and implementation of Adders and Subtractors using logic gates. 2. Design and implementation of code converters using logic gates (i) BCD to excess- code and voice versa (ii) Binar! to gra! and vice-versa . Design and implementation of " bit binar! Adder# subtractor and BCD adder using $C %"& ". Design and implementation of 2Bit 'agnitude Comparator using logic gates & Bit 'agnitude Comparator using $C %"&( (. Design and implementation of 1) bit odd#even parit! c*ec+er #generator using $C%"1&,. ). Design and implementation of 'ultiplexer and De-multiplexer using logic gates and stud! of $C%"1(, and $C %"1(" %. Design and implementation of encoder and decoder using logic gates and stud! of $C%""( and $C%"1"% &. Construction and verification of " bit ripple counter and 'od-1, # 'od-12 -ipple counters .. Design and implementation of -bit s!nc*ronous up#do/n counter 1,. $mplementation of S$S01 S$201 2$S0 and 2$20 s*ift registers using 3lip- flops. 11. Design of experiments 11)1&11, using 4erilog 5D6.

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

LIST OF EXPERIMENTS

1. Stud! of logic gates. 2. Design and implementation of adders and subtractors using logic gates. . Design and implementation of code converters using logic gates. ". Design and implementation of "-bit binar! adder#subtractor and BCD adder using $C %"& . (. Design and implementation of 2-bit magnitude comparator using logic gates1 &-bit magnitude comparator using $C %"&(. ). Design and implementation of 1)-bit odd#even parit! c*ec+er# generator using $C %"1&,. %. Design and implementation of multiplexer and demultiplexer using logic gates and stud! of $C %"1(, and $C %"1(". &. Design and implementation of encoder and decoder using logic gates and stud! of $C %""( and $C %"1"%. .. Construction and verification of "-bit ripple counter and 'od1,#'od-12 ripple counter. 1,. 11. Design and implementation of -bit s!nc*ronous up#do/n counter. $mplementation of S$S01 S$201 2$S0 and 2$20 s*ift registers using flip-flops.

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

INDEX

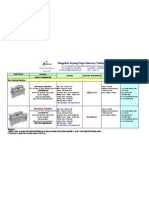

EXP. NO DATE NAME OF THE EXPERIMENT PAGE NO MARKS SIGNATURE

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

EX NO: 1 DATE:

STUDY OF LOGIC GATES

AIM: To study about logic gates and verify their truth tables. APPARATUS REQUIRED: S# o. C$MP$ E T ). A D *ATE /. $0 *ATE 1. $T *ATE ,. A D *ATE / %/P 2. $0 *ATE 3. 45$0 *ATE +. A D *ATE 1 %/P .. %C T0A% E0 6%T 7. PATC8 C$0D SPEC%&%CAT%$ %C +,-. %C +,1/ %C +,-, %C +,-%C +,-/ %C +,.3 %C +,)5 5 'T( ) ) ) ) ) ) ) ) ),

THEORY: AND GATE: The A D gate performs a logical multiplication commonly !no"n as A D function. The output is high "hen both the inputs are high. The output is lo" level "hen any one of the inputs is lo".

OR GATE: Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE The $0 gate performs a logical addition commonly !no"n as $0 function. The output is high "hen any one of the inputs is high. The output is lo" level "hen both the inputs are lo".

NOT GATE: The NAND GATE: The are high. NOR GATE: The $0 gate is a contraction of $05 $T. The output is high "hen both inputs A D gate is a contraction of A D5 $T. The output is high "hen both $T gate is called an inverter. The output is high "hen the input is lo".

The output is lo" "hen the input is high.

inputs are lo" and any one of the input is lo" .The output is lo" level "hen both inputs

are lo". The output is lo" "hen one or both inputs are high. X-OR GATE: The output is high "hen any one of the inputs is high. The output is lo" "hen both the inputs are lo" and both the inputs are high. PROCEDURE: 9i: Connections are given as per circuit diagram. 9ii: 9iii: A D *ATE; SYMBOL: #ogical inputs are given as per circuit diagram. $bserve the output and verify the truth table. PIN DIAGRAM:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

OR GATE:

$T *ATE; SYMBOL: PIN DIAGRAM:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

X-OR GATE : SYMBOL : PIN DIAGRAM :

2-INPUT NAND GATE: SYMBOL: Prepared by M.Marimuthu Assistant Professor/ ECE PIN DIAGRAM:

Sri Subramanya college of Engineering and Technology Department of ECE

3-INPUT NAND GATE :

NOR GATE:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

RESULT: The study of logic gates "ere performed by verifying their truth tables.

EX NO: 2

DATE:

DESIGN OF ADDER AND SUBTRACTOR

AIM: To design and construct half adder< full adder< half subtractor and full subtractor circuits and verify the truth table using logic gates. APPARATUS REQUIRED: Sl. o. ). /. 1. ,. 1. C$MP$ E T A D *ATE 45$0 *ATE $T *ATE $0 *ATE %C T0A% E0 6%T SPEC%&%CAT%$ %C +,-. %C +,.3 %C +,-, %C +,1/ 5 'T(. ) ) ) ) )

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

,.

PATC8 C$0DS

/1

THEORY:

HALF ADDER: A half adder has t"o inputs for the t"o bits to be added and t"o outputs one from the sum = S> and other from the carry = c> into the higher adder position. Above circuit is called as a carry signal from the addition of the less significant bits sum from the 45$0 *ate the carry out from the A D gate. FULL ADDER: A full adder is a combinational circuit that forms the arithmetic sum of input? it consists of three inputs and t"o outputs. A full adder is useful to add three bits at a time but a half adder cannot do so. %n full adder sum output "ill be ta!en from 45$0 *ate< carry output "ill be ta!en from $0 *ate. HALF SUBTRACTOR: The half subtractor is constructed using 45$0 and A D *ate. The half subtractor has t"o input and t"o outputs. The outputs are difference and borro". The difference can be applied using 45$0 *ate< borro" output can be implemented using an A D *ate and an inverter. FULL SUBTRACTOR: The full subtractor is a combination of 45$0< A D< $0< $T *ates. %n a full subtractor the logic circuit should have three inputs and t"o outputs. The t"o half subtractor put together gives a full subtractor .The first half subtractor "ill be C and A @. The output "ill be difference output of full subtractor. The eApression A@ assembles the borro" output of the half subtractor and the second term is the inverted difference output of first 45$0.

LOGIC DIAGRAM:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

HALF ADDER

TRUTH TABLE: A 0 0 1 1 K-Ma !"# SUM: B 0 1 0 1 CARRY 0 0 0 1 SUM 0 1 1 0 K-Ma !"# CARRY:

SUM $ A%B & AB% LOGIC DIAGRAM:

CARRY $ AB

FULL ADDER FULL ADDER USING T'O HALF ADDER

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

TRUTH TABLE: A 0 0 0 0 1 1 1 1 K-Ma !"# SUM: B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 CARRY 0 0 0 1 0 1 1 1 SUM 0 1 1 0 1 0 0 1

SUM $ A%B%C & A%BC% & ABC% & ABC K-Ma !"# CARRY:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

CARRY $ AB & BC & AC LOGIC DIAGRAM: HALF SUBTRACTOR

TRUTH TABLE: A 0 0 1 1 B 0 1 0 1 BORRO' DIFFERENCE 0 1 0 0 0 1 1 0

K-Ma !"# DIFFERENCE:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

DIFFERENCE $ A%B & AB% K-Ma !"# BORRO':

BORRO' $ A%B FULL SUBTRACTOR

FULL SUBTRACTOR USING T'O HALF SUBTRACTOR:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

TRUTH TABLE: A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

BORRO' DIFFERENCE 0 1 1 1 0 0 0 1 0 1 1 0 1 0 0 1

K-Ma !"# D(!!)#)*+):

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

D(!!)#)*+) $ A%B%C & A%BC% & AB%C% & ABC K-Ma !"# B"##",:

B"##", $ A%B & BC & A%C PROCEEDURE: 9i: Connections are given as per circuit diagram. 9ii: 9iii: #ogical inputs are given as per circuit diagram. $bserve the output and verify the truth table.

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

RESULT: T-) .#/.- .a01)2 "! -a1! a*3 !/11 a33)# ,)#) 4)#(!()35 A12" .-) .#/..a01)2 "! -a1! a*3 !/11 2/0.#a+."# /2(*6 1"6(+ 6a.)2 ,)#) 4)#(!()35

EX NO: 3

DATE:

DESIGN AND IMPLEMENTATION OF CODE CON7ERTOR AIM: To design and implement ,5bit 9i: @inary to gray code converter 9ii: *ray to binary code converter 9iii: @CD to eAcess51 code converter 9iv: EAcess51 to @CD code converter APPARATUS REQUIRED: Sl. o. C$MP$ E T ). 45$0 *ATE

Prepared by M.Marimuthu Assistant Professor/ ECE

SPEC%&%CAT%$ %C +,.3

'T(. )

Sri Subramanya college of Engineering and Technology Department of ECE

/. 1. ,. 2. 3.

A D *ATE $0 *ATE $T *ATE %C T0A% E0 6%T PATC8 C$0DS

%C +,-. %C +,1/ %C +,-, 5 5

) ) ) ) 12

THEORY: The availability of large variety of codes for the same discrete elements of information results in the use of different codes by different systems. A conversion circuit must be inserted bet"een the t"o systems if each uses different codes for same information. Thus< code converter is a circuit that ma!es the t"o systems compatible even though each uses different binary code. The bit combination assigned to binary code to gray code. Since each code uses four bits to represent a decimal digit. There are four inputs and four outputs. *ray code is a non5"eighted code. The input variable are designated as @1< @/< @)< @- and the output variables are designated as C1< C/< C)< Co. from the truth table< combinational circuit is designed. The @oolean functions are obtained from 65Map for each output variable. A code converter is a circuit that ma!es the t"o systems compatible even though each uses a different binary code. To convert from binary code to EAcess51 code< the input lines must supply the bit combination of elements as specified by code and the output lines generate the corresponding bit combination of code. Each one of the four maps represents one of the four outputs of the circuit as a function of the four input variables. A t"o5level logic diagram may be obtained directly from the @oolean eApressions derived by the maps. These are various other possibilities for a

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

logic diagram that implements this circuit. o" the $0 gate "hose output is CBD has been used to implement partially each of three outputs. LOGIC DIAGRAM: BINARY TO GRAY CODE CON7ERTOR

K-Ma !"# G3:

G3 $ B3 K-Ma !"# G2:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

K-Ma !"# G1:

K-Ma !"# G0:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

TRUTH TABLE: 8 B(*a#9 (* /. B3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 B0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

8 G3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

G#a9 +"3) "/. /. G2 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 G1 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 G0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0

LOGIC DIAGRAM: GRAY CODE TO BINARY CON7ERTOR

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

K-Ma !"# B3:

B3 $ G3 K-Ma !"# B2:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

K-Ma !"# B1:

K-Ma !"# B0:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

TRUTH TABLE: 8 G3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 G#a9 C"3) G2 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 G1 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 G0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 8 B3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B(*a#9 C"3) B2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 B0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 8

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

LOGIC DIAGRAM: BCD TO EXCESS-3 CON7ERTOR

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

K-Ma

!"#

E3:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

K-Ma !"# E0:

TRUTH TABLE: 8 BCD (* /. B3 B2 0 0

8 B1 0 B0 0

E:+)22 ; 3 "/. /. G3 G2 G1 0 0 1

8 G0 1

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

0 0 0 0 1 1 1 1 1 : : : : : :

1 1 1 1 0 0 0 0 1 : : : : : :

0 0 1 1 0 0 1 1 0 : : : : : :

0 1 0 1 0 1 0 1 0 : : : : : :

LOGIC DIAGRAM: EXCESS-3 TO BCD CON7ERTOR

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

K-Ma !"# A:

A $ X1 X2 & X3 X< X1 K-Ma !"# B:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

K-Ma !"# C:

K-Ma !"# D:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

TRUTH TABLE: 8 B3 0 0 0 0 0 1 1 1 1 1 E:+)22 ; 3 I* /. B2 0 1 1 1 1 0 0 0 0 1 B1 1 0 0 1 1 0 0 1 1 0 B0 1 0 1 0 1 0 1 0 1 0 8 BCD O/. /. G3 0 0 0 0 0 0 0 0 1 1 G2 0 0 0 0 1 1 1 1 0 0 G1 0 0 1 1 0 0 1 1 0 0 G0 0 1 0 1 0 1 0 1 0 1 8

PROCEDURE:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

9i: 9ii: 9iii:

Connections "ere given as per circuit diagram. #ogical inputs "ere given as per truth table $bserve the logical output and verify "ith the truth tables.

RESULT: The truth tables of the given code converters "ere verified from the circuit designed

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

EX NO: < DESIGN OF <-BIT ADDER AND SUBTRACTOR DATE : AIM: To design and implement ,5bit adder and subtractor using %C +,.1 APPARATUS REQUIRED: Sl. o. C$MP$ E T SPEC%&%CAT%$ ). %C %C +,.1 /. E45$0 *ATE %C +,.3 1. $T *ATE %C +,-, 1. %C T0A% E0 6%T 5 ,. PATC8 C$0DS 5 THEORY: < BIT BINARY ADDERS: A binary adder is a digital circuit that produces the arithmetic sum of t"o binary numbers. %t can be constructed "ith full adders connected in cascade< "ith the output carry from each full adder connected to the input carry of neAt full adder in chain. The augends bits of =A> and the addend bits of =@> are designated by subscript numbers from right to left< "ith subscript - denoting the least significant bits. The carries are connected in chain through the full adder. The input carry to the adder is C - and it ripples through the full adder to the output carry C,. < BIT BINARY SUBTRACTOR The circuit for subtracting A5@ consists of an adder "ith inverters< placed bet"een each data input =@> and the corresponding input of full adder. The input carry C- must be eCual to ) "hen performing subtraction. < BIT BINARY ADDER=SUBTRACTOR:

Prepared by M.Marimuthu Assistant Professor/ ECE

'T(. ) ) ) ) ,-

Sri Subramanya college of Engineering and Technology Department of ECE

The addition and subtraction operation can be combined into one circuit "ith one common binary adder. The mode input M controls the operation. Dhen ME-< the circuit is adder circuit. Dhen ME)< it becomes subtractor. < BIT BCD ADDERS: Consider the arithmetic addition of t"o decimal digits in @CD< together "ith an input carry from a previous stage. Since each input digit does not eAceed 7< the output sum cannot be greater than )7< the ) in the sum being an input carry. The output of t"o decimal digits must be represented in @CD and should appear in the form listed in the columns. A@CD adder that adds / @CD digits and produce a sum digit in @CD The / decimal digits< together "ith the input carry< are first added in the top , bit adder to produce the binary sum. PIN DIAGRAM FOR IC 7<>3:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

LOGIC DIAGRAM: <-BIT BINARY ADDER

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

LOGIC DIAGRAM: <-BIT BINARY SUBTRACTOR

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

LOGIC DIAGRAM: <-BIT BINARY ADDER=SUBTRACTOR

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

TRUTH TABLE:

I* /. Da.a A

I* /. Da.a B C 0 1 0 0 1 1 1

A33(.("* S< S3 S2 S1 1 0 1 1 0 1 0 0 0 0 0 0 0 1 1 0 1 0 1 1 1 0 0 0 0 0 0 1 B 1 1 0 0 0 0 0

S/0.#a+.("* D< D3 D2 D1 0 0 1 1 1 1 1 1 0 0 0 1 1 1 1 0 1 1 1 1 0 0 0 0 0 1 1 1

A< A3 A2 A1 B< B3 B2 B1 1 1 0 0 1 1 1 0 0 0 0 0 1 0 0 0 1 0 1 1 1 0 0 0 1 0 0 0 0 1 1 0 1 1 1 0 0 0 1 0 1 1 1 0 0 1 1 1 0 0 0 0 1 1 1 1

LOGIC DIAGRAM: BCD ADDER

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

K MAP

Y $ S< ?S3 & S2@ TRUTH TABLE:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE S< 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 BCD SUM S3 S2 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 S1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 CARRY C 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1

PROCEDURE: 9i: 9ii: 9iii: RESULT:

The truth tables of , bit adder/subtractor and @CD "ere verified.

Connections "ere given as per circuit diagram. #ogical inputs "ere given as per truth table $bserve the logical output and verify "ith the truth tables.

EX NO: A DATE:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

DESIGN AND IMPLEMENTATION OF MAGNITUDE COMPARATOR AIM: To design and implement 9i: 9ii: / F bit magnitude comparator using basic gates. . F bit magnitude comparator using %C +,.2.

APPARATUS REQUIRED: Sl. o. ). /. 1. ,. 2. 3. +. C$MP$ E T A D *ATE 45$0 *ATE $0 *ATE $T *ATE ,5@%T MA* %TGDE C$MPA0AT$0 %C T0A% E0 6%T PATC8 C$0DS SPEC%&%CAT%$ %C +,-. %C +,.3 %C +,1/ %C +,-, %C +,.2 5 5 'T(. / ) ) ) / ) 1-

THEORY: The comparison of t"o numbers is an operator that determine one number is greater than< less than 9or: eCual to the other number. A magnitude comparator is a combinational circuit that compares t"o numbers A and @ and determine their relative magnitude. The outcome of the comparator is specified by three binary variables that indicate "hether AH@< AE@ 9or: AI@. A E A1 A/ A) A@ E @1 @/ @) @Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

The eCuality of the t"o numbers and @ is displayed in a combinational circuit designated by the symbol 9AE@:. This indicates A greater than @< then inspect the relative magnitude of pairs of significant digits starting from most significant position. A is - and that of @ is -. De have AI@< the seCuential comparison can be eApanded as AH@ E A1@1) B 41A/@/) B 414/A)@)) B 414/4)A-@-) AI@ E A1)@1 B 41A/)@/ B 414/A))@) B 414/4)A-)@The same circuit can be used to compare the relative magnitude of t"o @CD digits. Dhere< A E @ is eApanded as< A E @ E 9A1 B @1: 9A/ B @/: 9A) B @): 9A- B @-: A1 A/ A) A-

LOGIC DIAGRAM: 2 BIT MAGNITUDE COMPARATOR

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

K MAP

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

TRUTH TABLE A1 A0 B1 B0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 ABB 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0 A$B 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 ACB 0 1 1 1 0 0 1 1 0 0 0 1 0 0 0 0

PIN DIAGRAM FOR IC 7<>A:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

LOGIC DIAGRAM: > BIT MAGNITUDE COMPARATOR

TRUTH TABLE:

A 0000 0001 0000 0000 0001 0000 0000 0000 0001

B 0000 0000 0001

ABB 0 1 0

A$B 1 0 0

ACB 0 0 1

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

PROCEDURE: 9i: 9ii: 9iii: Connections are given as per circuit diagram. #ogical inputs are given as per circuit diagram. $bserve the output and verify the truth table.

RESULT: The truth tables of magnitude comparator "ere verified.

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

EX NO: D DATE: 1D BIT ODD=E7EN PARITY CHECKER =GENERATOR AIM: To design and implement )3 bit odd/even parity chec!er generator using %C +,).-. APPARATUS REQUIRED: Sl. o. ). ). /. 1. C$MP$ E T $T *ATE %C T0A% E0 6%T PATC8 C$0DS SPEC%&%CAT%$ %C +,-, %C +,).5 5 'T(. ) / ) 1-

THEORY: A parity bit is used for detecting errors during transmission of binary information. A parity bit is an eAtra bit included "ith a binary message to ma!e the number is either even or odd. The message including the parity bit is transmitted and then chec!ed at the receiver ends for errors. An error is detected if the chec!ed parity bit doesn>t correspond to the one transmitted. The circuit that generates the parity bit in the transmitter is called a =parity generator> and the circuit that chec!s the parity in the receiver is called a =parity chec!er>. %n even parity< the added parity bit "ill ma!e the total number is even amount. %n odd parity< the added parity bit "ill ma!e the total number is odd

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

amount. The parity chec!er circuit chec!s for possible errors in the transmission. %f the information is passed in even parity< then the bits reCuired must have an even number of )>s. An error occur during transmission< if the received bits have an odd number of )>s indicating that one bit has changed in value during transmission. PIN DIAGRAM FOR IC 7<1>0:

FUNCTION TABLE: INPUTS N/E0)# "! H(6- Da.a I* /.2 ?I0 ; I7@ E7EN ODD E7EN ODD X X

PE 1 1 0 0 1 0

PO 0 0 1 1 1 0

OUTPUTS FE JO 1 0 0 1 0 1 0 1 1 0 0 1

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

LOGIC DIAGRAM: 1D BIT ODD=E7EN PARITY CHECKER

TRUTH TABLE:

I7 ID IA I< I3 I2 I1 I0 I7%ID%IA%I<%I3%I2%11% I0% A+.(4) 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 1 1 0 0 0 0 0 0 1 1 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 1 1 0 1

FE 1 1 0

FO 0 0 1

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

LOGIC DIAGRAM: 1D BIT ODD=E7EN PARITY GENERATOR

TRUTH TABLE: I7 ID IA I< I3 I2 I1 I0 1 1 0 0 0 0 0 0 1 1 0 0 0 0 0 0 1 1 0 0 0 0 0 0 I7 ID IA I< I3 I2 I1 I0 A+.(4) 1 1 0 0 0 0 0 0 1 1 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 FE 1 0 1 FO 0 1 0

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

PROCEDURE: 9i: 9ii: 9iii: Connections are given as per circuit diagram. #ogical inputs are given as per circuit diagram. $bserve the output and verify the truth table.

RESULT:

The truth table of )3 bit odd/even parity generator and chec!er "as verified successfully.

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

EX NO: 7 DATE: DESIGN AND IMPLEMENTATION OF MULTIPLEXER AND DEMULTIPLEXER AIM: To design and implement multipleAer and demultipleAer using logic gates and study of %C +,)2- and %C +,)2, APPARATUS REQUIRED: Sl. o. ). /. 1. /. 1. C$MP$ E T 1 %/P A D *ATE $0 *ATE $T *ATE %C T0A% E0 6%T PATC8 C$0DS SPEC%&%CAT%$ %C +,)) %C +,1/ %C +,-, 5 5 'T(. / ) ) ) 1/

THEORY: MULTIPLEXER: MultipleAer means transmitting a large number of information units over a smaller number of channels or lines. A digital multipleAer is a combinational circuit that selects binary information from one of many input lines and directs it to a single output line. The selection of a particular input line is controlled by a set of selection lines. selected. DEMULTIPLEXER: The function of DemultipleAer is in contrast to multipleAer function. %t ta!es information from one line and distributes it to a given number of

Prepared by M.Marimuthu Assistant Professor/ ECE

ormally there are / n input line

and n selection lines "hose bit combination determine "hich input is

Sri Subramanya college of Engineering and Technology Department of ECE

output lines. &or this reason< the demultipleAer is also !no"n as a data distributor. Decoder can also be used as demultipleAer. %n the ); , demultipleAer circuit< the data input line goes to all of the A D gates. The data select lines enable only one gate at a time and the data on the data input line "ill pass through the selected gate to the associated data output line. BLOCK DIAGRAM FOR <:1 MULTIPLEXER:

FUNCTION TABLE:

S1 0 0 1 1

S0 0 1 0 1

INPUTS Y D0 G D0 S1% S0% D1 G D1 S1% S0 D2 G D2 S1 S0% D3 G D3 S1 S0

Y $ D0 S1% S0% & D1 S1% S0 & D2 S1 S0% & D3 S1 S0 CIRCUIT DIAGRAM FOR MULTIPLEXER:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

TRUTH TABLE: S1 0 0 1 1 S0 0 1 0 1 Y $ OUTPUT D0 D1 D2 D3

BLOCK DIAGRAM FOR 1:< DEMULTIPLEXER:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

FUNCTION TABLE:

S1 0 0 1 1

S0 0 1 0 1

INPUT X G D0 $ X S1% S0% X G D1 $ X S1% S0 X G D2 $ X S1 S0% X G D3 $ X S1 S0

Y $ X S1% S0% & X S1% S0 & X S1 S0% & X S1 S0

LOGIC DIAGRAM FOR DEMULTIPLEXER:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

TRUTH TABLE: S1 0 INPUT S0 0 I=P 0 D0 0 OUTPUT D1 D2 0 0 D3 0

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

0 0 0 1 1 1 1

0 1 1 0 0 1 1

1 0 1 0 1 0 1

1 0 0 0 0 0 0

0 0 1 0 0 0 0

0 0 0 0 1 0 0

0 0 0 0 0 0 1

PIN DIAGRAM FOR IC 7<1A0:

PIN DIAGRAM FOR IC 7<1A<:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

PROCEDURE: 9i: Connections are given as per circuit diagram. 9ii: 9iii: RESULT: The truth tables of multipleAer and de5multipleAer "ere verified. #ogical inputs are given as per circuit diagram. $bserve the output and verify the truth table.

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

EX NO: > DATE: DESIGN AND IMPLEMENTATION OF ENCODER AND DECODER

AIM: To design and implement encoder and decoder using logic gates and study of %C +,,2 and %C +,),+ APPARATUS REQUIRED: Sl. o. ). /. 1. /. 1. THEORY: ENCODER: An encoder is a digital circuit that perform inverse operation of a decoder. An encoder has /n input lines and n output lines. %n encoder the output lines generates the binary code corresponding to the input value. %n octal to binary encoder it has eight inputs< one for each octal digit and three output that generate the corresponding binary code. %n encoder it is assumed that only one input has a value of one at any given time other"ise the circuit is meaningless. %t has an ambiguila that "hen all inputs are Kero the outputs are Kero. The Kero outputs can also be generated "hen D- E ). DECODER:

Prepared by M.Marimuthu Assistant Professor/ ECE

C$MP$ E T 1 %/P A D *ATE $0 *ATE $T *ATE %C T0A% E0 6%T PATC8 C$0DS

SPEC%&%CAT%$ %C +,)%C +,1/ %C +,-, 5 5

'T(. / 1 ) ) /+

Sri Subramanya college of Engineering and Technology Department of ECE

A decoder is a multiple input multiple output logic circuit "hich converts coded input into coded output "here input and output codes are different. The input code generally has fe"er bits than the output code. Each input code "ord produces a different output code "ord i.e there is one to one mapping can be eApressed in truth table. %n the bloc! diagram of decoder circuit the encoded information is present as n input producing / n possible outputs. /n output values are from - through out /n F ).

PIN DIAGRAM FOR IC 7<<A: BCD TO DECIMAL DECODER:

PIN DIAGRAM FOR IC 7<1<7:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

LOGIC DIAGRAM FOR ENCODER:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

TRUTH TABLE: INPUT Y1 Y2 Y3 Y< YA YD 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 LOGIC DIAGRAM FOR DECODER: Y7 0 0 0 0 0 0 1 A 0 0 0 1 1 1 1 OUTPUT B 0 1 1 0 0 1 1 C 1 0 1 0 1 0 1

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

TRUTH TABLE: INPUT A 0 0 0 1 1 OUTPUT D1 D2 1 1 1 1 0 1 1 0 1 1

E 1 0 0 0 0

B 0 0 1 0 1

D0 1 0 1 1 1

D3 1 1 1 1 0

PROCEDURE:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

9i: 9ii: 9iii:

Connections are given as per circuit diagram. #ogical inputs are given as per circuit diagram. $bserve the output and verify the truth table.

RESULT:

The truth tables of encoder and decoder "ere verified

EX NO: H DATE:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

CONSTRUCTION AND 7ERIFICATION OF < BIT RIPPLE COUNTER AND MOD 10=MOD 12 RIPPLE COUNTER AIM: To design and verify , bit ripple counter mod )-/ mod )/ ripple counter. APPARATUS REQUIRED: Sl. o. ). /. 1. ,. C$MP$ E T L6 &#%P &#$P A D *ATE %C T0A% E0 6%T PATC8 C$0DS SPEC%&%CAT%$ %C +,+3 %C +,-5 5 'T(. / ) ) 1-

THEORY: A counter is a register capable of counting number of cloc! pulse arriving at its cloc! input. Counter represents the number of cloc! pulses arrived. A specified seCuence of states appears as counter output. This is the main difference bet"een a register and a counter. There are t"o types of counter< synchronous and asynchronous. %n synchronous common cloc! is given to all flip flop and in asynchronous first flip flop is cloc!ed by eAternal pulse and then each successive flip flop is cloc!ed by ' or ' output of previous stage. A soon the cloc! of second stage is triggered by output of first stage. @ecause of inherent propagation delay time all flip flops are not activated at same time "hich results in asynchronous operation. PIN DIAGRAM FOR IC 7<7D:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

LOGIC DIAGRAM FOR < BIT RIPPLE COUNTER:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

TRUTH TABLE: CLK 0 1 2 3 < A D 7 > H 10

Prepared by M.Marimuthu Assistant Professor/ ECE

QA 0 1 0 1 0 1 0 1 0 1 0

QB 0 0 1 1 0 0 1 1 0 0 1

QC 0 0 0 0 1 1 1 1 0 0 0

QD 0 0 0 0 0 0 0 0 1 1 1

Sri Subramanya college of Engineering and Technology Department of ECE

11 12 13 1< 1A

1 0 1 0 1

1 0 0 1 1

0 1 1 1 1

1 1 1 1 1

LOGIC DIAGRAM FOR MOD - 10 RIPPLE COUNTER:

TRUTH TABLE: CLK 0 1 2 QA 0 1 0 QB 0 0 1 QC 0 0 0 QD 0 0 0

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

3 < A D 7 > H 10

1 0 1 0 1 0 1 0

1 0 0 1 1 0 0 0

0 1 1 1 1 0 0 0

0 0 0 0 0 1 1 0

LOGIC DIAGRAM FOR MOD - 12 RIPPLE COUNTER:

TRUTH TABLE: CLK 0 1 2 3 < A D 7 > H 10 QA 0 1 0 1 0 1 0 1 0 1 0 QB 0 0 1 1 0 0 1 1 0 0 1 QC 0 0 0 0 1 1 1 1 0 0 0 QD 0 0 0 0 0 0 0 0 1 1 1

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

11 12

1 0

1 0

0 0

1 0

PROCEDURE: 9i: 9ii: 9iii: Connections are given as per circuit diagram. #ogical inputs are given as per circuit diagram. $bserve the output and verify the truth table.

RESULT:

The "or!ing of , bit ripple counter< mod )- and mod )/ counters "ere verified by their truth tables.

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

EX NO: 10 DATE: DESIGN AND IMPLEMENTATION OF 3 BIT SYNCHRONOUS UP=DO'N COUNTER AIM: To design and implement 1 bit synchronous up/do"n counter. APPARATUS REQUIRED: Sl. o. ). /. 1. ,. 2. 3. +. C$MP$ E T L6 &#%P &#$P 1 %/P A D *ATE $0 *ATE 4$0 *ATE $T *ATE %C T0A% E0 6%T PATC8 C$0DS SPEC%&%CAT%$ %C +,+3 %C +,)) %C +,1/ %C +,.3 %C +,-, 5 5 'T(. / ) ) ) ) ) 12

THEORY: A counter is a register capable of counting number of cloc! pulse arriving at its cloc! input. Counter represents the number of cloc! pulses arrived. An up/do"n counter is one that is capable of progressing in increasing order or decreasing order through a certain seCuence. An up/do"n counter is also called bidirectional counter. Gsually up/do"n operation of the counter is controlled by up/do"n signal. Dhen this signal is high counter

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

goes through up seCuence and "hen up/do"n signal is lo" counter follo"s reverse seCuence. K MAP

STATE DIAGRAM:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

CHARACTERISTICS TABLE: Q 0 0 1 1 Q.&1 0 1 0 1 I 0 1 X X K X X 1 0

LOGIC DIAGRAM:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

TRUTH TABLE: I* /. P#)2)*. S.a.) U =D",* QA QB QC 0 0 0 0 0 1 1 1 0 1 1 0 0 1 0 1 0 1 0 0 0 0 1 1 0 0 1 0 0 0 0 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1

Prepared by M.Marimuthu Assistant Professor/ ECE

N):. S.a.) QA&1 Q B&1 QC&1 1 1 1 1 1 0 1 0 1 1 0 0 0 1 1 0 1 0 0 0 1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0

A IA 1 X X X X 0 0 0 0 0 0 1 X X KA X 0 0 0 1 X X X X X X X 0 0 IB 1 X X 0 1 X X 0 0 1 X X 0 1

B KB X 0 1 X X 0 1 X X X 0 1 X X IC 1 X 1 X 1 X 1 X 1 X 1 X 1 X

C KC X 1 X 1 X 1 X 1 X 1 X 1 X 1

Sri Subramanya college of Engineering and Technology Department of ECE

1 1

1 1

1 1

0 1

1 0

1 0

1 0

X X

0 1

X X

0 1

1 X

X 1

PROCEDURE: 9i: Connections are given as per circuit diagram. 9ii: 9iii: RESULT:

The truth table of 1 bit synchronous up/do"n counter "as verified.

#ogical inputs are given as per circuit diagram. $bserve the output and verify the truth table.

EX NO: 10 DATE : DESIGN AND IMPLEMENTATION OF SHIFT REGISTER AIM: To design and implement 9i: Serial in serial out 9ii: Serial in parallel out 9iii: Parallel in serial out 9iv: Parallel in parallel out APPARATUS REQUIRED: Sl. o. ). /. 1. ,. C$MP$ E T D &#%P &#$P $0 *ATE %C T0A% E0 6%T PATC8 C$0DS SPEC%&%CAT%$ %C +,+, %C +,1/ 5 5 'T(. / ) ) 12

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

THEORY: A register is capable of shifting its binary information in one or both directions is !no"n as shift register. The logical configuration of shift register consist of a D5&lip flop cascaded "ith output of one flip flop connected to input of neAt flip flop. All flip flops receive common cloc! pulses "hich causes the shift in the output of the flip flop. The simplest possible shift register is one that uses only flip flop. The output of a given flip flop is connected to the input of neAt flip flop of the register. Each cloc! pulse shifts the content of register one bit position to right. PIN DIAGRAM:

LOGIC DIAGRAM: SERIAL IN SERIAL OUT:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

TRUTH TABLE:

S)#(a1 (* CLK 1 2 3 < A D 7 1 0 0 1 X X X 0 0 0 1 0 0 1 S)#(a1 "/.

LOGIC DIAGRAM: SERIAL IN PARALLEL OUT:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

TRUTH TABLE: CLK DATA 1 1 2 0 3 0 < 1 LOGIC DIAGRAM: QA 1 0 0 1 OUTPUT QB QC 0 1 0 0 0 0 1 0 QD 0 0 1 1

PARALLEL IN SERIAL OUT:

TRUTH TABLE: CLK 0 1 2 3 Q3 1 0 0 0 Q2 0 0 0 0 Q1 0 0 0 0 Q0 1 0 0 0 O=P 1 0 0 1

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

LOGIC DIAGRAM: PARALLEL IN PARALLEL OUT:

TRUTH TABLE: CLK 1 2 DA 1 1 DATA INPUT DB DC 0 0 0 1 DD 1 0 QA 1 1 OUTPUT QB QC 0 0 0 1 QD 1 0

PROCEDURE: 9i: 9ii: 9iii: Connections are given as per circuit diagram. #ogical inputs are given as per circuit diagram. $bserve the output and verify the truth table.

RESULT:

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

The outputs of shift register types "ere verified "ith their truth tables.

EX NO: 11 DATE: DESIGN AND IMPLEMENTATION OF ADDERSJ SUBTRACTORSJ < BIT RIPPLE COUNTERJ SHIFT REGISTERS USING 7ERILOG HDL LANGUAGE AIM: To design and implement the follo"ing using verilog 8D# 8alf adder and subtractor &ull adder and subtractor , bit ripple carry counter Serial in serial out Serial in parallel out Parallel in serial out Parallel in parallel out APPARATUS REQUIRED: Sl. o. ). C$MP$ E T PC "ith 4ilinA SPEC%&%CAT%$ 5 'T(. )

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

soft"are

P0$*0AM &$0 8A#& ADDE0 GS% * ME0%#$*;

module halfNadder9a< b< sum< carry:? input a? input b? output sum? output carry? Aor g)9sum<a<b:? and g/9carry<a<b:? endmodule

$GTPGT;

P0$*0AM &$0 &G## ADDE0 GS% * ME0%#$*;

module fullNadder9a< b<cin< sum< carry:? input a? input b? input cin? output sum? output carry? "ire e<f<g? Aor g)9e<a<b:? Aor g/9sum<e<cin:? and g19f<a<b:? and g,9g<e<cin:? or g29carry<f<g:? endmodule

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE $GTPGT;

P0$*0AM &$0 8A#& SG@T0ACT$0 GS% * ME0%#$*; module halfNsub9a<b<diff<bout:? input a<b? output diff<bout? "ire c? Aor g)9diff<a<b:? not g/9c<a:? and g19bout c<b:? endmodule $GTPGT;

P0$*0AM &$0 &G## SG@T0ACT$0 GS% * ME0%#$*; module fulNsub9a<b<cin<diff<bout:? input a<b<cin? output diff<bout? "ire e<f<g<h<i?

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

Aor g)9e<a<b:? Aor g/9diff<e<cin:? not g19f<a:? not g,9g<e:? and g29h<f<b:? and g39i<g<cin:? or g+9bout<i<h:? endmodule

$GTPGT;

P0$*0AM &$0 MG#T%P#E4E0 GS% * ME0%#$*; module muAN,9s<d<y:? input O);-Ps? input O1;-Pd? output y? "ire a<b<c<e<f<g? not g)9a<sO)P:? not g/9b<sO-P:? and g19c<a<b<dO-P:? and g,9e<a<sO-P<dO)P:? and g29f<sO)P<b<dO/P:? and g39g<sO)P<sO-P<dO1P:?

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

or g+9y<c<e<f<g:? endmodule

$GTPGT;

P0$*0AM &$0 DEMG#T%P#E4E0 GS% * ME0%#$*; module dmuAN,9s<d<y:? input O);-Ps? input d? output O1;-Py? "ire a<b? not g)9a<sO)P:? not g/9b<sO-P:? and g19yO-P<a<b<d:? and g,9yO)P<a<sO-P<d:? and g29yO/P<sO)P<b<d:? and g39yO1P<sO)P<sO-P<d:? endmodule $GTPGT;

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

P0$*0AM &$0 , @%T 0%PP#E C$G TE0 GS% * ME0%#$*; module co9C<cl!<clr:? input cl!<clr? outputO1;-PC? regO1;-PC? al"aysQ9posedge clr or negedge cl!: begin if9clr: CIE,Rb----? else CIECB)? end endmodule. 9$0:

, @%T @% A0( C$G TE0;

module Counter_4Bit ( clk ,reset ,dout ); output [3:0] dout ; reg [3:0] dout ; input clk ; wire clk ; input reset ; wire reset ; initial dout 0; alwa!s " (posedge (clk)) #egin i$ (reset) dout % 0; else dout % dout & '; end endmodule

$GTPGT;

PROGRAM FOR SISO SHIFT REGISTER module sdsad9din< cl!< reset< dout:? Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE input din? "ire din? input cl!?"ire cl!? input reset? "ire reset? output dout? reg dout? reg O,;-Ps? al"ays Q 9posedge 9cl!:: begin if 9reset: dout IE -? else begin sO-P IE din ? sO)P IE sO-P ? sO/P IE sO)P ? dout IE sO/P? end end endmodule

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

P0$*0AM &$0 S%P$ S8%&T 0E*%STE0

module hghg9din< cl!< reset< dout:? input din? "ire din? input cl!? "ire cl!? input reset? "ire reset? output O1;-Pdout? "ire O1;-Pdout? reg O1;-Ps? al"ays Q 9posedge 9cl!:: begin if 9reset: s IE -? else begin sO1P IE din? sO/P IE sO1P? sO)P IE sO/P? sO-P IE sO)P? end end assign dout E s? endmodule

Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE

P0$*0AM &$0 P%S$ S8%&T 0E*%STE0

module parallelNinNserialNout 9 din <cl! <reset <load <dout :? output dout ? reg dout ? input O1;-P din ? "ire O1;-P din ? input cl! ? "ire cl! ? input reset ? "ire reset ? input load ? "ire load ? reg O1;-Ptemp? al"ays Q 9posedge 9cl!:: begin if 9reset: temp IE )? else if 9load: temp IE din? else begin dout IE tempO1P? temp IE StempO/;-P<)Rb-T? Prepared by M.Marimuthu Assistant Professor/ ECE

Sri Subramanya college of Engineering and Technology Department of ECE end end endmodule

P0$*0AM &$0 P%P$ S8%&T 0E*%STE0

module P%P$ 9 din <cl! <reset <dout :? output O1;-P dout ? reg O1;-P dout ? input O1;-P din ? "ire O1;-P din ? input cl! ? "ire cl! ? input reset ? "ire reset ? al"ays Q 9posedge 9cl!:: begin if 9reset: dout IE -? else dout IE din? end endmodule

0ESG#T; Thus the outputs of all the programs "ritten above "ere simulated and verified

Prepared by M.Marimuthu Assistant Professor/ ECE

Potrebbero piacerti anche

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Cobit 2019 Design Toolkit With Description - Group x.20201130165617871Documento46 pagineCobit 2019 Design Toolkit With Description - Group x.20201130165617871Izha Mahendra75% (4)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- B777 ChecklistDocumento2 pagineB777 ChecklistMarkus Schütz100% (1)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- (EngineeringEBookspdf) Failure Investigation of Bolier PDFDocumento448 pagine(EngineeringEBookspdf) Failure Investigation of Bolier PDFcarlos83% (6)

- How To Calculate Floor Load CapacityDocumento3 pagineHow To Calculate Floor Load CapacityNatarajan KrishnanNessuna valutazione finora

- Binthen Motorized Curtain Price List Rev1.0 Jan 2022Documento4 pagineBinthen Motorized Curtain Price List Rev1.0 Jan 2022Emil EremiaNessuna valutazione finora

- Pressure-Controlled Pumps CascadeDocumento2 paginePressure-Controlled Pumps Cascadecc_bauNessuna valutazione finora

- Unit - I Signals and SystemsDocumento15 pagineUnit - I Signals and SystemsmuthubeNessuna valutazione finora

- Vetri Nichayam by Suki Sivam TamilDocumento145 pagineVetri Nichayam by Suki Sivam Tamilparamsothy2000Nessuna valutazione finora

- Submitted in Partial Fulfillment For The Award of The DegreeDocumento3 pagineSubmitted in Partial Fulfillment For The Award of The DegreemuthubeNessuna valutazione finora

- Unit Ii Two Marks QuestionsDocumento3 pagineUnit Ii Two Marks QuestionsmuthubeNessuna valutazione finora

- Communication Theory Question Bank Unit 4Documento2 pagineCommunication Theory Question Bank Unit 4muthubeNessuna valutazione finora

- IT2032 - Software Testing: Staff - in Charge Hod / Cse&ItDocumento1 paginaIT2032 - Software Testing: Staff - in Charge Hod / Cse&ItmuthubeNessuna valutazione finora

- CountersDocumento13 pagineCountersmuthubeNessuna valutazione finora

- Digital Video ProcessingDocumento261 pagineDigital Video ProcessingmuthubeNessuna valutazione finora

- Rfid and GSM Based Intelligent Mail BoxDocumento23 pagineRfid and GSM Based Intelligent Mail BoxmuthubeNessuna valutazione finora

- Unit Ii Construction Practice - 10Documento94 pagineUnit Ii Construction Practice - 10Arun KumarNessuna valutazione finora

- Mouse 200Documento2 pagineMouse 200Amjad AliNessuna valutazione finora

- Grade 7 and 8 November NewsletterDocumento1 paginaGrade 7 and 8 November Newsletterapi-296332562Nessuna valutazione finora

- Android VersionsDocumento7 pagineAndroid VersionsEdna Mae Salas GarciaNessuna valutazione finora

- Photometric Design White PaperDocumento5 paginePhotometric Design White PaperScott VokeyNessuna valutazione finora

- Teacher Evaluation in A Blended Learning EnviornmentDocumento11 pagineTeacher Evaluation in A Blended Learning Enviornmentapi-287748301Nessuna valutazione finora

- H S ™ PHC P H C: Ypertherm Ensor Lasma Eight OntrolDocumento58 pagineH S ™ PHC P H C: Ypertherm Ensor Lasma Eight OntrolCRISTIANNessuna valutazione finora

- Seguridad en Reactores de Investigación PDFDocumento152 pagineSeguridad en Reactores de Investigación PDFJorge PáezNessuna valutazione finora

- ASSA ABLOY - Digital Cam LocksDocumento12 pagineASSA ABLOY - Digital Cam LocksSales Project 2 VCPNessuna valutazione finora

- Alimentacion Baterias TiposDocumento11 pagineAlimentacion Baterias TiposjulioclavijoNessuna valutazione finora

- Move Order APIDocumento11 pagineMove Order APIsubbaraocrm100% (3)

- Compressor Service ProcedureDocumento22 pagineCompressor Service ProcedureFriget Rusianto100% (2)

- Microsoft ISA Server 2006 - Certificate Troubleshooting - Part IIDocumento7 pagineMicrosoft ISA Server 2006 - Certificate Troubleshooting - Part IIKhodor AkoumNessuna valutazione finora

- The Role of Social Media and Its Implication On Economic Growth On Society in IndiaDocumento3 pagineThe Role of Social Media and Its Implication On Economic Growth On Society in IndiaSara EmamiNessuna valutazione finora

- Power Network Telecommunication: Powerlink - Technical DataDocumento10 paginePower Network Telecommunication: Powerlink - Technical Datawas00266Nessuna valutazione finora

- JeeleDocumento9 pagineJeeleAnonymous SZDGk7SvGNessuna valutazione finora

- Electricalprep Com Transformers More 5Documento16 pagineElectricalprep Com Transformers More 5gokulchandruNessuna valutazione finora

- Camsco Breaker PDFDocumento12 pagineCamsco Breaker PDFMichael MaiquemaNessuna valutazione finora

- A Neural Network Model For Electric PDFDocumento6 pagineA Neural Network Model For Electric PDFR Adhitya ArNessuna valutazione finora

- Quotation For Blue Star Printek From Boway2010 (1) .09.04Documento1 paginaQuotation For Blue Star Printek From Boway2010 (1) .09.04Arvin Kumar GargNessuna valutazione finora

- Hard Disk Formatting and CapacityDocumento3 pagineHard Disk Formatting and CapacityVinayak Odanavar0% (1)

- Assessment of Reinforcement CorrosionDocumento5 pagineAssessment of Reinforcement CorrosionClethHirenNessuna valutazione finora

- 8 Candidate Quiz Buzzer Using 8051Documento33 pagine8 Candidate Quiz Buzzer Using 8051prasadzeal0% (1)

- Amplificador LA42102Documento8 pagineAmplificador LA42102SilvestrePalaciosLópezNessuna valutazione finora