Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Modified Harvard Architecture - Wikipedia, The Free Encyclopedia PDF

Caricato da

beta2009Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Modified Harvard Architecture - Wikipedia, The Free Encyclopedia PDF

Caricato da

beta2009Copyright:

Formati disponibili

10/28/13

Modified Harvard architecture - Wikipedia, the free encyclopedia

Modified Harvard architecture

From Wikipedia, the free encyclopedia

The Modified Harvard architecture is a variation of the Harvard computer architecture that allows the contents of the instruction memory to be accessed as if it were data. Most modern computers that are documented as Harvard architecture are, in fact, Modified Harvard architecture.

Contents

1 Harvard architecture 2 Von Neumann architecture 3 Modified Harvard architecture 3.1 Split cache architecture 3.2 Access instruction memory as data 3.3 Read instructions from data memory 4 Comparisons 5 Modern uses of the Modified Harvard architecture 6 See also 7 Notes and references

Harvard architecture

Main article: Harvard architecture The original Harvard architecture computer, the Harvard Mark I, employed entirely separate memory systems to store instructions and data. The CPU fetched the next instruction and loaded or stored data simultaneously and independently. This is in contrast to a Von Neumann architecture computer, in which both instructions and data are stored in the same memory system and (without the complexity of a CPU cache) must be accessed in turn. The physical separation of instruction and data memory is sometimes held to be the distinguishing feature of modern Harvard architecture computers. With microcontrollers (entire computer systems integrated onto single chips), the use of different memory technologies for instructions (e.g. flash memory) and data (typically read/write memory) in von Neumann machines is becoming popular. The true distinction of a Harvard machine is that instruction and data memory occupy different address spaces. In other words, a memory address does not uniquely identify a storage location (as it does in a Von Neumann machine); you also need to know the memory space (instruction or data) to which the address belongs.

Von Neumann architecture

Main article: Von Neumann architecture A computer with a Von Neumann architecture has the advantage over pure Harvard machines in that code can also be accessed and treated the same as data, and vice versa. This allows, for example, data to be read from disk storage and executed as code, or self-optimizing software systems using technologies such as just-in-time compilation to write machine code into their own memory and then later execute it. Another example is self-

en.wikipedia.org/wiki/Modified_Harvard_architecture

1/4

10/28/13

Modified Harvard architecture - Wikipedia, the free encyclopedia

modifying code, which allows a program to modify itself. A disadvantage of these methods are issues with executable space protection, which increase the risks from malware and software defects. In addition, in these systems it is notoriously difficult to document code flow, and also can make debugging much more difficult.

Modified Harvard architecture

Accordingly, some pure Harvard machines are specialty products. Most modern computers instead implement a modified Harvard architecture. Those modifications are various ways to loosen the strict separation between code and data, while still supporting the higher performance concurrent data and instruction access of the Harvard architecture.

Split cache architecture

The most common modification builds a memory hierarchy with a CPU cache separating instructions and data. This unifies all except small portions of the data and instruction address spaces, providing the von Neumann model. Most programmers never need to be aware of the fact that the processor core implements a (modified) Harvard architecture, although they benefit from its speed advantages. Only programmers who write instructions into data memory need to be aware of issues such as cache coherency and executable space protection.

Access instruction memory as data

Another change preserves the "separate address space" nature of a Harvard machine, but provides special machine operations to access the contents of the instruction memory as data. Because data is not directly executable as instructions, such machines are not always viewed as "modified" Harvard architecture: Read access: initial data values can be copied from the instruction memory into the data memory when the program starts. Or, if the data is not to be modified (it might be a constant value, such as pi, or a text string), it can be accessed by the running program directly from instruction memory without taking up space in data memory (which is often at a premium). Write access: a capability for reprogramming is generally required; few computers are purely ROM based. For example, a microcontroller usually has operations to write to the flash memory used to hold its instructions.[citation needed ] This capability may be used for purposes including software updates and EEPROM replacement.

Read instructions from data memory

A few Harvard architecture processors, such as the MAXQ, can execute instructions fetched from any memory segment -- unlike the original Harvard processor, which can only execute instructions fetched from the program memory segment. Such processors, like other Harvard architecture processors -- and unlike pure Princeton architecture -- can read an instruction and read a data value simultaneously, if they're in separate memory segments, since the processor has (at least) two separate memory segments with independent data buses. The most obvious programmer-visible difference between this kind of modified Harvard architecture and a pure Princeton architecture is that -- when executing an instruction from one memory segment -- the same memory segment cannot be simultaneously accessed as data.[1][2]

Comparisons

Three characteristics may be used to distinguish Modified Harvard machines from Harvard and Von Neumann machines:

en.wikipedia.org/wiki/Modified_Harvard_architecture 2/4

10/28/13

Modified Harvard architecture - Wikipedia, the free encyclopedia

Instruction and data memories occupy different address spaces. For pure Harvard machines, there is an address 'zero' in instruction space that refers to an instruction storage location and a separate address 'zero' in data space that refers to a distinct data storage location. By contrast, Von Neumann and "split cache" modified Harvard machines store both instructions and data in a single address space, so address 'zero' refers to only one thing and whether the binary pattern in that location is interpreted as an instruction or data is defined by how the program is written. This characteristic unambiguously identifies a pure Harvard machine. By a strict interpretation of this distinction, for example, the Microchip PIC17 and PIC18 architectures, as well as the Atmel 8-bit AVR architecture, would be regarded as pure Harvard architecture machines because they do, in fact, maintain a distinct separation between code and data spaces, and address 'zero' of each does, in fact, refer to a physically different piece of memory. However, the distinction is made ambiguous by the colloquial use of the term "modified Harvard architecture" to refer to such machines' inclusion of special instructions to read and/or write the contents of code space as though it were data.[3] Instruction and data memories have separate hardware pathways to the central processing unit (CPU). This is the point of pure or modified Harvard machines, and why they co-exist with the more flexible and general von Neumann architecture: separate memory pathways to the CPU allow instructions to be fetched and data to be accessed at the same time, improving throughput. The pure Harvard machines have separate pathways with separate address spaces. Modified Harvard machines have such separate access paths for CPU caches or other tightly coupled memories, but a unified address space covers the rest of the memory hierarchy. A Von Neumann processor has only that unified address space. From a programmer's point-of-view, a modified Harvard processor in which instruction and data memories share an address space is usually treated as a Von Neumann machine until cache coherency becomes an issue, as with self-modifying code and program loading. This can be confusing, but such issues are usually visible only to systems programmers and integrators. Instruction and data memories may be accessed in different ways. The original Harvard machine, the Mark I, stored instructions on a punched paper tape and data in electro-mechanical counters. This, however, was entirely due to the limitations of technology available at the time. Today a Harvard machine such as the PIC microcontroller might use 12-bit wide flash memory for instructions, and 8-bit wide SRAM for data. In contrast, a Von Neumann microcontroller such as an ARM7TDMI, or a modified Harvard ARM9 core, necessarily provides uniform access to flash and SRAM (as 8 bit bytes, in those cases).

Modern uses of the Modified Harvard architecture

Outside of applications where a cacheless DSP or microcontroller is required, most modern processors have a CPU cache which partitions instruction and data. There are also processors which are Harvard machines by the most rigorous definition (that program and data memory occupy different address spaces), and are only modified in the weak sense that there are operations to read and/or write program memory as data. For example, LPM (Load Program Memory) and SPM (Store Program Memory) instructions in the Atmel AVR implement such a modification. Similar solutions are found in other microcontrollers such as the PIC and Z8Encore!, many families of digital signal processors such as the TI C55x cores, and more. Because instruction execution is still restricted to the program address space, these processors are very unlike von Neumann machines.

en.wikipedia.org/wiki/Modified_Harvard_architecture

3/4

10/28/13

Modified Harvard architecture - Wikipedia, the free encyclopedia

Having separate address spaces creates certain difficulties in programming with high-level languages such as C, which do not directly support the notion that tables of read-only data might be in a different address space from normal writable data (and thus need to be read using different instructions).[3]

See also

Von Neumann architecture NX bit

Notes and references

1. ^ "MAXQ Family User's Guide" (http://www.maxim-ic.com/MAXQUG). Section "1.2 Harvard Memory Architecture" and Section "2.5 Pseudo-Von Neumann Memory Access". 2. ^ Konark Goel et. al. "About MAXQ GCC port" (http://gcc.gnu.org/ml/gcc-patches/2004-12/txt00149.txt). 3. ^ a b The maintainers of the standard C library for the GCC port to the Atmel AVR microcontroller, which has separate address spaces for code and data, state in Data in Program Space (http://www.nongnu.org/avrlibc/user-manual/pgmspace.html) that separate address spaces imply a Harvard architecture. They go on to explain that the C language only has one pointer address space, and thus was not designed for Harvard architecture machines. They then describe the non-standard extensions adopted by GCC for the AVR and the AVR C library to allow access to data stored in instruction (program) memory. They even explain why the const keyword cannot be pressed into service to distinguish data objects to be placed in instruction memory.

Retrieved from "http://en.wikipedia.org/w/index.php?title=Modified_Harvard_architecture&oldid=575103821" Categories: Computer architecture Classes of computers This page was last modified on 30 September 2013 at 06:33. Text is available under the Creative Commons Attribution-ShareAlike License; additional terms may apply. By using this site, you agree to the Terms of Use and Privacy Policy. Wikipedia is a registered trademark of the Wikimedia Foundation, Inc., a non-profit organization.

en.wikipedia.org/wiki/Modified_Harvard_architecture

4/4

Potrebbero piacerti anche

- SAS Programming Guidelines Interview Questions You'll Most Likely Be AskedDa EverandSAS Programming Guidelines Interview Questions You'll Most Likely Be AskedNessuna valutazione finora

- Harvard Architecture PDFDocumento3 pagineHarvard Architecture PDFsathkar220% (1)

- Harvard Architecture: Memory DetailsDocumento11 pagineHarvard Architecture: Memory DetailsWan ShahmisufiNessuna valutazione finora

- The Von NeumannDocumento5 pagineThe Von NeumannPluvio PhileNessuna valutazione finora

- 65608543Documento4 pagine65608543Van SinNessuna valutazione finora

- Harvard Architecture Vs Von Neumann ArchitectureDocumento2 pagineHarvard Architecture Vs Von Neumann Architecturena_hariprsadNessuna valutazione finora

- Harvard ArchitectureDocumento3 pagineHarvard Architecturebalu4allNessuna valutazione finora

- Computer Architecture AssignDocumento9 pagineComputer Architecture AssignZawar HussainNessuna valutazione finora

- Unit 1Documento9 pagineUnit 1Harikrishnan NairNessuna valutazione finora

- Harvard ArchitectureDocumento4 pagineHarvard ArchitectureminchenggoNessuna valutazione finora

- The Anatomy of A ComputerDocumento2 pagineThe Anatomy of A ComputerIlieTaranuNessuna valutazione finora

- Activity 2 CPE07Documento3 pagineActivity 2 CPE07Ralstine Jane IgneNessuna valutazione finora

- What Is The Difference Between A Von NeumannDocumento2 pagineWhat Is The Difference Between A Von NeumannYogendra UikeyNessuna valutazione finora

- Harvard ArchiDocumento10 pagineHarvard ArchiWin RevansNessuna valutazione finora

- What Is The Difference Between A Von Neumann Architecture and A Harvard Architecture? PDFDocumento2 pagineWhat Is The Difference Between A Von Neumann Architecture and A Harvard Architecture? PDFAsher N GonzalezNessuna valutazione finora

- What Is The Difference Between A Von Neumann Architecture and A Harvard Architecture?Documento2 pagineWhat Is The Difference Between A Von Neumann Architecture and A Harvard Architecture?Asher N GonzalezNessuna valutazione finora

- Computer ArchitectureDocumento2 pagineComputer ArchitectureadonisNessuna valutazione finora

- Micro Controller ArchitectureDocumento4 pagineMicro Controller ArchitectureMichaelDyksonNessuna valutazione finora

- Von Neumann HavardDocumento11 pagineVon Neumann HavardMohd Zahiruddin ZainonNessuna valutazione finora

- Coa Activity-2Documento1 paginaCoa Activity-2Althea IgnacioNessuna valutazione finora

- Difference Between Harvard and Princeton or Von Neumann ArchitectureDocumento3 pagineDifference Between Harvard and Princeton or Von Neumann ArchitectureTarek Bin Zahid67% (3)

- Von Neumann Vs Harvard ArchitectureDocumento8 pagineVon Neumann Vs Harvard ArchitectureHarry DabasNessuna valutazione finora

- Different Classification of Computer ArchitectureDocumento5 pagineDifferent Classification of Computer ArchitecturePRINTDESK by Dan0% (1)

- v3 A-Level Presentation - 01 Computer Architecture Auto-Saved Auto-SavedDocumento63 paginev3 A-Level Presentation - 01 Computer Architecture Auto-Saved Auto-SavedYi-Sin Lin - OXF.StudentNessuna valutazione finora

- Von Neumann and Harvard ArchitectureDocumento13 pagineVon Neumann and Harvard ArchitectureYuvraj KatwalNessuna valutazione finora

- 03 - Harvard Architecture Comparison PDFDocumento4 pagine03 - Harvard Architecture Comparison PDFKaemryn SaeNessuna valutazione finora

- Von Neuman ArchitectureDocumento4 pagineVon Neuman ArchitectureAmeenNessuna valutazione finora

- Von-Neumann Architecture Vs Harvard Architecture: February 2019Documento6 pagineVon-Neumann Architecture Vs Harvard Architecture: February 2019MnshNessuna valutazione finora

- Processors Used in SOCsDocumento25 pagineProcessors Used in SOCsA B ShindeNessuna valutazione finora

- Lect 3Documento15 pagineLect 3Blaser TacticalNessuna valutazione finora

- Brief Intro Abt Von-Neumann and Harvard ArchitectureDocumento6 pagineBrief Intro Abt Von-Neumann and Harvard ArchitectureAnonymous U8awvgZ3pDNessuna valutazione finora

- VonneumanDocumento8 pagineVonneumanJayson TibayanNessuna valutazione finora

- Presentation 2 Csc337Documento19 paginePresentation 2 Csc337Ilori KoredeNessuna valutazione finora

- Machine CodeDocumento1 paginaMachine CodeVishal BhagatNessuna valutazione finora

- Computer Architecture 2Documento6 pagineComputer Architecture 2Clovisprom 2003Nessuna valutazione finora

- Architecture of DSP ProcessorsDocumento13 pagineArchitecture of DSP ProcessorsSugumar Sar DuraiNessuna valutazione finora

- Computer Architecture 2Documento6 pagineComputer Architecture 2Kiapuch Airuch CuophiNessuna valutazione finora

- Computer ArchitectureDocumento12 pagineComputer Architecturejaibirthakran47Nessuna valutazione finora

- Harvard ArchitectureDocumento11 pagineHarvard Architecturepratham gunjNessuna valutazione finora

- Reduced Instruction Set Computer 1 PDFDocumento6 pagineReduced Instruction Set Computer 1 PDFKunal PawarNessuna valutazione finora

- Difference Between Von Neumann and Harvard ArchitectureDocumento4 pagineDifference Between Von Neumann and Harvard Architectureramadan hundessaNessuna valutazione finora

- Von-Neumann Vs Harvard Architecture Differences & UsesDocumento12 pagineVon-Neumann Vs Harvard Architecture Differences & UsesK.bhogendranathareddy KuppireddyNessuna valutazione finora

- Asynchronous IIIDocumento5 pagineAsynchronous IIIJiever AustriaNessuna valutazione finora

- CPU ArchitectureDocumento14 pagineCPU ArchitectureTrynosNessuna valutazione finora

- Microprocessor NotesDocumento44 pagineMicroprocessor NotesMag CreationNessuna valutazione finora

- Processor ArchitecturesDocumento2 pagineProcessor Architecturesramadan hundessaNessuna valutazione finora

- Coa D2.1Documento31 pagineCoa D2.1Csk CskNessuna valutazione finora

- 3.2.4 Architecture of The DSPDocumento4 pagine3.2.4 Architecture of The DSPawanitNessuna valutazione finora

- Memory HierarchyDocumento6 pagineMemory HierarchyIsuru KasthurirathneNessuna valutazione finora

- Memory and ClassificationDocumento8 pagineMemory and Classificationsingh7863Nessuna valutazione finora

- Embedded Processor Architecture: 16bec033@nirmauni - Ac.in 16bec034@nirmauni - Ac.inDocumento4 pagineEmbedded Processor Architecture: 16bec033@nirmauni - Ac.in 16bec034@nirmauni - Ac.inSARTHAK SETHNessuna valutazione finora

- Microprocessor and Assembly Language: Lecture-2-Computer ArchitectureDocumento21 pagineMicroprocessor and Assembly Language: Lecture-2-Computer ArchitectureIqraNessuna valutazione finora

- Part 1B, DR S.W. MooreDocumento16 paginePart 1B, DR S.W. MooreElliottRosenthal100% (3)

- Sr. No. Key Computer Architecture Computer OrganizationDocumento11 pagineSr. No. Key Computer Architecture Computer OrganizationKashif ZamanNessuna valutazione finora

- Gaurav Chaudhary COADocumento11 pagineGaurav Chaudhary COAVISHAL KUMAR SHAWNessuna valutazione finora

- Von-Neumann Vs Harvard Architecture - Differences & UsesDocumento14 pagineVon-Neumann Vs Harvard Architecture - Differences & UsesbigumangabaNessuna valutazione finora

- Lovely Professional University: Computer Organization and ArchitectureDocumento7 pagineLovely Professional University: Computer Organization and ArchitectureYogesh Verma YogiNessuna valutazione finora

- Anatomy of A Program in Memory - Gustavo DuarteDocumento41 pagineAnatomy of A Program in Memory - Gustavo DuarteRigs JuarezNessuna valutazione finora

- Modern X86 Assembly Language Programming: Covers x86 64-bit, AVX, AVX2, and AVX-512Da EverandModern X86 Assembly Language Programming: Covers x86 64-bit, AVX, AVX2, and AVX-512Nessuna valutazione finora

- Listofproprietar1419unit 7Documento44 pagineListofproprietar1419unit 7beta2009Nessuna valutazione finora

- DatasheetDocumento5 pagineDatasheetbeta2009Nessuna valutazione finora

- Britannia (TV Series) - Wikipedia PDFDocumento5 pagineBritannia (TV Series) - Wikipedia PDFbeta2009Nessuna valutazione finora

- Condor (TV Series) - WikipediaDocumento7 pagineCondor (TV Series) - Wikipediabeta2009Nessuna valutazione finora

- Chilling Adventures of Sabrina (TV Series) - WikipediaDocumento17 pagineChilling Adventures of Sabrina (TV Series) - Wikipediabeta2009Nessuna valutazione finora

- The Adventures of Rocky and Bullwinkle (TV Series) - WikipediaDocumento7 pagineThe Adventures of Rocky and Bullwinkle (TV Series) - Wikipediabeta2009Nessuna valutazione finora

- Uranus - Wikipedia, The Free Encyclopedia1Documento13 pagineUranus - Wikipedia, The Free Encyclopedia1beta2009Nessuna valutazione finora

- Underwater Wellhead Casing Patch: Instruction Manual 6480Documento8 pagineUnderwater Wellhead Casing Patch: Instruction Manual 6480Ragui StephanosNessuna valutazione finora

- Ces Presentation 08 23 23Documento13 pagineCes Presentation 08 23 23api-317062486Nessuna valutazione finora

- Catalogo AWSDocumento46 pagineCatalogo AWScesarNessuna valutazione finora

- Departmental Costing and Cost Allocation: Costs-The Relationship Between Costs and The Department Being AnalyzedDocumento37 pagineDepartmental Costing and Cost Allocation: Costs-The Relationship Between Costs and The Department Being AnalyzedGeorgina AlpertNessuna valutazione finora

- MSDS - Tuff-Krete HD - Part DDocumento6 pagineMSDS - Tuff-Krete HD - Part DAl GuinitaranNessuna valutazione finora

- SM Land Vs BCDADocumento68 pagineSM Land Vs BCDAelobeniaNessuna valutazione finora

- Sourcing Decisions in A Supply Chain: Powerpoint Presentation To Accompany Powerpoint Presentation To AccompanyDocumento58 pagineSourcing Decisions in A Supply Chain: Powerpoint Presentation To Accompany Powerpoint Presentation To AccompanyAlaa Al HarbiNessuna valutazione finora

- Address MappingDocumento26 pagineAddress MappingLokesh KumarNessuna valutazione finora

- 06-Apache SparkDocumento75 pagine06-Apache SparkTarike ZewudeNessuna valutazione finora

- QA/QC Checklist - Installation of MDB Panel BoardsDocumento6 pagineQA/QC Checklist - Installation of MDB Panel Boardsehtesham100% (1)

- Getting StartedDocumento45 pagineGetting StartedMuhammad Owais Bilal AwanNessuna valutazione finora

- Section 8 Illustrations and Parts List: Sullair CorporationDocumento1 paginaSection 8 Illustrations and Parts List: Sullair CorporationBisma MasoodNessuna valutazione finora

- Lab 6 PicoblazeDocumento6 pagineLab 6 PicoblazeMadalin NeaguNessuna valutazione finora

- Transparency Documentation EN 2019Documento23 pagineTransparency Documentation EN 2019shani ChahalNessuna valutazione finora

- Dialog Suntel MergerDocumento8 pagineDialog Suntel MergerPrasad DilrukshanaNessuna valutazione finora

- Information Security Chapter 1Documento44 pagineInformation Security Chapter 1bscitsemvNessuna valutazione finora

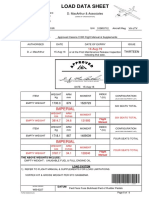

- Load Data Sheet: ImperialDocumento3 pagineLoad Data Sheet: ImperialLaurean Cub BlankNessuna valutazione finora

- SBL - The Event - QuestionDocumento9 pagineSBL - The Event - QuestionLucio Indiana WalazaNessuna valutazione finora

- COOKERY10 Q2W4 10p LATOJA SPTVEDocumento10 pagineCOOKERY10 Q2W4 10p LATOJA SPTVECritt GogolinNessuna valutazione finora

- Wind Energy in MalaysiaDocumento17 pagineWind Energy in MalaysiaJia Le ChowNessuna valutazione finora

- CIR Vs PAL - ConstructionDocumento8 pagineCIR Vs PAL - ConstructionEvan NervezaNessuna valutazione finora

- CLAT 2014 Previous Year Question Paper Answer KeyDocumento41 pagineCLAT 2014 Previous Year Question Paper Answer Keyakhil SrinadhuNessuna valutazione finora

- My CoursesDocumento108 pagineMy Coursesgyaniprasad49Nessuna valutazione finora

- Weekly Learning PlanDocumento2 pagineWeekly Learning PlanJunrick DalaguitNessuna valutazione finora

- Perkins 20 Kva (404D-22G)Documento2 paginePerkins 20 Kva (404D-22G)RavaelNessuna valutazione finora

- Financial Derivatives: Prof. Scott JoslinDocumento44 pagineFinancial Derivatives: Prof. Scott JoslinarnavNessuna valutazione finora

- Oracle Exadata Database Machine X4-2: Features and FactsDocumento17 pagineOracle Exadata Database Machine X4-2: Features and FactsGanesh JNessuna valutazione finora

- A320 Basic Edition Flight TutorialDocumento50 pagineA320 Basic Edition Flight TutorialOrlando CuestaNessuna valutazione finora

- Job Description For QAQC EngineerDocumento2 pagineJob Description For QAQC EngineerSafriza ZaidiNessuna valutazione finora

- 1400 Service Manual2Documento40 pagine1400 Service Manual2Gabriel Catanescu100% (1)