Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Unidad 1 Modelo de Arquitecturas de Cómputo

Caricato da

Rosario Ramírez RiosTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Unidad 1 Modelo de Arquitecturas de Cómputo

Caricato da

Rosario Ramírez RiosCopyright:

Formati disponibili

Unidad 1 Modelo de arquitecturas de cmputo.

1.1 Modelos de arquitecturas de cmputo.

Arquitecturas Clsicas. Estas arquitecturas se desarrollaron en las primeras computadoras electromecnicas y de tubos de vaco. Aun son usadas en procesadores empotrados de gama baja y son la base de la mayora de las arquitecturas modernas

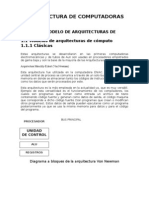

Arquitectura Mauchly-Eckert (Von Newman)

Esta arquitectura fue utilizada en la computadora ENIAC. Consiste en una unidad central de proceso que se comunica a travs de un solo bus con un banco de memoria en donde se almacenan tanto los cdigos de instruccin del programa, como los datos que sern procesados por este.

Esta arquitectura es la ms empleada en la actualidad ya, que es muy verstil.

Ejemplo de esta versatilidad es el funcionamiento de los compiladores, los cuales son programas que toman como entrada un archivo de texto conteniendo cdigo fuente y generan como datos de salida, el cdigo maquina que corresponde a dicho cdigo fuente: (Son programas que crean o modifican otros programas). Estos datos de salida pueden ejecutarse como un programa posteriormente ya que se usa la misma memoria para datos y para el cdigo del programa.

La principal desventaja de esta arquitectura, es que el bus de datos y direcciones nico se convierte en un cuello de botella por el cual debe pasar toda la informacin que se lee de o se escribe a la memoria, obligando a que todos los accesos a esta sean secuenciales.

Esto limita el grado de paralelismo (acciones que se pueden realizar al mismo tiempo) y por lo tanto, el desempeo de la computadora.

Este efecto se conoce como el cuello de botella de Von Newman

En esta arquitectura apareci por primera vez el concepto de programa almacenado. Anteriormente la secuencia de las operaciones era dictada por el alambrado de la unidad de control, e cambiarla implicaba un proceso de recableado laborioso, lento(hasta tres semanas) y propenso a errores. En esta arquitectura se asigna un cdigo numrico a cada instruccin. Dichos cdigos se almacenan en la misma unidad de memoria que los datos que van a procesarse, para ser ejecutados en el orden en que se encuentran almacenados en memoria. Esto permite cambiar rpidamente la aplicacin de la computadora y dio origen a las computadoras de propsito general.

Mas a detalle, el procesador se subdivide en una unidad de control (C.U.), una unidad lgica aritmtica (A.L.U.) y una serie de registros. Los registros sirven para almacenar internamente datos y estado del procesador. La unidad aritmtica lgica proporciona la capacidad de realizar operaciones aritmticas y lgicas. La unidad de control genera las seales de control para leer el cdigo de las instrucciones, decodificarlas y hacer que la ALU las ejecute.

Arquitectura Harvard

Esta arquitectura surgi en la universidad del mismo nombre, poco despus de que la arquitectura Von Newman apareciera en la universidad de Princeton. Al igual que en la arquitectura Von Newman, el programa se almacena como un cdigo numrico en la memoria, pero no en el mismo espacio de memoria ni en el mismo formato que los datos. Por ejemplo, se pueden almacenar las instrucciones en doce bits en la memoria de programa, mientras los datos de almacenan en 8 bits en una memoria aparte.

El hecho de tener un bus separado para el programa y otro para los datos permite que se lea el cdigo de operacin de una instruccin, al mismo tiempo se lee de la memoria de datos los operados de la instruccin previa. As se evita el problema del cuello de botella de Von Newman y se obtiene un mejor desempeo.

En la actualidad la mayora de los procesadores modernos se conectan al exterior de manera similar a a la arquitectura Von Newman, con un banco de memoria masivo nico, pero internamente incluyen varios niveles de memoria cache con bancos separados en cache de programa y cache de datos, buscando un mejor desempeo sin perder la versatilidad.

1.1.2 Arquitecturas Segmentadas.

Las arquitecturas segmentadas o con segmentacin del cauce buscan mejorar el desempeo realizando paralelamente varias etapas del ciclo de instruccin al mismo tiempo. El procesador se divide en varias unidades funcionales independientes y se dividen entre ellas el procesamiento de las instrucciones. Para comprender mejor esto, supongamos que un procesador simple tiene un ciclo de instruccin sencillo consistente solamente en una etapa de bsqueda del cdigo de instruccin y en otra etapa de ejecucin de la instruccin. En un procesador sin segmentacin del cauce, las dos etapas se realizaran de manera secuencial para cada una de la instrucciones, como lo muestra la siguiente figura.

En un procesador con segmentacin del cause, cada una de estas etapas se asigna a una unidad funcional diferente, la bsqueda a la unidad de bsqueda y la ejecucin a la unidad de ejecucin. Estas unidades pueden trabajar en forma paralela en instrucciones diferentes. Estas unidades se comunican por medio de una cola de instrucciones en la que la unidad de bsqueda coloca los cdigos de instruccin que ley para que la unidad de ejecucin los tome de la cola y los ejecute. Esta cola se parece a un tubo donde las instrucciones entran por un extremo y salen por el otro. De esta analoga proviene el nombre en ingles: Pipelining o entubamiento. En general se divide al procesador segmentado en una unidad independiente por cada etapa del ciclo de instruccin.

Completando el ejemplo anterior, en un procesador con segmentacin, la unidad de bsqueda comenzara buscando el cdigo de la primera instruccin en el primer ciclo de reloj. Durante el segundo ciclo de reloj, la unidad de bsqueda obtendra el cdigo de la instruccin 2, mientras que la unidad de ejecucin ejecuta la instruccin 1 y as sucesivamente. La siguiente figura muestra este proceso.

En este esquema sigue tomando el mismo numero de ciclos de reloj (el mismo tiempo), pero como se trabaja en varias instrucciones al mismo tiempo, el nmero promedio de instrucciones por segundo se multiplica. En teora, el rendimiento de un procesador segmentado mejora con respecto a uno no segmentado en un factor igual al numero de etapas independientes. Sin embargo, la mejora en el rendimiento no es proporcional al numero de segmentos en el cauce debido a que cada etapa no toma el mismo tiempo en realizarse, adems de que se puede presentar competencia por el uso de algunos recursos como la memoria principal. Otra razn por la que las ventajas de este esquema se pierden es cuando se encuentra un salto en el programa y todas las instrucciones que ya se buscaron y se encuentran en la cola, deben descartarse y comenzar a buscar las instrucciones desde cero a partir de la direccin a la que se salto. Esto reduce el desempeo del procesador y an se investigan maneras de predecir los saltos para evitar este problema.

1.1.3 Arquitecturas de multiprocesamiento.

Cuando se desea incrementar el desempeo ms aya de lo que permite la tcnica de segmentacin del cauce (limite terico de una instruccin por ciclo de reloj), se requiere utilizar ms de un procesador para la ejecucin del programa de aplicacin.

Las CPU de multiprocesamiento se clasifican de la siguiente manera:

SISO (Single Instruction, Single Operand ) computadoras independientes

SIMO (Single Instruction, Multiple Operand ) procesadores vectoriales

MISO (Multiple Instruction, Single Operand ) No implementado

MIMO (Multiple Instruction, Multiple Operand ) sistemas SMP, Clusters

Procesadores vectoriales Son computadoras pensadas para aplicar un mismo algoritmo numrico a una serie de datos matriciales, en especial en la simulacin de sistemas fsicos complejos, tales como simuladores para predecir el clima, explosiones atmicas, reacciones qumicas complejas, etc., donde los datos son representados como grandes nmeros de datos en forma matricial sobr los que se deben se aplicar el mismo algoritmo numrico.

En los sistemas SMP (Simetric Multiprocesesors), varios procesadores comparten la misma memoria principal y perifricos de I/O, Normalmente conectados por un bus comn. Se conocen como simtricos, ya que ningn procesador toma el papel de maestro y los dems de esclavos, sino que todos tienen derechos similares en cuanto al acceso a la memoria y perifricos y ambos son administrados por el sistema operativo.

Los Clusters son conjuntos de computadoras independientes conectadas en una red de rea local o por un bis de interconexin y que trabajan cooperativamente para resolver un problema. Es clave en su funcionamiento contar con un sistema operativo y programas de aplicacin capaces de distribuir el trabajo entre las computadoras de la red.

1.2 Anlisis de los componentes.

1.2.1 CPU.

1.2.1.1 Arquitecturas.

Ademas de las arquitecturas clsicas mencionadas anteriormente, en la actualidad han aparecido arquitecturas hbridas entre la Von Newman y la Harvard, buscando conservar la flexibilidad, pero mejorando el rendimiento.

El cambio ms importante de los ltimos aos en diseo de las computadoras de los ltimos aos se dio durante los aos 1980, con la aparicin de la corriente de diseo conocida como computadoras de conjunto reducido de instrucciones (RISC, por sus siglas en ingles). Esta escuela pretende aplicar un enfoque totalmente distinto al tradicional hasta entonces, que paso a conocerse como computadoras de conjunto complejo de instrucciones (CISC) para diferenciarla de la nueva tendencia.

La tendencia tradional, representada por las arquitecturas CISC (Complex Instruction Set Computers) se caracterizan por tener un nmero amplio de instrucciones y modos de direccionamiento. Se implementan instrucciones especiales que realizan funciones complejas, de manera que un programador puede encontrar con seguridad, una instruccin especial que realiza en hardware la funcin que el necesita. El nmero de registros del CPU es limitado, ya que las compuertas lgicas del circuito integrado se emplean para implementar las secuencias de control de estas instrucciones especiales.

Al investigar las tendencias en la escritura de software cientfico y comercial al inicio de los 80, ya se pudo observar que en general ya no se programaba mucho en ensamblador, sino en lenguajes de alto nivel, tales como C. Los compiladores de lenguajes de alto nivel no hacan uso de las instrucciones especiales implementadas en los procesadores CISC, por lo que resultaba un desperdicio de recursos emplear las compuertas del circuito de esta forma. Por lo anterior, se decidi que era mejor emplear estos recursos en hacer que las pocas instrucciones que realmente empleaban los compiladores se ejecutaran lo ms rpidamente posible. As surgi la escuela de diseo RISC (Reduced Instruction Set Computers) donde solo se cuenta con unas pocas instrucciones y modos de direccionamiento, pero se busca implementarlos de forma muy eficiente y que todas las instrucciones trabajen con todos los modos de direccionamiento.

Ademas, se observo que una de las tareas que tomaban ms tiempo en ejecutarse en lenguajes de alto nivel, era el pasar los parmetros a las subrutinas a travs de la pila.

Como la forma ms rpida de hacer este paso es por medio de registros del CPU, se busco dotarlo con un amplio nmero de registros, a travs de los cuales se pueden pasar dichos parmetros.

1.2.1.2 Tipos.

Los CPUs modernos pueden clasificarse de acuerdo a varias caractersticas, tales como: el tamao del ALU o del Bus de conexin al exterior (8, 16, 32, 64 bits),si tienen cauce segmentado o no segmentado, si con tipo CISC o RISC, Von Newan o Harvard y si solo tienen instrucciones enteras o implementan tambin instrucciones de punto flotante.

1.2.1.3 Caractersticas.

Las caractersticas ms importantes a considerar al escoger un CPU para usarlo en una aplicacin, son:

Modelo del programador (Conjunto de registros que el programador puede utilizar), forman el modelo mental del C P U que el programador utiliza al programar en ensamblador.

Conjunto de instrucciones que puede ejecutar el C P U

Modos de direccionamiento que pueden usarse para obtener los operandos de las instrucciones.

Ciclo de instruccin (el conjunto de pasos que realiza el C P U para procesar cada instruccin)

Buses de interconexin, usados para que el C P U lea y escriba a la memoria y a los dispositivos de entrada y salida.

1.2.1.4 Funcionamiento.

Debido a la gran variedad de CPU disponibles comercialmente, se explicara el funcionamiento de un unidad central de proceso imaginaria muy simple, pero que resume el funcionamiento bsico de la mayora de los CPUs. Este CPU es similar a las primeras computadoras existentes en los aos 1950s.

Esta computadora contara con una memoria de 4096 palabras de 16 bits cada una. Esto corresponde a un bus de direcciones de 12 bits y un bus de datos de 16 bits). En cada localidad de memoria se podr almacenar un entero de 16 bits o el cdigo de una instruccin, tambin de 16 bits.

Todos los CPU tienen como funcin principal la ejecucin de un programa acorde a la aplicacin del mismo. Un programa es un conjunto de instrucciones almacenadas de acuerdo al orden en que deben ejecutarse. Por lo tanto, toda computadora debe ser capaz de procesar las instrucciones de su programa en un ciclo de instruccin, consistente en un nmero de etapas que varia con cada CPU, pero que tradicionalmente han sido tres:

1-Bsqueda del cdigo de Instruccin. Esta consiste en leer de la memoria cual ser la siguiente instruccin a ejecutar, la cual esta almacenada en forma de un cdigo numrico que indica cual de todas las operaciones que puede realizar el CPU sera la siguiente y con que operandos se ejecutara.

2- Decodificacin. Consiste en tomar el cdigo numrico e identificar a cual de las operaciones que puede realizar el CPU corresponde dicho cdigo. El proceso contrario, la codificacin, consiste en conociendo la instruccin, determinar el nmero que la va a representar. Esta etapa usualmente se realiza con un decodificador binario.

3- Ejecucin. En esta etapa se lleva a cabo la operacin sobre los datos que se vallan a procesar. En general, la unidad de control (CU) genera las seales de control necesarias para llevar los datos a las entradas de la Unidad Aritmtica Lgica, la cual efectuar las operaciones aritmticas y lgicas.

Posteriormente, la unidad de control generara las seales de control necesarias para transferir la salida de la Unidad Aritmtica Lgica al registro donde sern almacenados los resultados para su uso posterior.

Es importante recordar que cada instruccin del programa se almacena en memoria como un nmero binario. Este nmero se conoce como cdigo de instruccin, y usualmente se divide en al menos dos campos: un cdigo de operacin (Opcode) y un nmero que representa al operando u operandos de la instruccin. En el caso de la computadora imaginaria que estamos estudiando, se almacena cada instruccin en una de las 4096 palabras de memoria de 16 bits cada una. Se utiliza un formato de un solo operando, con un segundo operando en el acumulador cuando es necesario. Los cuatro bits ms significativos de los diecisis bits de la palabra se dedican a almacenar el cdigo de operacin. Los doce bits menos significativos se dedican a almacenar la direccin del operando.

Las partes del CPU de la computadora imaginaria son:

ACC Acumulador, se usar para almacenar uno de los operandos y el resultado de varias de las instrucciones

MAR (Memory Address Register) Registro de direccin de memoria, selecciona a que localidad de memoria se va a leer o a escribir.

MBR (Memory Bus Register) Registro de bus de memoria. A travs de l se lee y se escriben los datos.

PC (Program Counter) El contador de programa almacena la direccin de la siguiente instruccin a buscar. Por esta razn tambin es conocido como apuntador de instrucciones.

IR Registro de instruccin, guarda el cdigo de la instruccin que se esta ejecutando.

Flags Registro de Banderas, agrupa a todas las banderas de la ALU en un registro, en el caso de nuestra computadora imaginaria, las banderas disponibles sern: Z Bandera de Cero, se pone en uno cuando todos los bits del resultado son cero; O Sobreflujo, se pone en uno cuando el resultado de la ultima operacin se sale de el rango de los nmeros de 16 bits con signo;

C Acarreo, se enciende cuando el resultado de la ultima operacin se sale del rengo de los nmeros de 16 bits sin signo.

Como se explico anteriormente, el funcionamiento del CPU se basa en los pasos del ciclo de instruccin, consistentes en bsqueda, decodificacin y ejecucin de la instruccin.

Comenzaremos revisando los pasos correspondientes a la bsqueda de la instruccin.

El registro PC contiene la direccin de la localidad de memoria que contiene el cdigo de instruccin de la siguiente instruccin a ejecutar. Como la etapa de bsqueda consistir bsicamente en leer este cdigo y almacenarlo en el registro IR para su posterior uso en las etapas de decodificacin y ejecucin, el contenido de PC se copia al MAR para poder leer esa localidad de memoria. Se lee la memoria y el resultado de dicha lectura se copia del MBR al IR. Finalmente, se incrementa el PC para que en el siguiente ciclo de instruccin se lea la instruccin de la localidad de memoria consecutiva.

Resumiendo estas operaciones en lenguaje de transferencia de registros:

MAR<-PC IR<-[MAR] PC<-PC+1

En la etapa de decodificacin simplemente se separan los cdigos de operacin de los operandos. Por ejemplo, la instruccin LOAD 023h se codificara como 0023h, siendo 0h el cdigo de operacin y 023h el operando. Adems, la unidad de control deber identificar que al opcode 0 corresponde a la instruccin LOAD para que en la siguiente etapa se realicen las operaciones correspondientes a esta instruccin.

En cuanto a la etapa de ejecucin, los pasos realizados en esta etapa varan dependiendo del cdigo de operacin ledo en la etapa de bsqueda. Por ejemplo, si el cdigo ledo es un 0, que corresponde con una instruccin LOAD, la etapa de ejecucin consistir en copiar la parte de la

direccin del operando en el registro MAR para poder leer la localidad en donde se encuentra el operando. Se lee el operando de memoria y el dato ledo se copia del MBR al acumulador. Resumiendo dichas operaciones en lenguaje de transferencia de registros se tiene:

MAR<-IR(M) //IR(M) representa los bits del registro IR que almacenan la direccin del operando

1.2.2 Memoria.

Una memoria es un dispositivo que puede mantenerse en por lo menos dos estados estables por un cierto periodo de tiempo. Cada uno de estos estados estables puede utilizarse para representar un bit. A un dispositivo con la capacidad de almacenar por lo menos un bit se le conoce como celda bsica de memoria.

Un dispositivo de memoria completo se forma con varias celdas bsicas y los circuitos asociados para poder leer y escribir dichas celdas bsicas, agrupadas como localidades de memoria que permitan almacenar un grupo de N bits. El nmero de bits que puede almacenar cada localidad de memoria es conocido como el ancho de palabra de la memoria. Coincide con el ancho del bus de datos. Uno de los circuitos auxiliares que integran la memoria es el decodificador de direcciones. Su funcin es la de activar a las celdas bsicas que van a ser ledas o escritas a partir de la direccin presente en el bus de direcciones. Tiene como entradas las n lineas del bus de direcciones y 2N lineas de habilitacin de localidad, cada una correspondiente a una combinacin binaria distinta de los bits de direcciones. Por lo tanto, el nmero de localidades de memoria disponibles en un dispositivo (T) se relaciona con el nmero de lineas de direccin N por T= 2N .

1.2.2.1 Arquitecturas

Desde hace unas decenas de aos, los procesadores han estado aumentando su velocidad de operacin a un paso mucho ms rpido que las memorias, lo que ha llevado a la situacin en que los procesadores actuales operan mucho ms rpidamente que la memoria principal de las computadoras. Esto hace que el procesador tenga que quedarse detenido por varios ciclos de reloj (estados de espera) cada vez que tiene que leer o escribir a la memoria principal.

Para aliviar un poco esta situacin conservando el precio de la computadora razonablemente bajo, se ha organizado a la memoria como una jerarqua de diversos niveles con distintos tamaos y velocidades.

Hay que recordar que la memoria ms rpida es mucho ms cara que la ms lenta y que por lo tanto, es menor la cantidad de memoria de este tipo que se puede usar. De esta manera, la mayor parte de la capacidad de almacenamiento de la maquina se encuentra en el disco duro, que tiene un costo por Gbyte muy bajo, pero que tambin es muy lento debido a que hay que mover piezas mecnicas para leer o escribir en l. En seguida se encuentra la memoria principal, que normalmente es del tipo RAM dinmica. Es en esta memoria donde se almacenan los programas para que los pueda ejecutar el procesador, as como los datos con que trabajan dichos programas. Con el objetivo de mejorar la velocidad del procesador al ejecutar ciclos y al leer repetidamente datos de uso comn, se coloca una pequea cantidad de memoria RAM esttica entre el procesador y la memoria principal. Esta memoria es conocida como memoria cache y guarda una copia de una pequea regin de la memoria principal, para que si se requiere volver a leer los datos almacenados en esta regin de memoria, no se tenga que esperar a que se lea la memoria principal, que es mucho ms lenta que la cache y que el procesador. Finalmente, en la cima de la jerarqua, se encuentran los registros del procesador que aunque son muy pocos, son los que se pueden leer y escribir ms rpidamente.

1.2.2.2 Tipos

Los diversos tipos de memorias se clasifican como memorias voltiles y memorias no voltiles. Las memorias voltiles pierden la informacin que almacenan al momento en que se les desconecta la energa, mientras que las no voltiles conservan su contenido aunque no estn alimentadas.

Las memorias voltiles son conocidas desde las primeras computadoras como memorias de acceso aleatorio (RAM), ya que en esa poca las memorias voltiles eran de acceso secuencial.

Dentro de las memorias voltiles se encuentran las subclases RAM Dinmica y RAM Esttica.

Las memorias no voltiles conservan sus datos a pesar de que en este conectadas el voltaje del alimentacin. De hecho pueden conservar sus datos por un periodo de tiempo relativamente largo, usualmente entre cien y 200 aos. Conforme evolucionado la tecnologa, se han desarrollado diversas familias de rumores no voltiles, entre las cuales se encuentran:

la memoria de solo lectura (ROM -Read only Memory)

la memoria de solo lectura programable (PROM -Programable Read only Memory)

la memoria de solo lectura programable y borrable (EPROM - Erasable Read only Memory)

la memoria de solo lectura programable y borrable elctricamente (EEPROM Electricaly Erasable Read only Memory) y la memoria flash.

1.2.2.3 Caractersticas

En cuanto a las memorias voltiles, la memoria RAM dinmica es muy rpida pero muy cara. En contraste, la memoria RAM esttica es muy barata pero muy lenta.

En general, las memorias no voltiles son baratas y su precio depende sobre todo de su capacidad de almacenamiento. Algunas de estas tecnologas son consideradas obsoletas y por lo tanto casi no son utilizadas en actualidad.

1.2.2.4 Funcionamiento (ALU, unidad de control, Registros y buses internos)

El tipo ms comn de memorias voltiles es la RAM dinmica, que utiliza la capacitancia parsita de los transistores MOSFET con los que esta construida para almacenar un bit. Como solo se requiere de un transistor por celda de memoria, esta memoria es muy econmica, pero debido al tiempo que toma cargar la gran capacitancia de los transistores con los que esta construida, es muy lenta.

El otro tipo de memoria RAM utilizado en la actualidad, es la RAM esttica. Esta memoria se construye con el mismo tipo de transistores con los que se construyen los procesadores, por lo que pueden operar a una velocidad similar a la del procesador. Sin embargo, como se requieren alrededor de 8 transistores por bit, el costo de esta memoria es mucho ms alto que el de la RAM dinmica.

En cuanto a las memorias no voltiles, En cuanto a las memorias no voltiles, histricamente han existido varios tipos. Los primeros slo podan ser ledos, por lo que fueron conocidos como memorias de solo lectura (ROM - Read Only Memory). A pesar de que los tipos ms modernos permiten que su contenido se ha modificado por el usuario, an son conocidos como memorias de solo lectura.

En las memorias de solo lectura originales (ROM), el almacenar en uno o un cero, depende de si el fabricante coloc o no un diodo fsicamente en el circuito de la memoria. De esta manera, el contenido de la memoria queda establecido por el fabricante desde el momento de su construccin y no es posible que el usuario no modifique. Sin embargo, este tipo de memoria es an muy usada debido a que es muy econmica y por lo tanto, ideal para la produccin en masa de muchos artefactos de consumo masivo.

Con el objetivo de hacer a la memoria de solo lectura un dispositivo ms verstil, algunos fabricantes de memorias sustituyeron a los diodos por fusibles semiconductores que el usuario poda quemar usando un programador especial. Esto permiti a los usuarios tener dispositivos de memoria de solo lectura cuyo contenido ellos mismos podan programar, por lo que estos dispositivos fueron conocidos como memorias de solo lectura programables (PROM - Programable Read Only Memory). El nico inconveniente que presentaban estas memorias era que si se necesitaba hacer un pequeo cambio, deba descartarse a la memoria ya programada y utilizar un dispositivo nuevo en blanco.

Este problema pudo eliminarse al sustituir los fusibles semiconductores por transistores con una compuerta flotante que les permita almacenar una carga elctrica por un tiempo muy grande.

Esta compuerta flotante permite almacenar una carga elctrica que reduce el voltaje que debe ser aplicado a la compuerta principal para hacer que el rector conduzca. De esta manera, aplicando un voltaje de prueba a la compuerta principal y observando si el transistor conduce, se puede saber si un transistor no tiene carga en su compuerta flotante (est borrado o almacena un uno) o s (estaba programado o almacena un cero).

La primera generacin de dispositivos que utiliz esta tecnologa, conocidos como memorias de solo lectura programables y borrables (EPROM), podan grabarse elctricamente aplicando un voltaje ms alto de lo normal a la compuerta principal. Sin embargo, para eliminar la carga tendra que aplicarse una luz ultravioleta intensa al dispositivo, lo cual eliminaba la carga almacenada en la compuerta flotante. Para realizar este proceso de borrado era necesario retirar al dispositivo del circuito de aplicacin y colocarlo en el borrador de luz ultravioleta por aproximadamente media hora.

En la segunda generacin de dispositivos de memoria que utilizaban transistores con compuertas flotante se logr eliminar la carga elctricamente, con lo que dichos dispositivos se volvieron ms verstiles. Los dispositivos de esta generacin se conocieron como memorias de solo lectura programables y borrables elctricamente (EEPROM). Como cada byte de la memoria poda ser borrado de forma independiente, requeran de muchos circuitos auxiliares para permitir este tipo de borrado, lo que aumentaba su costo.

Para la tercera generacin, se busc reducir el costo de los dispositivos reduciendo la cantidades circuitos auxiliares necesarios para el borrado. Esto se logr permitiendo nicamente el borrado de bloques de memoria de tamao relativamente grande. Tambin se busc almacenar ms de un bit por celda de memoria controlando la cantidad de carga almacenada en cada celda, de manera que con ocho voltajes discretos se pueden representar las ocho combinaciones correspondientes a tres bits.

. 1.2.2.1 Conceptos bsicos del manejo de la memoria

El termino ubicacin indica si la memoria es interna o externa al computador. La memoria interna suele identificarse con la memoria principal. Sin embargo hay adems otras formas de memoria interna. El procesador necesita su propia memoria local en forma de registros. La unidad de control del procesador tambin puede necesitar su propia memoria interna. La memoria cache es tambin otro tipo de memoria interna. La memoria externa consta de dispositivos perifricos de almacenamiento, tales como discos, cintas que son accesibles al procesador por controladores de E/S.

Una caracterstica obvia de la memoria es su capacidad. Para memorias internas se expresa normalmente en trminos de bytes (1 byte=8 bits) o de palabras. Longitudes de palabra comunes son 8, 16 y 32 bits. Las memorias externas suelen expresarse en bytes.

Unidad de transferencia: para memorias internas es igual al numero de lneas de entrada/salida de datos del modulo de memoria. A menudo es igual a la longitud de palabra, pero suele ser mayor, por ejemplo 64, 128 o 256 bits.

Palabra: es la unidad natural de organizacin de la memoria. El tamao de la palabra suele coincidir con el numero de bits utilizados para representar nmeros y con la longitud de las instrucciones. Aunque existen muchas excepciones.

Ejemplo: CRAY C90 tiene una longitud de palabra de 64 bits, pero utiliza una representacin de nmeros enteros de 46 bits.

Unidades direccionables: en algunos sistemas la unidad direccionable es la palabra. Sin embargo muchos de ellos permiten direccionar a nivel de bytes. En cualquier caso, la relacin entre la longitud A de una direccin y el numero N de unidades direccionables es 2 = .

Unidad de transferencia: para la memoria principal es el numero de bits que se leen o escriben en memoria a la vez. La unidad de transferencia no tiene porque coincidir con una palabra o con una unidad direccionable.

Para la memoria externa, los datos se transfieren normalmente en unidades mas grandes que la palabra denominada bloques.

Otro distintivo entre tipos de memoria es el mtodo de acceso que incluye:

Acceso secuencial: la memoria se organiza en unidades de datos llamadas registros. El acceso debe realizarse con una secuencia lineal especifica. Se hace uso de informacin almacenada de direccionamiento que permite separar los registros y ayudar en el proceso de recuperacin de datos. Se utiliza un mecanismo de lectura/escritura compartida que debe ir trasladndose desde su posicin actual a la deseada, pasando cada registro intermedio. El tiempo necesario para acceder a un registro es variable.

Acceso directo: este acceso igual tiene asociado un mecanismo de lectura/escritura. Sin embargo los bloques individuales o registros tienen una direccin nica basada en su direccin fsica.

El acceso se lleva a cabo mediante un acceso directo, seguido de una bsqueda secuencial, bien contando, o bien esperando hasta alcanzar la posicin final. El tiempo de acceso es variable.

Acceso aleatorio (random): cada posicin direccionable de memoria tiene un nico mecanismo de acceso cableado fsicamente. El tiempo para acceder a una posicin dada es constante e

independiente de la secuencia de accesos previos. Por tanto, cualquier posicin puede seleccionarse aleatoriamente y ser direccionada directamente. La memoria principal y algunos sistemas de cach son de acceso aleatorio.

Asociativa: es una memoria del tipo de acceso aleatorio que permite hacer una comparacin de ciertas posiciones de bits dentro de una palabra buscando que coincidan con unos valores dados, y hacer esto para todas las palabras simultneamente. Una palabra es por tanto recuperada basndose en una porcin de su contenido en lugar de su direccin.

Para el usuario, las dos caractersticas mas importantes de una memoria son su capacidad y sus prestaciones, teniendo en cuenta tres parmetros:

Tiempo de acceso (latencia): para memorias de acceso aleatorio es el tiempo que tarda en realizarse una operacin de escritura o lectura, es decir, el tiempo que transcurre desde el instante en el que se presenta una direccin a la memoria hasta que el dato, o ha sido memorizado, o esta disponible para su uso. Para memorias de otro tipo, el tiempo de acceso es el que se tarda en situar el mecanismo de lectura/escritura en la posicin deseada.

Tiempo de ciclo de memoria: este concepto se aplica principalmente a las memorias de acceso aleatorio y consiste en el tiempo de acceso y algn tiempo mas que se requiere antes de que pueda iniciarse un segundo acceso a memoria. Este tiempo adicional puede que sea necesario para que finalicen las transiciones en las lneas de seal o para regenerar los datos en el caso de lecturas destructivas. El tiempo del ciclo de memoria depende de las caractersticas del bus del sistema y no del procesador.

Velocidad de transferencia: es la velocidad a la que se pueden transferir datos a, o desde, una unidad de memoria. Para memorias de acceso aleatorio coincide con el inverso del tiempo de ciclo.

Para otras memorias se usa la siguiente relacin:

Tiempo medio de escritura o de lectura de N bits.Tiempo de acceso medio.

N Numero de bits.

R Velocidad de transferencia, en bits por segundo (bps).

Las caractersticas fsicas en el almacenamiento de datos en memoria: las memorias voltiles la informacin se va perdiendo o desaparece cuando se desconecta la alimentacin. En las no voltiles, la informacin una vez grabada, no se deteriora hasta que se modifique intencionalmente, no necesita fuente de alimentacin.

Las memorias de superficie magntica son no voltiles. Las memorias semiconductoras pueden ser voltiles o no voltiles. Las memorias no borrables no pueden modificarse, salvo que se destruya la unidad de almacenamiento. Estas memorias se conocen como ROM, una memoria no borrable es no voltil.

1.2.2.2 Memoria principal semiconductora.

En computadores antiguos, la forma mas comn de almacenamiento de acceso aleatorio para la memoria principal consista en una matriz de pequeos anillos ferromagnticos denominados ncleos. Por eso la memoria principal reciba el nombre de ncleo (core). La llegada de la microelectrnica y sus ventajas a cabo con las memorias de ncleos. Hoy en da es casi universal el uso de chip semiconductores para la memoria principal.

El elemento bsico de una memoria semiconductora es la celda de memoria, todas las celdas de memoria comparten ciertas propiedades:

Presentan dos estados estables (o semiestables) que pueden emplearse para representar el 1 y el 0 binario.

Puede escribirse en ellas (al menos una vez) para fijar su estado.

Pueden leerse para detectar su estado.

La celda contempla tres terminales para transportar seales elctricas:

El terminal de seleccin, selecciona la celda para que pueda realizarse una operacin de lectura o escritura.

El terminal de control, indica si se trata de una lectura o escritura. Para la escritura el tercer terminal proporciona la seal que fija el estado de la celda a uno o a cero. En una lectura, el tercer terminal se utiliza como salida del estado de la celda.

La memoria de acceso aleatorio (RAM, Random access memory) una de sus caractersticas distintivas es que es posible tanto leer datos como escribir rpidamente nuevos datos en ellas.

Otra caracterstica es que es voltil, siempre tiene que estar alimentada.

Las tecnologas de RAM se dividen en dos variantes: dinmicas y estticas.

RAM dinmica (DRAM):

Esta hecha con celdas que almacenan los datos como cargas elctricas en condensadores. La presencia o ausencia de carga en un condensador se interpretan como el uno o el cero binarios. Los condensadores ya que tienen una tendencia natural a descargarse, las DRAM requieren refrescos peridicos para mantener memorizados los datos.

RAM esttica (SRAM):

En contraste con la DRAM, un SRAM es un dispositivo digital, basado en los mismo elementos que se usan en el procesador. En una SRAM los valores binarios se almacenan utilizando configuraciones de puertas que forman biestables (flip-flops). Una SRAM mantendr sus datos en tanto se mantenga alimentada.

Tanto las SRAM como las DRAM son voltiles; es decir, debe aplicarse continuamente tensin de alimentacin a la memoria para mantener los valores de los bits.

Otra diferencia es que una celda de una DRAM es mas simple que una SRAM y en consecuencia mas pequea.

Tipos de ROM

Una memoria de solo lectura (ROM Read only memory) contiene un patrn permanente de datos que no puede alterarse. Una ROM es no voltil, es decir, no requiere fuente de alimentacin para mantener memorizados los valores de los bits. Aunque es posible leer de una ROM, no se pueden escribir nuevos datos en ella.

Una aplicacin importante de la ROM es la microprogramacin y otras aplicaciones potenciales son subrutinas de biblioteca para funciones de uso frecuente, programas del sistema y tabla de funciones.

Cuando se requiere un tamao modesto, la ventaja de una ROM es que el programa o los datos estaran permanentemente en memoria principal y nunca seria necesario cargarlos desde un dispositivo de memoria secundaria.

Cuando se necesitan pocas ROM con un contenido particular, una alternativa mas econmica es la ROM programable (PROM) estas son no voltiles y pueden grabarse solo una vez. Para la PROM el proceso de escritura se lleva a cabo elctricamente . Las PROM proporcionan flexibilidad y comodidad.

La memoria de sobre-todo-lectura (read-mostly) que es til para aplicaciones en las que las operaciones de lectura son bastante mas frecuentes que las de escritura, pero para las que se requiere un almacenamiento no voltil, hay tres formas comunes de memoria de este tipo: EPROM, EEPROM y memorias flash.

La memoria de solo lectura programable y borrable pticamente (EPROM, Erasable programmable read only memory) se lee y escribe elctricamente como la PROM, pero antes de la operacin de escritura, todas las celdas de almacenamiento deben primero borrarse a la vez, mediante la exposicin del chip encapsulado a radiacin ultravioleta. Este proceso de borrado puede

La memoria de solo lectura programable y borrable electricamente (EEPROM, Electrically erasable programmable read only memory) esta memoria se puede escribir en cualquier momento sin borrar su contenido anterior, solo se actualiza el byte o bytes direccionados. La EEPROM combina la ventaja de no ser voltil, con la flexibilidad de ser actualizable.

Por ultimo la memoria flash (llamada as por la velocidad con la que puede reprogramarse) esta memoria puede borrarse entera en uno o cuantos segundos, mucho mas rpido que las EPROM. Las memorias flash deben su nombre a que su microchip esta organizado de manera que cada una de sus secciones de celdas se borra mediante una nica accin, de un golpe o flash. Estas memorias no permiten borrar a nivel de byte.

1.2.2.3 Memoria cache.

El objetivo de la memoria cache es lograr que la velocidad de la memoria sea lo mas rpida posible, consiguiendo al mismo tiempo un tamao grande al precio de memorias semiconductoras menos costosas.

La cach consta de C lneas, cada lnea contiene k palabras, ms una etiqueta de unos cuantos bits; denominndose tamao de lnea al numero de palabras que hay en la lnea. El numero de lneas es considerablemente menor que el numero de bloques de memoria principal. Cada lnea incluye una etiqueta que identifica que bloque particular almacena. La etiqueta es usualmente una porcin de la direccin de memoria principal.

El tamao del cache nos gustara que fuera suficientemente pequeo como para que el costo total medio por bit se aproxime al de la memoria principal sola, y que fuera suficientemente grande como para que el tiempo de acceso medio total sea prximo al de la cach sola.

El tamao del cach es tambin limitado por las superficies disponibles de chip y de tarjeta. Como las prestaciones de la cach son muy sensibles al tipo de

La eleccin de la funcin de correspondencia determina como se organiza la cach. Pueden utilizarse tres tcnicas:

Correspondencia directa: consiste en hacer corresponder cada bloque de memoria principal a solo una lnea posible de cach. La correspondencia se expresa como

i:numero de lnea de cach.

j:numero de bloque de memoria principal.

m:numero de lneas en la cach.

La tcnica de correspondencia directa es sencilla y poco costosa de implementar. Su principal desventaja es que hay una posicin concreta de cach para cada bloque dado.

Correspondencia asociativa: esta correspondencia supera la desventaja de la directa, permitiendo que cada bloque de memoria principal pueda cargarse en cualquier lnea de la cach. En este caso, la lgica de control de la cach interpreta una direccin de memoria simplemente como una etiqueta y un campo de palabra. El campo de etiqueta identifica unvocamente un bloque de memoria principal. Para determinar si un bloque est en la cach, su lgica de control debe examinar simultneamente todas las etiquetas de lneas para buscar una coincidencia.

Con esta correspondencia hay flexibilidad para que cualquier bloque sea remplazado cuando se va a escribir uno nuevo en la cach. La principal desventaja de la correspondencia asociativa es la compleja circuitera necesaria para examinar en paralelo las etiquetas de todas las lneas de cach.

Correspondencia asociativa por conjuntos: es la unin de las correspondencias directa y asociativa, sin tomar en cuenta sus desventajas. En este caso, la cach se divide en v conjuntos, cada uno de k lneas. Las relaciones que se tienen son:

i:numero de conjunto de cach. j:numero de bloque de memoria principal. v:numero de lneas de la cach.

Algoritmos de sustitucin

Una vez que se ha llenado la cach, para introducir un nuevo bloque debe sustituirse uno de los bloques existentes. Para la correspondencia directa, solo hay una posible lnea para cada bloque particular y no hay eleccin posible. Para las tcnicas asociativas se requieren algoritmos de sustitucin:

Utilizado menos recientemente (LRU, least - recently used) : sustituye el bloque que se ha mantenido en la cach por mas tiempo sin haber sido referenciado.

Primero en entrar, primero en salir (FIFO, first - in first - out) : se sustituye aquel bloque del conjunto que ha estado mas tiempo en la cach.

Utilizado menos frecuentemente (LFU, least - recently used) : sustituye aquel bloque del conjunto que ha experimentado menos referencias. LFU podra implementarse asociando un contador a cada lnea.

1.2.3 Manejo de la entrada/salida.

1.2.3.1 Mdulos de entrada/salida.

Las principales funciones y requisitos de un modulo de E/S se encuentran dentro de las siguientes categoras:

Control y temporizacin.

Comunicacin con el procesador.

Comunicacin con los dispositivos.

Almacenamiento temporal de datos.

Deteccin de errores.

En cualquier momento, el procesador puede comunicarse con uno o mas dispositivos externos en cualquier orden, segn las necesidades de E/S del programa. Los recursos internos tales como la memoria principal y el bus del sistema deben compartirse entre distintas actividades incluyendo la E/S de datos. As, la funcin de E/S incluye ciertos requisitos de control y temporizacin, para coordinar el trafico entre los recursos internos y los dispositivos externos.

La transferencia de datos desde un dispositivo externo al procesador implica la siguiente secuencia de datos:

1.El procesador interroga al modulo de E/S para comprobar el estado del dispositivo conectado al mismo.

2.El modulo de E/S devuelve el estado del dispositivo.

3.Si el dispositivo esta operativo y preparado para transmitir, el procesador solicita la transferencia del dato mediante una orden al modulo de E/S.

4.El modulo de E/S obtiene un dato del dispositivo externo.

5.Los datos se transfieren desde el modulo de E/S al procesador.

La comunicacin con el procesador implica:

Decodificacin de ordenes: el modulo de E/S acepta ordenes del procesador. Estas ordenes generalmente se envan utilizando lneas del bus de control.

Datos: el procesador y el modulo de E/S intercambian datos a travs del bus de datos. Informacin de estado: puesto que los perifricos son lentos, es importante conocer el estado del modulo de E/S. las seales de estado usuales son busy y ready.

Reconocimiento de direccin: igual que cada palabra de memoria tiene una direccin, cada dispositivo de E/S tiene otra. As, un modulo de E/S puede reconocer una nica direccin para cada uno de los perifricos que controla.

Una tarea esencial para un modulo de E/S es el almacenamiento temporal de datos (Data buffering).

Un modulo de E/S a menudo es responsable de la deteccin de errores y de informar estos errores al procesador. Una clase de errores son los defectos mecnicos y elctricos en el funcionamiento del dispositivo.

1.2.3.2 Entrada/salida programada.

Con la E/S programada, los datos se intercambian entre el procesador y el modulo de E/S. El procesador ejecuta un programa que controla directamente la operacin de E/S, incluyendo la comprobacin del estado del dispositivo, el envi de una orden de lectura o escritura y la transferencia del dato.

Cuando el procesador enva una orden al modulo de E/S, debe esperar hasta que la operacin de E/S concluya. Si el procesador es mas rpido que el modulo de E/S, el procesador desperdicia este tiempo.

Hay cuatro tipos de ordenes de E/S que puede recibir el modulo de E/S cuando es direccionado por el procesador:

Control: se utiliza para activar el perifrico e indicarle que hacer.

Test: se utiliza para comprobar diversas condiciones de estado asociadas con el modulo de E/S y sus perifricos. El procesador podr comprobar si el perifrico en cuestin esta conectado y disponible para su uso. Tambin podr saber si la operacin de E/S mas reciente ha terminado y si se ha producido algn error.

Lectura: hace que el modulo de E/S capte un dato de un perifrico y lo situ en un buffer interno. Despus el procesador, puede obtener el dato solicitando que el modulo de E/S lo ponga en el bus de datos.

Escritura: hace que el modulo de E/S capte un dato (byte o palabra) del bus de datos y posteriormente lo transmita al perifrico.

Cuando el procesador, la memoria principal y las E/S comparten un bus comn, son posibles dos modos de direccionamiento: asignado a memoria y aislado.

1.2.3.3 Entrada/salida mediante interrupciones.

Con la E/S mediante interrupciones, el procesador proporciona la orden de E/S, continua ejecutando otras instrucciones y es interrumpido por el modulo de E/S cuando este ha terminado su trabajo.

Cuando un dispositivo de E/S termina una operacin de E/S, se produce la siguiente secuencia de eventos en el hardware:

1.El dispositivo enva una seal de interrupcin al procesador.

2.El procesador termina la ejecucin de la instruccin en curso antes de responder a la interrupcin.

3.El procesador comprueba si hay interrupciones, determina que hay una, y enva una seal de reconocimiento al dispositivo que origino la interrupcin. La seal de reconocimiento hace que el dispositivo desactive su seal de interrupcin.

4.Ahora el procesador necesita prepararse para transferir el control a la rutina de interrupcin.

5.Despus, el procesador carga el contador de programa con la posicin de inicio del programa de gestin de la interrupcin solicitada. Segn sea la arquitectura del computador y el diseo del sistema operativo puede haber un solo programa, uno por cada tipo de interrupcin, o uno por cada dispositivo y cada tipo de interrupcin.

6.Hasta este momento se han guardado en la pila del sistema el contador de programa y el PSW del programa interrumpido. En concreto, se deben guardar los contenidos de los registros del procesador puesto que estos registros pueden ser utilizados por la rutina de interrupcin.

7.La rutina de gestin de la interrupcin puede continuar ahora procesando la interrupcin.

8.Cuando el procesamiento de la interrupcin ha terminado, los valores de los registros almacenados se recuperan de la pila y se vuelven a almacenar en los registros.

9.El paso final es recuperar los valores del registro PSW (palabra de estado del programa) y del contador del programa desde la pila.

1.2.3.4 Acceso directo a memoria

La E/S con interrupciones, aunque mas eficiente que la sencilla E/S programada, tambin requiere la intervencin activa del procesador para transferir datos entre la memoria y el modulo de E/S y cualquier transferencia de datos debe seguir un camino a travs del procesador. Por tanto, ambas formas de E/S presentan dos inconvenientes:

La velocidad de transferencia de E/S esta limitada por la velocidad a la cual el procesador puede comprobar y dar servicio a un dispositivo.

El procesador debe dedicarse a la gestin de las transferencias de E/S; se debe ejecutar cierto numero de instrucciones por cada transferencia de E/S.

Cuando hay que transferir grandes volmenes de datos, se requiere una tcnica mas eficiente el acceso directo a memoria (DMA).

El DMA requiere un modulo adicional en el bus del sistema. El modulo o controlador del DMA es capaz de imitar al procesador y de hecho de recibir el control del sistema cedido por el procesador. Necesita dicho control para transferir datos a, y desde, memoria a travs del bus del sistema. Para hacerlo el DMA debe utilizar solo cuando el procesador no lo necesita, o debe forzar al procesador a que se suspenda temporalmente su funcionamiento. Esta ultima tcnica es la comn y se denomina robo de ciclo ya que el modulo DMA roba un ciclo de bus.

1.2.3.5 Canales y procesadores de entrada/salida

Funcionamiento de las E/S:

1.El CPU controla directamente al perifrico.

2.Se aade un controlador o modulo de E/S. La CPU utiliza E/S programada por interrupciones, con esta accin de independiza de los detalles especficos de las interfaces de los dispositivos externos.

3.Se utiliza la misma configuracin anterior pero ahora usando interrupciones. La CPU no necesita esperar a que se realice la operacin de E/S.

4.El modulo de E/S tiene acceso directo a la memoria a travs de DMA. Ahora se puede transferir un bloque de datos a, o desde, la memoria sin implicar a la CPU, excepto al comienzo y al final de la transferencia.

5.El modulo de E/S se mejora haciendo que se comporte como un procesador en s, con un repertorio especializado de instrucciones orientado a las E/S.

6.El modulo de E/S tiene una memoria local propia y es, de hecho, un computador en si. Con esta arquitectura, se puede controlar un conjunto grande de dispositivos de E/S con la mnima intervencin de la CPU.

Tipos de canales de E/S:

Un canal selector controla varios dispositivos de velocidad elevada y, en un instante dado, se dedica a transferir datos a uno de esos dispositivos. Es decir, que el canal de E/S selecciona un dispositivo y efecta la transferencia de datos.

Un canal multiplexor puede manejar las E/S de varios dispositivos al mismo tiempo. Para dispositivos de velocidad reducida, un multiplexor de byte acepta o transmite caracteres tan rpido como es posible a varios dispositivos.

1.2.4 Buses

Un bus es un camino de comunicacin entre dos o mas dispositivos. Una caracterstica clave de un bus es que trata de un medio de transmisin compartido. Al bus se conectan varios dispositivos y cualquier seal transmitida por uno de esos dispositivos est disponible para que los otros dispositivos conectados al bus puedan acceder a ella. Si dos dispositivos transmiten durante el mismo periodo de tiempo, sus seales pueden solaparse y distorsionarse. Solamente un dispositivo puede transmitir con xito en un momento dado.

1.2.4.1 Tipos de buses

Los computadores poseen diferentes tipos de buses que proporcionan comunicacin entre sus componentes a distintos niveles dentro de la jerarqua del sistema. El bus conecta los componentes principales del computador (procesador, memoria, E/S) se denomina bus del sistema (system bus).

Un bus es un camino de comunicacin entre dos o mas dispositivos. Una caracterstica clave de un bus es que trata de un medio de transmisin compartido. Al bus se conectan varios dispositivos y cualquier seal transmitida por uno de esos dispositivos est disponible para que los otros dispositivos conectados al bus puedan acceder a ella. Si dos dispositivos transmiten durante el mismo periodo de tiempo, sus seales pueden solaparse y distorsionarse. Solamente un dispositivo puede transmitir con xito en un momento dado.

1.2.4.2 Estructura de los buses

El bus del sistema est constituido, usualmente por entre 50 y 100 lneas. A cada lnea se le asigna un significado o una funcin particular. Las lneas se pueden clasificar en tres grupos funcionales:

Las lneas de datos proporcionan un camino para transmitir datos entre los mdulos del sistema. El conjunto constituido por estas lneas se denomina bus de datos. El bus de datos puede incluir entre 32 y cientos de lneas, cuyo numero se conoce como anchura del bus de datos. Puesto que cada lnea solo puede transportar un bit cada vez, el numero de lneas determina cuantos bits se pueden transferir al mismo tiempo.

Las lneas de direccin se utilizan para designar la fuente o el destino del dato situado en el bus de datos. La anchura del bus de direcciones determina la mxima capacidad de memoria posible en el sistema. Adems, las lneas de direcciones generalmente se utilizan tambin para direccionar los puertos de E/S.

Las lneas de control se utilizan para controlar el acceso y el uso de las lneas de datos y de direcciones. Las seales de control transmiten tanto ordenes como informacin de temporizacin entre los mdulos del sistema. Las seales de temporizacin indican la validez de los datos y las direcciones. Las seales de ordenes especifican las operaciones a realizar. Clasificacin de lneas de control

Escritura en memoria: hace que el dato del bus se escriba en la posicin direccionada.

Lectura de memoria: hace que el dato de la posicin direccionada se situ en el bus.

Escritura de E/S: hace que el dato del bus se transfiera a travs del puerto de E/S direccionado.

Lectura de E/S: hace que el dato del puerto de E/S direccionado se site en el bus.

Transferencia reconocida: indica que el dato se ha aceptado o se ha situado en el bus.

Peticin del bus: indica que un modulo necesita disponer del control del bus.

Cesin del bus: indica que se cede el control del bus a un modulo que lo haba solicitado.

Peticin de interrupcin: indica si hay una interrupcin pendiente. Interrupcin reconocida: seala que la interrupcin pendiente se ha aceptado.

1.2.4.3 Jerarquas de buses

El bus local entre el procesador y la cache asla el trfico de E/S del procesador: se puede transferir informacin entre la memoria y la E/S sin interrumpir la actividad del procesador. El bus de expansin reduce el trfico en el bus del sistema:

La transferencia entre cache y memoria principal se pueden realizar de forma ms eficiente.

Se pueden realizar una transferencia de memoria cache a memoria principal al mismo tiempo que el interfaz recibe datos desde un dispositivo de E/S.

El procesador + cache o el coprocesador tienen la misma prioridad en el acceso al bus que todos los dispositivos conectados al bus de expansin de forma conjunta.

Se elimina el problema de la incompatibilidad:

El bus local y del sistema suelen ser propietarios (no estndar) y estn optimizados para cada arquitectura particular

Los buses de expansin son buses estndares o abiertos (ISA, EISA, PCI, VME, etc.).

1.2.5. Interrupciones

Todos los computadores disponen de un mecanismo mediante el que otros mdulos (E/S, memoria) pueden interrumpir el procesamiento normal de la CPU.

Clases de interrupciones:

Programa: generadas por alguna condicin que se produce como resultado de la ejecucin de una instruccin, tal como desbordamiento aritmtico (overflow) divisin por cero, intento de ejecutar una instruccin maquina inexistente e intento de acceder fuera del espacio de memoria permitido para el usuario.

Temporizacin: generadas por un temporizador interno al procesador. Esto permite al sistema operativo realizar ciertas funciones de manera regular.

E/S: generadas por un controlador de E/S, para indicar la finalizacin sin problemas de una operacin o para avisar de ciertas condiciones de error.

Fallo de hardware: generadas por un fallo tal como la falta de potencia de alimentacin o un error de paridad en la memoria.

Con el uso de interrupciones, el procesador puede dedicarse a ejecutar otras instrucciones mientras una operacin de E/S esta en curso.

Para permitir el uso de interrupciones, se aade un ciclo de interrupcin al ciclo de instruccin. En el ciclo de interrupcin, el procesador comprueba si se ha generado alguna interrupcin, indicada por la presencia una seal de interrupcin. Si no hay seales de interrupcin pendientes, el procesador continua con el ciclo de captacin y accede a la siguiente instruccin del programa en curso. Si hay alguna interrupcin pendiente, el procesador hace lo siguiente:

1.Suspende la ejecucin del programa en curso y guarda su contexto. Esto significa almacenar la direccin de la siguiente instruccin a ejecutar y cualquier otro dato relacionado con la actividad en curso del procesador.

2.Carga el contador de programa con la direccin de comienzo de una rutina de gestin de interrupcin.

Potrebbero piacerti anche

- APEX Learner Guide EspDocumento17 pagineAPEX Learner Guide EspUniP IngenierNessuna valutazione finora

- Aprendephpconejercicios Sample PDFDocumento14 pagineAprendephpconejercicios Sample PDFIestp ChongoyapeNessuna valutazione finora

- Base de Datos Avanzado IDocumento206 pagineBase de Datos Avanzado IMiguel Angel FernandezNessuna valutazione finora

- Fundamentos CA y CCDocumento56 pagineFundamentos CA y CCTorres Anaya Luis Daniel100% (1)

- SALTOS CICLOS ENSAMBLADORDocumento9 pagineSALTOS CICLOS ENSAMBLADORGabriela Guzmán Rosas100% (1)

- Tipos de Arquitectura de PCDocumento41 pagineTipos de Arquitectura de PCJeffrey De La Cruz100% (1)

- Unidad IDocumento278 pagineUnidad ICaraveo PorfirioNessuna valutazione finora

- ETL SQL Server 2019 Caso Ventas GourmetDocumento288 pagineETL SQL Server 2019 Caso Ventas GourmetErnestoSantaMaríaNessuna valutazione finora

- Educación Inclusiva - Módulo 2 - DiseñadoDocumento23 pagineEducación Inclusiva - Módulo 2 - DiseñadoClaudia Acosta100% (1)

- Tema 1 Fundamentos de Un Circuito EléctricoDocumento72 pagineTema 1 Fundamentos de Un Circuito EléctricogokuNessuna valutazione finora

- Energía ElectrostáticaDocumento12 pagineEnergía ElectrostáticaJuan perezNessuna valutazione finora

- Preguntas múltiples sobre conceptos informáticosDocumento2 paginePreguntas múltiples sobre conceptos informáticosJasiel MolinaNessuna valutazione finora

- Impacto de Las Normas en Gestion Energeticas NADIA PAOLA ALTAMIRANODocumento39 pagineImpacto de Las Normas en Gestion Energeticas NADIA PAOLA ALTAMIRANONadia Paola Altamirano Ordaz100% (1)

- Actividad1 - Arquitectura de ComputadorasDocumento7 pagineActividad1 - Arquitectura de Computadorasedgar jafet murillo silvaNessuna valutazione finora

- Tarea-1 Arquitectura de ComputadorasDocumento6 pagineTarea-1 Arquitectura de ComputadorasGinoNessuna valutazione finora

- Arquitecturas de ComputoDocumento34 pagineArquitecturas de ComputoStephanie Martinez100% (1)

- Arquitectura de Computadoras IDocumento35 pagineArquitectura de Computadoras IJorge Díaz Ordás100% (1)

- Manual de Prácticas Principios Eléctricos 2015.Documento53 pagineManual de Prácticas Principios Eléctricos 2015.JuanCarlosMontalvoPerezNessuna valutazione finora

- Arquitectura de ComputadorasDocumento53 pagineArquitectura de Computadorastilsma100% (3)

- Modelos de Arquitectura de Computo Equipo 3Documento11 pagineModelos de Arquitectura de Computo Equipo 3Jorge Alberto Jimenez Rosales100% (1)

- Principios Electrónicos Cuestionario 1Documento3 paginePrincipios Electrónicos Cuestionario 1Jesús David Valdivia Ríos100% (1)

- Lenguaje EnsambladorDocumento18 pagineLenguaje EnsambladorAdrian VegaNessuna valutazione finora

- Formulación de La Politica EnergeticaDocumento18 pagineFormulación de La Politica EnergeticaPABLO ROMERO VALDEZ100% (1)

- Unidad I Introducción Al Lenguaje EnsambladorDocumento125 pagineUnidad I Introducción Al Lenguaje EnsambladorOmar RamosNessuna valutazione finora

- Lenguaje de Interfaz - TemasDocumento91 pagineLenguaje de Interfaz - TemasCarlos Cruz80% (5)

- Circuitos eléctricos básicosDocumento12 pagineCircuitos eléctricos básicosIvana SegoviaNessuna valutazione finora

- Niveles de máquina, ciclo de instrucción y modelo de Von NeumannDocumento30 pagineNiveles de máquina, ciclo de instrucción y modelo de Von NeumannDaniel RioNessuna valutazione finora

- LYA T5 Resumen Tema 5Documento19 pagineLYA T5 Resumen Tema 5Jorge Alberto Jimenez RosalesNessuna valutazione finora

- Principios Electricos ManualDocumento94 paginePrincipios Electricos ManualAlejandro Emmanuel MercantilNessuna valutazione finora

- SensoresDocumento48 pagineSensoresSANTOS100% (1)

- 2.1 Ensamblador y Ligado A UtilizarDocumento3 pagine2.1 Ensamblador y Ligado A UtilizarJerzain CarrilloNessuna valutazione finora

- Fundamentos Basicos ElectronicaDocumento5 pagineFundamentos Basicos ElectronicaDillis Yordan Gomez Larez100% (1)

- Proceso de Ensamblado y LigadoDocumento14 pagineProceso de Ensamblado y LigadoGraciela Lo'GsNessuna valutazione finora

- EstaticaDocumento0 pagineEstaticaRicardo AimóNessuna valutazione finora

- Arquitectura de Computadoras Unidad I - Otoño 2021Documento42 pagineArquitectura de Computadoras Unidad I - Otoño 2021rafaelNessuna valutazione finora

- 0.2. Principios EléctricosDocumento56 pagine0.2. Principios EléctricosChema SaizNessuna valutazione finora

- Tecnologia Risc y CiscDocumento5 pagineTecnologia Risc y CiscSonia CordovaNessuna valutazione finora

- Ensamblador y Ligador A UtilizarDocumento3 pagineEnsamblador y Ligador A UtilizarJesus Alberto Bonilla Ramos100% (1)

- UNIDAD 1 SensoresDocumento11 pagineUNIDAD 1 SensoresDonald Kurt100% (1)

- Infografia Modelo Von NeumannDocumento1 paginaInfografia Modelo Von NeumannDulce Maria Perez GrijalvaNessuna valutazione finora

- Arquitectura de Computadores - Cuestionario ResueltoDocumento3 pagineArquitectura de Computadores - Cuestionario ResueltoJuanPabloValdiviesoMosqueraNessuna valutazione finora

- Interrupciones EnsambladorDocumento18 pagineInterrupciones EnsambladorViridiana MoNessuna valutazione finora

- Circuito en Serie y ParaleloDocumento6 pagineCircuito en Serie y ParaleloDiego JamiNessuna valutazione finora

- VrmsDocumento4 pagineVrmsJose Manuel Herrera OsorioNessuna valutazione finora

- Mediciones de Voltaje Corriente y Resistencias EléctricaDocumento8 pagineMediciones de Voltaje Corriente y Resistencias EléctricaEinar PérezNessuna valutazione finora

- Manual de Prácticas Arquitectura de ComputadorasDocumento74 pagineManual de Prácticas Arquitectura de ComputadorasTanni DiazNessuna valutazione finora

- Cuestionario Unidad 1Documento4 pagineCuestionario Unidad 1Enrique MartinezNessuna valutazione finora

- Procesadores IntelDocumento22 pagineProcesadores IntelSilvia Maza NimaNessuna valutazione finora

- Modos de Direccionamiento en EnsambladorDocumento17 pagineModos de Direccionamiento en EnsambladorRene Zahori Torres BecerraNessuna valutazione finora

- Arquitectura Del Computador - Memoria RamDocumento44 pagineArquitectura Del Computador - Memoria RamLuis Angel Manrique JulcaNessuna valutazione finora

- SISTEMAS PROGRAMABLES (Sensores Opticos)Documento4 pagineSISTEMAS PROGRAMABLES (Sensores Opticos)alberto michelNessuna valutazione finora

- Ley de OhmDocumento3 pagineLey de OhmCarlosChirinos100% (1)

- Lenguajes de InterfazDocumento8 pagineLenguajes de Interfazmalameda73Nessuna valutazione finora

- Energía potencial electrostática y capacitanciaDocumento49 pagineEnergía potencial electrostática y capacitanciaAngel Granados100% (1)

- Iso 9000Documento49 pagineIso 9000emiliroheNessuna valutazione finora

- LEY DE OHM (Georg Simon Ohm)Documento4 pagineLEY DE OHM (Georg Simon Ohm)Rod AngiieNessuna valutazione finora

- Examen de Arquitectura de Computadoras 3er ParcialDocumento3 pagineExamen de Arquitectura de Computadoras 3er ParcialNimzay NavarreteNessuna valutazione finora

- Máxima potencia transferenciaDocumento12 pagineMáxima potencia transferenciacristhianNessuna valutazione finora

- Unidad IDocumento14 pagineUnidad IEsteban JiménezNessuna valutazione finora

- Lenguaje EnsambladorDocumento25 pagineLenguaje EnsambladorJhonnySanchezNessuna valutazione finora

- UNIDAD - 1.introducción e Instalación de Los SODocumento87 pagineUNIDAD - 1.introducción e Instalación de Los SOLuis AlfredoNessuna valutazione finora

- Arquitectura de ComputadorasDocumento47 pagineArquitectura de ComputadorasRigoberto He HeNessuna valutazione finora

- 04) Fraga, M. (1997)Documento14 pagine04) Fraga, M. (1997)Julio César Sosa YeladaquiNessuna valutazione finora

- Antologia de Arquitectura de ComputadorasDocumento95 pagineAntologia de Arquitectura de ComputadorasCésar Vicente Morales Morales100% (1)

- EjemploDocumento2 pagineEjemploMaljolys BaezNessuna valutazione finora

- Qué Significa Red LANDocumento1 paginaQué Significa Red LANRosario Ramírez RiosNessuna valutazione finora

- SQL Lenguaje de Estructura de ConsultaDocumento2 pagineSQL Lenguaje de Estructura de ConsultaRosario Ramírez RiosNessuna valutazione finora

- Programacin en MvilesviejoDocumento7 pagineProgramacin en MvilesviejoChayto JimenezNessuna valutazione finora

- 15 Guia de Estudio InforDocumento14 pagine15 Guia de Estudio InforJean Baptiste LamarckNessuna valutazione finora

- SQL Lenguaje de Estructura de ConsultaDocumento2 pagineSQL Lenguaje de Estructura de ConsultaRosario Ramírez RiosNessuna valutazione finora

- Qué Es CMMIDocumento4 pagineQué Es CMMIRosario Ramírez RiosNessuna valutazione finora

- Qué Significa Red LANDocumento1 paginaQué Significa Red LANRosario Ramírez RiosNessuna valutazione finora

- Contrato Privado de CompraventaDocumento4 pagineContrato Privado de CompraventaEric Carranza GonzalezNessuna valutazione finora

- COCOMO para DAKYD en PHP con 6 mesesDocumento2 pagineCOCOMO para DAKYD en PHP con 6 mesesRosario Ramírez RiosNessuna valutazione finora

- ItzelDocumento1 paginaItzelRosario Ramírez RiosNessuna valutazione finora

- Adm BD Isc10Documento13 pagineAdm BD Isc10Leonardo Herrera RomeroNessuna valutazione finora

- Gestor de Base de DatosDocumento41 pagineGestor de Base de DatosjuamatestNessuna valutazione finora

- R 86197Documento3 pagineR 86197Rosario Ramírez RiosNessuna valutazione finora

- Modelo RelacionalDocumento19 pagineModelo RelacionalRosario Ramírez RiosNessuna valutazione finora

- Problemas AritmeticosDocumento4 pagineProblemas AritmeticosRosario Ramírez RiosNessuna valutazione finora

- Exa Sec 03 2010Documento56 pagineExa Sec 03 2010Cesar FloresNessuna valutazione finora

- Sesion10 - Operadores de Cadena y ComparacionDocumento6 pagineSesion10 - Operadores de Cadena y ComparacionNearNessuna valutazione finora

- Modelo ER-40Documento2 pagineModelo ER-40Alejandro Daniel SanabriaNessuna valutazione finora

- Repaso para Base de Datos 2Documento9 pagineRepaso para Base de Datos 2Jose Agustin Torres BaezNessuna valutazione finora

- Redes de Computadoras - Natalia OliferDocumento2 pagineRedes de Computadoras - Natalia OliferchatopradaNessuna valutazione finora

- 2.5.5 Packet Tracer - Configure Initial Switch Settings - Luis Andres RamosDocumento21 pagine2.5.5 Packet Tracer - Configure Initial Switch Settings - Luis Andres Ramosluis andres ramos100% (1)

- Evolucion Ansi SQLDocumento4 pagineEvolucion Ansi SQLGiovanniHernandezCastillo100% (1)

- Diagrama ER HospitalDocumento9 pagineDiagrama ER HospitalVictor FraideNessuna valutazione finora

- Listado DAHUA IP - WiFi Enero 2021Documento15 pagineListado DAHUA IP - WiFi Enero 2021rayNessuna valutazione finora

- Reporte de Practicas ProfesionalesDocumento28 pagineReporte de Practicas ProfesionalesSergio SchnaiderNessuna valutazione finora

- Manual SNMPDocumento9 pagineManual SNMPchavarryaNessuna valutazione finora

- SMBDDocumento83 pagineSMBDapi-3800751100% (1)

- Tutorial OpencvDocumento4 pagineTutorial OpencvCésar MartínezNessuna valutazione finora

- Listas de Control de AccesoDocumento20 pagineListas de Control de AccesoRoy Fernando Chavarría MoraNessuna valutazione finora

- Informe Procedimientos AlmacenadosDocumento20 pagineInforme Procedimientos AlmacenadosRamón Vázquez ToledoNessuna valutazione finora

- Placa Base Manual UsuarioDocumento30 paginePlaca Base Manual UsuarioFercho D. O. UranNessuna valutazione finora

- Ejercicios Seccion 3.3Documento19 pagineEjercicios Seccion 3.3Christian DiazNessuna valutazione finora

- Redes de Computadoras II (CI-5832)Documento2 pagineRedes de Computadoras II (CI-5832)CORAL ALONSO JIMÉNEZNessuna valutazione finora

- Cuadros ComparativosDocumento7 pagineCuadros Comparativoslmiguel12Nessuna valutazione finora

- Clúster de Servidores Con PostgreSQLDocumento31 pagineClúster de Servidores Con PostgreSQLjr.camacho.1982Nessuna valutazione finora

- Informe de Tipos de JoinDocumento20 pagineInforme de Tipos de JoinJonathan Correa ChavezNessuna valutazione finora

- Instalación y Configuración de Windows Server 2016Documento11 pagineInstalación y Configuración de Windows Server 2016GRUPO LA CATOLICANessuna valutazione finora

- pa-gestion-bd-procedimientosDocumento4 paginepa-gestion-bd-procedimientosEstefany CarranzaNessuna valutazione finora

- Examen Final Informatica e InternetDocumento4 pagineExamen Final Informatica e InternetGabriel Rodriguez MinayaNessuna valutazione finora

- Ejemplos de CRC de Ingenieria de SoftwareDocumento9 pagineEjemplos de CRC de Ingenieria de SoftwareFranciscoFloresNessuna valutazione finora

- 9.1 Tablespaces y Datafiles Inicial PDFDocumento4 pagine9.1 Tablespaces y Datafiles Inicial PDFAriel Yapari HuayllaniNessuna valutazione finora

- ABEND Code Causas y SolucionesDocumento3 pagineABEND Code Causas y Solucionesluis_programacionNessuna valutazione finora

- Informe FoxProDocumento36 pagineInforme FoxProGuillermo González Murillo100% (1)

- Futuro de Las Bases de DatosDocumento15 pagineFuturo de Las Bases de DatosSheilla Lin Morales MercadoNessuna valutazione finora