Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Fuzzy Logic Control For Single Phase Multilevel Inverter

Caricato da

Mohan KumarTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Fuzzy Logic Control For Single Phase Multilevel Inverter

Caricato da

Mohan KumarCopyright:

Formati disponibili

1

FUZZY LOGIC CONTROL FOR SINGLE PHASE MULTILEVEL INVERTER

Shanthi B.

Reader, Centralised Instrumentation and Service Laboratory, Annamalai University,

Annamalainagar, Chidambaram, Tamilnadu, India

aushanyahoo.com

Natarajan S.P.

ProIessor and Head, Department oI Instrumentation Engineering, Annamalai University,

Annamalainagar, Chidambaram, Tamilnadu, India

spnannamalairediIImail.com

Anbukodi S.P.

P.G. Student, Department oI Instrumentation Engineering, Annamalai University,

Annamalainagar, Chidambaram, Tamilnadu, India

Abstract : A single phase cascaded inverter consisting of two full

bridges creates a five level AC output voltage. Due to switch

combination redundancies, there are certain degrees of freedom

to generate the five level AC output voltage. A single phase Pulse

Width Modulation (PWM) Multil Level Inverter (MLI) produces

AC output voltage of desired magnitude and frequencv. The

purpose of voltage controller for the inverter is to produce

regulated output voltage with low distortion under all loading

conditions. A Fu::v Logic Controller (FLC) isdeveloped using

Matlab-Simulink for the chosen inverter having application in

Uninterruptible Power Supplies (UPSs). For comparison

purposes, a PI controller is also developed. The results are

presented and evaluated. FLC is found to have better

performance.

Key words: MLI, PWM, PI control, fu::v logic control.

1. Introduction

The general requirement oI inverter system Ior high

power AC power supply application is to maintain high

quality output voltage with Total Harmonic Distortion

(THD) typically speciIied to be less than 5 at a Iixed

Irequency regardless oI the loading condition |1|.

Multilevel inverter has drawn tremendous interest in high

power applications because it has many advantages: it can

realize high voltage and high power output through the use

oI semiconductor switches without use oI transIormer and

without dynamic voltage balance circuits. When the

number oI output levels increases, harmonics oI the output

voltage and current as well as Electro Magnetic

InterIerence (EMI) decrease. The main Ieature oI a MLI is

its ability to reduce the voltage stress on each power

device due to utilisation oI multiple levels on the DC bus.

In |1| and |2|, Fuzzy Proportional Integral Control (FPIC)

is proposed to replace the conventional linear PI controller

employed in the on line optimal PWM control scheme

presented in |3|-|5|. Development oI a DSP-based Iuzzy

PI controller Ior an optimal PWM control scheme Ior MLI

is presented in |6|. Three PWM methods with diIIerent

vertical and horizontal oIIset combinations are

investigated in |7|-|9| leading to the quantiIication oI their

output harmonics. Multilevel PWM methods based on

control degrees oI Ireedom combination and their

theoretical analysis are discussed in |10|.

Since above survey oI literature reports little work on

intelligent control Ior MLIs, an attempt is made in this

work to develop Iuzzy controllers Ior the chosen inverter.

The simulation results are presented and analysed with PI

controller developed.

2. Multilevel Inverter

Multilevel inverters are being considered Ior an

increasing number oI applications due to their high power

capability associated with lower output harmonics and

lower commutation losses. There are several types oI

multilevel inverters but the one considered in this work is

the Modular Structured Multilevel Inverter (MSMI).

Multilevel inverters have become an eIIective and

practical solution Ior increasing power and reducing

harmonics oI AC load. Fig.1 shows a single phase Iive

level conIiguration oI the MSMI. The MSMI is unique

when compared to other types oI multilevel inverters in

the sense that it consists oI several modules that require

separate DC sources. Compared to other types oI

multilevel inverters, the MSMI requires less number oI

components with no extra clamping diodes or voltage

balancing capacitors that only Iurther complicate the

overall inverter operation. As can be seen Irom Fig. 1,

each module oI the MSMI has the same structure whereby

it is represented by a single phase Iull-bridge inverter. This

simple modular structure not only allows practically

2

unlimited number oI levels Ior the MSMI by stacking up

the modules but also Iacilitates its packaging.

Fig.1. Five Level MSMI.

The operation oI the MSMI can be easily understood

whereby the load voltage is equal to the summation oI the

output voltage oI the respective modules that are

connected in series. The number oI modules (M) which is

equal to the number oI DC sources required depends on

the total number oI positive, negative and zero levels (m)

oI the MSMI. It is usually assumed that m is odd as this

would give an integer valued M which would simpliIy

Iurther analysis. In this work, load voltage consists oI Iive

levels which include 2V

DC

, V

DC

, 0, - V

DC

and -2V

DC

and the number oI modules needed is 2. The Iollowing

equation gives the relationship between M and m:

M(m-1)/2

3. Modulation Strategies for Multilevel Inverter

A number oI modulation strategies are used in

multilevel power conversion applications. They can

generally be classiIied into three categories:

Multistep, staircase or Iundamental Irequency

switching strategies

Space Vector PWM strategies

Carrier based PWM strategies

OI all the PWM methods Ior cascaded multilevel

inverter, carrier based PWM methods and space vector

methods are oIten used but when the number oI output

levels is more than Iive, the space vector method will be

very complicated with the increase oI switching states. So

the carrier based PWM method is preIerred under this

condition in multilevel inverters. This paper Iocuses on

carrier based PWM techniques which have been extended

Ior use in multilevel inverter topologies by using multiple

carriers.

Multilevel carrier based PWM methods have more than

one carrier that can be triangular waves or sawtooth waves

and so on. The modulating/ reIerence wave oI multilevel

carrier based PWM method can be sinusoidal or

trapezoidal. This paper presents the Carrier Overlapping

PWM (COPWM) method that utilizes the vertical oIIsets

among carriers.

3.1. COPWM Strategy

For an m-level inverter using carrier overlapping

technique, m-1 carriers with the same Irequency I

c

and

same peak-to-peak amplitude A

c

are disposed such that the

bands they occupy overlap each other; the overlapping

vertical distance between each carrier is A

c

/2. The

reIerence waveIorm has amplitude oI A

m

and Irequency oI

I

m

and it is centered in the middle oI the carrier signals.

The reIerence wave is continuously compared with each oI

the carrier signals. II the reIerence wave is more than a

carrier signal, then the active devices corresponding to that

carrier are switched on. Otherwise, the devices switch oII.

The amplitude modulation index m

a

and the Irequency

ratio m

I

are deIined in the carrier overlapping method as

Iollows:

m

a

A

m

/((m/4)* A

c

)

m

f

f

c

/ f

m

The vertical oIIset oI carriers Ior Iive level inverter

with COPWM method is illustrated in Fig.2. Table 1

provides details about chosen inverter.

Fig. 2. Carrier arrangement Ior COPWM strategy.

Fig. 3. Five level output voltage generated by COPWM

strategy.

The gate signals Ior chosen Iive level cascaded inverter

are developed using MATLAB-SIMULINK. The gate

signal generator model developed is tested Ior various

values oI modulation index. The results oI the open loop

simulation study are obtained in this work in the Iorm oI

the PWM outputs oI the chosen multilevel inverter and

Fig.3 shows a sample output Ior only one value oI m

a

0.8.

3

The THD and Vrms are evaluated Ior Iive level output

using COPWM strategy and presented as in Table 2. A

non-overlapping Sub-Harmonic PWM (SHPWM) strategy

is also presented in this work Ior comparison purposes

(Table 2).

Table 1 Inverter parameters

Parameter Value Unit

Switching Irequency, I

s

2 KHz

DC source voltage, V

dc

100 V

Rated output voltage 300 V

p-p

Rated output Irequency 50 Hz

Rated output current 30 A

p-p

Rated load (linear) 10 O

Filter inductor, L

I

1 mH

Filter capacitor, C

I

2.2 mF

Table 2 THD and V

rms

Ior diIIerent modulation indices

SHPWM COPWM m

a

THD Vrms (V) THD Vrms (V)

1.0 7.7 141.4 12.9 150.16

0.9 7.35 127.3 10.39 141.7

0.8 8.5 113.1 7.84 131.2

0.7 9.7 98.98 5.72 119.8

0.6 11 84.84 4.28 106.9

0.5 -- -- 3.79 88.36

0.4 -- -- 5.10 75.1

0.3 -- -- 6.74 53.1

The closed loop control is perIormed (as presented in

the next two sections) using the COPWM switching

strategy because it gives the minimum THD Ior low and

medium modulation indices (Table 2).

4. PI Control

Today diIIerent controllers are used in industry and in

many other Iields. They are divided into two main groups:

i) conventional controllers ii) non-conventional controllers.

PI controllers belong to the Iormer category whereas Iuzzy

controller belong to latter. Inverter control reIers to

speciIying the desired nominal operating point and then

regulating the inverter so that it stays close to the nominal

operating point in the presence oI disturbances and noise.

PI controller settings Kp and Ki are designed in this work

using Ziegler Nichols tuning technique. The designed

values oI Kp and Ki are 0.0125 and 1 sec

-1

respectively.

5. Fuzzy Logic Control

Fuzzy logic control uses non-mathematical decision

based algorithms that use operators` experiences. This type

oI control strategy is well suited Ior non-linear systems.

Fuzzy logic control is developed in this work to obtain

desired output voltage oI the chosen inverter. In order to

obtain the Iuzzy control surIace Ior non-linear, time-

varying and complex dynamic systems, there are a number

oI steps to be Iollowed as discussed below. The block

diagram oI Iuzzy logic control scheme developed Ior the

chosen single phase PWM inverter is shown in Fig.4. The

FLC is divided into Iive modules: IuzziIier, database, rule

base, decision maker and deIuzziIier. The computational

structure oI Iuzzy logic control scheme is composed oI the

Iollowing:

5.1. Identification of Inputs and Output

The inputs to the FLC are the error e V

reI

V

o

and

the change in error ce e

n

e

n-1

where V

o

is the actual

output voltage oI the MLI, V

reI

is the desired output

voltage and subscript n denotes sampling instances. m

n

is

the change oI modulation index inIerred by the FLC at the

n

th

sampling instant. Using om

n

, the updated modulated

signal m

s

is obtained and Ied to the SPWM generator

which provides appropriate PWM signals m

n

.

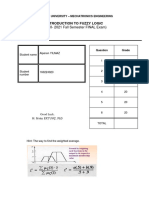

5.2. Fuzzification of Inputs

The crisp input values oI e and ce are to be IuzziIied

and sevent riangular membership Iunctions (Fig.5 ) are

chosen in this work Ior simplicity.

Fig. 4. Fuzzy logic control scheme Ior chosen single

phase PWM inverter.

5.3. Rule Table and Inference Mechanism

The Iuzzy rules are in the Iorm

R

i

: II e is A

i

and ce is B

i

then m

n

is C

i

where A

i

, B

i

and C

i

are Iuzzy subsets in their universe oI

discourse. Each universe oI discourse is divided into seven

Iuzzy subsets namely PB (Positive Big), PM (Positive

Medium), PS (Positive Small), ZE (Zero), NS (Negative

Small), NM (Negative Medium) and NB (Negative Big) as

shown in Figs.5 and 6. The values oI e and ce are

normalised to |-1, 1| as in Fig.5 and values oI m

n

have

the range |-1, 1| as in Fig.6. For any combination oI e and

ce, a maximum oI Iour rules are adopted.

4

Fig.5. Membership Iunctions Ior e and ce.

Fig.6. Membership Iunctions Ior change in modulation

Index.

The derivation oI Iuzzy control rules Ior chosen

inverter is heuristic in nature and is based on the Iollowing

criteria:

i. When the output oI the inverter deviates Iar Irom

the reIerence, the change oI modulation index

must be large so as to bring the output to the

reIerence quickly.

ii. When the output oI the inverter is approaching

the reIerence, a small change oI modulation index

is necessary.

iii. When the output oI the inverter is near the

reIerence and is approaching it rapidly, the

modulation index must be kept constant so as to

prevent Iurther deviation.

iv. When the reIerence is reached and the output is

still changing, the modulation index must be

changed a little bit to prevent the output Irom

moving away.

v. When the reIerence is reached and the output is

steady, the modulation index remains unchanged.

vi. When the output is larger than the reIerence, the

sign oI the change oI modulation index must be

negative and vice versa.

According to these criteria, a rule base is derived as in

Table 3.

Table 3 Rule base

e\ce NB NM NS ZE PS PM PB

NB NB NB NB NB NM NS ZE

NM NB NB NB NM NS ZE PS

NS NB NB NM NS ZE PS PM

ZE NB NM NS ZE PS PM PB

PS NM NS ZE PS PM PB PB

PM NS ZE PS PM PB PB PB

PB ZE PS PM PB PB PB PB

The inIerence result oI each rule consists oI two parts,

the weighting Iactor w

i

oI the individual rule and the

degree oI change oI modulation index C

i

according to the

rule and it is written as

:

i

min {

e

(e)

,

ce

(ce) }. C

i

w

i

C

i

where z

i

denotes the change in modulation index inIerred

by the i

th

rule and C

i

is looked up Irom the rule table which

shows the mapping Irom the product space oI e and ce to

C

i

.

5.4. Defuzzification

The deIuzziIication is carried out in this work using the

bisector oI area method.

6. Simulation Results

The cascaded Iive level inverter is modelled in

SIMULINK using Power system block set. Switching

signals Ior cascaded multilevel inverter using SHPWM

and COPWM techniques are simulated using the gate

signal generator model developed. Open loop simulations

are perIormed Ior diIIerent values oI m

a

ranging Irom

0.3 1.0 and the corresponding THD and V

rms

are

evaluated using the FFT block and their values are shown

in Table 2. SHPWM produces three level output only

when m

a

is less than 0. 6.

Fig.7 shows the simulated closed loop dynamic

responses oI load voltage and load current oI PI controlled

inverter when the load changes Irom Iull load (10) to no

load (10k) suddenly at t0. 3 45secs. Fig.8 shows the

corresponding simulated dynamic responses with Iuzzy

controller. Figs. 9 and 10 display the simulated dynamic

responses oI load voltage and load current oI chosen

inverter when the load changes Irom noload (10 k) to

Iull load (10) suddenly at t0.345secs with PI and Iuzzy

controllers. The next two Iigures display the corresponding

steady-state responses Ior a resistive load. Table 4 and Figs.

13 to 18 provide the comparison oI THD Ior the PI and

Iuzzy controllers Ior the chosen inverter.

5

Fig.7. Transient responses oI the MLI with PI control.

Fig.8. Transient responses oI MLI with Iuzzy control.

Fig.9. Transient responses oI the MLI with PI control.

Fig.10. Transient responses oI the MLI with Iuzzy

control.

Fig.11. Steady-state responses oI the MLI with PI

Control.

Fig.12. Steady-state responses oI the MLI with Iuzzy

control.

Fig. 13. FFT Plot Ior PI control - load voltage

sudden load change(10 -10k).

Fig.14. FFT Plot Ior Iuzzy control - load voltage

sudden load change(10 -10k).

.

6

Fig. 15. FFT Plot Ior PI control - load voltage

sudden load change(10k -10).

Fig. 16. FFT Plot Ior Iuzzy control - load voltage

sudden load change(10 k -10).

Fig. 17. FFT Plot Ior PI control - load voltage 10 load.

Fig. 18.FFT Plot Ior Iuzzy control -load voltage 10 load.

7. Conclusion

The PI and Iuzzy controllers developed have been

tested through simulation Ior regulating output voltage and

minimising the harmonics oI the chosen cascaded Iive

level inverter. The closed loop responses oI the inverter

have been obtained under diIIerent loading conditions such

as sudden change Irom no load to Iull load and vice versa.

The simulation results (Table 4) show that the inverter

with Iuzzy control has minimum amount oI harmonics.

Table 4 Comparison oI THD Ior diIIerent loading

conditions

Load

PI Control Fuzzy Control

Steady State

R10O

0.88 0.75

Transient State

R10kO to 10O

0.95 0.59

Transient State

R 10O to 10kO

1.1 0.7

References

1. Azli N.A. and Ning W.S.: Application of Fu::v Logic in an

Optimal PWM based control Scheme for a Multilevel

Inverter. In: Proceedings oI the 2003 International

ConIerence on Power Electronics and Drive Systems PED

2003, Singapore, 17-20 November 2003, p. 1280 1285.

2. Azli N.A. and Ning W.S.: Application of Fu::v Logic in

Regulating a Multilevel Inverter output. In: Proceedings oI

2004 International ConIerence on Power System

Technolpgy, Singapore, 21-24 November 2004.

3. Azli N.A. and Yatim A.H.M.: Modular Structured Multilevel

Inverter (MSMI) for high power AC Power Supplv

Application. In: Proceedings oI the IEEE International

Symposium on Industrial Electronics ISIE`01, 2001, Vol.2,

p.728-733.

4. Azli N.A. and Yatim A.H.M.: A DSP-based Online Optimal

Pulse Width Modulation (PWM) Switching Strategies for a

Modular Structured Multilevel Inverter. In: Proceedings oI

the 6

th

International Symposium on Signal Processing and

its Application ISSPA`01, 2001, Vol.2, p.623-626.

5. Azli N.A. and Yatim A.H.M.: Optimal Pulse Width

Modulation (PWM) online Control of a Modular Structured

Multilevel Inverter (MSMI). In: Proceedings oI the 4

th

IEEE

International ConIerence on Power Electronics and Drive

Systems PEDS`01, 2001, Vol.2, p.598-604.

6. Azli N.A. and Wong S.N.: Development of a DSP-based

Fu::v PI Controller for an Online Optimal PWM Control

Scheme for a Multilevel Inverter. In: Proceedings oI IEEE

International ConIerence on Power Electronics and Drive

Systems PEDS`05, 2005, p.1457-1461.

7. Nabae A., Takahashi I., Akagi H.: A New Neutral-Point

Clamped PWM Inverter. In: IEEE Trans. Ind. Applicat.,

Sept/Oct.1981, Vol. IA-17, p. 518-523.

8. Lai J.S., Peng F.Z.: Multilevel Converters-A New Breed of

Power Converters. In: IEEE Trans. Ind. Applicat., May/June

1996, Vol. 32, p. 509-517.

9. Carrara G., Gardella S., Marchesoni M.,Salutari R., Sciutto

G..: A New Multilevel PWM Method. A Theoretical Analvsis.

In: IEEE Trans. Power Electron, July 1992, Vol. 7, p. 497

505.

10. Yan Deng, Hongyan Wang, Chao Zhang, Lei Hu, Xiangning

He.: Multilevel PWM Methods Based on Control Degrees of

Freedom Combination and its Theoretical Analvsis. In:

Proceedings oI the IEEE IAS 2005 ConIerence Record no.:

0-7803-9208-6/05, p. 1692 1699.

Potrebbero piacerti anche

- Simulation of Some Power System, Control System and Power Electronics Case Studies Using Matlab and PowerWorld SimulatorDa EverandSimulation of Some Power System, Control System and Power Electronics Case Studies Using Matlab and PowerWorld SimulatorNessuna valutazione finora

- Investigation of the Usefulness of the PowerWorld Simulator Program: Developed by "Glover, Overbye & Sarma" in the Solution of Power System ProblemsDa EverandInvestigation of the Usefulness of the PowerWorld Simulator Program: Developed by "Glover, Overbye & Sarma" in the Solution of Power System ProblemsNessuna valutazione finora

- Ijeet: International Journal of Electrical Engineering & Technology (Ijeet)Documento9 pagineIjeet: International Journal of Electrical Engineering & Technology (Ijeet)Koukou AmkoukouNessuna valutazione finora

- Improving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshDocumento5 pagineImproving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshsarathNessuna valutazione finora

- Mali 2019Documento7 pagineMali 2019aymenNessuna valutazione finora

- A Comparative Study of Various Multi-Level Inverter Based On Multi-CellDocumento4 pagineA Comparative Study of Various Multi-Level Inverter Based On Multi-CellTarak BenslimaneNessuna valutazione finora

- Selective Harmonic Elimination by Programmable Pulse Width Modulation in InvertersDocumento6 pagineSelective Harmonic Elimination by Programmable Pulse Width Modulation in InvertersseventhsensegroupNessuna valutazione finora

- Identification of Optimal SVPWM Technique For MLI Fed Induction Motor DriveDocumento6 pagineIdentification of Optimal SVPWM Technique For MLI Fed Induction Motor DriveManu ThomasNessuna valutazione finora

- MW Scas 2008Documento4 pagineMW Scas 2008pk27575Nessuna valutazione finora

- Simulation of Five Level Diode Clamped Multilevel InverterDocumento6 pagineSimulation of Five Level Diode Clamped Multilevel InverterEditor IJRITCCNessuna valutazione finora

- Single-Phase Five-Level Inverter With Less Number of Power Elements For Grid ConnectionDocumento7 pagineSingle-Phase Five-Level Inverter With Less Number of Power Elements For Grid Connectionvinay kumarNessuna valutazione finora

- Cascaded 5-Level Inverter Type Dstatcom For Power Quality ImprovementDocumento5 pagineCascaded 5-Level Inverter Type Dstatcom For Power Quality ImprovementSiri SarojaNessuna valutazione finora

- Design of Multi-Level Inverter and Its Application As Statcom To Compensate Voltage Sags Due To FaultsDocumento6 pagineDesign of Multi-Level Inverter and Its Application As Statcom To Compensate Voltage Sags Due To FaultsManpreet SinghNessuna valutazione finora

- Induction Motor Drive Using Seven Level Multilevel Inverter For Energy Saving in Variable Torque Load ApplicationDocumento8 pagineInduction Motor Drive Using Seven Level Multilevel Inverter For Energy Saving in Variable Torque Load ApplicationAnonymous 22GBLsme1Nessuna valutazione finora

- Single Phase PWM InverterDocumento11 pagineSingle Phase PWM InverterFoom A. Alshekh100% (2)

- 3 Phase Cascaded H-Bridge InverterDocumento7 pagine3 Phase Cascaded H-Bridge InverterAnil ShahNessuna valutazione finora

- Minimization of Total Harmonic Distortion Using Pulse Width TechniqueDocumento12 pagineMinimization of Total Harmonic Distortion Using Pulse Width TechniqueIOSRjournalNessuna valutazione finora

- A High-Performance Generalized Discontinuous PWM Algorithm: Ahmet M. Hava,, Russel J. Kerkman,, and Thomas A. LipoDocumento13 pagineA High-Performance Generalized Discontinuous PWM Algorithm: Ahmet M. Hava,, Russel J. Kerkman,, and Thomas A. LipoSherif M. DabourNessuna valutazione finora

- Advanced PWM Techniques For Control of Power Electronic Converters in PV and Motor Drive SystemsDocumento21 pagineAdvanced PWM Techniques For Control of Power Electronic Converters in PV and Motor Drive SystemsAman MalikNessuna valutazione finora

- THD Analysis of Cascaded Multi Level Inverters Using Different PWM TechniquesDocumento4 pagineTHD Analysis of Cascaded Multi Level Inverters Using Different PWM TechniquesEditor IJTSRDNessuna valutazione finora

- 25 - Sinusoidal Pulse Width Modulation (SPWM) With Variable Carrier PDFDocumento6 pagine25 - Sinusoidal Pulse Width Modulation (SPWM) With Variable Carrier PDFDevendra HoleyNessuna valutazione finora

- Multistring Five-Level Inverter With Novel PWMDocumento13 pagineMultistring Five-Level Inverter With Novel PWMsandeepbabu28Nessuna valutazione finora

- Development of Single SPWM Microcontroller-Based Inverter: A PhaseDocumento4 pagineDevelopment of Single SPWM Microcontroller-Based Inverter: A Phasemalini72Nessuna valutazione finora

- Design of Microcontroller Based Multilevel InverterDocumento4 pagineDesign of Microcontroller Based Multilevel InverterInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- An Optimized Three-Phase Multilevel Inverter Topology With Separate Level and Phase Sequence Generation PartDocumento26 pagineAn Optimized Three-Phase Multilevel Inverter Topology With Separate Level and Phase Sequence Generation PartNaga AnanthNessuna valutazione finora

- International Review of Applied Sciences and Engineering: 2. Structure of DCL Based Reversing Voltage Type MliDocumento1 paginaInternational Review of Applied Sciences and Engineering: 2. Structure of DCL Based Reversing Voltage Type MliManjunathBudagaviMatamNessuna valutazione finora

- Fuzzy Logic Controller Based On Voltage Source Converter-Hvdc SystemDocumento7 pagineFuzzy Logic Controller Based On Voltage Source Converter-Hvdc SystemBhuvneshRathoreNessuna valutazione finora

- Design of SPWM Based Three Phase Inverter Model: Tanuhsree Bhattacharjee Dr. Majid Jamil Dr. Anup JanaDocumento6 pagineDesign of SPWM Based Three Phase Inverter Model: Tanuhsree Bhattacharjee Dr. Majid Jamil Dr. Anup JanaandersonNessuna valutazione finora

- Analysis of Modulation Strategies For Switched Boost Multilevel Inverter With Embedded SourceDocumento12 pagineAnalysis of Modulation Strategies For Switched Boost Multilevel Inverter With Embedded SourceDavilNessuna valutazione finora

- Design and Simulation of an Inverter With High Frequency Sinusoidal PWM Switching Technique for Harmonic Reduction in a Standalone Utility Grid Harmonic Reduction in a Standalone Utility Grid Synchronized Photovoltaic SystemDocumento6 pagineDesign and Simulation of an Inverter With High Frequency Sinusoidal PWM Switching Technique for Harmonic Reduction in a Standalone Utility Grid Harmonic Reduction in a Standalone Utility Grid Synchronized Photovoltaic SystemS.m. FerdousNessuna valutazione finora

- A Study of Comparative Analysis of Different PWMDocumento6 pagineA Study of Comparative Analysis of Different PWMwilliam chaconNessuna valutazione finora

- Cascaded H-Bridge Multilevel Inverter For Induction Motor DrivesDocumento7 pagineCascaded H-Bridge Multilevel Inverter For Induction Motor DrivesesatjournalsNessuna valutazione finora

- Performance Analysis and Comparison of Conventional and Interleaved DC/DC Boost Converter Using MULTISMDocumento10 paginePerformance Analysis and Comparison of Conventional and Interleaved DC/DC Boost Converter Using MULTISMIam AbdiwaliNessuna valutazione finora

- Total Harmonic Distortion, Distortion Factor & Crest Factor in Sven Level Cascaded H-Bridge Inverter For Different PWM Control Strategies: A Comparative StudyDocumento14 pagineTotal Harmonic Distortion, Distortion Factor & Crest Factor in Sven Level Cascaded H-Bridge Inverter For Different PWM Control Strategies: A Comparative StudyabieNessuna valutazione finora

- An Effective Control Technique For Medium-Voltage High-Power Induction Motor Fed by Cascaded Neutral-Point-Clamped InverterDocumento10 pagineAn Effective Control Technique For Medium-Voltage High-Power Induction Motor Fed by Cascaded Neutral-Point-Clamped InverterRaviraj VishvakarmaNessuna valutazione finora

- Microcontroller Based Low Cost Controlled Rectifiers Training Module For Power Electronics LaboratoryDocumento4 pagineMicrocontroller Based Low Cost Controlled Rectifiers Training Module For Power Electronics LaboratoryJubari FikriNessuna valutazione finora

- 2013 A Simple Carrier-Based Modulation For The SVM of The Matrix ConverterDocumento10 pagine2013 A Simple Carrier-Based Modulation For The SVM of The Matrix ConverterTran Quoc HoanNessuna valutazione finora

- D EEPU05491634Documento4 pagineD EEPU05491634Deepu ChinnaNessuna valutazione finora

- Chapter 2 NewDocumento11 pagineChapter 2 NewKyaw SoeNessuna valutazione finora

- Simulation of Single Phase Inverter Using PSIM Software For Solar P.V. System Give Constant Output Voltage at Different Solar RadiationDocumento6 pagineSimulation of Single Phase Inverter Using PSIM Software For Solar P.V. System Give Constant Output Voltage at Different Solar Radiationkk_kamalakkannanNessuna valutazione finora

- Design and Development of 3 Phase PWM inDocumento4 pagineDesign and Development of 3 Phase PWM inMarc TcheukabaNessuna valutazione finora

- Design and Construction of Single Phase Pure Sine Wave Inverter For Photo Voltaic ApplicationDocumento4 pagineDesign and Construction of Single Phase Pure Sine Wave Inverter For Photo Voltaic ApplicationRafid Haider ShantonuNessuna valutazione finora

- InvertersDocumento8 pagineInvertersJeffrey A PobladorNessuna valutazione finora

- An Analysis On Switching Loss Optimized PWM Strategies For Three Phase PWM Voltage Source ConvertersDocumento6 pagineAn Analysis On Switching Loss Optimized PWM Strategies For Three Phase PWM Voltage Source ConvertersGanesh ChallaNessuna valutazione finora

- SPWM V/HZ InverterDocumento51 pagineSPWM V/HZ InverterLabi BajracharyaNessuna valutazione finora

- Seven Level InverterDocumento41 pagineSeven Level InverterAYONA THOMASNessuna valutazione finora

- IET-PEL - Modulation and Control of Multilevel Inverter For An Open-End Winding Induction Motor With Constant Voltage Levels and HarmonicsDocumento9 pagineIET-PEL - Modulation and Control of Multilevel Inverter For An Open-End Winding Induction Motor With Constant Voltage Levels and HarmonicsKartick JanaNessuna valutazione finora

- Practical-9: AIM: To Simulate PWM InverterDocumento5 paginePractical-9: AIM: To Simulate PWM InverterHardik PatoliyaNessuna valutazione finora

- Practical-9: AIM: To Simulate PWM InverterDocumento5 paginePractical-9: AIM: To Simulate PWM InverterHardik PatoliyaNessuna valutazione finora

- Technical LRDocumento23 pagineTechnical LRThesis IndiaNessuna valutazione finora

- Iiii JJJJ S S S S A A A A A A A A: Simulation of Cascaded Multilevel Inverter Using Hybrid PWM TechniqueDocumento4 pagineIiii JJJJ S S S S A A A A A A A A: Simulation of Cascaded Multilevel Inverter Using Hybrid PWM TechniqueKanaga VaratharajanNessuna valutazione finora

- Cascaded Multilevel Inverter With PWM Control MethodDocumento6 pagineCascaded Multilevel Inverter With PWM Control MethodseventhsensegroupNessuna valutazione finora

- 5 Level InverterDocumento6 pagine5 Level InverterRameshRtsNessuna valutazione finora

- PES Lab Report 1Documento22 paginePES Lab Report 1UJJAL CHATTERJEENessuna valutazione finora

- Comparative Study of SPWM and SVPWM Cascaded H-Bridge Multilevel InverterDocumento6 pagineComparative Study of SPWM and SVPWM Cascaded H-Bridge Multilevel InverterakshayNessuna valutazione finora

- Different PWM Modulation Techniques Indexes Performance Evaluation, 1993.Documento7 pagineDifferent PWM Modulation Techniques Indexes Performance Evaluation, 1993.Ali H. NumanNessuna valutazione finora

- (X) Comparison of 3 PWM Strategies SPWM SVPWM One Cycle CTRLDocumento4 pagine(X) Comparison of 3 PWM Strategies SPWM SVPWM One Cycle CTRLsrikanthboddunaNessuna valutazione finora

- Survey of CascadeDocumento10 pagineSurvey of Cascadesumiths32Nessuna valutazione finora

- A High-Performance Generalized Discontinuous PWM Algorithm: Ahmet M. Hava,, Russel J. Kerkman,, and Thomas A. LipoDocumento13 pagineA High-Performance Generalized Discontinuous PWM Algorithm: Ahmet M. Hava,, Russel J. Kerkman,, and Thomas A. LipoBrahmananda Reddy TeegalaNessuna valutazione finora

- Bare AreaDocumento2 pagineBare AreaMohan KumarNessuna valutazione finora

- Gmail - Booking Confirmation On IRCTC, Train - 02654, 11-Jun-2021, SL, TPJ - MSDocumento1 paginaGmail - Booking Confirmation On IRCTC, Train - 02654, 11-Jun-2021, SL, TPJ - MSMohan KumarNessuna valutazione finora

- Gmail - Booking Confirmation On IRCTC, Train - 02654, 11-Jun-2021, SL, TPJ - MSDocumento1 paginaGmail - Booking Confirmation On IRCTC, Train - 02654, 11-Jun-2021, SL, TPJ - MSMohan KumarNessuna valutazione finora

- Design Considerations and Topology Selection For A 120-kW IGBT Converter For EV Fast ChargingDocumento11 pagineDesign Considerations and Topology Selection For A 120-kW IGBT Converter For EV Fast ChargingMohan KumarNessuna valutazione finora

- 10 1 1 362 4613Documento24 pagine10 1 1 362 4613sumanthNessuna valutazione finora

- L (2-2) - Kirchhoffs Laws KCL KVL (Compatibility Mode) PDFDocumento21 pagineL (2-2) - Kirchhoffs Laws KCL KVL (Compatibility Mode) PDFDevith Menon Thirumangalath100% (1)

- Fuzzy Logic Control For Single Phase Multilevel InverterDocumento6 pagineFuzzy Logic Control For Single Phase Multilevel InverterMohan KumarNessuna valutazione finora

- MOSFET Power Losses Calculation Using The Data-Sheet ParametersDocumento23 pagineMOSFET Power Losses Calculation Using The Data-Sheet ParametersElvis Yu0% (1)

- 2018 IEEE TPE MogorovicDocumento15 pagine2018 IEEE TPE MogorovicMohan KumarNessuna valutazione finora

- 15 Switching Dissipation and Power LossesDocumento28 pagine15 Switching Dissipation and Power LossesSwifty SpotNessuna valutazione finora

- HellpDocumento1 paginaHellpMohan KumarNessuna valutazione finora

- Induction Motor Fault Diagnosis Using Fuzzy Decision SystemDocumento3 pagineInduction Motor Fault Diagnosis Using Fuzzy Decision SystemMohan KumarNessuna valutazione finora

- R 2008 Eee SyllabusDocumento74 pagineR 2008 Eee Syllabusrajavel_rajeshNessuna valutazione finora

- Anna University Report FormatDocumento7 pagineAnna University Report Formatdilip_66690% (10)

- Anna University Report FormatDocumento7 pagineAnna University Report Formatdilip_66690% (10)

- Load Forecasting Techniques and MethodologiesDocumento11 pagineLoad Forecasting Techniques and MethodologiespotatoNessuna valutazione finora

- Artificial Intelligence: Agents, Architecture, and TechniquesDocumento79 pagineArtificial Intelligence: Agents, Architecture, and TechniquesgopitheprinceNessuna valutazione finora

- FINAL (Revised) PDFDocumento109 pagineFINAL (Revised) PDFakumautobatNessuna valutazione finora

- Course-Content MSAIDocumento7 pagineCourse-Content MSAIAsany HerdianaNessuna valutazione finora

- EED7Documento14 pagineEED7Hill HermitNessuna valutazione finora

- (2020-2021 Fall Semester FINAL Exam) : Introduction To Fuzzy LogicDocumento21 pagine(2020-2021 Fall Semester FINAL Exam) : Introduction To Fuzzy LogicAlperen YılmazNessuna valutazione finora

- Soft β -compactness in soft topological spacesDocumento5 pagineSoft β -compactness in soft topological spacesAbedaNessuna valutazione finora

- CPE/CSC 481: Knowledge-Based Systems: Computer Science Department Cal PolyDocumento32 pagineCPE/CSC 481: Knowledge-Based Systems: Computer Science Department Cal PolygeorgesharmokhNessuna valutazione finora

- Hybrid SystemsDocumento5 pagineHybrid Systemsjyoti singhNessuna valutazione finora

- The Importance of Intelligent Control SystemsDocumento3 pagineThe Importance of Intelligent Control Systemsresearchparks100% (1)

- A Comprehensive Overview of Hybrid ConstructionDocumento15 pagineA Comprehensive Overview of Hybrid ConstructionShativel ViswanathanNessuna valutazione finora

- Cirp Journal of Manufacturing Science and Technology: A.M.M. Sharif Ullah, Md. Mamunur Rashid, Jun'ichi TamakiDocumento12 pagineCirp Journal of Manufacturing Science and Technology: A.M.M. Sharif Ullah, Md. Mamunur Rashid, Jun'ichi TamakiDr. Engr. Md Mamunur RashidNessuna valutazione finora

- AI & ML NotesDocumento22 pagineAI & ML Noteskarthik singaraoNessuna valutazione finora

- Modeling Inverse Kinematics in A Robotic Arm - MATLAB & Simulink ExampleDocumento5 pagineModeling Inverse Kinematics in A Robotic Arm - MATLAB & Simulink Exampletdit84Nessuna valutazione finora

- ANFIS - Identification With Special Emphasis On Training Data MinimizationDocumento141 pagineANFIS - Identification With Special Emphasis On Training Data MinimizationAlchemist7Nessuna valutazione finora

- Literature ReviewDocumento37 pagineLiterature ReviewFelix WalterNessuna valutazione finora

- Anfis Adap Tive-Ne Twork-Based Fuzzy Inference SystemDocumento21 pagineAnfis Adap Tive-Ne Twork-Based Fuzzy Inference SystemshathyaNessuna valutazione finora

- A Not Too Short Introduction To: Fuzzy SystemDocumento99 pagineA Not Too Short Introduction To: Fuzzy Systemfrans williamNessuna valutazione finora

- Functions - Add - MathsDocumento12 pagineFunctions - Add - MathsKris DookharanNessuna valutazione finora

- Driver Behavior Detection Techniques: A Survey: Sarah Kadhim Alluhaibi, Munaf S. Najim Al-Din, Aiman MoyaidDocumento6 pagineDriver Behavior Detection Techniques: A Survey: Sarah Kadhim Alluhaibi, Munaf S. Najim Al-Din, Aiman MoyaidPranesh KrishnanNessuna valutazione finora

- Fuzzy Expert SystemDocumento20 pagineFuzzy Expert SystemAditya KumarNessuna valutazione finora

- Intelligent Solar Tracking Control System Implemented On An FPGADocumento30 pagineIntelligent Solar Tracking Control System Implemented On An FPGAMurat Yasar ERTASNessuna valutazione finora

- Bangla Digit RecognitionDocumento18 pagineBangla Digit RecognitionDr. Shankar MaliNessuna valutazione finora

- A Review of Artificial Intelligence Technologies To Achieve Machining ObjectivesDocumento22 pagineA Review of Artificial Intelligence Technologies To Achieve Machining ObjectivesSaksham SetiaNessuna valutazione finora

- AI and AC in BuildingsDocumento15 pagineAI and AC in BuildingsPrincipal SSIETNessuna valutazione finora

- Fuzzy Logic & Fuzzy Sets: Siti Zaiton Mohd Hashim, PHDDocumento48 pagineFuzzy Logic & Fuzzy Sets: Siti Zaiton Mohd Hashim, PHDalexander frayaNessuna valutazione finora

- Fuzzy Logic Examples Using Matlab PDFDocumento7 pagineFuzzy Logic Examples Using Matlab PDFCarlos MuñizNessuna valutazione finora

- 1 s2.0 S092188902100155X MainDocumento15 pagine1 s2.0 S092188902100155X MainSherjanNessuna valutazione finora

- Principles/Foundations of Artificial Intelligence.: Inferencing MethodsDocumento35 paginePrinciples/Foundations of Artificial Intelligence.: Inferencing MethodsSabria OmarNessuna valutazione finora