Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

An 294

Caricato da

shirtquittersTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

An 294

Caricato da

shirtquittersCopyright:

Formati disponibili

Special Sample and Hold Techniques

AN-294

Special Sample and Hold Techniques

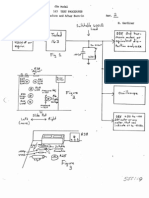

Although standard devices (e.g., the LF398) fill most sample and hold requirements, situations often arise which call for special capabilities. Extended hold times, rapid acquisition and reduced hold step are areas which require special circuit techniques to achieve good results. The most common requirement is for extended hold time. The circuit of Figure 1 addresses this issue. EXTENDED HOLD TIME SAMPLE AND HOLD In this circuit, extended hole time is achieved by stacking two sample and hold circuits in a chain. In addition, rapid acquisition time is retained by use of a feed-forward path. When a sample command is applied to the circuit (trace A, Figure 2 ), A1 acquires the input very rapidly because its

National Semiconductor Application Note 294 April 1982

0.002 F hold capacitor can charge very quickly. The sample command is also used to trigger the DM74C221 one-shot (trace B, Figure 2 ), which turns on the FET switch, S1. In this fashion, A1s output is fed immediately to the A3 output buffer. During the time the one-shot is high, A2 acquires the value of A1s output. When the one-shot drops low, S1 opens, disconnecting A1s output from A3s input. At this point A2s output is allowed to bias A3s input and the circuit output does not change from A1s initial sampled value. Trace C details what happens when S1 opens. A small glitch, due to charge transfer through the FET, appears but the steady state output value does not change. This circuit will acquire a 10V step in 10 s to 0.01% with a droop rate of just 30 V/second.

AN005637-1

FIGURE 1.

AN-294

AN005637-2

FIGURE 2.

1998 National Semiconductor Corporation

AN005637

www.national.com

PrintDate=1998/03/24 PrintTime=15:10:42 36764 an005637 Rev. No. 3

cmserv

Proof

AN005637-3

S1 = LF13331 A1, A3, A5 = LF411 A2 = LF400 *Ratio match 0.1%

FIGURE 3. INFINITE HOLD SAMPLE AND HOLD Figure 3 details a circuit which extends the hold time to infinity with an acquisition time of 10 s. Once a signal has been acquired, this circuit will hold its output with no droop for as long as is desired. If this arrangement, A4s divided down output is fed directly to the circuit output via A5 as soon as a sample command (trace A, Figure 4 ) is applied. The sample command is also used to trigger the DM74123 one-shots. The first one-shot (trace B, Figure 4 ) is used to bias the FET switch OFF during the time it is low. The second one-shot (trace C, Figure 4 ) delivers a pulse to the ADC0801 A/D converter which then performs an A/D conversion on A4s output. The DAC1020, in combination with A2 and A3, converts the A/D output back to a voltage. The A/D/A process requires about 100 s. When the one-shot (trace B) times out, its output goes high, closing the FET switch. This action effectively connects A3s output to A5 while disconnecting A4s output. In this manner, the circuit output will remain at the DC level that was originally determined by A4s sampling action. Because the sampled value is stored digitally, no droop error can occur. The precision resistors noted in the circuit provide offsetting capability for the unipolar A/D output so that a 10V to +10V input range can be accommodated. To calibrate this circuit, apply 10V to the input and drive the sample command input with a pulse generator. Adjust the gain match potentiometer so that minimum hop occurs at the circuit output when S1 closes. Next, ground the input and adjust the zero potentiometer for 0V output. Finally, apply 10V to the input and adjust the gain trim for a precise 10V circuit output. Once adjusted, this circuit will hold a sampled input to within the 8-bit quantization level of the A/D converter over a full range of +10V to 10V. Trace D, Figure 4 shows the circuit output in great detail. The small glitch is due to parasitic capacitance in the FET switch, while the level shift is caused by quantization in the A/D. An A/D with higher resolution could be used to minimize this effect.

www.national.com

PrintDate=1998/03/24 PrintTime=15:10:42 36764 an005637 Rev. No. 3

cmserv

Proof

junction. If the error is negative, the inverse will occur. After some number of input pulses, A1s output will settle at a DC level which is equivalent to the value of the level sampled during the 100 ns window. Note that the delay time of one-shot A is variable, allowing the sample pulse from one-shot B to be placed at any desired point on the input waveform. Figure 6 shows the circuit waveforms. Trace A is the circuit input. After the variable delay provided by one-shot A, one-shot B generates the sample pulse (trace B). In this case the delay has been adjusted so that sampling occurs at the mid-point of the input waveform, although any point may be sampled by adjusting the delay appropriately.

AN005637-4

FIGURE 4. HIGH SPEED SAMPLE AND HOLD Another requirement encountered in sample and hold work is high speed. Although conventional sample and hold circuits can be built for very fast acquisition times, they are difficult and expensive. If the input waveform is repetitive, the circuit of Figure 5 can be employed. In this circuit a very fast comparator and a digital latch are placed in front of a differential integrator. Feedback is used to close a loop around all these elements. Each time an input pulse is applied, the DM7475 latch is opened for 100 ns. If the summing junction error at the LM361 is positive, A1 will pull current out of the

Figure 7 shows the circuit at work sampling a 1 MHz sine wave input. The optional comparator (C2) shown in dashed lines is used to convert the sine wave input into a TTL compatible signal for the DM74123 one-shot. Trace A is the sine wave input while trace B represents the output of C2. Trace C is the delay generated by one-shot A and trace D is the sample width window out of one-shot B. Note that this pulse can be positioned at any point on the high speed sine wave with the resultant voltage level appearing at A1s output.

REDUCED HOLD STEP SAMPLE AND HOLD Another area where special techniques may offer improvement is minimization of hold step. When a standard sample and hold switches from sample to hold, a large amplitude high speed spike may occur. This is called hold step and is usually due to capacitive feedthrough in the FET switches used in the circuit.

AN005637-5

FIGURE 5.

www.national.com

PrintDate=1998/03/24 PrintTime=15:10:43 36764 an005637 Rev. No. 3

cmserv

Proof

AN005637-7 AN005637-6

FIGURE 6.

FIGURE 7.

AN005637-8

NPN = 2N2369 PNP = 2N2907 C1, C2 = LM311 A1 = LF356 Note: All capacitor values are in F.

FIGURE 8. The circuit of Figure 8 greatly reduces hold step by using an unusual approach to the sample and hold function. In this circuit sampling is started when the sample and hold command input goes low (trace A, Figure 9 ). This action also sets the DM7474 flip-flop low (trace B, Figure 9 ). At the same time, C1s output clamps at Q3s emitter potential of 12V (trace C, Figure 9 ). When the sample pulse returns high, C1s output floats high and the 0.003 F capacitor is linearly charged by current source Q1. This ramp is followed by A1, which feeds C2. When the ramp potential equals the circuits input voltage, C2s output (trace D, Figure 9 ) goes high, setting the flip-flop high. This turns on Q2, very quickly cutting off the Q1 current source. This causes the ramp to stop and sit at the same potential at the circuits input. The hold step generated when the circuit goes into hold mode (e.g., when the flip-flop output goes high) is quite small. Trace E, a greatly enlarged version of trace C, details this. Note the hold step is less than 10 mV high and only 30 ns in duration. Acquisition time for this circuit is directly dependent on the input value, at a rate of 5 s/V.

www.national.com

Book Extract End

PrintDate=1998/03/24 PrintTime=15:10:43 36764 an005637 Rev. No. 3

cmserv

Proof

REFERENCE One IC Makes Precision Analog Sampler , S. Dendinger; EDN May 20, 1977.

Book Extract End

AN005637-9

FIGURE 9.

www.national.com

PrintDate=1998/03/24 PrintTime=15:10:43 36764 an005637 Rev. No. 3

cmserv

Proof

Special Sample and Hold Techniques

LIFE SUPPORT POLICY NATIONALS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein: 2. A critical component in any component of a life support 1. Life support devices or systems are devices or sysdevice or system whose failure to perform can be reatems which, (a) are intended for surgical implant into sonably expected to cause the failure of the life support the body, or (b) support or sustain life, and whose faildevice or system, or to affect its safety or effectiveness. ure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

National Semiconductor Corporation Americas Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com National Semiconductor Europe Fax: +49 (0) 1 80-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 1 80-530 85 85 English Tel: +49 (0) 1 80-532 78 32 Franais Tel: +49 (0) 1 80-532 93 58 Italiano Tel: +49 (0) 1 80-534 16 80 National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5620-6175 Fax: 81-3-5620-6179

AN-294

www.national.com

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

PrintDate=1998/03/24 PrintTime=15:10:43 36764 an005637 Rev. No. 3

cmserv

Proof

Potrebbero piacerti anche

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- Snoa 600 ADocumento16 pagineSnoa 600 ALoret1086Nessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Valutazione: 2.5 su 5 stelle2.5/5 (3)

- 10 1 1 120 9436Documento4 pagine10 1 1 120 9436Mohammad Ayatullah MaktoomNessuna valutazione finora

- 110 Waveform Generator Projects for the Home ConstructorDa Everand110 Waveform Generator Projects for the Home ConstructorValutazione: 4 su 5 stelle4/5 (1)

- UC3842 current mode controller application noteDocumento7 pagineUC3842 current mode controller application noteCui BapNessuna valutazione finora

- Influence of System Parameters Using Fuse Protection of Regenerative DC DrivesDa EverandInfluence of System Parameters Using Fuse Protection of Regenerative DC DrivesNessuna valutazione finora

- UC3845 Technical ExplanationDocumento15 pagineUC3845 Technical ExplanationankurmalviyaNessuna valutazione finora

- MS Project ReportDocumento11 pagineMS Project ReportArnab Jyoti BaruahNessuna valutazione finora

- Uc3842 Provides Low-Cost Current-Mode Control: Application NoteDocumento16 pagineUc3842 Provides Low-Cost Current-Mode Control: Application NoteLeonardo Ortiz100% (1)

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsDa EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsNessuna valutazione finora

- Soft Start Circuit For Peak Current Mode DC-DC ConverterDocumento5 pagineSoft Start Circuit For Peak Current Mode DC-DC ConverterHassan SharghiNessuna valutazione finora

- Switching Power Supply Design Review - 60 Watt Flyback Regulator by Raoji Patel and Glen FRFTZ Slup072Documento17 pagineSwitching Power Supply Design Review - 60 Watt Flyback Regulator by Raoji Patel and Glen FRFTZ Slup072Burlacu AndreiNessuna valutazione finora

- 60W Flyback TIDocumento16 pagine60W Flyback TIe_magazin3821Nessuna valutazione finora

- H BridgeDocumento16 pagineH BridgeSkiron ThrasciusNessuna valutazione finora

- AppNote03 Uc3842Documento14 pagineAppNote03 Uc3842Heriberto Flores AmpieNessuna valutazione finora

- Aplicacion Uc3842Documento15 pagineAplicacion Uc3842Gian Mejia100% (1)

- Slua 143Documento15 pagineSlua 143Tonia KataNessuna valutazione finora

- A High Efficiency Boost Converter For TFT-LCD Bias SupplyDocumento4 pagineA High Efficiency Boost Converter For TFT-LCD Bias SupplyHamid BoualiNessuna valutazione finora

- Frequency Modulator Experiment ReportDocumento7 pagineFrequency Modulator Experiment ReportreganoctNessuna valutazione finora

- Overcoming Leakage Current by Output Precharging in Error AmplifiersDocumento4 pagineOvercoming Leakage Current by Output Precharging in Error AmplifiersSudhakar SpartanNessuna valutazione finora

- Resonant DC Link in PWM AC ChopperDocumento5 pagineResonant DC Link in PWM AC ChopperMukesh SharmaNessuna valutazione finora

- ESM740G TiristorDocumento2 pagineESM740G Tiristorjosenicolas12000Nessuna valutazione finora

- Digital Current Limiting Techniques For Switching Power Supplies PDFDocumento9 pagineDigital Current Limiting Techniques For Switching Power Supplies PDFAdolfo A HerreraNessuna valutazione finora

- UC2842 Philips AN1272 PDFDocumento7 pagineUC2842 Philips AN1272 PDFupali01Nessuna valutazione finora

- 128122-Accelerometer & VelomitorTransducerOperationDocumento22 pagine128122-Accelerometer & VelomitorTransducerOperationNorman MoralesNessuna valutazione finora

- Ec 4112: Analog Communication Laboratory List of Experiments: Compulsory ExperimentsDocumento68 pagineEc 4112: Analog Communication Laboratory List of Experiments: Compulsory ExperimentsArchit SrivastavaNessuna valutazione finora

- UC3842 Inside SchematicsDocumento17 pagineUC3842 Inside Schematicsp.c100% (1)

- DC Chopper Circuit Performance StudyDocumento10 pagineDC Chopper Circuit Performance StudykamalNessuna valutazione finora

- MC13783 Buck and Boost Inductor Sizing: Application NoteDocumento8 pagineMC13783 Buck and Boost Inductor Sizing: Application NoteSyed Qaseem AliNessuna valutazione finora

- Griffith University-Gold Coast School of Engineering: 3312eng: Digital Signal ProcessingDocumento7 pagineGriffith University-Gold Coast School of Engineering: 3312eng: Digital Signal ProcessingSamanthaFlohrNessuna valutazione finora

- Bioelectric Potential Amplfier Design: Senior Design Project P09004Documento30 pagineBioelectric Potential Amplfier Design: Senior Design Project P09004Liliana Maria Plata SarmientoNessuna valutazione finora

- Tty To Rs232Documento8 pagineTty To Rs232sandeepverma8257100% (2)

- A Single Stage Flyback Power Supply Unit For LED Lighting ApplicationsDocumento5 pagineA Single Stage Flyback Power Supply Unit For LED Lighting ApplicationsPhạm Văn TưởngNessuna valutazione finora

- CMOS Comparator Design: TSMC 0.25 Um TechnologyDocumento15 pagineCMOS Comparator Design: TSMC 0.25 Um TechnologySharath_Patil_7623Nessuna valutazione finora

- Simple automatic-shutoff circuit uses few componentsDocumento5 pagineSimple automatic-shutoff circuit uses few componentsJuan Manuel Han MacNessuna valutazione finora

- Slua 080Documento24 pagineSlua 080HauvuNessuna valutazione finora

- An IC Operational Transconductance Amplifier (OTA) With Power CapabilityDocumento11 pagineAn IC Operational Transconductance Amplifier (OTA) With Power CapabilityhakimshujaNessuna valutazione finora

- AS3842Documento10 pagineAS3842kik020Nessuna valutazione finora

- Speed Control IC for Motors with Tacho FeedbackDocumento11 pagineSpeed Control IC for Motors with Tacho FeedbackAlex FierăscuNessuna valutazione finora

- Phone Charger SchematicDocumento6 paginePhone Charger Schematicyudi_sibaraniNessuna valutazione finora

- Chopper Controlled DC Drive: INSTRUCTED BY: Dr. BuddhikaDocumento8 pagineChopper Controlled DC Drive: INSTRUCTED BY: Dr. BuddhikaNipuna Thushara WijesekaraNessuna valutazione finora

- Blazer 400-800 Service ManualDocumento34 pagineBlazer 400-800 Service ManualdaossaNessuna valutazione finora

- Design Note: Optimizing Performance in Uc3854 Power Factor Correction ApplicationsDocumento42 pagineDesign Note: Optimizing Performance in Uc3854 Power Factor Correction ApplicationsidsufixNessuna valutazione finora

- Ieee Current ModeDocumento7 pagineIeee Current ModepqqpNessuna valutazione finora

- Ground Fault Protection PaperDocumento4 pagineGround Fault Protection PaperAbhishek ParmarNessuna valutazione finora

- Building Blocks of An OpampDocumento11 pagineBuilding Blocks of An OpampChathunikaNessuna valutazione finora

- A 50A, 1-S-Rise-Time, Programmable Electronic Load Instrument For Measurement of Microprocessor Power Supply Transient PerformanceDocumento5 pagineA 50A, 1-S-Rise-Time, Programmable Electronic Load Instrument For Measurement of Microprocessor Power Supply Transient PerformanceAnonymous 3mJfZENessuna valutazione finora

- New Microsoft Word DocumentDocumento4 pagineNew Microsoft Word Documentalaa delewarNessuna valutazione finora

- Microprocessor Based Impedance Relay: TechnicalsymposiumDocumento14 pagineMicroprocessor Based Impedance Relay: TechnicalsymposiumGaurav JaiswalNessuna valutazione finora

- Mini Project DocumentationDocumento34 pagineMini Project DocumentationSri Krishna RakeshNessuna valutazione finora

- Sepic Converter Design and Operation: by Gregory SharpDocumento21 pagineSepic Converter Design and Operation: by Gregory SharpSingam SridharNessuna valutazione finora

- Research Article: A Four Quadrature Signals' Generator With Precise Phase AdjustmentDocumento7 pagineResearch Article: A Four Quadrature Signals' Generator With Precise Phase Adjustmentaamir.nedian4139Nessuna valutazione finora

- Application Note 149 January 2015 Modeling and Loop Compensation Design of Switching Mode Power SuppliesDocumento22 pagineApplication Note 149 January 2015 Modeling and Loop Compensation Design of Switching Mode Power SuppliesArumugam RajendranNessuna valutazione finora

- 5-10542 Viper 100 DatasheetDocumento9 pagine5-10542 Viper 100 DatasheetMahmoud NaguibNessuna valutazione finora

- Obsolete Product(s) - Obsolete Product(s) Obsolete Product(s) - Obsolete Product(s)Documento15 pagineObsolete Product(s) - Obsolete Product(s) Obsolete Product(s) - Obsolete Product(s)teomondoNessuna valutazione finora

- Electric Fence Controllers ExplainedDocumento11 pagineElectric Fence Controllers Explainedjavier_valdivia_4250% (2)

- An 311Documento6 pagineAn 311ayatullah21Nessuna valutazione finora

- Poptronics 1975 09Documento100 paginePoptronics 1975 09shirtquittersNessuna valutazione finora

- DBX 117 Cut SheetDocumento2 pagineDBX 117 Cut SheetshirtquittersNessuna valutazione finora

- Transistor Circuit Manual 1961 - Allan LytelDocumento256 pagineTransistor Circuit Manual 1961 - Allan LytelshirtquittersNessuna valutazione finora

- Poptronics 1975 11Documento66 paginePoptronics 1975 11shirtquittersNessuna valutazione finora

- Crossover Operation ManualDocumento16 pagineCrossover Operation ManualjoseismarNessuna valutazione finora

- Olson 1968Documento40 pagineOlson 1968shirtquittersNessuna valutazione finora

- McGee 1967 PDFDocumento176 pagineMcGee 1967 PDFshirtquittersNessuna valutazione finora

- Poptronics 1975 08Documento92 paginePoptronics 1975 08shirtquittersNessuna valutazione finora

- Radio Shack 68Documento116 pagineRadio Shack 68shirtquittersNessuna valutazione finora

- SMPE Standards PDFDocumento17 pagineSMPE Standards PDFshirtquittersNessuna valutazione finora

- Lafayette 1968 SpringDocumento130 pagineLafayette 1968 SpringwhyoryNessuna valutazione finora

- THAT 202 VCA ModulesDocumento2 pagineTHAT 202 VCA ModulesshirtquittersNessuna valutazione finora

- Radio Shack 1967Documento144 pagineRadio Shack 1967shirtquitters100% (1)

- Lafayette 1968 SummerDocumento128 pagineLafayette 1968 SummershirtquittersNessuna valutazione finora

- Cherry Kino Wondermental Super8 and 16mm Film Techniques PDFDocumento15 pagineCherry Kino Wondermental Super8 and 16mm Film Techniques PDFshirtquittersNessuna valutazione finora

- 200x IIDocumento21 pagine200x IIshirtquittersNessuna valutazione finora

- 163 Calibration ProcedureDocumento6 pagine163 Calibration ProcedureshirtquittersNessuna valutazione finora

- That:Dbx2002 VcaDocumento4 pagineThat:Dbx2002 VcashirtquittersNessuna valutazione finora

- 122 and 124 DBX II Tape Noise Reduction Systems SpécificationsDocumento1 pagina122 and 124 DBX II Tape Noise Reduction Systems SpécificationsshirtquittersNessuna valutazione finora

- 163X Owners ManualDocumento15 pagine163X Owners ManualshirtquittersNessuna valutazione finora

- Dbx2150vca AnDocumento8 pagineDbx2150vca AnshirtquittersNessuna valutazione finora

- 163-164 SchematicDocumento29 pagine163-164 SchematicshirtquittersNessuna valutazione finora

- Uses DBX 146221Documento8 pagineUses DBX 146221shirtquittersNessuna valutazione finora

- An 311Documento6 pagineAn 311ayatullah21Nessuna valutazione finora

- Audio Applications of Linear IcsDocumento6 pagineAudio Applications of Linear IcsscribdmantomNessuna valutazione finora

- An 286Documento6 pagineAn 286shirtquittersNessuna valutazione finora

- An 262Documento10 pagineAn 262shirtquittersNessuna valutazione finora

- bstj29 1 94Documento11 paginebstj29 1 94shirtquittersNessuna valutazione finora

- Scheme Oscilatoare de Joasa FrecvantaDocumento16 pagineScheme Oscilatoare de Joasa FrecvantaadipanNessuna valutazione finora

- Daewoo Model Dwl-28w8Documento53 pagineDaewoo Model Dwl-28w8livionetespanNessuna valutazione finora

- Serial Communication in AVRDocumento35 pagineSerial Communication in AVRgopalgeniusNessuna valutazione finora

- C264-R Application: Modular Remote Terminal UnitDocumento4 pagineC264-R Application: Modular Remote Terminal UnitLa Picarona del PeruNessuna valutazione finora

- Discrete 1Documento14 pagineDiscrete 1Narmatha RamasamyNessuna valutazione finora

- Electrical Machines LabDocumento8 pagineElectrical Machines LabrabbystarNessuna valutazione finora

- SMX Range: Operating InstructionsDocumento28 pagineSMX Range: Operating InstructionsIanRendallNessuna valutazione finora

- 3 1 5 Ohms Law 1Documento3 pagine3 1 5 Ohms Law 1api-291536640Nessuna valutazione finora

- Week 8:: ObjectivesDocumento12 pagineWeek 8:: ObjectivesJohn Kenneth MantesNessuna valutazione finora

- ROM Laboratory v1.00Documento548 pagineROM Laboratory v1.00Carlos Reaper Jaque OlivaresNessuna valutazione finora

- Dell Se178wfpc Service Manual PDFDocumento73 pagineDell Se178wfpc Service Manual PDFBoata EtaNessuna valutazione finora

- Pentium CacheDocumento5 paginePentium CacheIsmet BibićNessuna valutazione finora

- Weekly Report JABO3 W42Documento32 pagineWeekly Report JABO3 W42Sehat MaruliNessuna valutazione finora

- Digilent Synchronous Parallel Interface (DSTM)Documento10 pagineDigilent Synchronous Parallel Interface (DSTM)Raul Gil BayardoNessuna valutazione finora

- SM 9412Documento30 pagineSM 9412Elton RibeiroNessuna valutazione finora

- EE3403 -MEASUREMENTS AND INSTRUMENTATION --Question Bank-1- refer CAT 1Documento8 pagineEE3403 -MEASUREMENTS AND INSTRUMENTATION --Question Bank-1- refer CAT 1Pandyselvi BalasubramanianNessuna valutazione finora

- Free - To - Air Satellite Receiver: Customer Careline 0901 293 0038Documento24 pagineFree - To - Air Satellite Receiver: Customer Careline 0901 293 0038mythulasiNessuna valutazione finora

- Fanuc Series 0i Model A CNC BatteryDocumento6 pagineFanuc Series 0i Model A CNC BatterymhdagungpratamaNessuna valutazione finora

- 8051 Microcontroller Part 1Documento21 pagine8051 Microcontroller Part 1Sardar IrfanullahNessuna valutazione finora

- BA01 - Analog IC DesignDocumento8 pagineBA01 - Analog IC DesignCláudio RegisNessuna valutazione finora

- LM324 Comparador de Voltaje Nte987Documento3 pagineLM324 Comparador de Voltaje Nte987criman45Nessuna valutazione finora

- The University of Texas at Arlington Timers, Capture/Compare/PWMDocumento22 pagineThe University of Texas at Arlington Timers, Capture/Compare/PWMadamwaiz100% (1)

- Bodo's Power SystemDocumento68 pagineBodo's Power SystemSanzad LumenNessuna valutazione finora

- ch03 PDFDocumento110 paginech03 PDFBad CodeNessuna valutazione finora

- 01 Semiconductor TheoryDocumento32 pagine01 Semiconductor TheoryAnmay MishraNessuna valutazione finora

- Os Unit 6Documento65 pagineOs Unit 6tseNessuna valutazione finora

- Alstom CT Calculation GuideDocumento2 pagineAlstom CT Calculation Guidesrinivasaphanikiran67% (3)

- Part 5 - Electroacoustic Devices - HandoutDocumento17 paginePart 5 - Electroacoustic Devices - HandoutJade Mark RamosNessuna valutazione finora

- Vlsi Design Lab ManualDocumento33 pagineVlsi Design Lab Manualjitu123456789100% (1)

- CTs & VTsDocumento48 pagineCTs & VTssulemankhalid100% (1)

- Electronics ReviewerDocumento3 pagineElectronics ReviewerTherence Michael GarciaNessuna valutazione finora