Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Artigo Arquitetura

Caricato da

Anderson MartimTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Artigo Arquitetura

Caricato da

Anderson MartimCopyright:

Formati disponibili

FACULDADES INTEGRADAS CAMES

Tecnologia em Anlise e Desenvolvimento de Sistemas Estudo sobre Arquitetura de Computadores

Ktia Kurt Jungbeck E-mail: katiakurtjungbeck@hotmail.com Prof. Claudio Kleina

Setembro - 2012 Curitiba PR

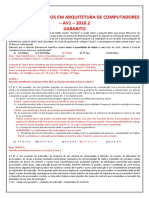

FACULDADES INTEGRADAS CAMES PROF. CLAUDIO KLEINA

PROCESSADORES: CISC e RISC

Trabalho apresentado pela aluna do 2 perodo de Anlise e Desenvolvimento de Sistemas disciplina de Arquitetura de Computadores.

CURITIBA 2012

NDICE

1. Introduo 2. CISC e RISC 2.1 2.2 2.3 2.4 O que um CISC? Como funciona um CISC? O que um RISC? Como funciona um RISC?

3. Diferenas entre Arquiteturas de CISC e RISC 3.1 Comparaes entre caractersticas de CISC e RISC

4. Exemplos de CISC e RISC 4.1 Exemplos de CISC 4.2 Exemplos e Aplicaes de RISC 5. Referncias Bibliogrficas

1. INTRODUO

Um processador CISC (complex Instruction Set Computer, ou computador com um conjunto complexo de instrues), capaz de executar vrias centenas de instrues complexas diferentes, sendo extremamente verstil. Exemplos de processadores CISC so o 386 e o 486. No comeo da dcada de 80, a tendncia era construir chips com conjunto de instrues cada vez mais complexos. Alguns fabricantes porm, resolveram seguir o caminho oposto, criando o padreo RISC (Reduced Instruction Set Computer, ou computador com um conjunto reduzido de instrues). Ao contrrio dos complexos CISC, os processadores RISC so cpazes de executarapenas algumas poucas instrues simples. Justamente por isso, os chips baseados nessa aqrquitetura so mais simples e muito mais baratos. Outra vantagem dos processadors RISC, que, por terem um menor nmero de circuitos internos, podem trabalhar a frequncias mais altas. Um exemplo so os processadores Alpha, que em 97 j operavam a 600 MHz. Nos processadores CISC, a lgica para a maioria das instrues, com exceo das mais primitivas (shift, add, etc...), guardada em microcdigo no processador, enquanto que para o processador RISC, fornecida por software. O conceito RISC, que o complementar de CISC, est se espalhando pelos sistemas dedicados. Essas mquinas, oferecem poucas instrues e, por isso, sua unidade de controle mais simples permitindo que se logre uma melhor otimizao. Os benefcios do RISC, alm de melhor desempenho, so um menor CI, uma menor quantidade de pinos e um menor consumo de energia. At poucos anos, a diviso foi contundente: arquiteturas RISC eram usados para rede, enquando a CISC era usado em computadores domsticos. Mas agora alguns esto afirmando que CISC esto esgotando sua possibilidades, enquanto outros defendem fervorosamente que CISC j teria alcanado RISC, adotando algumas das suas principais caractersticas.

2. CISC E RISC

2.1 O que um CISC?

um processador capaz de executar centenas de instrues complexas diferentes sendo, assim, extremamente verstil. Grande parte dos processadores Intel e Motorola Tm o desenho CISC. A vantagem de uma arquitetura CISC que j temos muitas das instrues guardadas nos prprio processador, o que facilita o trabalho dos programadores de linguagem de mquina, dispondo assim de praticamente todas as instrues que sero usadas em seus programas. O CISC tem uma grande riqueza na especificao de modos de endereamento.

2.2 Como funciona um CISC?

Essa arquiteturas faz o parelelismo entre as instrues, para que hoje a maioria dos sitemas CISC de alto desempenho implementem um sistema que converta as instrues complexas em vrias instrues simples, normalmente chamado de microinstrues. O firmware um recurso importante e essencial de quase todas as arquiteturas CISC. O frmware significa que cada instruo de mquina interpretado por um microprograma localizado em uma memria de circuito integrado no processador. As instrues so compostas so decodificadas internamente e executas com uma srie de microinstrues armazenadas em uma ROM interna. Isso vai exigir vrios ciclos de clock, pelo menos uma microinstruo. Portanto, assim como os chips CISC utilizam comandos que incorporam uma variedade de pequenas instrues para executar uma nica operao. Quando um sistema operacional ou um aplicativo requer uma dessas aes, envia ao processador o nome do comando a ser feito em conjunto com outras informaes complementares caso necessite. Mas cada um desses comandos da ROM do CISC

variam em tamanho e, portanto, o chip deve verificar primeiro a quantidade de espao necessrio para executar o comando e poder reserv-lo na memria interna. Alm disso, o processador deve determinar a maneira correta de carregar e armazenar o comando, processos que juntos prejudicam a agilidade do sistema. O processador envia o comando solicitando uma unidade que o decodifica em instrues menores que podero ser executadas por um nanoprocessador, uma espcie de processador dentro do processador. E a no ser as instrues independente, pois so instrues menores procedentes da decodificao de ma instruo maior, s permitido realizar uma intruo por vez. Atrves do complexo circuito do chip, o nanoprocessador executa cada uma das instrues de comando. A execuo deste circuito tambm lentilizam o processo. Para cada instruo um chip CISC requer de quatro a dez ciclos de clock.

2. CISC E RISC

2.3 O que um RISC?

Procurando aumentar a velocidade de processamento se descobriu com base em experimentos que, com uma determinada arquitetura de base, a execuo de programas compilados diretamente com microinstrues e uso da memria externa para o circuito integrado resultavam ser mais eficiente, graas ao tempo de acesso a memria que foi diminuindo medida que melhorou a sua tecnologia de encapsulamento. A idia foi inspirada no fato de muitas das caractersticas que foram includas nos projetos tradicionais de CPU para aumentar a velocidade estavam sendo ignoradas pelos programas que foram executados neles. Alm disso, a velocidade do processador em relao a memria de computador que a acessava estava cada vez mais alto. Devido a um conjunto de intrues simplificadas, estas que podem ser implantadas por um hardware diretamente ligado CPU a qual elimina o microcdigo e a necessidade de decodificar instrues completas. Tanto a Intel como a AMD, perceberam que usar alguns conceitos da arquitetura RISC em seus processadores poderia ajud-las a criar processadores mais rpidos. Porm, ao mesmo tempo, existia a necessidade de continuar criando processadores compatveis com os antigos. No adiantaria muito lanar um Pentium ll ou Athlon extremamente rpidos, se estes no fossem compatveis com os programas que utilizamos. A idia ento passou a ser contruir chips hbridos, que fossem capazes de executar as instrues x86, sendo compatveis com todos os programas, mas ao mesmo tempo comportando-se iinternamente como chips RISC, quebrando essas instrues complexas em instrues simples, que podem ser processadas por seu ncleo RISC. Tanto o Pentium ll e III, quanto ao Athlom, Duron e Celeron, utilizam este sistema.

Do lado dos chips supostamente RISC, como por exemplo o G4 usados nos Macs, temos esta mesma tendncia de contruir chips cada vez mais complexos, abandonando a idia dos chips RISC simples e baratos em favor da complexidade tpica dos processadores CISC.

2.4 Como funciona um RISC?

Pode parecer estranho que um chip que capaz de executar algumas poucas instrues, possa ser considerado por muitos, mais rpido do que o outro que executa centenas delas, seria como comparar um professor de matemtica com algum que sabe apenas as quatro operaes. Mas o que acontece, que um processador RISC capaz de executar tais instrues muito mais rapidamente. A idia principal, que apesar de um processador CISC ser capaz de executar centenas de instrues diferentes, apenas algumas so usadas frequentemente. Em conjunto com um software adequado, este processador seria capaz de desempenhar quase todas as funes de um processador CISC, acabando por compensar suas limitaes com uma maior velocidade de processamento. indiscutvel, porm, que em instrues complexas os processadores CISC saemse melhor. Por isso, ao invs da vitria de uma das duas tecnologias, atualmente vemos processadores hbridos, que so essencialmente processadores CISC, mas incorporam muitos recursos encontrados nos processadores RISC (ou vice-versa).

3. DIFERENAS ENTRE ARQUITETURAS CISC E RISC

A transio de CISC para RISC foi uma mudana radical na arquitetura. Os conjuntos de instrues foram mudados, sacrificando a compatibilidade binria para o desempenho. Reduzindo o conjunto de instrues, o processador cabia em um chip menor que permitia que os desenvolvedores aumentassem a velocidade do clock. Alm disso, o processador poderia ser pipelineado e uma unidade de controle microcodificada tornou-se desnecessria. RISC resolve os casos comuns mais rpidos, era o princpio que conduziu a um aumento impressionante da performance comparados com os processadores CISC. Enquanto a tecnologia avanava para aumentar os tamanhos dos dados e aumentar a densidade do transitor, os desenvolvedores do processador RISC comearam a considerar maneiras de usar esse espao novo do chip. Alguns dos usos desse espao incluram: On-chip chaces que so cronometradosto rapidamente quanto ao processador; Unidades funcionais adicionais para execuo superescalar; Intrues adicionais no-RISC (mais rpidas); On-chip aceitando operaes de ponto flutuante; Profundidade aumentada do pipeline.

Assim, a gerao atual de processadores de desempenho elevado carrega poucas caractersticas dos processadores que iniciram a revoluo RISC. Todos os processadores dispem de instrues de salto de ida e volta, normalmente designados de instrues de chamada de sub-rotinas: nestas, para alm de se alterar o contedo do registro PC como qualquer instruo de salto, primeiro guarda-se o endereo de instruo de salto (e que se encontra no PC). Nas arquiteturas CISC normalmente este valor guardado na stack. Nas aquiteturas RISC o valor normalmente guardado num registro. CISC - Grande riqueza na especificao de modos de endereamento; RISC - Apenas em operaes load/store e apenas 1 ou 2 modos; CISC - 1 ou mais operandos em memria (Max 1 i86 e M68K); RISC Operandos sempre em registros.

Atualmente pode-se dizer que no existem mais chips CISC ou RISC, mas sim chips hbridos, que misturam caractersticas das duas arquiteturas, a fim de obter o melhor desempenho possvel.

3.1 COMPARAO ENTRE CARACTERSTICAS CISC E RISC

Principais caractersticas de microprocessadores CISC: Muitas instrues; Instrues so complexas; Microcodificao das instrues; Alta capacidade de endereamento para operaes de memria; Nmero reduzido de registradores.

Em comparao, microprocessadores RISC so mais ou menos opostos aos CISC: Conjunto reduzido de instrues; Instrues menos complexas; Unidade de controle hardwarizada; Baixa capacidade de endereamento para operaes de memria; Apenas duas instrues bsicas, LOAD e STORE; Grande nmero de registradores.

4. Exemplos de CISC e RISC 4.1- Exemplos de arquitetura CISC

X86: Basicamente todos os processadores atuais desktop se enquadram nessa categoria, desde os 80386 at os modernos Core i7;

4.2 Exemplos de Aplicao e Arquitetura RISC DEC Alpha: Workstations, servidores; PA-RISC Packard, da Hewlett; ARC: Chips multimdia; ARM: iPad, Smartphones, Celulares; Modens; Power PC, Apple Motorola, IBM; Power: Playstation 3, Xbox 360, Wii; Supercomputadores.

5. REFERNCIAS BIBLIOGRFICAS

[1] Wikipedia, CISC [2] Wikipedia, RISC [3] www.guidohacker.com.br [4] WWW.scrib.com [5] WWW.diegomacedo.com.br

Potrebbero piacerti anche

- Sistemas Embarcados Ou EmbutidosDocumento6 pagineSistemas Embarcados Ou EmbutidosBragança BragançaNessuna valutazione finora

- 03 - AOC II - Cisc - Risc - EpicDocumento48 pagine03 - AOC II - Cisc - Risc - EpicRanderson AfonsoNessuna valutazione finora

- Compilado de Provas de Organização de Computadores - UNIP EADDocumento9 pagineCompilado de Provas de Organização de Computadores - UNIP EADFelipe Vts100% (1)

- Gabarito Top Av Arq MM Prova Av1 2018 2Documento5 pagineGabarito Top Av Arq MM Prova Av1 2018 2Alexandre Melo100% (1)

- Hardware de Computadores 1Documento161 pagineHardware de Computadores 1Hernane BiniNessuna valutazione finora

- Curso de Assembly RBT - 1994 - Frederico Lamberti PissarraDocumento132 pagineCurso de Assembly RBT - 1994 - Frederico Lamberti PissarrathoomaswillNessuna valutazione finora

- Micro ControladoresDocumento295 pagineMicro Controladoresglebson100% (1)

- Bambozi 385 EdDocumento10 pagineBambozi 385 EdINTERPLASMA CORTE E SOLDANessuna valutazione finora

- BS-BSG, BSG, 05dgr, BSG 05d, BSG 04dgr, BSG 04d, BSG 02d, Bs 90d, Bs 240dgr, Bs 240d, Bs 150dDocumento24 pagineBS-BSG, BSG, 05dgr, BSG 05d, BSG 04dgr, BSG 04d, BSG 02d, Bs 90d, Bs 240dgr, Bs 240d, Bs 150dJoão Francisco MontanhaniNessuna valutazione finora

- Projecto Com TwidoDocumento141 pagineProjecto Com TwidoDiana SilvaNessuna valutazione finora

- Trabalho de TICsDocumento15 pagineTrabalho de TICsOmar Issa JorgeNessuna valutazione finora

- Microprocessadores e MicrocontroladoresDocumento2 pagineMicroprocessadores e Microcontroladoresnoturno.am548Nessuna valutazione finora

- Ficha de Trabalho Nº 3 CorretaDocumento8 pagineFicha de Trabalho Nº 3 CorretasadoveiroNessuna valutazione finora

- Manual ST 4265Documento5 pagineManual ST 4265Antonio CarlosNessuna valutazione finora

- 02 Teste Avaliacao d1Documento7 pagine02 Teste Avaliacao d1Maggie VazNessuna valutazione finora

- Memoria Tecnico Descriptivo Estacion de Servicio de Gas Natural Comprimido para Expendio Al PúblicoDocumento9 pagineMemoria Tecnico Descriptivo Estacion de Servicio de Gas Natural Comprimido para Expendio Al PúblicoEdith MendezNessuna valutazione finora

- M10 - Progrmação de Microprocessadores - TrabalhoDocumento20 pagineM10 - Progrmação de Microprocessadores - TrabalhoDiogo Fernandes100% (1)

- Manual Football Manager 2012Documento133 pagineManual Football Manager 2012rafael1611Nessuna valutazione finora

- AIC - Arquitectura Interna Do Computador: Formatus - Susana NevesDocumento21 pagineAIC - Arquitectura Interna Do Computador: Formatus - Susana NevesViDuarte33Nessuna valutazione finora

- Apostila de InformáticaDocumento91 pagineApostila de InformáticaCristiane MoreiraNessuna valutazione finora

- Apostila Arm Univ Est LondrinaDocumento99 pagineApostila Arm Univ Est LondrinaCarlos Amadeu CasarimNessuna valutazione finora

- Curso de Manutenção em Controle RemotosDocumento24 pagineCurso de Manutenção em Controle Remotosmbacx100% (1)

- Apostila PDA Peteqs OriginalDocumento38 pagineApostila PDA Peteqs OriginalNaiane Reis100% (1)

- Z80 SlidesDocumento42 pagineZ80 SlidesMilton Hélder MalateNessuna valutazione finora

- Microarquitetura e A Evolução Dos ProcessadoresDocumento4 pagineMicroarquitetura e A Evolução Dos ProcessadoresLuísa Eulália100% (1)

- Detalhamento Do CPU (UC e ULA)Documento44 pagineDetalhamento Do CPU (UC e ULA)Luiz Alexandre FranzoniNessuna valutazione finora

- Tecnologias de ProcessadoresDocumento4 pagineTecnologias de ProcessadoresIrineuNessuna valutazione finora

- A Revolução Da Tecnologia Da InformaçãoDocumento2 pagineA Revolução Da Tecnologia Da InformaçãoWallyson RodrigoNessuna valutazione finora

- 18aula - Arquiteturas Paralelas PDFDocumento31 pagine18aula - Arquiteturas Paralelas PDFRaonyNascimentoNogueira100% (1)

- TDG 415 Ed BambozziDocumento10 pagineTDG 415 Ed BambozziReimaq ManutencaoNessuna valutazione finora