Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

A Phase Shifted Semi-Bridgeless Boost Power Factor Corrected Converter For Plug in Hybrid Electric Vehicle Battery Chargers

Caricato da

surok19Descrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

A Phase Shifted Semi-Bridgeless Boost Power Factor Corrected Converter For Plug in Hybrid Electric Vehicle Battery Chargers

Caricato da

surok19Copyright:

Formati disponibili

A Phase Shifted Semi-Bridgeless Boost Power Factor

Corrected Converter for Plug in Hybrid Electric

Vehicle Battery Chargers

Fariborz Musavi

Department of Research, Engineering

Delta-q Technologies Corp.

Burnaby, BC, Canada

fmusavi@delta-q.com

1

Wilson Eberle and

2

William G. Dunford

Dept. of Electrical and Computer Engineering

University of British Columbia |

1

Okanagan |

2

Vancouver

1

Kelowna, BC, Canada |

2

Vancouver, BC, Canada

1

wilson.eberle@ubc.ca |

2

wgd@ece.ubc.ca

AbstractIn this paper, a phase shifted semi-bridgeless boost

power factor corrected converter is proposed for plug in

hybrid electric vehicle battery chargers. The converter features

high efficiency at light loads and low lines, which is critical to

minimize the charger size, charging time and the amount and

cost of electricity drawn from the utility; the component count,

which reduces the charger cost; and reduced EMI. The

converter is ideally suited for automotive level I residential

charging applications.

A detailed converter description and steady state operation

analysis of this converter is presented. Experimental results of

a prototype boost converter, converting universal AC input

voltage to 400 V DC at 3.4 kW are given and the results are

compared to an interleaved boost converter to verify the proof

of concept, and analytical work reported. The results show a

power factor greater than 0.99 from 750 W to 3.4 kW, THD

less than 5% from half load to full load and a peak efficiency of

98.6 % at 240 V input and 1000 W load.

I. INTRODUCTION

A plug in hybrid electric vehicle (PHEV) is a hybrid

vehicle with a storage system that can be recharged by

connecting a plug to an external electric power source. The

charging AC outlet inevitably needs an on-board AC-DC

charger with power factor correction [1]. An on-board 3.4

kW charger could charge a depleted battery pack in PHEVs

to 95% charge in about four hours from a 240 V supply [2].

A variety of circuit topologies and control methods have

been developed for PHEV battery chargers. The two-stage

approach with cascaded PFC AC-DC and DC-DC converters

is the common architecture of choice for PHEV battery

chargers, where the power rating is relatively high, and

lithium-ion batteries are used as the main energy storage

system [3]. The single-stage approach is generally only

suitable for lead acid batteries due to large low frequency

ripple in the output current.

In the two-stage architecture, the PFC stage rectifies the

input AC voltage and transfers it into a regulated

intermediate DC link bus. At the same time, power factor

correction is achieved [4]. The boost circuit-based PFC

topology operated in CCM is employed in this study as the

main candidate for front end single-phase solutions for AC-

DC power factor corrected converters used in PHEV battery

chargers.

A. Conventional Boost Converter

The conventional boost topology shown in Fig.1 uses a

dedicated diode bridge to rectify the AC input voltage to DC,

which is then followed by the boost section. In this topology,

the output capacitor ripple current is very high [5] and is the

difference between diode current and the dc output current.

Furthermore, as the power level increases, the diode bridge

losses significantly degrade the efficiency, so dealing with

the heat dissipation in a limited area becomes problematic.

Due to these constraints, this topology is good for a low to

medium power range up to approximately 1kW. For power

levels >1kW, typically, designers parallel semiconductors in

order to deliver greater output power. The inductor volume

also becomes a problematic design issue at high power

because of permeability drops at higher load and heat

associated with core and copper losses.

Figure 1. Conventional PFC boost topology

This work has been sponsored and supported by Delta-q Technologies

Corporation.

B. Bridgeless Boost Converter

The bridgeless configuration topology shown in Fig.2

avoids the need for the rectifier input bridge yet maintains

the classic boost topology [6-13]. It is an attractive solution

for applications >1kW, where power density and efficiency

are important. The bridgeless boost converter solves the

problem of heat management in the input rectifier diode

bridge, but it introduces increased EMI [14, 15]. Another

disadvantage of this topology is the floating input line with

respect to the PFC stage ground, which makes it impossible

to sense the input voltage without a low frequency

transformer or an optical coupler. Also in order to sense the

input current, complex circuitry is needed to sense the

current in the MOSFET and diode paths separately, since the

current path does not share the same ground during each

half-line cycle [8, 16].

Figure 2. Bridgeless PFC boost topology

C. Interleaved Boost Cconverter

The interleaved boost converter shown in Fig.3 is simply

two boost converters in parallel operating 180 out of phase

[20-22]. The input current is the sum of the two inductor

currents. Because the inductors ripple currents are out of

phase, they tend to cancel each other and reduce the input

ripple current caused by the boost switching action. The

interleaved boost converter has the advantage of paralleled

semiconductors. Furthermore, by switching 180 out of

phase, it doubles the effective switching frequency and

introduces smaller input current ripple, so the input EMI

filter can be smaller [23-25]. This converter also has reduced

output capacitor high frequency ripple, but it still has the

problem of heat management for the input diode bridge

rectifiers.

Figure 3. Interleaved PFC boost topology

In the following section, a new phase shifted semi-

bridgeless boost PFC converter is proposed in order to

improve overall efficiency of the AC-DC PFC converter,

while maintaining all the advantages of the existing

solutions.

II. PHASE SHIFTED SEMI-BRIDGELESS BOOST TOPOLOGY

The phase shifted semi-bridgeless topology shown in

Fig.4 is proposed as a solution to address the problems

outlined in section I for the conventional boost, bridgeless

boost and interleaved boost topologies. This topology

features high efficiency at light loads and low lines, which is

critical to minimize the charger size, charging time and the

amount and cost of electricity drawn from the utility; the

component count, which reduces the charger cost; and

reduced EMI. The converter is ideally suited for automotive

level I residential charging applications in North America

where the typical supply is limited to 120V and 1.44kVA.

The proposed topology introduces two more slow diodes

(Da and Db) to the bridgeless configuration to link the

ground of the PFC to the input line. However, the current

does not always return through these diodes, so their

associated conduction losses are low. This occurs since the

inductors exhibit low impedance at the line frequency, a

large portion of the current flows through the FET intrinsic

body diodes. Also the gating signals for FETs are 180 out of

phase.

A detailed converter description and steady-state

operation analysis is given in the following section.

Figure 4. Phase shifted semi-bridgeless PFC boost topology

III. OPERATING PRINCIPLE AND STEADY-STATE

ANALYSIS

To analyze the circuit operation, the input line cycle has

been separated into the positive and negative half-cycles as

explained in sub-sections A and B that follow. In addition,

the detailed circuit operation depends on the duty cycle.

Positive half-cycle operation analysis is provided for D > 0.5

in sub-section C and D < 0.5 in sub-section D.

A. Positive Half-Cycle Operation

Referring to Fig. 4, during the positive half-cycle, when

the AC input voltage is positive, Q1 turns on and current

flows through L1 and Q1 and continues through Q2 and then

L2, returning to the line while storing energy in L1 and L2.

When Q1 turns off, energy stored in L1 and L2 is released as

current flows through D1, through the load and returns

through the body diode of Q2/partially through Db back to

the input.

B. Negative Half-Cycle Operation

Referring to Fig. 4, during the negative half-cycle, when

the AC input voltage is negative, Q2 turns on and current

flows through L2 and Q2 and continues through Q1 and then

L1, returning to the line while storing energy in L2 and L1.

When Q2 turns off, energy stored in L2 and L1 is released as

current flows through D2, through the load and returns split

between the body diode of Q1 and Da back to the input.

C. Detailed Positive Half-Cycle Operation and Analysis for

D > 0.5

The detailed operation of the proposed converter depends

on the duty cycle. During any half-cycle, the converter duty

cycle is either greater than 0.5 (when the input voltage is

smaller than half of output voltage) or smaller than 0.5

(when the input voltage is greater than half of output

voltage). The three unique operating interval circuits of the

proposed converter are provided in Fig. 5 to Fig. 7 for duty

cycles larger than 0.5 during the positive half-cycle.

Figure 5. Interval 1and 3: Q1 and Q2 are ON

Figure 6. Interval 2: Q1 ON, body diode of Q2 conducting

Figure 7. Interval 4: Q1 OFF and Q2 ON

Waveforms of the proposed converter during positive

half-cycle operation with D>0.5 are shown in Fig. 8. The

intervals of operation are explained as follows. In addition,

the ripple current components are derived, enabling

calculation of the input ripple current, which provides design

guidance to meet the required input current ripple standard.

Figure 8. Phase shifted semi-bridgeless boost converter steady-state

Waveforms at D > 0.5

Interval 1 [t

0

-t

1

]: At t

0

, Q1/ Q2 are on, as shown in Fig.5.

During this interval, the current in series inductances L1 and

L2 increases linearly and stores the energy in these inductors.

The energy stored in Co provides energy to the load. The

ripple currents in Q1 and Q2 are the same as the current in

series inductances L1 and L2, where the ripple current is

given by:

I

In

=

1

L

1

+L

2

v

I

(B -

1

2

)T

s

(1)

Interval 2 [t

1

-t

2

]: At t

1

, Q1 is on and Q2 is off, as shown

in Fig.6. During this interval, the current in series

inductances L1 and L2 continues to increase linearly and

store the energy in these inductors. The energy stored in Co

provides the load energy. The ripple currents in Q1 and body

diode of Q2 are the same as the current in series inductances

L1 and L2, where the ripple current is given by:

I

In

=

1

L

1

+L

2

v

I

(1 - B)T

s

(2)

Interval 3 [t

2

-t

3

]: At t

2

, Q1/Q2 are on again, and interval

1 is repeated, as shown in Fig. 5. During this interval, the

current in series inductances L1 and L2 increases linearly

and stores the energy in these inductors. The ripple currents

in Q1 and Q2 are the same as the ripple current in series

inductances L1 and L2, as shown in equation (1).

Interval 4 [t

3

-t

4

]: At t

3

, Q1 is off and Q2 is on, as shown I

Fig. 7. During this interval, the energy stored in L1 and L2 is

released to the output through L1, D1, Q2 and L2. The ripple

currents in D1 and Q2 are the same as the ripple currents in

L1 and L2:

I

n

=

1

L

1

+L

2

(:

- I

o

)(1 -)I

s

(3)

Figure 9. Interval 1and 3: Q1 and Q2 are OFF, body diode of Q2

conducting

Figure 10. Interval 2: Q1 ON, body diode of Q2 conducting

Figure 11. Interval 4: Q1 OFF and Q2 ON

D. Detailed Positive Half-Cycle Operation and Analysis for

D < 0.5

The three unique operating interval circuits of the

proposed converter are given in Fig. 9 to Fig. 11 for duty

cycles smaller than 0.5 during the positive half-cycle. The

waveforms of the proposed converter during these conditions

are shown in Fig. 12. The intervals of operation are

explained as follows.

Figure 12. Phase shifted semi-bridgeless boost converter steady-state

waveforms at D < 0.5

Interval 1 [t

0

-t

1

]: At t

0

, Q1/ Q2 are off, as shown in Fig.9.

During this interval, the energy stored in L1 and L2 are

released to the output through L1, D1, body diode of Q2 and

L2. The ripple currents in D1 and body diode of Q2 are the

same as the ripple currents in L1 and L2:

I

In

=

1

L

1

+L

2

(:

- I

o

)(

1

2

- B)T

s

(4)

Interval 2 [t

1

-t

2

]: At t

1

, Q1 is on and Q2 is off, as shown

in Fig.10. During this interval, the current in series

inductances L1 and L2 continues to increase linearly and

store the energy in these inductors. The energy stored in Co

provides energy to the load. The ripple currents in Q1 and

the body diode of Q2 are the same as the current in series

inductances L1 and L2, where the ripple current is given by:

I

In

=

1

L

1

+L

2

v

I

BT

s

(5)

Interval 3 [t

2

-t

3

]: At t

2

, Q1/Q2 are off again, and interval

1 is repeated, as shown in Fig. 9. During this interval, the

current in series inductances L1 and L2 increases linearly

and stores the energy in these inductors. The ripple currents

in D1 and body diode of Q2 are the same as the ripple

current in series inductances L1 and L2, as shown in

equation (1).

Interval 4 [t

3

-t

4

]: At t

3

, Q1 is off and Q2 is on, as shown I

Fig. 11. During this interval, the energy stored in L1 and L2

is released to the output through L1, D1, Q2 and L2. The

ripple currents in D1 and Q2 are the same as the ripple

currents in L1 and L2:

I

n

=

1

L

1

+L

2

(:

- I

o

)I

s

(6)

The operation of converter during the negative input

voltage half-cycle is similar to the operation of converter

during the positive input voltage half-cycle.

IV. LOSS EVALUATION

The estimated loss distribution of the semiconductors is

provided in Fig. 13 at 70 kHz switching frequency, 240V

input and 3300W load for benchmark conventional boost and

interleaved boost converters and the proposed phase shifted

semi-bridgeless boost converter. The currents in regular

diodes Da and Db were assumed to be split with the current

going through intrinsic body diodes for phase shifted semi-

bridgeless topology. The regular diodes in input bridge

rectifiers have the largest share of losses among the

topologies with the input bridge rectifier. The phase shifted

semi-bridgeless topology nearly eliminates this large loss

component (~30W). However, the tradeoff is that the FET

losses are higher and the intrinsic body diodes of FETs

conduct, producing new losses (~8W). The fast diodes in the

conventional and interleaved PFC have slightly lower power

losses, since the boost RMS current is higher in these

topologies.

Figure 13. Comparison of the estimated loss distribution in the

semiconductors at 70kHz switching frequency, 240V input, 3300W load at

400V

Overall the FETs are under slightly more stress in phase

shifted semi-bridgeless topology, but the total loss for the

proposed phase shifted semi-bridgeless boost are 17% lower

than the benchmark conventional boost and 7% lower than

the interleaved boost . Since the benchmark converter bridge

rectifier losses are large, it is expected that phase shifted

semi-bridgeless boost converter should have the lowest

losses among the topologies investigated. Additionally, it is

noted that the losses in the input bridge rectifiers are 63% of

total losses in the conventional PFC converter and 71% of

total losses in the interleaved PFC converter. Therefore,

eliminating the input bridge in PFC converters is justified

despite that the introduction of new losses.

V. EXPERIMENTAL RESULTS

Prototypes of a phase shifted bridgeless boost converter

and an interleaved boost converter were built to verify the

proof-of-concept and analytical work presented in this paper

and to benchmark the proposed converter. The devices used

in experimental prototypes are provided in Table 1.

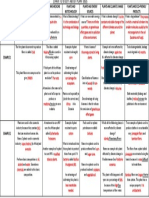

TABLE I. DEVICES/COMPONENTS USED IN EXPERIMENTAL PROTOTYPES

Topology

Components Used in Prototype Unit Head

Device Part # / Value # of Devices

P

h

a

s

e

S

h

i

f

t

e

d

S

e

m

i

-

b

r

i

d

g

e

l

e

s

s

P

F

C

c

o

n

v

e

r

t

e

r

Regular Diode

25ETS08S 2

Fast Diode

IDB06S60C 2

MOSFET

IPB60R099CP 2

Inductors

400 H 2

I

n

t

e

r

l

e

a

v

e

d

P

F

C

c

o

n

v

e

r

t

e

r

Regular Diode

25ETS08S 4

Fast Diode

IDB06S60C 2

MOSFET

IPB60R099CP 2

Inductors

400 H 2

Pictures of the proposed phase shifted bridgeless boost

prototype are provided in Fig. 14. It consists of a control

board, a capacitor bank of 820 F and an IMS power board

attached to a heatsink with the PFC inductors.

Figure 14. Top: control board, Bottom: power board

3

0

.

0

W

6

.

9

W

1

0

.

8

W

0

.

0

W

4

7

.

7

W

3

0

.

0

W

6

.

9

W

5

.

4

W

0

.

0

W

4

2

.

3

W

4

.

1

9

.

8

2

1

.

6

4

.

1

3

9

.

4

0

10

20

30

40

50

60

R

e

g

u

l

a

r

D

i

o

d

e

s

F

a

s

t

D

i

o

d

e

s

F

E

T

s

I

n

t

r

i

n

s

i

c

B

o

d

y

D

i

o

d

e

s

T

o

t

a

l

L

o

s

s

e

s

P

o

w

e

r

L

o

s

s

e

s

(

W

)

Semiconductor Losses

Conventional Boost

Interleaved Boost

Phase Shifted Semi-Bridgeless Boost

The experimental efficiency of the phase shifted

bridgeless boost converter and benchmark interleaved boost

converter is provided in Fig. 15 for 240V input and Fig. 17

for 120V input at 70 kHz switching frequency and 400 V

output. Loss reduction curves as a function of output power

are provided in Fig. 16 and Fig. 18 for 240V and 120V input,

respectively.

Figure 15. Efficiency as a function of output power at Vin = 240V,

Vo=400V and 70kHz switching frequency

Figure 16. Loss reduction as a function of output power at Vin = 240V,

Vo=400V and 70kHz switching frequency

Figure 17. Efficiency as a function of output power at Vin = 120V,

Vo=400V and 70kHz switching frequency

Figure 18. Loss reduction as a function of output power at Vin = 120V,

Vo=400V and 70kHz switching frequency

From the results, it is noted that proposed semi-bridgeless

PFC converter achieves a peak efficiency of 98.6% at 1 kW

output power. Additionally, the light load efficiency of the

proposed converter is significantly better than that of the

interleaved PFC due to the absence of input bridge rectifier.

However, as the load increases, the efficiency drops due to

additional heat dissipation in the intrinsic body diodes of the

FETs.

Figure 19. THD as a function of output power at Vin = 120 V and 240V,

Vo=400V and 70kHz switching frequency

Figure 20. Power Factor as a function of output power at Vin = 120 V and

240V, Vo=400V and 70kHz switching frequency

94

95

96

97

98

99

100

0

5

0

0

1

0

0

0

1

5

0

0

2

0

0

0

2

5

0

0

3

0

0

0

3

5

0

0

E

f

f

i

c

i

e

n

c

y

(

%

)

Output Power (W)

Interleaved PFC Converter

Phase Shifted Semi-

Bridgeless PFC Converter

0

10

20

30

40

50

60

70

0

5

0

0

1

0

0

0

1

5

0

0

2

0

0

0

2

5

0

0

3

0

0

0

3

5

0

0

L

o

s

s

R

e

d

u

c

t

i

o

n

(

%

)

Output Power (W)

Loss Reduction for PFC

Converters at Vin = 240 V

91

92

93

94

95

96

97

98

0

2

0

0

4

0

0

6

0

0

8

0

0

1

0

0

0

1

2

0

0

1

4

0

0

1

6

0

0

1

8

0

0

E

f

f

i

c

i

e

n

c

y

(

%

)

Output Power (W)

Interleaved PFC Converter

Phase Shifted Semi-

Bridgeless PFC Converter

0

10

20

30

40

50

60

70

0

2

0

0

4

0

0

6

0

0

8

0

0

1

0

0

0

1

2

0

0

1

4

0

0

1

6

0

0

1

8

0

0

L

o

s

s

R

e

d

u

c

t

i

o

n

(

%

)

Output Power (W)

Loss Reduction for PFC

Converters at Vin = 120 V

0

5

10

15

20

25

30

35

40

45

0

5

0

0

1

0

0

0

1

5

0

0

2

0

0

0

2

5

0

0

3

0

0

0

3

5

0

0

T

H

D

(

%

)

Output Power (W)

Vin=240

Vin=120

0.84

0.86

0.88

0.9

0.92

0.94

0.96

0.98

1

1.02

0

5

0

0

1

0

0

0

1

5

0

0

2

0

0

0

2

5

0

0

3

0

0

0

3

5

0

0

P

o

w

e

r

f

a

c

t

o

r

Output Power (W)

Vin=240

Vin=120

Figure 21. Harmonics orders at Vin = 120 V and 240V, compared against

EN61000-3-2 standard.

In order to verify the quality of the input current, the input

current THD is shown in Fig.19. The power factor and

harmonic orders are given and compared with EN 61000-3-2

standard in Fig.20 and 21. It is noted that mains current THD

is less than 5% from 50% load to full load and it is compliant

to IEC 6100-3-2 (Fig. 19 and Fig. 21). The converter power

factor is shown over entire load range for 120 and 240V

input in Fig. 20. The power factor is greater than 0.99 from

50% load to full load.

Experimental waveforms from the proposed converter

prototype are provided in Fig. 22 through Fig. 26. The input

current, input voltage and output voltage are given in Fig. 22.

As it can be seen, the input current is in phase with the input

voltage and has a sinusoidal shape. Additionally, there is a

low frequency ripple on output voltage, which is inversely

proportional to the value of PFC bus output capacitors.

In Fig. 23, the inductor current is provided in addition to

the above mentioned waveforms from Fig. 22. It is noted that

during the positive half-cycle, the inductor current is the

same as input current. However, during the negative half-

cycle, the input current is partially flowing through slow

diodes, Da and Db.

Figure 22. Inut current, input voltage and output voltage.

Ch1= Vo 100V/div. Ch2= Vin 100V/div. Ch4= Iin 10A/div.

Figure 23. Inut current, inducotr current, input voltage and output voltage.

Ch1= Vo 100V/div. Ch2= Vin 100V/div. Ch3= IL1 10A/div. Ch4= Iin

10A/div.

Figure 24. Inductor current, input current and sensed FET current.

Ch1= Sensed IQ1 2V/div. Ch3= IL1 / IDb 10A/div. Ch4= Iin 10A/div

Figure 25. Gating signal, Inductor and sensed FET current for D < 0.5

Ch1= Vg 10V/div. Ch2= IQ1 2V/div. Ch3= IL1 10A/div

In Fig.24 the inductor current, input current and current

sensed in the FET through a current transformer are given.

0

0.5

1

1.5

2

2.5

3579

1

1

1

3

1

5

1

7

1

9

2

1

2

3

2

5

2

7

2

9

3

1

3

3

3

5

3

7

3

9

A

m

p

l

i

t

u

d

e

(

A

)

Harmonics Order

EN 61000-3-2 Class D Limits (A)

Amplitude (A) Vin = 120 V

Amplitude (A) Vin = 240 V

Input Voltage

Output Voltage

Input Current

Input Voltage

Output Voltage

Input Current

Inductor

Current

Input

Current Inductor

Current

Sensed FET Current

Inductor Current

Gating Signal

Sensed FET

Current

The gating signals, sensed FET current and the inductor

current are provided for duty cycles less than 0.5, Fig 25, and

greater than 0.5, Fig. 26. These waveforms match the

theoretical models.

Figure 26. Gating signal, Inductor and sensed FET current for D > 0.5

Ch1= Vg 10V/div. Ch2= IQ1 2V/div. Ch3= IL1 10A/div

VI. CONCLUSIONS

A new high performance phase shifted semi-bridgeless

AC-DC Boost converter topology has been presented in this

paper for the front-end AC-DC converter in PHEV battery

chargers. The proposed converter features high efficiency at

light loads and low lines, which is critical to minimize the

charger size, charging time and the amount and cost of

electricity drawn from the utility; the component count,

which reduces the charger cost; and reduced EMI. The

converter is ideally suited for automotive level I residential

charging applications in North America where the typical

supply is limited to 120V and 1.44kVA.

An analysis and performance characteristics are presented.

A breadboard converter circuit has been built to verify the

proof-of-concept. The theoretical waveforms were compared

with the results taken from prototype unit. Additionally, key

experimental waveforms were provided and input current

harmonics at each harmonic order were compared more

explicitly with the IEC 6100-3-2 standard limits.

Experimental results demonstrate that the mains current

THD is smaller than 5% from 50% load to full load and the

converter is compliant with the IEC 6100-3-2 standard. The

converter power factor was also provided for full power

range at 120 and 240V input. The power factor is greater

than 0.99 from 50% load to full load. The proposed

converter achieves a peak efficiency of 98.6 % at 240 V

input and 1 kW output power.

REFERENCES

[1] Young-Joo Lee; Khaligh, A.; Emadi, A.; "Advanced Integrated

Bidirectional AC-DC and DC-DC Converter for Plug-In Hybrid

Electric Vehicles," IEEE Trans. on Vehicular Technology, vol. 58,

pp. 3970 - 3980 2009.

[2] K. Morrow, D. Karner, and J. Francfort, "Plug-in Hybrid Electric

Vehicle Charging Infrastructure Review," U.S. Departent of Energy -

Vehicle Technologies Program, 2008.

[3] Petersen, L.; Andersen, M.; "Two-Stage Power Factor Corrected

Power Supplies: The Low Component-Stress Approach " in Proc.

IEEE Applied Power Electronics Conference and Exposition, APEC.

vol. 2, 2002, pp. 1195 - 1201.

[4] Singh, B.; Singh, B.N.; Chandra, A.; Al-Haddad, K.; Pandey, A.;

Kothari, D.P.; "A Review of Single-Phase Improved Power Quality

AC-DC Converters," IEEE Trans. on Industrial Electronics, vol. 50,

pp. 962 - 981, 2003.

[5] Dehong Xu; Jindong Zhang; Weiyun Chen; Jinjun Lin; Lee, F.C.;

"Evaluation of output filter capacitor current ripples in single phase

PFC converters " in Proc. IEEE Power Conversion Conference, PCC.

vol. 3 Osaka, Japan, 2002, pp. 1226 - 1231.

[6] Lu, B.; Brown, R.; Soldano, M.; "Bridgeless PFC implementation

using one cycle control technique," in Proc. IEEE Applied Power

Electronics Conference and Exposition, APEC, vol. 2, 2005, pp. 812 -

817.

[7] Petrea, C.; Lucanu, M.; "Bridgeless Power Factor Correction

Converter Working at High Load Variations," in Proc. International

Symposium on Signals, Circuits and Systems, ISSCS. vol. 2, 2007, pp.

1 - 4

[8] U. Moriconi, "A Bridgeless PFC Configuration based on L4981 PFC

Controller ": STMicroelectronics Application Note AN1606, 2002.

[9] J. M. Hancock, "Bridgeless PFC Boosts Low-Line Efficiency,"

Infineon Technologies, 2008.

[10] Yungtaek Jang; Jovanovic, M.M.; Dillman, D.L.; "Bridgeless PFC

boost rectifier with optimized magnetic utilization," in Proc. IEEE

Applied Power Electronics Conference and Exposition, APEC, 2008,

pp. 1017 1021.

[11] Yungtaek Jang; Jovanovic, M.M.; "A Bridgeless PFC Boost Rectifier

With Optimized Magnetic Utilization," IEEE Trans. on Power

Electronics, vol. 24, pp. 85 - 93 2009.

[12] Woo-Young Choi; Jung-Min Kwon; Eung-Ho Kim; Jong-Jae Lee;

Bong-Hwan Kwon; "Bridgeless Boost Rectifier With Low

Conduction Losses and Reduced Diode Reverse-Recovery Problems,"

IEEE Trans. on Industrial Electronics, vol. 54, pp. 769 780, April

2007.

[13] Huber, L.; Yungtaek Jang; Jovanovic, M.M.; "Performance

Evaluation of Bridgeless PFC Boost Rectifiers," IEEE Trans. on

Power Electronics, vol. 23, pp. 1381 - 1390 2008.

[14] Pengju Kong; Shuo Wang; Lee, F.C.; "Common Mode EMI Noise

Suppression for Bridgeless PFC Converters," IEEE Trans. on Power

Electronics, vol. 23, pp. 291 297, January 2008 2008.

[15] Baur, T.; Reddig, M.; Schlenk, M.; "Line-conducted EMI-behaviour

of a High Efficient PFC-stage without input rectification," Infineon

Technology Application Note, 2006.

[16] Frank, W.; Reddig, M.; Schlenk, M.; "New control methods for

rectifier-less PFC-stages," in Proc. EEE International Symposium on

Industrial Electronics. vol. 2, 2005, pp. 489 - 493

[17] M. OLoughlin;, "An Interleaved PFC Preregulator for High-Power

Converters." vol. Topic 5: Texas Instrument Power Supply Design

Seminar, 2007, pp. 5-1, 5-14.

[18] Yungtaek Jang; Jovanovic, M.M.; "Interleaved Boost Converter With

Intrinsic Voltage-Doubler Characteristic for Universal-Line PFC

Front End," IEEE Trans. on Power Electronics, vol. 22, pp. 1394

1401, July 2007.

[19] Balogh, L.; Redl, R.; "Power-factor correction with interleaved boost

converters in continuous-inductor-current mode," in Proc. IEEE

Applied Power Electronics Conference and Exposition, 1993, pp. 168

- 174.

Inductor Current

Gating Signal

Sensed FET Current

Potrebbero piacerti anche

- Active Power Factor Correction Technique For Single Phase Full Bridge RectifierDocumento6 pagineActive Power Factor Correction Technique For Single Phase Full Bridge RectifierAnand KumarNessuna valutazione finora

- A High-Performance ChargerDocumento11 pagineA High-Performance ChargerCR AthiraNessuna valutazione finora

- High Power Factor Boost Converter With Bridgeless Rectifier: Kavithamani K Vigneswari SDocumento6 pagineHigh Power Factor Boost Converter With Bridgeless Rectifier: Kavithamani K Vigneswari SInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Ijert: Power Stress Reduction in Single-Stage Power Factor Correction by AC/DC Fly Back ConverterDocumento9 pagineIjert: Power Stress Reduction in Single-Stage Power Factor Correction by AC/DC Fly Back ConverterAnjali SharmaNessuna valutazione finora

- Power Factor Improvement With High Efficiency ConvertersDocumento7 paginePower Factor Improvement With High Efficiency ConvertersAnjali SharmaNessuna valutazione finora

- A New Single-Phase Single-Stage Three-Level Power Factor Correction AC-DC ConverterDocumento12 pagineA New Single-Phase Single-Stage Three-Level Power Factor Correction AC-DC Convertersurya_v988Nessuna valutazione finora

- Bridgeless High-Power-Factor Buck Converter: Yungtaek Jang, Senior Member, IEEE, and Milan M. Jovanovic, FellowDocumento16 pagineBridgeless High-Power-Factor Buck Converter: Yungtaek Jang, Senior Member, IEEE, and Milan M. Jovanovic, FellowSpk Sudhin100% (1)

- AC/DC Converter With Active Power Factor Correction Applied To DC Motor DriveDocumento9 pagineAC/DC Converter With Active Power Factor Correction Applied To DC Motor DriveIJERDNessuna valutazione finora

- Musavi2010 GoodDocumento6 pagineMusavi2010 GoodJie99Nessuna valutazione finora

- A Three-Level Quasi-Two-Stage Three-Phase PFC ConverterDocumento10 pagineA Three-Level Quasi-Two-Stage Three-Phase PFC ConverterjohnsonNessuna valutazione finora

- Single Stage PFCconverterDocumento10 pagineSingle Stage PFCconvertersquall8712Nessuna valutazione finora

- Control of DC Drive by Bridgeless PFC Boost TopologyDocumento3 pagineControl of DC Drive by Bridgeless PFC Boost TopologyDivya ShriNessuna valutazione finora

- CHAPTER ThreeDocumento20 pagineCHAPTER ThreeAung MyatNessuna valutazione finora

- Ijet V2i2p17Documento9 pagineIjet V2i2p17International Journal of Engineering and TechniquesNessuna valutazione finora

- High Efficiency and High Power Factor Single-Stage Balanced Forward-Flyback ConverterDocumento6 pagineHigh Efficiency and High Power Factor Single-Stage Balanced Forward-Flyback ConverterKarthik KumarNessuna valutazione finora

- Topic Assignment14Documento6 pagineTopic Assignment14cuongakamarineNessuna valutazione finora

- Three-Port Rectifier-Based AC-DC Power Converters With Sigma Architecture and Reduced Conversion StagesDocumento10 pagineThree-Port Rectifier-Based AC-DC Power Converters With Sigma Architecture and Reduced Conversion StagesifyNessuna valutazione finora

- Analysis of Different Topologies For Active Power Factor CorrectionDocumento8 pagineAnalysis of Different Topologies For Active Power Factor Correctionnnpatel1990Nessuna valutazione finora

- Continuous Conduction Mode of Bridgeless SEPIC Power Factor Correction RectifierDocumento4 pagineContinuous Conduction Mode of Bridgeless SEPIC Power Factor Correction Rectifiersindhuja selvamNessuna valutazione finora

- Super High Gain DC DC Converter EpiphanyDocumento31 pagineSuper High Gain DC DC Converter EpiphanyForbeniusNessuna valutazione finora

- A New Single-Phase Single-Stage Three-LevelDocumento12 pagineA New Single-Phase Single-Stage Three-LevelGururaj BandaNessuna valutazione finora

- Power ConverterDocumento9 paginePower ConverterSrini VasuluNessuna valutazione finora

- Design Bi-Directional Charger For Phev Application: Chaudhari Tejal A., Bariya Chetan K., Upadhyay Chetan DDocumento6 pagineDesign Bi-Directional Charger For Phev Application: Chaudhari Tejal A., Bariya Chetan K., Upadhyay Chetan Dmohd786azharNessuna valutazione finora

- A New Approach For High Efficiency Buck-Boost DC/DC Converters Using Series CompensationDocumento7 pagineA New Approach For High Efficiency Buck-Boost DC/DC Converters Using Series CompensationAswin MathewNessuna valutazione finora

- High-Efficiency, High Step-Up DC-DC ConvertersDocumento9 pagineHigh-Efficiency, High Step-Up DC-DC ConvertersC_hakan_CNessuna valutazione finora

- An Advanced Two Level Double Dual Boost ConverterDocumento5 pagineAn Advanced Two Level Double Dual Boost ConverterGRD JournalsNessuna valutazione finora

- Power ConverterDocumento11 paginePower ConverterNaga Sai KiranNessuna valutazione finora

- Single-Stage Bridgeless AC-DC PFC Converter Using A Lossless Passive Snubber and Valley SwitchingDocumento9 pagineSingle-Stage Bridgeless AC-DC PFC Converter Using A Lossless Passive Snubber and Valley SwitchingAshwin Kumar JNessuna valutazione finora

- A Zero-Voltage Switching Full-Bridge DC - DC ConverterDocumento8 pagineA Zero-Voltage Switching Full-Bridge DC - DC Convertersuresh100% (1)

- A New Method For DC-AC Conversion Using Simplified Multilevel Inverter - Design and Analysis Using PSIM 1. V.Gowri Shankar, 2.C.UdhayashankarDocumento7 pagineA New Method For DC-AC Conversion Using Simplified Multilevel Inverter - Design and Analysis Using PSIM 1. V.Gowri Shankar, 2.C.UdhayashankarraghuevmNessuna valutazione finora

- Single-Ended High-Efficiency Step-Up Converter Using The Isolated Switched-Capacitor CellDocumento13 pagineSingle-Ended High-Efficiency Step-Up Converter Using The Isolated Switched-Capacitor CellHarjinder SinghNessuna valutazione finora

- Bridgeless AC-DC Buck-Boost Converter WithDocumento5 pagineBridgeless AC-DC Buck-Boost Converter WithJishnu VenugopalNessuna valutazione finora

- Modified Ac-Dc Single-Stage Converters: Gerry Moschopoulos, Yan Liu, and Sondeep BassanDocumento11 pagineModified Ac-Dc Single-Stage Converters: Gerry Moschopoulos, Yan Liu, and Sondeep BassanAnjali SharmaNessuna valutazione finora

- 2002apr08 Icd Amd Pow TacDocumento9 pagine2002apr08 Icd Amd Pow TacMihaela CaciumarciucNessuna valutazione finora

- An Improved Battery Charger For Electric VehicleDocumento8 pagineAn Improved Battery Charger For Electric VehicleSanyog Jayant PohareNessuna valutazione finora

- 358 2132 1 PBDocumento7 pagine358 2132 1 PBM UMAR ABBASINessuna valutazione finora

- Development of New AC To DC Converters For EHVDocumento5 pagineDevelopment of New AC To DC Converters For EHVMouliNessuna valutazione finora

- Design of A Single-Switch DC-DC Converter For PV-Battery Powered Pump SystemDocumento6 pagineDesign of A Single-Switch DC-DC Converter For PV-Battery Powered Pump SystemRaveendhra IitrNessuna valutazione finora

- Karthikeyan 0th ReviewDocumento2 pagineKarthikeyan 0th ReviewSibi Ibi'sNessuna valutazione finora

- A New Approach For High Efficiency Buck-Boost DC-DC Converters Using Series CompensationDocumento6 pagineA New Approach For High Efficiency Buck-Boost DC-DC Converters Using Series CompensationBishoo ShenoudaNessuna valutazione finora

- Soft Switched High Step-Up DC-DC Converter For Automotive ApplicationDocumento4 pagineSoft Switched High Step-Up DC-DC Converter For Automotive Applicationkarthi.r.tNessuna valutazione finora

- A High Efficiency Bridgeless Flyback PFC Converter For Adapter ApplicationDocumento5 pagineA High Efficiency Bridgeless Flyback PFC Converter For Adapter ApplicationAshwin Kumar JNessuna valutazione finora

- A Modified SEPIC Converter For High Power Factor Rectifier and Universal Input Voltage ApplicationsDocumento12 pagineA Modified SEPIC Converter For High Power Factor Rectifier and Universal Input Voltage ApplicationsBritto TigerNessuna valutazione finora

- Buck-Boost PWM Converters Having Two Independently Controlled SwitchesDocumento6 pagineBuck-Boost PWM Converters Having Two Independently Controlled SwitchesBals BalaNessuna valutazione finora

- A DC-DC Converter With High Voltage Gain and Two Input Boost StagesDocumento10 pagineA DC-DC Converter With High Voltage Gain and Two Input Boost Stagesnadeemq_0786Nessuna valutazione finora

- A Novel Single Switch High Gain DC-DC ConverterDocumento6 pagineA Novel Single Switch High Gain DC-DC ConverterAbhishek MeenaNessuna valutazione finora

- Basheer UpdatedDocumento39 pagineBasheer UpdatedAhmad ShaikNessuna valutazione finora

- Matteini PHD Part1Documento15 pagineMatteini PHD Part1Anonymous EnggrUsmNessuna valutazione finora

- Lawler Trans Pe Jan 2004 PDFDocumento12 pagineLawler Trans Pe Jan 2004 PDFAshok KumarNessuna valutazione finora

- A Unity Power Factor Converter Using HalfDocumento14 pagineA Unity Power Factor Converter Using HalfLivia Faria PeresNessuna valutazione finora

- A Step Down Transformerless Single Switch Integerated Buck and Buck-Boost ConverterDocumento7 pagineA Step Down Transformerless Single Switch Integerated Buck and Buck-Boost ConverterMogal RajeshNessuna valutazione finora

- Advanced Inter Grated Bidirectional ACDC and DCDCDocumento11 pagineAdvanced Inter Grated Bidirectional ACDC and DCDCMadanda RichardNessuna valutazione finora

- CanonicalDocumento7 pagineCanonicalTechnos_IncNessuna valutazione finora

- Nonisolated High Step-Up Boost Converter Integrated With Sepic ConverterDocumento10 pagineNonisolated High Step-Up Boost Converter Integrated With Sepic ConverterShirlyNessuna valutazione finora

- A Buck-or-Boost Converter Module With Embedded Inductor and Fast Current LimitDocumento10 pagineA Buck-or-Boost Converter Module With Embedded Inductor and Fast Current LimitVeeraiah BodduNessuna valutazione finora

- High Power Topology: "AlbacomDocumento7 pagineHigh Power Topology: "AlbacomRaveendhra IitrNessuna valutazione finora

- First Quadrant Single Phase Ac To DC Converter Semiconverter Separately Excited DC MotorDocumento9 pagineFirst Quadrant Single Phase Ac To DC Converter Semiconverter Separately Excited DC MotorzaidNessuna valutazione finora

- International Journal of Engineering Research and Development (IJERD)Documento9 pagineInternational Journal of Engineering Research and Development (IJERD)IJERDNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Valutazione: 2.5 su 5 stelle2.5/5 (3)

- I.V Murali Krishna and Valli Manickam (Auth.) - Environmental Management. Science and Engineering For Industry (2017, Butterworth-Heinemann)Documento10 pagineI.V Murali Krishna and Valli Manickam (Auth.) - Environmental Management. Science and Engineering For Industry (2017, Butterworth-Heinemann)Richard Solis Toledo0% (1)

- Circuit BreakerDocumento10 pagineCircuit BreakermeraatNessuna valutazione finora

- APsystems Microinverter DS3 L DS3 DS3 H For Tunisia Datasheet - Rev1.4 - 2023 06 16Documento2 pagineAPsystems Microinverter DS3 L DS3 DS3 H For Tunisia Datasheet - Rev1.4 - 2023 06 16adveosNessuna valutazione finora

- Catalog-EQ - Kingsbury BearingDocumento42 pagineCatalog-EQ - Kingsbury BearingZohaib AnserNessuna valutazione finora

- Wind Turbine DesignDocumento7 pagineWind Turbine DesignJia Le ChowNessuna valutazione finora

- Module 1 ENERGY CONVERSIONDocumento12 pagineModule 1 ENERGY CONVERSIONJeremy MacalaladNessuna valutazione finora

- Voltage Regulation On Micro GridDocumento61 pagineVoltage Regulation On Micro GridkarthikNessuna valutazione finora

- Nano Solar Utility Panel WhitepaperDocumento14 pagineNano Solar Utility Panel WhitepaperShawn ScullyNessuna valutazione finora

- FormulasDocumento9 pagineFormulasShankar JhaNessuna valutazione finora

- Start-Up Costs of Thermal Power Plants in Markets With Increasing Shares of Variable Renewable GenerationDocumento6 pagineStart-Up Costs of Thermal Power Plants in Markets With Increasing Shares of Variable Renewable GenerationIkenna OnyegbadueNessuna valutazione finora

- Entrepreneurial Skill Development: A Case Study of The Design and Construction of Charcoal Baking OvenDocumento4 pagineEntrepreneurial Skill Development: A Case Study of The Design and Construction of Charcoal Baking OvenInnovative Research PublicationsNessuna valutazione finora

- EnergyNext Vol 03 Issue 8 Aug 2013Documento68 pagineEnergyNext Vol 03 Issue 8 Aug 2013IndiaNextNessuna valutazione finora

- Adjustable Tilt CMP Mounting KitDocumento2 pagineAdjustable Tilt CMP Mounting KitBharat KaushikNessuna valutazione finora

- University of San Agustin: Chemical Engineering DepartmentDocumento43 pagineUniversity of San Agustin: Chemical Engineering DepartmentReynee Shaira Lamprea MatulacNessuna valutazione finora

- Soal Excel TerakhirDocumento63 pagineSoal Excel TerakhirAndika njayNessuna valutazione finora

- Answers Chart Plants Act 3Documento1 paginaAnswers Chart Plants Act 3api-279490884Nessuna valutazione finora

- Potential Eolian Nalbant COFRET 2010Documento10 paginePotential Eolian Nalbant COFRET 2010Ghiocel AndreeaNessuna valutazione finora

- Presentation Hydro FrackingDocumento12 paginePresentation Hydro Frackingapi-287716683Nessuna valutazione finora

- Pulp&Paper Vol1Documento169 paginePulp&Paper Vol1dude100% (1)

- Briquette Research TitleDocumento6 pagineBriquette Research TitleOscar MirandaNessuna valutazione finora

- Wind EnergyDocumento22 pagineWind EnergyASHWANINessuna valutazione finora

- Climate Finance and Net ZeroDocumento1 paginaClimate Finance and Net ZeroMansiNessuna valutazione finora

- MCB - Miniature Circuit Breaker ConstructionDocumento4 pagineMCB - Miniature Circuit Breaker ConstructionEngr. AbdullahNessuna valutazione finora

- Sector Case Study: Biomass Pellets: The Pellet Export Opportunity in The Near-TermDocumento5 pagineSector Case Study: Biomass Pellets: The Pellet Export Opportunity in The Near-Termm0k123_112640140Nessuna valutazione finora

- MANUEL 1 SEMINAR LatDocumento27 pagineMANUEL 1 SEMINAR Latcrazy hoursNessuna valutazione finora

- Briggs & Stratton Model 091200 Illustrated Parts ListDocumento20 pagineBriggs & Stratton Model 091200 Illustrated Parts Listb0beiiiNessuna valutazione finora

- Lifan Breez 1.3 HBDocumento323 pagineLifan Breez 1.3 HBDenis_1969Nessuna valutazione finora

- Survey and Review PaperDocumento9 pagineSurvey and Review Paperdavinder SinghNessuna valutazione finora

- Installation of Sustainable Street Lights System For "IIM Indore"Documento9 pagineInstallation of Sustainable Street Lights System For "IIM Indore"Akash DeepNessuna valutazione finora

- The Sun's Apparent Position and The Optimal Tilt AngleDocumento11 pagineThe Sun's Apparent Position and The Optimal Tilt AngleWilliam Mejia GalarzaNessuna valutazione finora