Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Di

Caricato da

pakojidastavimDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Di

Caricato da

pakojidastavimCopyright:

Formati disponibili

design

Edited by Bill Travis and Anne Watson Swager

ideas

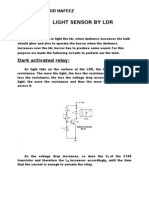

input of IC8. R1, R2, and the 15V power supply shift the 0 to 5V output level to approximately 2 to +2V. C1 filters any high-speed transients that arise from the switching action of IC6s output. Op amp IC9 attenuates the integrators output by 100 and sums the result with the output of the pedestal DAC. For the component values of IC8s integrator stage, the maximum ramp rate at the input of the ADC is approximately 2 V/sec, which is equivalent to 0.067 LSB per conversion. Feedback of the servo-loop circuit maintains the dc level of the integrators output by continuously adjusting the input voltage of the ADS7805 to the level required for the Codei-to-Codei+1 output transition. Thus, the servo-loop circuit locks in the input voltage to the ADC to maintain the Codei-to-Codei+1 output transition. The P=Q16 signal that the circuit clocks into flip-flop IC7 indicates whether the programmed Codei exists for the ADC under test. The output of IC7 connects to an input control line, CNTL6, on the controlling PCs I/O card. After the control program sends each new Codei to the tester, the PC reads the state of CNTL6. A high level on CNTL6 indicates that Codei exists and is not missing. ALIGN PEDESTAL DAC WITH ADC UNDER TEST Before starting the missing-codes test, the procedure requires alignment of the pedestal DACs endpoints with those of the ADC under test. This alignment ensures that the pedestal DACs output closely matches the corresponding ADC input voltage for all codes programmed to the tester. Under this condition, the voltage needed to sum with the pedestal DAC output should be only a few LSBs (referred to the ADC input), thus keeping the dc output level of the integrating op

June 10, 1999 | edn 113

Missing-codes tester checks 16-bit ADC in 7 sec

Mark A Shill, Burr-Brown Corp, Tucson, AZ

s the resolution of ADCs increases from 12 to 16 bits and higher, the difficulty in testing the nomissing-codes specification grows proportionately. To fully guarantee no missing codes for a 16-bit ADC requires testing all 2161 possible output codes. Undertaking such a production test could add much extra cost to the ADC without a quick method for testing all codes. Fortunately, a simple approach can test the no-missing-codes specification for a 16-bit ADCin this case, a 10-sec ADS7805, in typically less than 7 sec (Figure 1). This missing-codes tester comprises an analog ADC servo loop that you can also use to measure the integral nonlinearity and differential nonlinearity of 16-bit ADCs (Reference 1). The servo loop works by finding the ADCs input voltage that corresponds to the Codei-to-Codei+1 output transition. The circuit uses an 18bit DAC729, IC1, as a pedestal DAC to quickly set the input voltage to the ADC

Missing-codes tester checks 16-bit ADC in 7 sec . . . . . . . . . . . . . . . . . . . . . . . . . . .113 Switch-mode supply draws 43-mW standby power . . . . . . . . . . . . . . .116 Circuit rejects ambient light . . . . . . . . . . .118 V/I converter accommodates grounded load . . . . . . . . . . . . . . . . . . . . .120 Digitally controlled potentiometer sets cutoff frequency . . . . . . . . . . . . . . . . . . . .122 Precision reference bans precision resistors . . . . . . . . . . . . . . . . . . .124 Easy method calculates comparator trip points . . . . . . . . . . . . . . . . . . . . . . . . .124 EDN selects 1998 Design Ideas grand-prize winners . . . . . . . . . . . . . . . . .128

under test to approximately the level corresponding to the programmed input code. The output transfer function of the pedestal DAC matches the transfer function of the ADC under testin this case, 10V for the ADS7805. The DAC729 MSB bit-adjustment pins, pins 36 to 40, are open because the unadjusted DAC729s linearity is sufficient for performing only the ADC missing codes test. The procedure successively tests each possible output code of the ADC under test by programming a PC with the desired 16-bit code, Codei. Applying a 100kHz clock to pin 24 of the ADC provides for continuous operation of the ADS7805. When the ADC completes a conversion, two 8-bit 74HC682 magnitude comparators, IC2 and IC3, and accompanying interface logic, IC4 and IC5, compare the ADCs output code to the programmed data-bus code. The signal output from IC4A signifies whether the input voltage to the ADC needs to increase or decrease to achieve an ADC output equal to the programmed Codei. The signal from IC4B indicates whether the output code from the ADC matches Codei; a logic-low level indicates that the code was found. Because both the P>Q16 and P=Q16 signals from IC4A and IC4B, respectively, can be momentarily indeterminate during the ADC conversion, the circuit latches these signals into flip-flops IC6 and IC7 when the conversion is complete. The clock signal for these latches is a delayed versionapproximately 200 nsecof the rising edge of the ADS7805 end-ofconversion signal, BUSY. The circuit uses the P>Q16 signal clocked into IC6 to control the ramp direction of integrator op amp IC8. The 0 to 5V output of HC-type flip-flop IC6 directly drives the integrator

www.ednmag.com

design

ideas

within the 100-mV window. A dual, 12-bit latched DAC, IC11, adjusts the pedestal DACs endpoints.VOUT1 and VOUT2 adjust the pedestal DACs offset and gain, respectively, to the endpoints of the ADC under test. First, the control program adjusts the DAC729s offset by programming and latching Codei to FFFE (hex) and then counting up or down accordingly so that VOUT1 brings the integrator voltage within the 100-mV setting of the window comparator. Next, the program sets IC1s gain by programming and latching Codei to 0000 and again counting up or down so that VOUT2 brings the integrator output to a null. The same I/O data bus programs both the DAC2813 and the 74HC682 digital comparators. The 74HC139 decoder, IC12, selects either the input Codei latches, IC13 and IC14, or the internal latches of the DAC2813. IC11 has two input-latchenable pins, one for each of its output DACs. Input LDAC loads the DACs input latch data into the internal latches, thus simultaneously programming both VOUT1 and VOUT2. I/O control lines CNTL0 and CNTL1 select the desired latch, and CNTL2 strobes in the data from the bus. The listing of the Pascal program for controlling the missing-codes tester is available for downloading from EDNs

amp, IC8, close to 0V. Thus, for each Codei setting, the integrator output never needs to slew very far from the dc level of 0V. Comparators IC10A and IC10B form a window comparator for the output of IC8. The window voltage is equal to 100 mV, which corresponds to approximately 3.3 LSBs, referred to the ADS7805 input. I/O control lines CNTL4 and CNTL5 read the outputs of IC10A and IC10B, respectively to determine the level of the integrators output voltage. If CNTL4 is high, the integrator output is more than 100 mV. If CNTL5 is high, the integrator is less than 100 mV. If both CNTL4 and CNTL5 are low, the integrator output is

Figure 1

5V 13

T SE U

FO

15V 21

T N

FI RE

15V 19

V

CC

26

1

25

2

24

1

23

OM O

2

18

OM DC AC

22 20

+V

CC

BP

BP

RE

RE

VOUT1

RE

28 1M 27 CB 0.0022 F 100k

FI

IC11 DAC2813

R EN 1 EN 2 LD AC DB 11 M DB SB

0L 10

DB 7 DB

DB

DB

DB

DB

DB

14 16 15 17

1 2 3 4 5 6 7 8 9 10 11 12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

DB

DB

DB

SB

VOUT2

15V 15V 34

J AD

33

D OU

32

IN T F RE

31

N AG

30

D

U

29

T

26

B

25

B SJ

24

V

22

CC

21

V

CC

GN

KF

KF

IO

IN

RE

RE

10

10

GA

B1MSB

IC1 DAC729 B18 LSB 18 VDD 19 DGND 20

VOUT

23

PEDESTAL DAC OUT

B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 B12 B13 B14 B15 B16 B17 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17

1 Y0 Y1 Y2 Y3 IC12 74HC139 G A B CNTL2 CNTL1 CNTL0

5V

PC0 PC1 PC2 8255 PORT C

Q15 Q14 Q13 Q12 Q11 Q10 Q9 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 Q15 Q14 Q13 Q12 Q11 Q10 Q9 PA7 PA6 PA5 PA4 PA3 PA2 PA1 PA0 8255 PORT A 11 C 19 18 17 16 15 14 13 12 8Q

Q8

Q7

Q6

Q5

Q4

Q3

Q2

Q1

Q0

Q8 11 C 19

Q7 18

Q6 17

Q5

Q4

Q3

Q2

Q1

Q0

PB7 PB6 PB5 PB4 PB3 PB2 PB1 PB0 8255 PORT B

16 15

14 13 12 8Q

1Q 2Q 3Q 4Q 5Q 6Q 7Q IC13 74HC573

1Q 2Q 3Q 4Q 5Q 6Q 7Q IC14 74HC573

OE 1

1D 2D 3D 4D 5D 6D 7D 8D 2 3 4 5 6 7 8 9 D15 D14 D13 D12 D11 D10 D9 D8

OE 1

1D 2D 3D 4D 5D 6D 7D 8D 2 3 4 5 6 7 8 9 D7 D6 D5 D4 D3 D2 D1 D0

An analog servo loop tests for no missing codes by finding the ADCs input voltage that corresponds to the Codei-to-Codei+1 output transition.

114 edn | June 10, 1999

www.ednmag.com

web site, www.ednmag.com. Click on Search Databases/Links Page and then enter the Software Center to download the file for Design Idea #2334. The section of the program that outputs codes to the data bus and reads the state of the CNTL6 line is based on a custom I/O card built with an Intel 8255A programmable peripheral interface. The I/O routines are for reference only, and you should modify them according to the protocol used by the users specific I/O card. The EndPoints procedure in the listing aligns the offset and gain of the pedestal DAC to that of the ADC under test. It programs IC11 as necessary to null the in-

tegrator output for both offset and gain. The Detect procedure programs each Codei, from 0 to 65534, to the missingcodes test board. After programming each new code, the program reads the state of the CNTL6 line. If CNTL6 is a logic high, indicating the programmed code exists, the Count variable is incremented. The Detect procedure loops for the given code until a minimum number of occurrences are detected, set by the variable MinCount. The variable MaxTry sets the maximum number of times that the program trys to find Codei. The program loops for an appropriate delay time to ensure that measurements of the state of

the line occur only once per analog-todigital conversion or, in the case of the ADS7805, approximately every 10 sec. For the variable MinCount set to 3 and MaxTry set to 30, the missing-codes tester can test the 10-sec ADS7805 for all 2161 codes in less than 7 sec. (DI #2334) Reference 1. Shill, Mark A, Servo loop speeds tests of 16-bit ADCs, Electronic Design, Feb 6, 1995, pg 93.

To Vote For This Design, Circle No. 415

0.1 F 15V 6 15V 14.9k 100 100 5 14.9k 1M 15V 6 + 3 2 5V + 7 2 3 100k C1

10 pF

5V R1 5k D

IC8 4 OPA602

R2 30k 15V

74HC74 IC6 CLK

15V 15V 10k + IC10A LM293 7 IC10B ADC CLOCK 100 kHz IC5B IC5C

1k

PR CL 5V

CNTL4 10k CNTL5

DUT POWER

D PR

74HC74 IC7 Q CLK CNTL6

15V

CL

330 pF 10k 15V 10k 2 7 6 + 3 4 IC9 OPA627 15V 200 1 33.2k 2 3 4 5 AGND2 23 BYTE 25 CS 24 R/C 26 BUSY 14 DGND + 8 9 4 P1 P2 Q2 7 Q1 5 + VIN D15 D14 D13 D12 D11 D10 D9 6 7 10 11 12 IC5A 74HC04 17 15 13 11 P7 P6 P5 P4 8 P3 6 IC2 74HC682 Q7 Q6 Q5 Q4 Q3 9 18 16 14 12 22.2 F

270 pF

CNTL6 CNTL5 CNTL4

27 VANA

28 VDIG + 10 F P>Q16

PC4 PC5 PC6 8255 PORT C

AGND1 VREF CAP

ADS7805 DUT D8 13 D7 D6 D5 D4 D3 D2 D1 D0

15 16 17 18 19

20 21 22

IC4A 74HCOO P=Q16 IC4C IC4D IC4B

2 P0 P>Q 1 P=Q Q0 3 P>QH

17 15 13 11 P7 P6 P5 P4

8 P3

6 P2

4 P1

2 P0 P>Q 1 P=Q Q0 3 Q1 Q0 P>QL

IC5D

19 P=QH Q7 Q7 Q6 Q6

IC3 74HC682 Q5 Q5 Q4 Q4 Q3 9 Q3 Q2 7 Q2 Q1 5

19 P=QL IC5E

18 16 14

12

Q15 Q14 Q13 Q12 Q11 Q10 Q9 Q8

www.ednmag.com

June 10, 1999 | edn 115

design

ideas

Switch-mode supply draws 43-mW standby power

Christophe Basso and Franois Lhermite, Motorola SPS, Toulouse, France

witch-mode offline supplies offer better efficiency than linear supplies. However, the efficiency of a switchmode power supply (SMPS) seriously degrades with light loads, and commutation losses provoke power dissipation well above 1W even with no load. A good way to build a low-standby-current SMPS is to use a hysteretic architecture, which delivers high-frequency pulses until the output passes a threshold and then no pulses until the output again drops below the threshold. The SMPS consumes little energy delivering the refreshment pulses. Figure 1 shows a circuit that uses an MC34063 controller IC and an insulated-gate bipolar-transistor (IGBT) output device. The MC34063 operates in current

mode. Q3 trips the IC when the voltage on sense resistor R16 drops to approximately 550 mV. (IPEAK=160 mA in this example.) You can adjust the peak current to compensate for the transformers magnetorestrictive effects. Any transformer you use in an SMPS produces audible noise at a low frequency. You can either buy an expensive transformer whose construction ensures low audible noise or keep peak current low, as in Figure 1s circuit. When reducing the peak current, you need to increase either the primary inductance or the switching frequency (by varying C8) to keep the output power constant. The MMG05N60D IGBT has low parasitic capacitance that degrades efficiency at low peak currents. When you open

the high-voltage switch in a MOSFETbased flyback converter, the peak current does not immediately drop to zero. Depending on the amount of parasitic capacitance, the current keeps circulating while the drain voltage rises, and efficiency suffers. Figure 2a illustrates this wasteful behavior in a high-voltage, MOSFET-based switcher. The MMG05N60D IGBT has low parasitic capacitance; its total gate charge at VGS=10V is only 4 nC. Figure 2b shows the current in Figure 1s circuit with zero output power. The start-up circuit for the MC34063 uses Q4 and Q2. When you apply the power main, the voltage on C14 starts to rise. The ratio of R20 and R22 causes Q4 and Q2 to remain open. The IC receives

T1 G6518-00* D5 1N5819

Figure 1

R18 2.5M R19 2.5M

L2 10 H C11 470 F + C12 100 F 7.4V 2.3W

D4 1N4148 Q2 MGSF1P02 Q1 MMG05N60D R17 270

41N4007

4.7 F/ 350V C13

R21 1M IC2 MOC8103

85 TO 260V AC R20 1M

R1 100k

1 2 Q4 BC559C C10 10 F

+

8 IC1 MC34063 7 6 5 R14 10k

R15 1k Q3 MMBT2222

D6 6.8V

3 R4 560 C8 470 pF 4

C14 47 F

R22 33k

R8 560 R16 3.3 *AVAILABLE FROM THOMSON OREGA.

C9 470 pF

A hysteretic architecture in an offline switch-mode power supply makes it possible to achieve less-than-100-mW standby power.

116 edn | June 10, 1999

www.ednmag.com

design

ideas

Figure 2

(a)

(b)

The turn-off characteristic of a lateral MOSFET (a) results in significant wasted power in a no-load condition; lower parasitic capacitance in an IGBT leads to lower dissipation during the turn-off period.

no power, and the current that flows in from C14 is small. When the voltage reaches a threshold, Q4 starts to conduct and pulls Q2s gate toward ground. Q2s drain voltage rises and strengthens the

conduction in Q4. C14 rapidly discharges into C10, and the MC34063 oscillates. The circuit offers efficiency ranging from 59.4 to 73%. It dissipates no-load power levels of 42.5, 65, and 82.8 mW at dc input

voltages of 120, 325, and 360V, respectively.(DI #2363).

To Vote For This Design, Circle No. 416

Circuit rejects ambient light

Massimo Gottardi, IRST, Trento, Italy

n some applications, you need to C2 detect light signals in the presence of 0.1 F background light whose in15V R2 1M Figure 1 tensity can change by orders of Q1 magnitude. The circuit in Figure 1 uses IC2 2N2222 an integrated photodiode/amplifier R1 1M + (OPT201) in conjunction with an inteC1 grator that drives two linear optocou0.1 F plers (TIL300). The optocouplers subIC3 TIL300 1M 4 tract the background-light-generated 40 pF current from the current the optical sensor produces. C2 integrates any dc signal 2 present at the output of IC1. The output IC4 TIL300 75 of IC2 drives two optocouplers, IC3 and 5 IC4. The four photodiodes in both TIL300s connect in parallel with the + 8 IC1 4000 pF diode in the OPT201 to subtract the dc R3 100 OPT201 1/2W component from the signal path. IC3 and IC4 need 60-mA drive to produce rejection current as high as 1.5 mA. This The two optocouplers use input-series, output-parallel connections to halve the driving current and design uses the optocoupler configura- double the output rejection current.

118 edn | June 10, 1999

www.ednmag.com

design

ideas

the transimpedance amplifier. The total output noise in the circuit is 80 V rms. A 6.8-k resistor can reject the same 1.5-mA dc current, but it produces 200V output noise. (DI #2364).

To Vote For This Design, Circle No. 417

tion instead of a simple resistor, because the optocouplers nonlinear characteristic allows a higher current range without substantially affecting the noise gain of

V/I converter accommodates grounded load

Michele Frantisek, Brno, Czech Republic

The voltage-to-current (V/I) converter in Figure 1 uses three common op amps, two medium-power transistors, and only a few passive components. The first op amp (IC1) inverts the sum of voltages VIN and VOUT to V1=-(VIN+VOUT). The second op amp (IC2) and transistors Q1 and Q2 invert this voltage to produce VIN+VOUT. The formula for calculating the output current is thus:

IOUT = V2VOUT = R6

VIN + VOUTVOUT VIN = . R6 R6 The formula shows that the value of IOUT depends only on VIN and R6. Voltage follower IC3 reduces to a negligible level the current from the circuit output to IC1. The advantages of the circuit are:

load-grounding possibility; simple control of IOUT/VIN ratio; high precision, linearity, stability, and bandwidth; wide IOUT range, approximately 1 A to IC(max) of Q1 and Q2; and high output resistance of approximately 50 M. (DI #2365). To Vote For This Design, Circle No. 418

Figure 1

15V

R2 100k 1% IC3 OP-77

R3 100k 1% 15V

15V

VIN

R1 100k 1%

+ IC1 OP-77 R7 33k 15V V1

R4 100k 1% + IC2 OP-77 R6 VOUT V2 1k 0.1% Q2 2N4033 15V 15V IOUT

A versatile voltage-to-current converter provides a handy current source in many analog applications.

120 edn | June 10, 1999

+ R5 100k 1% 15V 15V Q1 2N3019 R8 47k

www.ednmag.com

design

ideas

As you program the wiper from one end of the potentiometer to the other, k varies from 0 to midscale (1/2) to 1, and the cutoff frequency varies from infinite hertz to a minimum frequency and back to infinite hertz. The minimum frequency is

fC(MIN) = 4 . 2R1C

Digitally controlled potentiometer sets cutoff frequency

Chuck Wojslaw, Xicor Inc, Milpitas, CA

C he traditional method of Figure 1 controlling the upper cutoff frequency in the basic inverting-amR2 plifier circuit of Figure 1 is to add capacR1 V S itor C in parallel with R2. The value of C VO controls the cutoff frequency. R1 and R2 + independently establish the magnitude of the circuit gain, which equals R2/R1. If you need a variable cutoff frequency, you Controlling the cutoff frequency using a tradiuse a variable capacitor. However, this ap- tional inverting amplifier circuit has some limiproach has two major problems: The cir- tations, such as a limited selection of variable cuit does not lend itself to computer con- capacitors. trol, and few variable capacitors are available with values in the nanofarad re- for the feedback port produces the following gain expression: gion. The circuit in Figure 2a is an invert R2 1 ing amplifier that uses a digitally con R R Ck ( 1 k ) VO y 1 1 trolled potentiometer and a fixed capac. = 21 A = 1 V y S 1 2 B itor as an input Tee network. The magj + R1Ck(1k) nitude of the gain for this inverting cirIn this equation, k is a number that cuit is also R2/R1. However, in this case, R1, C, and the location of the wiper along varies from 0 to 1 and reflects the prothe resistor array of the potentiometer es- portionate position of the wiper from tablish the cutoff frequency. The upper one end of the potentiometer (0) to the cutoff frequency is programmable be- other end (1). cause the wiper of the potentiometer is The circuits gain expression is under digital or computer control. VO A = o C . Several analysis approaches help deVS j + C termine the circuit gain as a function of frequency. One approach is to use y, or This equation has the same form as an admittance, parameters. If you treat net- equation for an amplifier or lowpass filworks A and B as two ports (Figure 2b), ter with a gain of R2/R1 and a cutoff frethe ratio of the short-circuit admittance quency of coefficient for the input port, y21 A, to y12B 1 fC = . 2R1Ck(1k)

For the XDCP family of digitally controlled potentiometers (Xicor Inc, www. xicor.com), k can vary from 0 to 1. The number of taps or programmable wiper positions determines the resolution. R1 represents the RTOTAL of the potentiometer. The number of taps varies from 32 to 256, and RTOTAL varies from 1 k to 1 M, depending on the potentiometer. The potentiometer can store a wiper or cutoff-frequency setting in nonvolatile memory, which permits the circuits cutoff frequency to return to a predetermined value on power-up. For the circuit in Figure 2a, gain is 4.7, and the cutoff frequency varies from 6.4 kHz to a theoretically infinite hertz. The circuit uses a 10-k potentiometer, the X9C103, which has 100 taps and a threewire interface. The circuit is useful for audio, control, and signal-processing applications. (DI #2367)

To Vote For This Design, Circle No. 419

NETWORK B

X9C103

Figure 2

CS INC UID 2 1 7 8 5V R2

R2 47k 5V 6 2 + 7 VS 6 VO kR1 (1k)R1 + C VO

VS

CONTROL AND MEMORY R1

3 C 0.01 F (a) 5 4

4 LT1097 5V (b) NETWORK A

An inverting amplifier that uses a digitally controlled potentiometer and a fixed capacitor provides for a programmable cutoff frequency (a). You can analyze the circuit as a two-port network (b).

122 edn | June 10, 1999

www.ednmag.com

design

ideas

Precision reference bans precision resistors

Budge Ing, Maxim Integrated Products, Sunnyvale, CA

ombining a switched-capacitor put of a 5V precision reference, IC1. IC1 partly on the initial accuracy of IC1, charge pump with a precision refer- has an input range of 5.2 to 12.5V. Re- which in this case is 1%. To determine the ence yields an inverted reference placing IC1 with a 2.5V reference that ac- overall accuracy, you must add the error from a positive power supply (Figure 1). cepts 2.7 to 12.5V inputs produces a from the dropout voltage, which is less Unlike the more typical combination of - 2.5V output. than 2 mV for 90 A of load current Output-voltage accuracy depends (Figure 2a). For a - 2.5V output, the cira positive three-terminal reference and an op-amp inverter, this circuit percuit draws quiescent current 3.3 F forms accurate inversions without that ranges from 86 A for a VIN VOUT the need for precision resistors 2.7V input to 105 A for a 12.5V 5.2 TO 12.5V 5V C C+ (2.7 TO 12.5V) (2.5V) IC1 and a negative supply. The cominput. For 5V outputs, the cirIC2 OUT IN MAX6150 OUT IN pact circuit requires only three cuit draws 127 A for 5.2V in(MAX6125) MAX828 + 3.3 F GND 3.3 F surface-mount capacitors, puts and 140 A for 12.5V inGND Figure 1 and the ICs occupy tiny puts (Figure 2b). (DI #2368) SOT-23 packages. Combining a voltage reference and a charge-pump inverter forms To Vote For This Design, The charge-pump inverter, IC2, a precision negative reference. delivers 5V by inverting the outCircle No. 420

0 VOUT=5V 2

250

200 OUTPUT VOLTAGE DROP (mV) 4 6 8 10 12 14 16 (a) 50 VOUT=2.5V SUPPLY CURRENT (A) A B C 100 D

150

10 100 OUTPUT CURRENT (A)

1000 (b)

0 0 10 20 30 40 50 60 70 80 90 100 LOAD CURRENT (A) A, VIN=12.5V, AND VOUT=5V. B VIN=5.2V, AND VOUT=5V. C, VIN=12.5V, AND VOUT=2.5V. D, VIN=2.7V, AND VOUT=2.5V.

Figure 2

NOTES: FOR TRACE FOR TRACE FOR TRACE FOR TRACE

For a S 5V output, the dropout voltage is less than 2 mV at 90 A of output current (a). For a 5V output, quiescent current ranges from 127 to 140 A.

Easy method calculates comparator trip points

Virgil Lawrence, Micro Linear, San Jose, CA

sing Millmans Theorem to calculate the resistor ratio reduces the time it takes to calculate the trip points on a comparator with hysteresis.

This method eliminates lengthy computations and substitutions. Using this resistor ratio, you select two resistors, assign convenient values, and then

124 edn | June 10, 1999

calculate the third value. Assume an inverting comparator with an upper limit of 4V and a lower trip voltage of 1.333V. The voltage on the in-

www.ednmag.com

design

ideas

where Gt 1/R. Using Millmans Theorem, with VCC at the top of R1 and RF (FigFigure 2 ure 2), set up the numerator with a Millman equation. Set up the denominator with another Millman equation when the output voltage is zero (with only one voltage source in the denominator). lRF and therefore negAssume that RC is l ligible in the calculations. The resultant equation for the voltage ratio is:

VIN(HIGH)

VCC 12V VCC RC R1

verting input needs to reach 1.333V for the output to switch to VCC. Then, for the output to return to zero, the input voltage needs to reach 4V. Millmans Theorem states that the sum of the products of the voltages times their respective conductances divided by the sum of the conductances gives the common junction-point voltage VX (Figure 1). Or,

VX =

Figure 1

VX

VNGN , GN

VIN(LOW )

VNG N GN VNG N GN

12 12 + R RF = 1 12 R1

R2

RF

R1

=

R2 RN VN

R F + R1 = VOLTAGE RATIO. RF

Millmans theorem states that the sum of the products of the voltages times their respective conductances divided by the sum of the conductances gives the common junction point voltage VX.

This large fraction equals the voltage ratio 4/1.333t 3. First solve for RF in terms of R1, and select R1 in relation to RF, such 1 M, and RFt 500 k. Then solve as R1t for R2. The resistance ratio always equals the voltage ratio minus one. (DI #2372)

Using Millmans theorem, you can calculate that the voltage ratio of the trip points equals (RF+R1)RF.

To Vote For This Design, Circle No. 421

Circle No 5 or visit www.ednmag.com/InfoAccess

126 edn | June 10, 1999

www.ednmag.com

design

ideas

EDN selects 1998 Design Ideas grand-prize winners

EDN is pleased to announce the grand-prize winners for Deliwczyn ski and Marcin sign Ideas published in 1998. Lukasz S ski of the Institute of Electronics at the University of MinLipin w, Poland, specialize in fiber-optic ing and Metallurgy, Krako transmission for nontelecommunications applications and other optoelectronic circuits. The pair takes the honors for Circuit uses simple LED for near-IR light, EDN, Sept 1, 1998, pg 92. The choice was difficult given the high quality of 1998s Design Ideas. EDN chose the winning Design Idea for its simplicity, cleverness, and usefulness. The circuit eliminates the need to configure a bulky and expensive mechanical fixture to generate light with precisely controlled power levels. The honors took the pair by surprise. We never suspected that, among so many interesting ideas, ski. He says that ours might be prized as the best one, says Lipin liwczyn ski thought of the idea after parhe and co-designer S ticipating in a project involving some optical reflectometers requiring a precise and stable light source. We have done lots of experiments with semiconductor lasers, but found that they are ski. After these experiunsuitable for this purpose, says Lipin ments, the pair decided to use the hybrid LED module that the winning Design Idea describes. The idea has already found use in a real-world application. A pro-ecological installation uses the reflectometer to measure the fumes from industrial chimneys. It has been in use for a long time and performs well, acliwski. This Design Idea was one of six that S cording to Lipin ski ski czyn submitted and the only one Lipin submitted last year. liwczyn ski, who is single, In his spare time, the 30-year-old S ski, 52, plays electric guitar and travels to historical sites. Lipin is married with two children and likes classical music, skiing in the wintertime, and camping in the summertime. Each designer plans to use his half of the $1500 cash prize for the upcoming summer holidays.

Every month readers pick one Design Idea from the issue as the winner. Congratulations to all the winners, and keep the innovative ideas coming.

Jan 1, 1998,Fax saver cuts wear, tear, and power, Hugh Adams, Fort Walton Beach, FL. Jan 15, 1998, LED flasher and triac pulser work off ac line, Dennis Eichenberg, Parma Heights, OH. Feb 2, 1998, Vital-signs monitor consumes less than 50 A, Leonard Schupak, Discovision Associates, Irvine, CA. Feb 16, 1998, Antenna extension provides open-door policy, Richard Panosh, Vista, Bolingbrook, IL. March 2, 1998,Isolated driver forms solid-state circuit breaker, Bob Watson, Corley Manufacturing Co, Chattanooga, TN. March 13, 1998, Inexpensive relays form digital potentiometer, Robert Perrin, Z-World, Davis, CA. March 26, 1998, Alternating LED blinker uses four parts, Andy Meng, Cincinnati, OH. April 9, 1998, 10-kHz VFC uses charge-pump variation, Stephen Woodward, University of North Carolina, Chapel Hill, NC. April 23, 1998, $5 junk-box circuit determines phase sequence, Hugh Adams, Fort Walton Beach, FL. May 7, 1998, MCS-51 endows MicroLan-like protocol to UARTs, SK Shenoy, NPOL, Kochi, India. May 21, 1998, High-frequency AGC has digital control, Ron Mancini, Harris Semiconductor, Melbourne, FL. liwczyn ski June 4, 1998, 25-kV generator tests insulation, Lukasz S w, and Przemyslaw Krehlik, University of Mining and Metallurgy, Krako Poland. June 18, 1998,Use a printer port to record digital waveforms, Dean Shen, Dycam Inc, Chatsworth, CA. July 2, 1998, Circuit protects against ac-line disturbances, Basilio Simoes, ISA, Coimbra, Portugal. July 16, 1998, Step-up/step-down converter takes 2 to 16V inputs, Luciano Bordogna and Luca Vasalli, Maxim Integrated Products, Milan, Italy. Aug 3, 1998,Circuit translates TTY current loop to RS-232C, Jerzy Chrzaszcz, Warsaw University, Poland. Aug 17, 1998,Replace an external gate with a resistor, Stan DSouza, Microchip Technology Inc, Chandler, AZ. liSept 1, 1998,Circuit uses simple LED for near-IR light, Lukasz S w, Poland. ski, Marcin Lipin ski, Institute of Electronics, Krako wczyn Sept 11, 1998, Add-on modulator has high bandwidth, MJ Salvati, Flushing Communications, Flushing, NY. Sept 24, 1998,Bipolars provide stable current source, Bill Morong, Morongs Harness, Dover-Foxcroft, ME. Oct 8, 1998, Video equalizer sharpens VCR images, Wayne Sward, Consultant, Bountiful, UT. Oct 22, 1998, Photo-flash charger minimizes parts count, Steven Chenetz, Micrel Semiconductor, San Jose, CA. Nov 5, 1998, Short-circuit finder uses few parts, Boris Khaykin, Candid Logic Inc, Madison Heights, WI. Nov 19, 1998, CMOS inverter VCO tunes octave to UHF, Shawn Stafford, AM Communications Inc, Quakertown, PA. Dec 3, 1998, Eight-channel data-acquisition system features autocalibration, Mark Shill, Burr-Brown Corp, Tucson, AZ. Dec 17, 1998, Circuit eases three-phase monitoring, Henno Normet, Tavares, FL.

128 edn | June 10, 1999

www.ednmag.com

Potrebbero piacerti anche

- Adc Lab Pic18Documento23 pagineAdc Lab Pic18Bolarinwa Joseph100% (1)

- ADC Measurement DetailDocumento9 pagineADC Measurement DetailMuhammad SiddiqueNessuna valutazione finora

- Experiment No. 4 ADC PDFDocumento16 pagineExperiment No. 4 ADC PDFRia Cordova0% (1)

- PIC based digital voltmeter circuit and codeDocumento7 paginePIC based digital voltmeter circuit and codeGaurav AroraNessuna valutazione finora

- ANALOG-TO-DIGITAL CONVERTER EXPLAINEDDocumento7 pagineANALOG-TO-DIGITAL CONVERTER EXPLAINEDPratyay DharNessuna valutazione finora

- Analog To Digital ConverterDocumento7 pagineAnalog To Digital ConverterRavi Patel100% (1)

- ADC Interfacing With MicrocontrollersDocumento9 pagineADC Interfacing With MicrocontrollersLuis MezaNessuna valutazione finora

- Interfacing - ADC & DAC: ADC (Analog To Digital Converter)Documento8 pagineInterfacing - ADC & DAC: ADC (Analog To Digital Converter)Jagan VNessuna valutazione finora

- ADC Interfacing Microcontroller TutorialDocumento17 pagineADC Interfacing Microcontroller TutorialNagabhushanam KoduriNessuna valutazione finora

- Introduction To PIC Programming: Baseline Architecture and Assembly LanguageDocumento0 pagineIntroduction To PIC Programming: Baseline Architecture and Assembly LanguageHugo DamnNessuna valutazione finora

- TMS320F2812-Analogue To Digital ConverterDocumento26 pagineTMS320F2812-Analogue To Digital ConverterPantech ProLabs India Pvt LtdNessuna valutazione finora

- Project Objective:: Simple AdcDocumento10 pagineProject Objective:: Simple AdcaravindnehaNessuna valutazione finora

- Adc0808 CodeDocumento3 pagineAdc0808 CodebalabooksNessuna valutazione finora

- ADC Conversion Microcontroller InterfaceDocumento4 pagineADC Conversion Microcontroller InterfaceSridhar DineshNessuna valutazione finora

- Digital Thermometer Circuit.Documento2 pagineDigital Thermometer Circuit.elvergonzalez1100% (1)

- Analog Device Micro ConverterDocumento20 pagineAnalog Device Micro ConvertershaileshNessuna valutazione finora

- ADC Interfacing with 8051 for Data AcquisitionDocumento5 pagineADC Interfacing with 8051 for Data AcquisitionSrideviKumaresanNessuna valutazione finora

- ADC0808Documento15 pagineADC0808Ketan SalviNessuna valutazione finora

- PIC PPT 13104022 (4th Year)Documento41 paginePIC PPT 13104022 (4th Year)Daman Deep Singh100% (1)

- Tda 10021 DatasheetDocumento17 pagineTda 10021 DatasheetWilly DacoNessuna valutazione finora

- Design: IdeasDocumento6 pagineDesign: IdeasSamantha EwingNessuna valutazione finora

- 6 Adc0804Documento5 pagine6 Adc0804esther_kakani919Nessuna valutazione finora

- Lab 11 DAC and ADC Full PackageDocumento5 pagineLab 11 DAC and ADC Full PackageLoveWorldCanadaNessuna valutazione finora

- Adc & DacDocumento10 pagineAdc & DacMohamed Irshad AboubackerNessuna valutazione finora

- ADC of PIC MicrocontrollerDocumento4 pagineADC of PIC Microcontrollerkillbill100% (2)

- Exp 8Documento5 pagineExp 8Ashwini KothavaleNessuna valutazione finora

- Ad-Da Module V1.1Documento7 pagineAd-Da Module V1.1Arpita PrasadNessuna valutazione finora

- 7-Segment Display & ADC Controls With 8051: LABORATORY - Experiment 5Documento12 pagine7-Segment Display & ADC Controls With 8051: LABORATORY - Experiment 5Vikas Ravi TPNessuna valutazione finora

- Parallel and Serial AdcDocumento45 pagineParallel and Serial AdcAman Deep100% (1)

- Measuring Distance Using Infrared SensorsDocumento5 pagineMeasuring Distance Using Infrared SensorsRajkeen ChamanshaikhNessuna valutazione finora

- Digital Thermometer Using 8051 Microcontroller Project ReportDocumento18 pagineDigital Thermometer Using 8051 Microcontroller Project Reportjs18ps56% (9)

- Analog To DigitalDocumento46 pagineAnalog To DigitalSaleem HaddadNessuna valutazione finora

- Digital ThermometerDocumento4 pagineDigital ThermometerPran KumarNessuna valutazione finora

- STM32 ADC Tutorial Complete Guide With ExamplesDocumento18 pagineSTM32 ADC Tutorial Complete Guide With Examplessuper_faca100% (1)

- Analog To Digital ConverterDocumento4 pagineAnalog To Digital Converterzero kimochiNessuna valutazione finora

- Adc Dac InterfacingDocumento25 pagineAdc Dac InterfacingSuchetha SriNessuna valutazione finora

- Pic 18 F 4520Documento51 paginePic 18 F 4520sitizarina78100% (1)

- Adc 0804Documento5 pagineAdc 0804gouttNessuna valutazione finora

- Firas 2010 1Documento2 pagineFiras 2010 1firasalraieNessuna valutazione finora

- Circuit Can Be Used For Many PurposesDocumento1 paginaCircuit Can Be Used For Many PurposesAszhar Al AmbaryNessuna valutazione finora

- Interfacing Microchip'S Mcp3201 Analog-To-Digital Converter To The Picmicro MicrocontrollerDocumento21 pagineInterfacing Microchip'S Mcp3201 Analog-To-Digital Converter To The Picmicro MicrocontrollerMaxi NozikovskyNessuna valutazione finora

- Rotary EncoderDocumento6 pagineRotary EncoderalesysNessuna valutazione finora

- ADC On A PICDocumento4 pagineADC On A PICDurgesh Kumar Singh100% (1)

- Analog-to-Digital Conversion: Industrial Embedded SystemsDocumento14 pagineAnalog-to-Digital Conversion: Industrial Embedded Systemschandramohan muruganNessuna valutazione finora

- Design and Simulation of DAC On The Basis of Capacitor ArrayDocumento4 pagineDesign and Simulation of DAC On The Basis of Capacitor ArrayAmitNessuna valutazione finora

- Understanding the ADC0804 8-bit Analog to Digital ConverterDocumento2 pagineUnderstanding the ADC0804 8-bit Analog to Digital ConverterSeenivasan Ma0% (1)

- Adc InterfacingDocumento17 pagineAdc Interfacing21ecuog059Nessuna valutazione finora

- Fpga Interface For An Analog Input Module: Volume 2, Issue 4, April 2013Documento6 pagineFpga Interface For An Analog Input Module: Volume 2, Issue 4, April 2013International Journal of Application or Innovation in Engineering & ManagementNessuna valutazione finora

- Applications of Handshake ModeDocumento3 pagineApplications of Handshake Modevyshnu3006Nessuna valutazione finora

- 5.AD and DA ConvertersDocumento7 pagine5.AD and DA ConvertersAkram TahaNessuna valutazione finora

- Applications of 8085 Microprocessor Dac InterfaceDocumento4 pagineApplications of 8085 Microprocessor Dac InterfaceSai PrakashNessuna valutazione finora

- Analog To Digital Conversion: IntroductionDocumento8 pagineAnalog To Digital Conversion: IntroductionKeyur ParekhNessuna valutazione finora

- 36 Interfacing Adc0808 With Serial Port Rs232 8051 Microcontroller Using Clock From D Flip FlopDocumento6 pagine36 Interfacing Adc0808 With Serial Port Rs232 8051 Microcontroller Using Clock From D Flip Flopprajapatiprashant40Nessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Valutazione: 2.5 su 5 stelle2.5/5 (3)

- Anais Do Workshop De Micro-ondasDa EverandAnais Do Workshop De Micro-ondasNessuna valutazione finora

- Z-TRAUQ Current Transducers GuideDocumento2 pagineZ-TRAUQ Current Transducers GuidepakojidastavimNessuna valutazione finora

- 500W48VDC Air-ConDocumento1 pagina500W48VDC Air-ConpakojidastavimNessuna valutazione finora

- 08 0033 1b E HK Kap 11 DCDocumento20 pagine08 0033 1b E HK Kap 11 DCpakojidastavimNessuna valutazione finora

- Cordless Tools Battery Technology ComparisonDocumento15 pagineCordless Tools Battery Technology ComparisonpakojidastavimNessuna valutazione finora

- BUS98Documento9 pagineBUS98pakojidastavimNessuna valutazione finora

- RM3048XE 3.0kW 48V DC Modular Rectifiers v1.0Documento2 pagineRM3048XE 3.0kW 48V DC Modular Rectifiers v1.0pakojidastavimNessuna valutazione finora

- R48-2000e Datasheet Rev1.1 20100629Documento2 pagineR48-2000e Datasheet Rev1.1 20100629pakojidastavimNessuna valutazione finora

- Spiral Series Fuse BodyDocumento1 paginaSpiral Series Fuse BodypakojidastavimNessuna valutazione finora

- Esure Rectifier R483500eDocumento2 pagineEsure Rectifier R483500epakojidastavimNessuna valutazione finora

- En PS TL 2CP550 BPS 001 - 0212Documento4 pagineEn PS TL 2CP550 BPS 001 - 0212pakojidastavimNessuna valutazione finora

- Engineering - A Pragmatic Introduction To The Art of Electrical EngineeringDocumento140 pagineEngineering - A Pragmatic Introduction To The Art of Electrical EngineeringUfuk DzlNessuna valutazione finora

- Mcu2500 GBDocumento8 pagineMcu2500 GBpakojidastavimNessuna valutazione finora

- Inverter Pack Solutions DatasheetDocumento2 pagineInverter Pack Solutions DatasheetpakojidastavimNessuna valutazione finora

- 10-22 kVA CAL Enclosure (GB) (0908)Documento2 pagine10-22 kVA CAL Enclosure (GB) (0908)pakojidastavimNessuna valutazione finora

- PowerWizard 2 0 (GB) 1006Documento2 paginePowerWizard 2 0 (GB) 1006pakojidastavimNessuna valutazione finora

- 04@trainig Cours ENP NetSure 701 UnitsDocumento1 pagina04@trainig Cours ENP NetSure 701 UnitspakojidastavimNessuna valutazione finora

- Abcde: Connect With ConfidenceDocumento2 pagineAbcde: Connect With ConfidencepakojidastavimNessuna valutazione finora

- 2N-Easy Gate (En)Documento2 pagine2N-Easy Gate (En)pakojidastavimNessuna valutazione finora

- WebSCADA Modbus BrochureDocumento2 pagineWebSCADA Modbus BrochurepakojidastavimNessuna valutazione finora

- Tsi Veda 48 230 Data Sheet v03Documento2 pagineTsi Veda 48 230 Data Sheet v03pakojidastavimNessuna valutazione finora

- Inverter Pack Solutions DatasheetDocumento2 pagineInverter Pack Solutions DatasheetpakojidastavimNessuna valutazione finora

- Emerson - BRAVO Inverter Data SheetDocumento2 pagineEmerson - BRAVO Inverter Data SheetOscar ReyesNessuna valutazione finora

- Emerson's Commitment to Workplace Safety and HealthDocumento1 paginaEmerson's Commitment to Workplace Safety and HealthpakojidastavimNessuna valutazione finora

- NOVA Inverter Data SheetDocumento2 pagineNOVA Inverter Data SheetpakojidastavimNessuna valutazione finora

- ENLZT145294RA BulkSystemsDocumento8 pagineENLZT145294RA BulkSystemspakojidastavimNessuna valutazione finora

- Terms and Conditions of SaleDocumento8 pagineTerms and Conditions of SalepakojidastavimNessuna valutazione finora

- IP55 Outdoor EnclosuresDocumento8 pagineIP55 Outdoor EnclosuresjaroldskiNessuna valutazione finora

- DSPDocumento13 pagineDSPanshujjainNessuna valutazione finora

- LDR SensorDocumento5 pagineLDR Sensorsyed_hafeez_2Nessuna valutazione finora

- High Precession Resistive Touch Screen Driver Circuitry For Ball On Plate Balancing SystemsDocumento5 pagineHigh Precession Resistive Touch Screen Driver Circuitry For Ball On Plate Balancing SystemsMona GhazalNessuna valutazione finora

- Toyopuc Line Up EngDocumento28 pagineToyopuc Line Up Engdollare100% (1)

- PTT To Computer InformationDocumento4 paginePTT To Computer InformationYayok S. Anggoro100% (4)

- Ecut Motion Control Card Manualv1.2Documento40 pagineEcut Motion Control Card Manualv1.2Rodrigo SalazarNessuna valutazione finora

- Ee 3Documento78 pagineEe 3Llewelyn ChaseNessuna valutazione finora

- LedDocumento20 pagineLedYogesh YadavNessuna valutazione finora

- Viper 53Documento36 pagineViper 53Heêr ÔccNessuna valutazione finora

- Aalborg KS 50-1 and KS 52-1 ManualDocumento68 pagineAalborg KS 50-1 and KS 52-1 Manual海澜Nessuna valutazione finora

- Panasonic Semiconductor Selection Guide 2004 Ver.2Documento268 paginePanasonic Semiconductor Selection Guide 2004 Ver.2BradNessuna valutazione finora

- LKN304-306 212Documento16 pagineLKN304-306 212Tol SirtNessuna valutazione finora

- BeneFusion SP1 - Service Manual - V1.0 - EN PDFDocumento70 pagineBeneFusion SP1 - Service Manual - V1.0 - EN PDFTheodor LuchkinNessuna valutazione finora

- NEC Opto Part ListDocumento1 paginaNEC Opto Part ListrejincjNessuna valutazione finora

- Four-Channel Universal Analog Input Using The MAX11270: Hardware SpecificationDocumento8 pagineFour-Channel Universal Analog Input Using The MAX11270: Hardware SpecificationcutoNessuna valutazione finora

- MIC-51 Microprocessor Controller OverviewDocumento18 pagineMIC-51 Microprocessor Controller OverviewIrfan MehmoodNessuna valutazione finora

- Utilization Category 1Documento2 pagineUtilization Category 1alageshvijayNessuna valutazione finora

- TCLT100. Series Optocoupler, Phototransistor Output, SOP-4L, Long Mini-Flat PackageDocumento10 pagineTCLT100. Series Optocoupler, Phototransistor Output, SOP-4L, Long Mini-Flat PackageHưng HQNessuna valutazione finora

- 4 Pin Sop Phototransistor Photocoupler Ac Input Photocouple EL354N-G SeriesDocumento11 pagine4 Pin Sop Phototransistor Photocoupler Ac Input Photocouple EL354N-G SeriesCristian C. OlayaNessuna valutazione finora

- A Smart Card Based PrepaidDocumento17 pagineA Smart Card Based PrepaidshubamNessuna valutazione finora

- Datasheet de Un OptoacopladorDocumento13 pagineDatasheet de Un OptoacopladorDaniel Palomares GNessuna valutazione finora

- Basic Knowledge of Discrete Semiconductor Device - Toshiba Electronic Devices & Storage Corporation - Asia-EnglishDocumento10 pagineBasic Knowledge of Discrete Semiconductor Device - Toshiba Electronic Devices & Storage Corporation - Asia-EnglishReetipragya SinghNessuna valutazione finora

- Tidu 412 ADocumento39 pagineTidu 412 AVo Thanh TungNessuna valutazione finora

- How To Design An Isolated Flyback Using LM5155: Application ReportDocumento19 pagineHow To Design An Isolated Flyback Using LM5155: Application ReportAzat ŞAHİNNessuna valutazione finora

- MASTER-K120S PLC Economic TypeDocumento6 pagineMASTER-K120S PLC Economic TypeMoustaffaNessuna valutazione finora

- TPC817Documento10 pagineTPC817Felipe CostaNessuna valutazione finora

- Mosfet and Igbt Drivers Theory and Application PDFDocumento26 pagineMosfet and Igbt Drivers Theory and Application PDFLuis Eduardo RibeiroNessuna valutazione finora

- Digital Panel Meters Modular Indicator and Controller Type UDM35Documento14 pagineDigital Panel Meters Modular Indicator and Controller Type UDM35Reca DewantoroNessuna valutazione finora

- Datasheet EL817 PDFDocumento12 pagineDatasheet EL817 PDFmuhamad.badar9285Nessuna valutazione finora

- Technical Manual OPTOIO - 16/32: Integrated Management System IMS I/O Module OPTOIO-32Documento16 pagineTechnical Manual OPTOIO - 16/32: Integrated Management System IMS I/O Module OPTOIO-32徐玉坤Nessuna valutazione finora

- NCP1399AA, NCP1399BA, NCP1399AC, NCP1399AF High Performance Current Mode Resonant Controller With Integrated High-Voltage DriversDocumento44 pagineNCP1399AA, NCP1399BA, NCP1399AC, NCP1399AF High Performance Current Mode Resonant Controller With Integrated High-Voltage DriversGoensNessuna valutazione finora