Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

SDA 5642 SDA 5642X: Preliminary Data Mos Ic

Caricato da

vdăduicăDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

SDA 5642 SDA 5642X: Preliminary Data Mos Ic

Caricato da

vdăduicăCopyright:

Formati disponibili

SDA 5642 SDA 5642X

1-Chip-VPS-Decoder

Preliminary Data Features

C

SDA 5642 SDA 5642X

MOS IC

suitable VPS data editing direct from CVBS signal n-channel MOS Generating of the line synchronous 5-MHz clock for the time base and data clock by means of PLL operation Very few external components necessary Adaptative data separation Frame signal recognition Decoder for line 16 Bi-phase and start code checking I2C-Bus interface Operating voltage: 5 V Video input signal level 1 2.0 Vpp

P-DIP-14-1

P-DSO-20-1

Type SDA 5642 SDA 5642X

Ordering Code Q67100-H8547 Q67100-H8637

Package P-DIP-14-1 P-DSO-20-1

Functional Description The MOS circuit SDA 5642 is used to retrieve the required data for the Video Program System (VPS) service from the data line No. 16 which is included in the CVBS signal. These data are decoded according to the specification given in "Richtlinie ARD/ZDF Nr. 8 R 2". This circuit incorporates the digital functions of the VPS decoder SDA 5640 and the analog functions of the video processor SDA 5232 on one chip. Together with a reduced number of external components this chip is a low cost solution for the VPS detector. The single chip solution can retrieve the data from line 16 of the CVBS signal. These data are decoded, checked for transmission errors and are stored in registers for further processing by a microcontroller. The I2C-Bus interface is used for communication of a microcontroller with the VPS-decoder. The recording of programs by a VTR is controlled by the VPS label, a program related datacode which accompanies each TV program during its transmission. As a result the circuit prevents errors in the recording, as can be seen when using the timer control, when programs are delayed, or are longer than expected.

Semiconductor Group

12.94

SDA 5642 SDA 5642X

Pin Configuration (top view)

P-DIP-14-1

P-DSO-20-1

Semiconductor Group

SDA 5642 SDA 5642X

Pin Definitions and Functions Pin No. 1 1 2 2 3 4 5 6 7 8 4 5 6 7 9 10 11 Pin No. Symbol Function VSS V SS 1 VSS 2 SCL SDA CSO VCS DAVN EHB TI Ground (0 V) Ground (0 V) Ground (0 V) Clock line for I2C-Bus Data line for I2C-Bus To switch the hardware address of the chip from 21 H (CSO = low) to 23 H (CSO = high). Data slicer derives the synchronous signal from the composite video blanking signal. The form of the output signal provides information whether the set transmitter is transmitting a VPS data line. Output, on "high" level during first half frame. By means of the test pins the outputs DAVN and EHB can be switched to test signals outputs; in order to retrieve internal signals for test purposes depending on the CSO pin. PLL loop filter from system clock phase detector. Connection for the resistor determining the lower limit of the VCO frequency. Control input for VCO, increase of control voltage raises the VCO frequency. Connection for the resistors determining the upper limit of the VCO frequency. Video signal input. Positive voltage supply (+ 5 V) Positive voltage supply (+ 5 V) Positive voltage supply (+ 5 V) Not connected Not connected Not connected Not connected

P-DIP-14-1 P-DSO-20-1

9 10 11 12 13 14

12 14 15 16 17 20 19 3 8 13 18

PD1 INUL VCO IREF CVBS VDD VDD 1 VDD 2 N.C. N.C. N.C. N.C.

Semiconductor Group

SDA 5642 SDA 5642X

Block Diagram for 1-Chip-VPS-Decoder Semiconductor Group 8

SDA 5642 SDA 5642X

Circuit Description The function of this integrated circuit is to regenerate the biphase coded VPS data from the CVBS signal. These data are transferred during line 16, which is part of the vertical blanking time. After decoding and a check for transmission errors, these data can be acquired by a microcontroller for further processing. The function of the circuit is explained in more detail by means of the block diagram. The CVBS signal (pos. video) from the IF-stage is coupled to the device by means of a capacitor. The required level is typically 1 Vpp. Then the signal path is split into two parts: In the synchronous pulse separator stage the CVBS signal is clamped, filtered and the video signal is clipped away from the synchronization pulses. The output signal of this stage is VCS signal. This is used as the control signal for the line 16 decoder and is also used for the blanking of the color burst. This signal is also used in the regeneration of the internal clock (PLL). The second signal path leads to the data slicer. After amplification of the video signal the level is averaged and the slicing level is derived from this signal. The slicing level is equal to one half of the level difference between the minimum and the maximum value of the data signal. This assures the optimal slicing of the data from the video signal. The biphase coded data signal sliced from the video signal and the synchronization pulse signal VCS are used in the clock generator circuit. Based upon a PLL, this circuit generates a clock frequency of 5 MHz from the VCS signal. This clock signal is synchronized to the line frequency. During line 16 the clock is synchronized to the data signal. The synchronization of the data clock is controlled by the signal Z 16, which is the output of the decoder for line 16. This decoder is used to detect line 16 from the VCS signal and to control the data acquisition during this time. An indication signal for the first field of a frame is generated by measuring the duration of the VCS signal pulses and the interval between them. The regenerated data signal and the recovered data clock are the input signals for a decoding logic which performs the test for the start code and the biphase code. For this purpose the data signal during line 16 is searched for the start bit. This bit, which is used for the synchronization of the decoding logic, is the only bit which does not comply with the biphase format (Manchester code). The detection of the startcode, which is contained in the next six bits following the start bit, is required for the transfer of the correct data into the output register. Among the 15 bytes (8 bits/byte), which are transferred by the data line 16, only 5 bytes are important for the operation of VPS in the video recorder. These are the 5th and the 11th through the 14th byte. These 40 bits in total are transferred into a serial operating register buffer. The check for the correct transfer of the data according the biphase code is performed during the complete transfer of the data telegram in line 16. After the end of word 14 the relevant bytes are transferred into the transmission register bank. This is done when a microcontroller can read the data from the transmission register bank via the I2C-Bus interface. The device can operate on the I2C-Bus as slave-transmitter device. After reading the data, all registers are set to hex "F". Only after the correct reception of data line 16, is the register content updated again. 1) 2) 3) the start code has been identified the transmission was done correctly according to the biphase code format, and if there is no concurrent access to the device via the I2C-Bus. 9

Semiconductor Group

SDA 5642 SDA 5642X

Because of the fact that data line 16 is transmitted only once during a frame (two fields), the reading of the transfer registers has to be done within a period of greater than 40 ms between read operations. The transfer of the data via I2C-Bus is explained according to the following description and the figures 5 and 6. The communication protocol uses the following format:

START

Chip address Word 11 AS of Master of Slave AM

Word 14 Word 5 AM of Slave of Slave

NAM

STOP

The information content of the bytes 11 through 14 and the byte number 5 are given in figure 7. As a chip address for the I2C-Bus the following address is selected Bit Number: 7 0 6 0 5 1 4 0 3 0 2 0 1 CSO 0 0

If the device's chip select input is set to a low level or a high level, then bit 1 (CSO) has to be set to "0" or "1"respectively. Bit 0 is the data direction bit and has to be set to "1" because of the fact that only "Read" operations can be performed. (Slave transmitter mode.) The data transfer between master (microcontroller) and slave (VPS decoder) uses the following procedure (See figure 5): 0. 1. If the bus is not occupied idle state then the clock line and the data line are both on logic "high" levels. The master starts the data transmission by generating the start condition. This means that the SDA line is pulled down to a logic "low" level during the time when the SCL line is still on a logic "high" level. The byte address counter in the slave device is reset by this operation and points to byte 11. The following data clock pulses on the SCL line are generated by the master. For the data transfer it has to be observed that changes in the logical level on the SDA line are only possible if the SCL line is kept on a "low" level. The only exceptions are the start and stop conditions on the I2C-Bus. The master sends the chip address on the SDA line with the first 8 data clock pulses on SCL to the VPS decoder. During the 9th clock pulse the master releases the SDA line. Due to the external pull-up, the SDA line goes to a "high" level and the VPS decoder (slave) generates an acknowledge by pulling the SDA line to a "low" level. At this time the slave switches in the transmission mode. During the next 8 clock pulses the slave outputs the data of the addressed data byte to the SDA line.

2. 3.

4.

Semiconductor Group

10

SDA 5642 SDA 5642X

5.

The reception of the byte will be acknowledged by the master during the following clock pulse. This means the master pulls the SDA line to a "low" level. This action increases the byte counter in the slave increments and prepares the output of the next data byte. The slave outputs the next data byte to the SDA line. and 8. For every data byte to be transferred, steps 5 and 6 have to be repeated. To conclude the read operation, the master does not acknowledge the last byte as described in step no.9.

6. 7.

9.

During the acknowledge interval the master lets the SDA line remain in the "high" status (so called Non Acknowledge by Master, NAM). The slave understands this NAM as the end of the communication process and switches from transmit mode to receiver mode.

10. The master now has the full control over the SDA line and finishes the communication process by issuing the stop-condition. This means that during the time when the SCL is on "high" level, the microcomputer generates a "low" to "high" transmission on the SDA line. This brings the I2C-Bus into the idle state. Description of Added Functions 1. The pin Data-Valid (DAVN) allows very easy control of the availability of the VPS signal by the selected TV transmitter. If the VPS data line is available, this pin will show pulses with the frequency of the frame repetition rate. This output is set "high" at the beginning of line 16 and is reset by the data transfer pulse, an internal signal at the end of byte 14 in the data line 16. If, due to a missing VPS information in the CVBS signal, this data transferpulse is not generated, the DAVN pin remains on a "high" level. This output is also set "high", when the circuit is accessed via the I2C-Bus. This may be useful in some cases when the output is low without the presence of a CVBS signal thus pretending a TV transmitter carrying VPS information. 2. By means of the "Test" pin (TI = "high") it is possible to use the DAVN pin to output internal test signals. Depending on the status of the input CSO, the internal signal Z16N (CSO = "low") or the ADIX signal (CSO = "high") is switched to the DAVN output. The data transfer from the VPS decoder to the microcomputer starts after the master controller has transmitted the chip address of SDA 5642. This chip address has to be identical with the hardware address of the VPS decoder. By means of the CSO input it is possible to switch this hardware address from 21 H (CSO = "low") to 23 H (CSO = "high"). The output EHB generates an indication for both of the fields in a frame. During the firstfield this pin shows the "high" level. The correct timing of this pulse is given in figure 4. For test purpose this pin can be switched to the test signal output mode. This is done by setting the TI pin to high. The output signal in this mode depends on the logical level on the CSO pin. If CSO is "low", the internal signal LL64ON is generated, if the CSO pin is "H" the output signal is DZDAX, which is also an internal test signal, is generated.

3.

4.

Semiconductor Group

11

SDA 5642 SDA 5642X

Absolute Maximum Ratings T A = 25 C Parameter Ambient temperature Storage temperature Total power dissipation Power dissipation per output Input voltage Supply voltage Thermal resistance Symbol

T T

Limit Values min. typ. max. 0 40 70 125 300 10 0.3 0.3 6 6 80

Unit C C mW mW V V K/W

Test Condition in operation by storage

A stg tot DQ

P P V V R

IM DO th SU

Operating Range Supply voltage Supply current VDD IDD 0 4.5 5 5.5 50 70 V mA C

Ambient temperature range T A

Semiconductor Group

12

SDA 5642 SDA 5642X

Characteristics T A = 25 C Parameter Symbol Limit Values min. typ. max. Unit Test Condition

Input Signals SDA, SCL H - input voltage L - input voltage Input capacitance Input voltage

V V

IH IL I

3.0 0

V DD 0.8 10 10

V V pF

A

C I

IM

Input Signals CSO, TI H - input voltage L - input voltage Input capacitance Input current

V V C I

IH IL I

2.0 0

V DD 0.8 10 10

V V pF

A

IM

Input Signals CVBS (pos. Video, neg. Sync) Video input signal level Synchron signal amplitude Data amplitude Coupling capacitor H - input current L - input current Source impedance Leakage resistance at coupling capacitor

V V V

CVBS SYNC DAT C

0.7 0.15 0.25

1.0 0.3 0.5 33

2.0 1.0 1.0

V V V nF

A A

C I I

IH IL S C

10 1000 400 100 250 0.91 1 1.2

V I= 5 V VI = 0 V

Semiconductor Group

13

SDA 5642 SDA 5642X

Characteristics (contd) T A = 25 C Parameter Symbol Limit Values min. typ. max. Unit Test Condition

Output Signals DAVN, EHB, VCS H - output voltage L - output voltage

V V

QH QL

DD

0.5

V 0.4 V

I = 100 A

Q Q

I = 1.6 mA

Output Signals SDA (Open-Drain-Stage) L - output voltage Permissible output voltage PLL Loop Filter Components Resistance at PD1 Resistance at VCO Attenuation resistance Integration capacitor

R R R

1 2 3

QL

0.4 5.5

V V

I = 3.0 mA

Q

100 820 5.6 100

150

k k nF

VCO Frequence Range Adjustment Resistance at IREF (for bias R 4 current adjustment) Resistance at INUL (for quiescent current adjustment)

R

5

100 820

k k

Semiconductor Group

14

SDA 5642 SDA 5642X

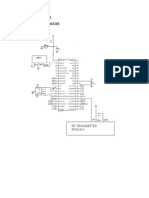

Test Circuit Data Line Receiver

Application Circuit Data Line Receiver Semiconductor Group 15

SDA 5642 SDA 5642X

Figure 1 CVBS Signal with Position of VPS Data Line

Figure 2 Insertion of Data Line into CVBS Signal Semiconductor Group 16

SDA 5642 SDA 5642X

Figure 3 Video Signal

Figure 4 VCS-DAVN-EHB Signal Semiconductor Group 17

SDA 5642 SDA 5642X

Figure 5 Transfer Protocol for I2C-Bus

Figure 6 I2C-Bus Timing Semiconductor Group 18

SDA 5642 SDA 5642X

Parameter Clock frequency Inactive time period prior to new transmission start-up

Symbol fSCL tBUF

Limit Values min. max. 0 4.7 4.0 100

Unit kHz

s s

Hold time during start condition tHD; STA (subsequent to this time period the first Clock pulse will be generated) LOW-period of clock HIGH-period of clock Set-up time for Data Rise time for SDA and SCL signal Fall time for SDA and SCL signal Set-up time for SCL clock during STOP conditions t LOW tHIGH tSU; DAT tR tF tSU; STO

4.7 4.0 250 1 300 4.7

s s

ns

s

ns

s

All values referred to VIH and VIL levels.

Semiconductor Group

19

SDA 5642 SDA 5642X

Figure 7 Data Format of Additional Information in Data Line 16 Semiconductor Group 20

Potrebbero piacerti anche

- Cat 3508-B Electr - DiagramDocumento2 pagineCat 3508-B Electr - DiagramCésar Pérez88% (8)

- Exploring Arduino: Tools and Techniques for Engineering WizardryDa EverandExploring Arduino: Tools and Techniques for Engineering WizardryValutazione: 4.5 su 5 stelle4.5/5 (5)

- Pic 18 F 4520Documento51 paginePic 18 F 4520sitizarina78100% (1)

- Using The Mid-Range Enhanced Core PIC16 Devices' MSSP Module For Slave I C CommunicationDocumento14 pagineUsing The Mid-Range Enhanced Core PIC16 Devices' MSSP Module For Slave I C CommunicationDario Darius100% (2)

- DC Motor Are of 3 Types They Are .Documento12 pagineDC Motor Are of 3 Types They Are .Krishna100% (1)

- Programming PIC16F877A Microcontroller for LED Pattern Display and Sensor ReadingDocumento57 pagineProgramming PIC16F877A Microcontroller for LED Pattern Display and Sensor ReadingDoodee Mohammed100% (4)

- Electronic A 51 Projects Using CD4011Documento53 pagineElectronic A 51 Projects Using CD4011Juan Carlos Cervantes89% (9)

- 7 A H-Bridge for DC-Motor ApplicationsDocumento29 pagine7 A H-Bridge for DC-Motor ApplicationsJoão JoséNessuna valutazione finora

- JET Emergency Power Supply: Installation and Operation ManualDocumento28 pagineJET Emergency Power Supply: Installation and Operation ManualIndiomarcio Ghelardi100% (1)

- Advanced Coal Fired Power Plants Single Line DiagramDocumento20 pagineAdvanced Coal Fired Power Plants Single Line DiagramJhen Gong ChengNessuna valutazione finora

- Voltage Dip Immunity of Equipment and InstallationsDocumento250 pagineVoltage Dip Immunity of Equipment and InstallationsHans De Keulenaer100% (1)

- Using The PIC Devices' SSP and MSSP Modules For Slave I2C CommunicationDocumento20 pagineUsing The PIC Devices' SSP and MSSP Modules For Slave I2C CommunicationthelutheranknightNessuna valutazione finora

- I2C TutorialDocumento9 pagineI2C TutorialLuis Angel Nina Sánchez100% (3)

- Clause 50: Wis Overview: Andy Baldman Unh Interoperability Lab Dec 13, 2000Documento27 pagineClause 50: Wis Overview: Andy Baldman Unh Interoperability Lab Dec 13, 2000very lili gunawanNessuna valutazione finora

- Interfacing Microchip'S Mcp3201 Analog-To-Digital Converter To The Picmicro MicrocontrollerDocumento21 pagineInterfacing Microchip'S Mcp3201 Analog-To-Digital Converter To The Picmicro MicrocontrollerMaxi NozikovskyNessuna valutazione finora

- Autonomous ManualDocumento12 pagineAutonomous ManualVarun ReddyNessuna valutazione finora

- Cmps03 ManualDocumento3 pagineCmps03 ManualEnggewe AwaNessuna valutazione finora

- Abstract 2. Circuit Diagram 3. Explanation 4. Working 5. Program Code 6. PCB Layout Fabrication and Assembly 8. Conclusion 9. Reference 10. DatasheetDocumento22 pagineAbstract 2. Circuit Diagram 3. Explanation 4. Working 5. Program Code 6. PCB Layout Fabrication and Assembly 8. Conclusion 9. Reference 10. Datasheetaditya_pundirNessuna valutazione finora

- I2CDocumento9 pagineI2CPrasanna VenkatesanNessuna valutazione finora

- Example of Serial Port W/R Operation SCLKDocumento5 pagineExample of Serial Port W/R Operation SCLKEliezer Peña del AguilaNessuna valutazione finora

- Lab # 03 I2C WriteDocumento4 pagineLab # 03 I2C WriteSOBAN KHANNessuna valutazione finora

- I2C Interfacing To XC3S400 FPGADocumento14 pagineI2C Interfacing To XC3S400 FPGAMahesh BhatkalNessuna valutazione finora

- I2c Bus Contr ReportDocumento13 pagineI2c Bus Contr ReportSreeshmith Sreedar100% (2)

- 24C02Documento27 pagine24C02Biswajit SarkarNessuna valutazione finora

- ST24 25C04, ST24 25W04Documento16 pagineST24 25C04, ST24 25W04Zoran KovacevicNessuna valutazione finora

- The I2C System Uses A Serial Data LineDocumento7 pagineThe I2C System Uses A Serial Data LineJerry JamesNessuna valutazione finora

- 4.1.3 Definition of The EE1002 and EE1002A Serial Presence Detect (SPD) EEPROMS 1. ScopeDocumento24 pagine4.1.3 Definition of The EE1002 and EE1002A Serial Presence Detect (SPD) EEPROMS 1. ScopemboopathiNessuna valutazione finora

- Tsa5512 CNV 3Documento21 pagineTsa5512 CNV 3soft4gsmNessuna valutazione finora

- 24C64 BMDocumento10 pagine24C64 BMdonghungstbNessuna valutazione finora

- 2.1 LPC2103 Microcontroller: 2.1.1 FeaturesDocumento18 pagine2.1 LPC2103 Microcontroller: 2.1.1 FeaturesBhaskar Rao PNessuna valutazione finora

- 512 Kbit Serial I C Bus EEPROM: DescriptionDocumento19 pagine512 Kbit Serial I C Bus EEPROM: DescriptionJavier MainarNessuna valutazione finora

- Agribot Project PresentationDocumento21 pagineAgribot Project Presentationumaiya1990100% (1)

- Manual RFID FastTagReaderDocumento40 pagineManual RFID FastTagReaderMARIGANTI SRINIVASULUNessuna valutazione finora

- Features Description: CMOS Manchester Encoder-DecoderDocumento14 pagineFeatures Description: CMOS Manchester Encoder-DecoderKaty KimberlynNessuna valutazione finora

- I2C-Master Core SpecificationDocumento17 pagineI2C-Master Core Specificationvarunmr100% (1)

- I2C Protocol in Fpga Using VHDL: Main Project Interim Report As A Partial Fullment of The CurriculumDocumento18 pagineI2C Protocol in Fpga Using VHDL: Main Project Interim Report As A Partial Fullment of The CurriculumShuvra Saha100% (1)

- SPI Pins SPI Clock SPI Master Slave Connection SPI Registers DAC SpecificationsDocumento7 pagineSPI Pins SPI Clock SPI Master Slave Connection SPI Registers DAC Specificationspiyushpandey100% (1)

- DS1624Documento15 pagineDS1624jnax101Nessuna valutazione finora

- 09 - I2C Serial CommunicationsmDocumento10 pagine09 - I2C Serial CommunicationsmSorabh DungNessuna valutazione finora

- Datasheet SDP600series Differential Pressure SensorDocumento9 pagineDatasheet SDP600series Differential Pressure SensorRahul Albuquerque100% (1)

- LS7366 PulseCounter PDFDocumento10 pagineLS7366 PulseCounter PDFJoan WascNessuna valutazione finora

- Mpi ReportDocumento20 pagineMpi ReportHoorain SajjadNessuna valutazione finora

- BoxDocumento20 pagineBoxu2006262918Nessuna valutazione finora

- Unit 3 Serial InterfacesDocumento111 pagineUnit 3 Serial Interfacesmtechewit100% (2)

- 24 LC 16 BDocumento12 pagine24 LC 16 BAnonymous UxrPsIVNessuna valutazione finora

- Analog Device Micro ConverterDocumento20 pagineAnalog Device Micro ConvertershaileshNessuna valutazione finora

- Nonvolatile Memory 8-Kbit E Prom With C Bus Interface SDA 2586-5Documento12 pagineNonvolatile Memory 8-Kbit E Prom With C Bus Interface SDA 2586-5insomnium86Nessuna valutazione finora

- Device Interconnects and Peripherals (Supporting Resources)Documento10 pagineDevice Interconnects and Peripherals (Supporting Resources)Rudra KNessuna valutazione finora

- SystemManual Rev0Documento44 pagineSystemManual Rev0localonNessuna valutazione finora

- Data Sheet: 1.3 GHZ Bidirectional I C-Bus Controlled SynthesizerDocumento19 pagineData Sheet: 1.3 GHZ Bidirectional I C-Bus Controlled Synthesizerlu1agpNessuna valutazione finora

- SPI in LPC2148 1567318675748Documento9 pagineSPI in LPC2148 1567318675748RaviNessuna valutazione finora

- DatasheetDocumento6 pagineDatasheetUlma HudinNessuna valutazione finora

- Pic18 Serial CommunicationDocumento25 paginePic18 Serial Communicationadamwaiz100% (3)

- Using The MSSP Module To Interface I2CDocumento16 pagineUsing The MSSP Module To Interface I2Csoft4gsmNessuna valutazione finora

- Circuit Diagram Wireless TransmitterDocumento17 pagineCircuit Diagram Wireless Transmitterumaiya1990100% (2)

- 24C02 24C04 24C08 24C16: Bookly MicroDocumento10 pagine24C02 24C04 24C08 24C16: Bookly MicroHùng Nguyễn VănNessuna valutazione finora

- Dual Digital Potentiometer Chip with Ultra-Low Power and Temperature CompensationDocumento12 pagineDual Digital Potentiometer Chip with Ultra-Low Power and Temperature CompensationManuel NolascoNessuna valutazione finora

- ADC Data Acquisition and AnalysisDocumento8 pagineADC Data Acquisition and AnalysisAnonymous kT0ONWNessuna valutazione finora

- Turbo IC, Inc.: Cmos I C 2-Wire Bus 4K Electrically Erasable Programmable Rom 512 X 8 Bit EepromDocumento8 pagineTurbo IC, Inc.: Cmos I C 2-Wire Bus 4K Electrically Erasable Programmable Rom 512 X 8 Bit EepromMohamed ZayedNessuna valutazione finora

- 16K 1.8V I C Serial EEPROM: FeaturesDocumento12 pagine16K 1.8V I C Serial EEPROM: FeaturesKrzysztof BondkaNessuna valutazione finora

- I2s ProtocolDocumento28 pagineI2s ProtocolNaruto UzumakiNessuna valutazione finora

- Unit III Peripherals and Interfacing GuideDocumento98 pagineUnit III Peripherals and Interfacing Guideabu taherNessuna valutazione finora

- 4-Digit LED Driver with I2C Interface Datasheet (SAA1064Documento19 pagine4-Digit LED Driver with I2C Interface Datasheet (SAA1064giapy0000Nessuna valutazione finora

- Anais Do Workshop De Micro-ondasDa EverandAnais Do Workshop De Micro-ondasNessuna valutazione finora

- Componentes SMDDocumento16 pagineComponentes SMDRicardo SantosNessuna valutazione finora

- 12.6 Service Manual PDFDocumento22 pagine12.6 Service Manual PDFvdăduicăNessuna valutazione finora

- S9014a DatasheetDocumento4 pagineS9014a DatasheetgajangiNessuna valutazione finora

- 2N2905-2N2907 Transistor Data SheetDocumento5 pagine2N2905-2N2907 Transistor Data SheetMicrotech SolutionsNessuna valutazione finora

- ThyristorDocumento1 paginaThyristorvdăduicăNessuna valutazione finora

- Toshiba TA8445K Power Amplifier for Driving a Deflection Circuit of a Color TelevisionDocumento8 pagineToshiba TA8445K Power Amplifier for Driving a Deflection Circuit of a Color TelevisionClaudio RodriguezNessuna valutazione finora

- Cat 24 WC 02Documento9 pagineCat 24 WC 02Feroz KhanNessuna valutazione finora

- 83C055Documento40 pagine83C055vdăduicăNessuna valutazione finora

- TYP 212 - TYP 2012: SCR For Overvoltage ProtectionDocumento6 pagineTYP 212 - TYP 2012: SCR For Overvoltage ProtectionvdăduicăNessuna valutazione finora

- 905 Mitsubishi M5218alDocumento6 pagine905 Mitsubishi M5218alvdăduicăNessuna valutazione finora

- 908 Mitsubishi m5218Documento6 pagine908 Mitsubishi m5218vdăduicăNessuna valutazione finora

- TNY253Documento20 pagineTNY253Nemere HunorNessuna valutazione finora

- 7Documento9 pagine7vdăduicăNessuna valutazione finora

- 24 C 02 ADocumento13 pagine24 C 02 ARun MouthNessuna valutazione finora

- 24C08ADocumento14 pagine24C08AAlex Morales PalominoNessuna valutazione finora

- 2SD2058Documento4 pagine2SD2058Benhur SmehaNessuna valutazione finora

- HGTG30N60A4D: 600V, SMPS Series N-Channel IGBT With Anti-Parallel Hyperfast Diode FeaturesDocumento9 pagineHGTG30N60A4D: 600V, SMPS Series N-Channel IGBT With Anti-Parallel Hyperfast Diode FeaturesvdăduicăNessuna valutazione finora

- 2SK1275Documento4 pagine2SK1275vdăduicăNessuna valutazione finora

- Ka5S-Series: KA5S0765C/KA5S0965/KA5S12656/KA5S1265 Fairchild Power Switch (FPS)Documento16 pagineKa5S-Series: KA5S0765C/KA5S0965/KA5S12656/KA5S1265 Fairchild Power Switch (FPS)Buga BuniciNessuna valutazione finora

- 6Documento8 pagine6vdăduicăNessuna valutazione finora

- TO-220F Plastic-Encapsulate Transistors: Jiangsu Changjiang Electronics Technology Co., LTDDocumento2 pagineTO-220F Plastic-Encapsulate Transistors: Jiangsu Changjiang Electronics Technology Co., LTDvdăduicăNessuna valutazione finora

- Power Transistor (50V, 3A) : 2SD1760 / 2SD1864Documento3 paginePower Transistor (50V, 3A) : 2SD1760 / 2SD1864vdăduicăNessuna valutazione finora

- 4Documento14 pagine4vdăduicăNessuna valutazione finora

- 2SK854Documento4 pagine2SK854vdăduicăNessuna valutazione finora

- Power Transistor (60V, 3A) : TransistorsDocumento1 paginaPower Transistor (60V, 3A) : TransistorsvdăduicăNessuna valutazione finora

- 2 SK 170Documento5 pagine2 SK 170vdăduicăNessuna valutazione finora

- HOT D1877 Datasheet PDFDocumento1 paginaHOT D1877 Datasheet PDFlaurentina52Nessuna valutazione finora

- 2SD1267Documento4 pagine2SD1267vdăduicăNessuna valutazione finora

- Silicon NPN Epitaxial Planer Type: TransistorDocumento2 pagineSilicon NPN Epitaxial Planer Type: TransistorvdăduicăNessuna valutazione finora

- Lenovo Thinkpad Helix Hardware Maintenance ManualDocumento82 pagineLenovo Thinkpad Helix Hardware Maintenance ManualEdward GillNessuna valutazione finora

- Fluke 190 504 ManualDocumento158 pagineFluke 190 504 Manualphuc nguyenNessuna valutazione finora

- TC P50VT20Documento145 pagineTC P50VT20floren arizaNessuna valutazione finora

- Advance E-Bike-WPS Office-1 Hari Hari Hari Hari HariDocumento26 pagineAdvance E-Bike-WPS Office-1 Hari Hari Hari Hari HariVIJAYNessuna valutazione finora

- Journal Jpe 18-3 249301697Documento8 pagineJournal Jpe 18-3 249301697Carlos DPNessuna valutazione finora

- NFPA 110 Compliant NRG Series Battery ChargersDocumento2 pagineNFPA 110 Compliant NRG Series Battery ChargersService Brags & Hayes, Inc.Nessuna valutazione finora

- IPU43K4-B3A21 PSU SpecificationDocumento2 pagineIPU43K4-B3A21 PSU SpecificationCharmer JiaNessuna valutazione finora

- VLC Install GuideDocumento34 pagineVLC Install GuidevirtechNessuna valutazione finora

- Instrukcja XT 546 - WWW - Ebmia.plDocumento3 pagineInstrukcja XT 546 - WWW - Ebmia.plAwdhesh Singh BhadoriyaNessuna valutazione finora

- DS IN0017 - en - Co - 20804Documento8 pagineDS IN0017 - en - Co - 20804NeoZeruelNessuna valutazione finora

- Welding Power SupplyDocumento3 pagineWelding Power SupplyDeepak Kumar Kant KesriNessuna valutazione finora

- Three Operating Regions of BJTsDocumento50 pagineThree Operating Regions of BJTsTamirat SilashNessuna valutazione finora

- Comparison Between ASIC TechnologyDocumento12 pagineComparison Between ASIC Technologyasifpatel1234Nessuna valutazione finora

- En Acs580-01 HW e A5 ScreenDocumento258 pagineEn Acs580-01 HW e A5 ScreenpravinNessuna valutazione finora

- SvcField8050 C500 CF5001MANUALDocumento428 pagineSvcField8050 C500 CF5001MANUALMarius ManNessuna valutazione finora

- Rembo LED Surface - Suspended Linear Task LightsDocumento1 paginaRembo LED Surface - Suspended Linear Task LightshelloovationNessuna valutazione finora

- IRMCK341: Sensorless Motor Control IC For AppliancesDocumento36 pagineIRMCK341: Sensorless Motor Control IC For AppliancesMeselao Meselao MeselaoNessuna valutazione finora

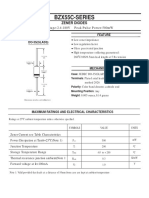

- T1 Datasheet DZ BZX55C-SeriesDocumento3 pagineT1 Datasheet DZ BZX55C-SeriesAlex GrigorieNessuna valutazione finora

- Installation Manual: Rbc-Ams51E-EsDocumento30 pagineInstallation Manual: Rbc-Ams51E-EsJaime A. AlvarezNessuna valutazione finora

- Allen Bradley AB 193 T1AA80 PDFDocumento11 pagineAllen Bradley AB 193 T1AA80 PDFDjonky TanaumaNessuna valutazione finora

- Accesorios FBP PB DPDocumento20 pagineAccesorios FBP PB DPEl HarryNessuna valutazione finora

- Circuit Elements and Sources ExplainedDocumento26 pagineCircuit Elements and Sources ExplainedHammad HussainNessuna valutazione finora

- Electric Service Guidelines for Indiana Commercial DevelopmentsDocumento23 pagineElectric Service Guidelines for Indiana Commercial DevelopmentsmattlaneNessuna valutazione finora

- Solar-Powered Battery Charging With Highly Efficient Buck ConverterDocumento20 pagineSolar-Powered Battery Charging With Highly Efficient Buck ConverterSusanNessuna valutazione finora

- 12-Chapter 3 3.1-3.2 Load Flow AnalysisDocumento5 pagine12-Chapter 3 3.1-3.2 Load Flow AnalysisRyan Anthony UmaliNessuna valutazione finora