Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

The Inverter - Static Properties

Caricato da

sreekanthreddy peramTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

The Inverter - Static Properties

Caricato da

sreekanthreddy peramCopyright:

Formati disponibili

45

3. The inverter - static

properties

In this chapter the basic properties of the inverter will be considered. While

not being a very exciting device per se, the inverter has some very basic

properties to which the properties of any logic gate, or analog amplifier

circuit for that matter, can be related. Both the static and the dynamic

properties of the inverter will be considered. The static properties concern

the logic function of the inverter, while the dynamic properties concerns the

transient switching of the output from one logical state to the other as a

result of a switching input.

Fig. 3.1. The inverter as a symbol for a Boolean truth table.

In essence, the inverter is a symbol representing a very simple Boolean truth

table as illustrated in Fig. 3.1, where a logical zero input produces a logical

one at the output and vice versa. In this model nothing is said about the

propagation delay between the switching of the input and the switching of

the input. To account for this dynamic property of the electronic

implementation of an inverter, a delay model could be added as shown in

Fig. 3.2. Delay models range from very simple models for hand calculations

to rather complicated models for timing analysis using electronic design

automation (EDA) tools. The most simple delay model only considers a

constant delay, while a more complicated delay model considers both the

size of the inverter and the output load as well as the input switching speed.

One value for the propagation delay that is often referred to is the fanout-

of-four delay, the FO4 delay, see Fig. 3.3 which shows the delay of an

inverter loaded by four identical inverters

V

IN

VIN VOUT

0 1

1 0

V

OUT

46

Fig. 3.2. An inverter with a delay model.

Fig. 3.3. An inverter with a fanout-of- four (FO4) delay.

3.1 Static properties

The aim of this section is to describe the static properties of a CMOS

inverter in rather simple terms.

The simplest electronic implementation of an inverter requires an

electronic switch such as the N-switch described in chapter 1, and a load

resistor as shown in Fig. 3.4. Here, a logical one is represented by the supply

voltage V

DD

, while a logical zero is represented by zero voltage V

SS

, or

ground. For this inverter to be robust the voltage transfer characteristic

(VTC) should be centered on V

DD

/2 so that the input voltage when the

inverter flips between logical states is V

DD

/2. The low output voltage when

the MOSFET is ON is given by resistive voltage division by

.

ON

OL DD

ON L

R

V V

R R

=

+

(3.1)

For this output voltage to go low the MOSFET ON resistance should be

much smaller than the load resistance, i.e. R

ON

<< R

L

. In Fig. 3.4 a simplified

voltage transfer characteristic is shown where the MOSFET switch is

assumed to turn on at V

IN

=V

DD

/2 and to have a constant on-resistance R

ON

(solid line). The real voltage transfer characteristic when the MOSFET

V

IN

V

OUT

FO4

delay

V

OUT

V

IN

A

47

switch is turned on at its threshold voltage V

TN

and the on-resistance R

ON

is

voltage dependent is indicated by the dashed line.

In CMOS technology the resistor could be implemented by using a pseudo-

NMOS load in form of a p-channel MOSFET as shown in Fig. 3.5. When

used as an amplifier in an analog design, the p-channel load device is usually

biased through a current mirror designed so that current I

B

, or fractions of

this current, also flows through the inverter.

Fig. 3.5. The pseudo-NMOS-inverter.

A more power-efficient implementation of an inverter uses two

complementary switches as shown in Fig. 3.6. For a high input V

IH

, the N-

switch turns ON and the P-switch turns OFF making the output go low, V

OL

.

For a low input V

IL

the N-switch turns OFF and the P-switch turns ON

making the output go high, V

OH

. Since one of the two switches is always

v

IN

v

OUT

V

DD

V

B

v

IN

v

OUT

V

DD

V

B

V

DD

I

B

Fig. 3.4. The basic inverter function illustrated with an N-switch and a load

resistance R

L

and its voltage transfer characteristic (VTC).

V

OUT

V

IN

V

DD

V

DD

V

DD

/2

V

DD

/2

V

OL

V

OH

V

SS

R

OFF

R

ON

V

IH

V

OL

V

IL

V

OH

V

DD

V

DD

V

SS

V

SS

R

L

V

IN

V

OUT

V

DD

V

SS

R

L

R

L

48

OFF, there is no static power dissipation in any of the two logic states, a fact

that is the main advantage of the CMOS technology.

In this CMOS implementation of an inverter there is a full output voltage

swing between the supply rails V

DD

and V

SS

, independent of the ON

resistances of the switches. The switching voltage of the CMOS inverter is

given by the input voltage for which both MOSFET devices deliver the same

saturation current. For a robust design with a switching voltage equal to

V

DD

/2 both MOSFETs should have the same driving capability.

In more detail, the accepted output voltage range for a logical one is

given by V

OH,min

<V

OUT

<V

DD

, while the accepted output voltage range for a

logical zero is given by V

SS

<V

OUT

<V

OL,max

, see Fig. 3.7. If the input voltage

resulting in V

OH,min

is denoted V

IL,max

, and the input voltage resulting in

V

OL,max

is denoted V

OL,min

we can draw a simplified, piecewise linear, voltage

transfer characteristics as shown in Fig. 3.7. In this VTC we can see that

V

OL,max

<V

IL,max

, and V

IH,min

<V

OH,min

, facts that indicate good noise margins.

These noise margins, NM

H

and NM

L

, are defined in Fig. 3.7.

Another property of the CMOS inverter is its level-restoring properties.

In Fig. 3.8 we can see that even if the input to a CMOS inverter is way

outside the allowed voltage ranges, the output voltage of is fully restored

already after two inverters. This is a consequence of the nonlinear voltage

transfer characteristics.

OFF

OFF

ON

ON

V

IH

V

OL

V

IL

V

OH

V

DD

V

DD

V

SS

V

SS

V

OUT

V

IN

V

DD

V

DD

V

DD

/2

V

DD

/2

V

OL

V

OH

Fig. 3.6. The CMOS-inverter function illustrated with switches and a

simplified voltage transfer characteristic (VTC).

V

SS

VTC

V

IN

V

OUT

V

DD

V

SS

49

Fig. 3.8. Illustration of the level-restoring properties of the inverter.

In summary, the basic properties of a CMOS inverter are

- Full voltage swing from rail to rail

- No static power dissipation

- Robustness

- Noise margins

- Level-restoring.

V

1

V

2

V

IN

Fig. 3.7. Definition of noise margins using a simplified piecewise-linear

voltage transfer curve (VTC).

V

DD

V

OH,min

V

OL,max

V

SS

V

SS

V

IL,max

V

IH,min

V

DD

V

OUT

N

MH

N

ML

V

IH,min

V

IL,max

V

IN

V

DD

V

SS

50

3.2 The voltage transfer curve (VTC) in detail

When calculating the inverter voltage transfer characteristic, we use a simple

circuit model where the MOSFET is represented by its ON resistance in the

linear region and by its saturation current I

DSAT

in the saturation region.

Exercise 3.1: Derive the equations describing the MOS-inverter voltage

transfer characteristic in Fig. 3.9.

Solution. The load line of the resistor is given by

.

DD OUT

L

V V

I

R

= (3.2)

The n-channel switch is either saturated or acting as a resistor: in the green

region where the MOSFET is saturated equal currents through the load

resistor and the MOSFET yield

R

ON

V

OUT

V

OUT

V

DD

V

SS

R

L

I

DSAT

V

SS

V

DD

R

L

S

U

B

T

H

R

E

S

H

O

L

D

R

E

G

I

O

N

V

SS

V

IN

V

OUT

V

DD

R

L

Fig. 3.9. The basic inverter with a load resistance R

L

and its voltage transfer

characteristic.

51

( )

2

.

2

DD OUT

DSAT IN TN

L

V V k

I V V

R

= = (3.3)

Solving for V

OUT

yields the following equation describing a parabola for the

transfer characteristic in the green region

( )

2

.

2

L

OUT DD IN TN

kR

V V V V = (3.4)

Using the same condition of current identity in the blue region where the

MOSFET behaves like a nonlinear resistor, we obtain

2

2 1 1

.

DD

OUT IN TN IN TN

L L L

V

V V V V V

kR kR kR

| |

= + +

|

\ .

(3.5)

When kR

L

, this expression simplifies to

( )

,

ON DD

OUT

L IN TN L

R V

V

kR V V R

=

which is nothing but plain simple voltage division between resistors R

ON

and

R

L

.

The basic parameter of this VTC is given by kR

L

; the higher the value of this

parameter, the better the inverter characteristic and the higher the voltage

amplification in the switching region. Large values of kR

L

means that R

L

>>

R

ON

, i. e. the MOSFET must be designed for high driving capability with

respect to the load resistance. This is why this logic style is named ratioed

logic. This VTC is again illustrated in the right-hand diagram of Fig. 3.10

while the left-hand diagram shows the resistor load line and MOSFET IV-

characteristic for two different input gate voltages.

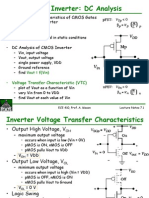

.1 The CMOS inverter

The voltage transfer characteristic of the CMOS inverter can be derived

similarly. However, it is just a little bit more complicated since we must

keep track of the operation regions of both the nMOS transistor and the

pMOS load transistor. As shown in Fig. 3.11, we have to keep track of the

following regions and MOSFET bias conditions:

52

Fig. 3.10. Load curves for the n-channel MOSFET for two different input

voltages plotted together with the resistor load line (left), and the inverter

voltage transfer characteristic (right).

Fig. 3.11. Regions of MOSFET operation for the CMOS inverter.

A

:

s

u

b

t

h

r

e

s

h

o

l

d

r

e

g

i

o

n

V

UT

V

DD V

IN

V

TN

V

DD

V

DD

+V

TP

BothMOSFETs

saturated

D:nMOS resistive

B:pMOS resistive

RegionA,B

V

OUT

V

DD

R

ON,P

I

DSAT,N

V

OUT

V

DD

I

DSAT,N

V

DD

R

ON,N

I

DSAT,P

RegionC

V

OUT

I

DSAT,P

RegionD,E

RegionC:

E

:

s

u

b

t

h

r

e

s

h

o

l

d

r

e

g

i

o

n

53

- both n-channel and p-channel MOSFETs are saturated (region C)

- n-channel MOSFET is saturated (or OFF) and p-channel MOSFET

is linear (regions A and B)

- p-channel MOSFET is saturated (or OFF) and n-channel MOSFET

is linear (regions C and D)

The circuit element representation of the MOSFETs in the CMOS inverter is

shown at the top of Fig. 3.11. In Fig. 3.12 we can see the current/voltage

characteristics of the two MOSFETs for three different input voltages (left)

and the resulting bias points on the VTC on the right. Most easily recognized

is the illustration of region C marked V

IN

=V

SW

. In the left-hand diagram we

can see that for this input voltage both MOSFETs deliver the same saturation

currents resulting in a region of infinite voltage amplification in the right-

hand VTC. This is the input voltage V

SW

for which the inverter flips. It can

be derived from the following equation of equal saturation currents:

2 2

where and .

2 2

p

n

GSTN SGTP GSTN IN TN SGTP DD IN TP

k

k

V V V V V V V V V = = = + (3.6)

The resulting switching voltage is then given by

1

DD TP TN

in sw

V V xV

V V

x

+ +

= =

+

, where x=k

N

/ k

P

. (3.7)

For V

TN

=-V

TP

and x=1 the switching voltage is V

DD

/2. For strong n-channel

devices, x >1, V

sw

< V

DD

/2 and for strong p-channel devices, V

sw

> V

DD

/2,

Fig.3.12. Finding bias points on the CMOS inverter VTC.

54

In region B, where the p-channel device is resistive, the VTC curve can be

derived from the following equal current condition:

( )

2

2 2

n DD OUT

GSTN p SGTP DD OUT

k V V

V k V V V

| |

=

|

\ .

, (3.8)

yielding

( ) ( )

2 2

.

N

OUT IN TP DD IN TP IN TN

P

k

V V V V V V V V

k

= + +

(3.9)

Similarly for region D, where the n-channel device is resistive, we obtain the

following equal current condition

( )

2

,

2

UT

N IN TN UT P DD IN TP

V

k V V V k V V V

| |

= +

|

\ .

(3.10)

yielding

( ) ( )

2 2

.

P

OUT IN TN IN TN DD IN TP

N

k

V V V V V V V V

k

= +

(3.11)

3.3 Process corners

Due to process variations k

n

/k

p

varies across the wafer and between wafers.

This results in a spread of inverter switching voltages as shown in Fig. 3.13.

The process corners of the MOSFET driving capabilities are also illustrated.

Fig. 3.13. MOSFET driving capability process window (right) and resulting

spread of inverter switching voltages (left).

k

P

HI,HI

k

N

LO,HI

HI,LO

LO,LO

55

3.4 The inverter as an analog amplifier

The inverter is of course a digital device, but the circuit implementation of

the inverter also works as an amplifier of small analog signals. This is

illustrated in Fig. 3.14. The figure shows how a MOSFET with a load

resistor has been biased in the saturation region where the MOSFET acts as a

voltage-controlled current source. A small sinusoidal input signal, on top of

the bias voltage, results in an amplified sinusoidal at the output. The voltage

amplification can be calculated from the small signal model, A

v

=-g

m

R

L

.

Fig. 3.14. Basic amplifier circuit.

v

OUT

V

SS

I

DSAT

R

L

V

SS

v

IN

v

OUT

V

DD

R

L

v

out

=g

m

R

L

v

in

V

SS

g

m

v

in

R

L

largesignalmodel smallsignalmodel

S

U

B

T

H

R

E

S

H

O

L

D

R

E

G

I

O

N

56

The design methodology assumed by the analog designer is to use nonlinear

large-signal analysis for calculating the bias point and the linear region of

operation of the amplifier, and to use linear small-signal analysis for

calculating the voltage amplification. The output voltage range of the

amplifier is limited by distortion due to the nonlinear transfer characteristic.

The linearized small-signal transfer curve with slope A

v

is shown dashed (in

red). The small-signal amplification is given by

.

OUT OUT OUT

v L m

IN OUT IN

v v i

A R g

v i v

c c c

= = =

c c c

(3.12)

The nonlinearity of the transfer curve that is an advantage in digital designs,

giving the inverter its level restoring properties, is a disadvantage in analog

designs due to distortion and creation of overtones.

3.4.1 The pseudo-NMOS amplifier

The most common analog integrated circuit CMOS amplifier is the pseudo-

NMOS-inverter amplifier shown in Fig. 3.15. In this design, the load resistor

is implemented by use of a pMOS device since area-efficient resistors are

not available in CMOS integrated circuit technology. The pMOS load

transistor has a fixed bias voltage V

B

indirectly set by the current mirror M2-

M3. The reference current I

B

, or multiples thereof, is mirrored from a

reference stage to the amplifier stage. The same current will flow through

M2 and M3 since they have the same gate to source voltage provided they

are designed for equal driving capabilities. The amplifier large-signal and

small-signal models are also shown in the figure.

Fig. 3.15. The pseudo-NMOS amplifier and its circuit models.

M

2

M

3

M

1

v

IN

v

OUT

V

DD

V

B

V

DD

I

B

I

B

v

OUT

I

DSAT

I

B

g

mn

v

in

g

dp

largesignalmodel smallsignalmodel

g

dn

mn IN

OUT

dn dp

g v

v

g g

=

+

57

The designer determines the amplifier current level to provide the n-channel

MOSFET with a certain transconductance at a certain gate bias,

,

,

/ 2

DSAT N

B

mn

GS GSTN

i

I

g

v V

c

= =

c

(3.13)

where typically the gate bias V

GSTN

=V

IN

-V

TN

is in the 100-200 mV range. The

nMOS-transistor is sized to sink the given current I

B

at this given bias

voltage, i.e.

( )

2

.

2

B IN TN

k

I V V = (3.14)

The amplifier transfer curve is shown in Fig. 3.16. Its region of linear

operation is determined by the saturation condition for the two MOSFETs

nMOS

.

pMOS

IN TN OUT

DD B TP DD OUT OUT B TP

V V V

V V V V V V V V

s

+ s s

(3.15)

Hence, the region of operation is given by

,

IN TN OUT B TP

V V V V V s s (3.16)

as shown in Fig. 3.16. The smaller the gate voltage overdrive, the larger the

region of linear amplifier operation. In essence, the gate voltage overdrives

chosen determines how close to the rails the amplifier will work.

Fig. 3.16. The amplifier and its linear region of operation.

S

U

B

T

H

R

E

S

H

O

L

D

R

E

G

I

O

N

58

For this amplifier circuit, the small-signal model must be more detailed than

before in that the MOSFET output conductance must be carefully

considered. From the small-signal model of the amplifier circuit, the

following small signal amplification can be derived

.

OUT mn

v

IN dn dp

v g

A

v g g

c

= =

c +

(3.17)

Example3.2. Calculate the circuit voltage amplification at a current level of

200 A if the MOSFETs are biased with gate voltage overdrives of 200 mV.

The Early voltages of the devices are assumed to be 5 V.

Solution: The transconductance is given by

200 [A]

2 mA/V.

/ 2 100 [mV]

B

mn

GSTN

I

g

V

= = =

The output conductance is approximately given by

200 [A]

40 A/V.

5 [V]

B

d

A

I

g

V

~ = =

The voltage amplification is then

2

25.

0.04 0.04

mn

v

dn dp

g

A

g g

= = =

+ +

It is interesting to note that, in the case of equal Early voltages, the voltage

amplification can be written

5

25.

0, 2

A

v

GST

V

A

V

= = =

Example 3.3. Is it reasonable to neglect velocity saturation for a MOSFET

biased at V

GST

=100 mV if the velocity saturation voltage is V

C

=2 V?

Solution: With V

C

=2 the drain current saturation voltage is given by

0.2

0.095 V.

2.1

GST C

DSAT

GST C

V V

V

V V

= = =

+

The error is only 5%, resulting in a 5% error in the calculation of the

saturation current. However, for V

GST

=200 mV and V

C

=1 V, the error is 20%.

For calculating the maximum saturation current available at say V

GST

=0.9 V,

great care must be taken to use the saturation voltages. For the two cases of

V

C

=1 V and V

C

=2 V, the correct saturation voltages are 0.47 V and 0.31 V.

59

Using V

DSAT

=0.9 V, instead of the correct values, for calculating the

saturation current would result in an overestimation of the saturation current

by a factor of two and three, respectively.

3.4.2 The CMOS inverter as an amplifier

The same type of analysis can be applied to calculate the small-signal

properties of the CMOS inverter. Its large-signal and small-signal equivalent

circuits are shown in Fig. 3.17.

The region of amplifier operation can be derived from large-signal

analysis using the saturation conditions

nMOS

.

pMOS

IN TN OUT

DD IN TP DD OUT OUT IN TP

V V V

V V V V V V V V

s

+ s s

(3.18)

Hence, the region of amplifier operation is given by

,

BIAS TN OUT BIAS TP

V V V V V s s (3.19)

where V

IN

=V

BIAS

is the input bias voltage. The bias point and the (green)

region of amplifier operation around the bias point are indicated in Fig. 3.18.

The Norton and Thevenin equivalent circuits resulting from the inverter

small-signal equivalent circuit in Fig. 3.17 is shown in Fig. 3.19. As

indicated by the figure, the CMOS inverter can be equivalently regarded as a

current source or a voltage source, both with an internal source resistance

determined by the sum of the output conductances.

Fig. 3.17. The CMOS-inverter, its large- and small-signal equivalent circuits

V

IN

V

OUT

V

DD

V

SS

V

OUT

V

DD

I

DSAT,N

I

DSAT,P

largesignalmodel

smallsignalmodel

v

out

g

mn

v

in

g

mp

v

in

g

dp

g

dp

60

Fig. 3.18. The CMOS-inverter and its voltage transfer characteristic.

Obviously, the voltage amplification of the CMOS inverter as an amplifier is

given by

.

mn mp

OUT

v

IN dn dp

g g

v

A

v g g

+

c

= =

c +

(3.20-)

Due to several reasons the CMOS inverter amplifier is not commonly used.

First, the input voltage range of the CMOS amplifier is often very narrow as

is apparent from the figure; secondly, it also receives poor marks on other

amplifier properties such as supply noise rejection [Rabaey et al., p 190].

Example 3.4: Compare the voltage amplification of the CMOS inverter to

that of the pseudo-NMOS amplifier in Example 3.2.

Solution: Provided g

mp

=g

mn

, the voltage amplification is given by

2 2

50.

0.04 0.04

mn mp

v

dn dp

g g

A

g g

+

+

= = =

+ +

Twice!

Fig. 3.19. Norton and Thevenin equivalent circuits of the CMOS amplifier.

v

out

+

g

dn

+g

dp

mn mp

in

dn dp

g g

v

g g

+

+

Thevenincircuit

v

out

(g

mn

+g

mp

)v

in

Nortoncircuit

g

dn

+g

dp

n

s

u

b

t

h

r

e

s

h

o

l

d

r

e

g

i

o

n

s

u

b

t

h

r

e

s

h

o

l

d

r

e

g

i

o

n

61

3.5 Summary

In this chapter we have investigated the functionality and the static

properties of the CMOS inverter. First, the digital properties of the inverter

were studied and its voltage transfer characteristic was derived and analyzed.

Three different inverter implementations were analyzed; with resistive load,

with pseudo nMOS load and with active pull-up pMOS load. The inverter

switching voltage and its noise margins were defined. Variations across the

wafer and between wafers due to process variations were mentioned.

Finally, the small-signal properties of the inverter as an analog amplifier

were discussed.

Potrebbero piacerti anche

- Dynamic Logic Circuits: A. MarzukiDocumento25 pagineDynamic Logic Circuits: A. Marzukisreekanthreddy peramNessuna valutazione finora

- Racefree Dynamic CMOS Technique For Pipelined Logic StructuresDocumento6 pagineRacefree Dynamic CMOS Technique For Pipelined Logic Structuressreekanthreddy peramNessuna valutazione finora

- Dynamic Logic CircuitsDocumento38 pagineDynamic Logic Circuitssreekanthreddy peramNessuna valutazione finora

- Digital Logic CircuitsDocumento20 pagineDigital Logic Circuitssreekanthreddy peramNessuna valutazione finora

- Std11 Bot EM 1Documento236 pagineStd11 Bot EM 1Irshad Ali100% (1)

- The InverterDocumento28 pagineThe Invertersreekanthreddy peramNessuna valutazione finora

- CMOS InverterDocumento16 pagineCMOS Invertersreekanthreddy peramNessuna valutazione finora

- Dynamic Logic Circuits: Kang and Leblebicic, Chapter 9Documento34 pagineDynamic Logic Circuits: Kang and Leblebicic, Chapter 9Lovey SalujaNessuna valutazione finora

- Advanced Topologiesand TechnologyDocumento34 pagineAdvanced Topologiesand TechnologylakshmiraniNessuna valutazione finora

- Electronics Ch14Documento22 pagineElectronics Ch14Denise NelsonNessuna valutazione finora

- Grazers and Browsers: How Digestive Morphology Affects Diet Selection Lisa A. ShipleyDocumento8 pagineGrazers and Browsers: How Digestive Morphology Affects Diet Selection Lisa A. Shipleysreekanthreddy peramNessuna valutazione finora

- Reproductive Morphology of Flowering PlantsDocumento12 pagineReproductive Morphology of Flowering Plantssreekanthreddy peramNessuna valutazione finora

- Dynamic Combinational Circuits: - Dynamic Circuits - Domino Logic - np-CMOS (Zipper CMOS)Documento29 pagineDynamic Combinational Circuits: - Dynamic Circuits - Domino Logic - np-CMOS (Zipper CMOS)vardhanNessuna valutazione finora

- Cmos InverterDocumento92 pagineCmos Invertersreekanthreddy peramNessuna valutazione finora

- CMOS Inverter: DC AnalysisDocumento32 pagineCMOS Inverter: DC Analysissreekanthreddy peram50% (2)

- Morphology of The Pteridophytes SporneDocumento200 pagineMorphology of The Pteridophytes Spornesreekanthreddy peram100% (1)

- 9 YeungDocumento19 pagine9 YeungNathan PittmanNessuna valutazione finora

- Upgraded Physics Syllabus for Std XI & XIIDocumento53 pagineUpgraded Physics Syllabus for Std XI & XIIPriyadarshini VaradkarNessuna valutazione finora

- 9 YeungDocumento19 pagine9 YeungNathan PittmanNessuna valutazione finora

- Dimensions UnitsDocumento5 pagineDimensions UnitsprithvijitNessuna valutazione finora

- Physical Quantities Handout.........Documento5 paginePhysical Quantities Handout.........sreekanthreddy peramNessuna valutazione finora

- Behaviour of OFDM System Using MATLAB SimulationDocumento5 pagineBehaviour of OFDM System Using MATLAB Simulationsreekanthreddy peramNessuna valutazione finora

- Introduction To Dimensional Analysis 2Documento3 pagineIntroduction To Dimensional Analysis 2sreekanthreddy peramNessuna valutazione finora

- BER Analysis & Comparison of Different Equalization Techniques For MIMO-OFDM SystemDocumento7 pagineBER Analysis & Comparison of Different Equalization Techniques For MIMO-OFDM Systemsreekanthreddy peramNessuna valutazione finora

- OFDM SIMULATION in MATLAB PDFDocumento59 pagineOFDM SIMULATION in MATLAB PDFaasmabaka100% (2)

- Dimensional Analysis A A SoninDocumento57 pagineDimensional Analysis A A SoninJeff WebbNessuna valutazione finora

- All About Fundamental Physical QuantitiesDocumento18 pagineAll About Fundamental Physical Quantitiessreekanthreddy peramNessuna valutazione finora

- FPGA Implementation of MIMO System Using Xilinx System Generator For Efficient Hardware/ Software Co-DesignDocumento9 pagineFPGA Implementation of MIMO System Using Xilinx System Generator For Efficient Hardware/ Software Co-Designsreekanthreddy peramNessuna valutazione finora

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5782)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (72)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- NTE1830 & NTE1831 Integrated Circuit Dual Audio Power Amplifier, 5.8W (19W BTL)Documento3 pagineNTE1830 & NTE1831 Integrated Circuit Dual Audio Power Amplifier, 5.8W (19W BTL)alex smuck kamusNessuna valutazione finora

- Amplifier Soft StartsDocumento7 pagineAmplifier Soft Startssarantapodarusa4009Nessuna valutazione finora

- Lecture 4-BJT Frequency Response-New!!Documento53 pagineLecture 4-BJT Frequency Response-New!!Muqthiar Ali100% (3)

- Obj 1997paper 2Documento15 pagineObj 1997paper 2Uday KakkarNessuna valutazione finora

- Tdoct5999a UsaDocumento100 pagineTdoct5999a UsambidNessuna valutazione finora

- DSP Lab ManualDocumento38 pagineDSP Lab ManualXP2009Nessuna valutazione finora

- Op Amp Design ThesisDocumento5 pagineOp Amp Design Thesismaryburgsiouxfalls100% (2)

- TCB-1100 Circuit Description GuideDocumento42 pagineTCB-1100 Circuit Description Guideyo8rzeNessuna valutazione finora

- MAX30034 Defibrillation/Surge/ESD Protector: General Description Benefits and FeaturesDocumento9 pagineMAX30034 Defibrillation/Surge/ESD Protector: General Description Benefits and Featuresmaria jose rodriguez lopezNessuna valutazione finora

- PDP Ph42hu31sDocumento38 paginePDP Ph42hu31sبوند بوندNessuna valutazione finora

- Physics Course ContentsDocumento84 paginePhysics Course ContentsAmbreen Khan100% (1)

- Audio VocaDocumento2 pagineAudio VocaheinzteinNessuna valutazione finora

- Contactless Liquid Level ControllerDocumento37 pagineContactless Liquid Level Controllerkitty100% (1)

- Ec 1Documento20 pagineEc 1helenseelanNessuna valutazione finora

- Low Power FM Transmitter Options from 25W to 250WDocumento2 pagineLow Power FM Transmitter Options from 25W to 250Wguestisor100% (1)

- Amplificador Fibra Optica KEYENCEDocumento30 pagineAmplificador Fibra Optica KEYENCEMaximo Jose Molina GutierrezNessuna valutazione finora

- Hewlett Packard 43100A Defibrillator - Service ManualDocumento113 pagineHewlett Packard 43100A Defibrillator - Service ManualcelltechgoyaNessuna valutazione finora

- Eshan Rao - 19ETEC004016 (EBD)Documento12 pagineEshan Rao - 19ETEC004016 (EBD)eshanraoNessuna valutazione finora

- Public Address & General Alarm System: Configuration & Installation ManualDocumento54 paginePublic Address & General Alarm System: Configuration & Installation Manualmuzammil shadabNessuna valutazione finora

- ST Micro User Manual - 3 Phase Inverter Based On STGIPN3H60Documento38 pagineST Micro User Manual - 3 Phase Inverter Based On STGIPN3H60smhbNessuna valutazione finora

- AP-M Series PDFDocumento5 pagineAP-M Series PDFVitorio LogoNessuna valutazione finora

- Fireswitch108 Managed Nac Power Extender: DescriptionDocumento2 pagineFireswitch108 Managed Nac Power Extender: DescriptionMd. Mominul IslamNessuna valutazione finora

- TU Physics Syllabus 2016Documento26 pagineTU Physics Syllabus 2016S.M. Ashikur RahmanNessuna valutazione finora

- Hcdslk1i DVD Receiver PDFDocumento88 pagineHcdslk1i DVD Receiver PDFfrgonzalezcNessuna valutazione finora

- Weighbridge Lightning Protection SystemsDocumento12 pagineWeighbridge Lightning Protection SystemssanjajsinghNessuna valutazione finora

- LIPO3 KM G 041221.de - en PDFDocumento4 pagineLIPO3 KM G 041221.de - en PDFLUis PEpeNessuna valutazione finora

- GE 300 MOOER ManualDocumento101 pagineGE 300 MOOER ManualThe Manila String MachineNessuna valutazione finora

- Jensen XDA91RB XDA92RB XDA94RB Octane Power Amplifier Installation Owners Manual ENDocumento18 pagineJensen XDA91RB XDA92RB XDA94RB Octane Power Amplifier Installation Owners Manual ENfred.fredNessuna valutazione finora

- Chapter 9: Electronic: 9.3 TransistorDocumento25 pagineChapter 9: Electronic: 9.3 TransistorSathya SeelanNessuna valutazione finora

- JBL Cinema ProPack 600 SUB135S Subwoofer Service ManualDocumento16 pagineJBL Cinema ProPack 600 SUB135S Subwoofer Service ManualJoko NelongsoNessuna valutazione finora