Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Aula 14a. 2013-06-24 - Introd-Sist-Digitais

Caricato da

Antoniel BordinCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Aula 14a. 2013-06-24 - Introd-Sist-Digitais

Caricato da

Antoniel BordinCopyright:

Formati disponibili

Introduo a Sistemas Digitais Aula 14 - 24/06/2013

Prof. Glauder Guimares Ghinozzi glauderguimaraes@gmail.com Baseado no material gentilmente cedido pelo Prof. Carlos Alberto

Flip-Flop, Registradores e Contadores

Lgica Digital

Lgica Combinacional: as sadas dependem somente das variveis de entrada;

Lgica Seqencial: as sadas dependem das variveis de entrada e/ou de seus estados anteriores;

Flip-Flop, Registradores e Contadores Flip-Flop RS Bsico

S Q

Q

B

Q

Q QNot

Q R

Flip-Flop, Registradores e Contadores Flip-Flop RS Bsico

S R Qa 0 0 0 0 0 1 0 1 0 0 1 1 S Q

Q

Qf Qf 0 1 0 0 1 1 1 1 1 0 1 1 0 0 1 1

seta Mantm anterior

reseta

1 0 0 1 0 1 1 1 0 1 1 1

No permitido

S R

Q

Qf Qa 0 1 No permitido

0 0 Q R 0 1 1 0 1 1

Flip-Flop, Registradores e Contadores

Flip-Flop RS comandado por PULSO de Clock

o circuito ir mudar de estado apenas quando o clock for igual a 1.

S R 0 0 S Q

Q

Qf Qa 0 1 No permitido

0 1 1 0 1 1

Clock Representao

S Q

Q

Ck

R

Q R

Flip-Flop, Registradores e Contadores

Flip-Flop JK

J K Qa Qa 0 0 0 0 0 1 0 1 1 0 1 0 0 1 0 1 0 1 0 1 1 0 1 0 1 0 1 0

S R 0 0 0 0 0 0 0 1 1 0 0 0 1 0 0 1

Qf Qa ( 0 ) Qa ( 1 ) Qa ( 0 ) 0 1 Qa ( 1 ) Qa ( 1 ) Qa ( 0 )

Para resolver o problema das entradas S = 1 e R = 1.

J

Q

S = J.Q

1 1 1 1

Clock

Q R = K.Q

Ck

FLIP-FLOP RS

J K

R

Qf Qa 0 1 Qa

0 0 0 1 1 0 1 1

Flip-Flop, Registradores e Contadores

Circuito do Flip-Flop JK

S Q

Q

J K 0 0 0 1 1 0 1 1

Qf Qa 0 1 Qa

Clock

Q R

Flip-Flop, Registradores e Contadores

Flip-Flop JK com entradas Preset e Clear (Reset)

Pr = 0 Q = 1 Preset (Pr) Pr = 1 Flip-Flop JK

O Flp-Flop JK poder assumir valores iniciais:

Q = 1 (Preset) ou Q = 0 (Clear).

Q

Q

Essas entradas so injetadas no circuito da seguinte maneira.

Clock

J K

Q

Qf Qa 0 1 Qa

0 0 Q 0 1 1 0

Clear (CL)

R

CL = 0 Q = 0 CL = 1 Flip-Flop JK

1 1

Flip-Flop, Registradores e Contadores

Flip-Flop tipo T

Pr T J Ck Q

T 0 1

K Q

Qf Qa Qa

CL

Flip-Flop, Registradores e Contadores

Flip-Flop tipo D

Pr D J Ck Q

D 0 1

K Q

Qf 0 1

CL

Flip-Flop, Registradores e Contadores

Flip-Flop Mestre-Escravo

Possui este nome devido aos dois blocos internos com os quais ele formado Estes dois blocos representam dois circuitos separados de latch. O latch mestre utilizado para aceitar a entrada do bit de dado A no flip-flop O valor de A armazenado no mestre e, ento, transferido para o escravo em um tempo posterior. Ambas as entradas so sincronizadas pelo sinal de clock

Mestre (Ativo)

Escravo

Mestre

Escravo (Ativo)

Q=A

Mestre ativo

Escravo ativo

Flip-Flop, Registradores e Contadores

Flip-Flop JK Mestre-Escravo

Para eliminar a oscilao do flip-flop JK, foram combinados dois flip-flops RS como no circuito a seguir, denominado flip-flop JK Master-Slave (Mestre-Escravo).

Flip-Flop, Registradores e Contadores

Flip-Flop JK Mestre-Escravo

Quando o clock for 0 o circuito de entrada est inativo, logo as entradas do escravo no sero alteradas e a sada do flip-flop JK MS no ser alterada. Quando o clock for 1 o mestre operar como um flip-flop JK normal, mas o escravo estar inativo e as sadas no sero alteradas. Quando o clock voltar para o nvel 0 o circuito mestre para de funcionar. O circuito escravo volta a funcionar (habilitado) e as sadas do mestre no instante que o clock volta a zero so transferidas para o escravo. Isto muito interessante porque no vai haver mais que uma mudana na sada do flip-flop JK mestre-escravo por ciclo de clock.

Flip-Flop, Registradores e Contadores

Flip-Flop JK Mestre-Escravo

Tabela da verdade:

J 0 0 1 1

K 0 1 0 1

Q QA 0 1 QA Note que este um circuito sensvel descida do clock. Para continuarmos um que seja sensvel subida do clock, basta colocarmos um inversor na entrada do clock.

Flip-Flop, Registradores e Contadores

C L P R 0 1 0 1 Q No permitido 0 1

Funcionamento normal

Flip-Flop JK Mestre-Escravo

0 0

Com entrada Preset e Clear

1 1

Flip-Flop, Registradores e Contadores

Flip-Flop JK Mestre-Escravo

Tabela da verdade:

CL 0 0 1 1

PR 0 1 0 1

Q No permitido 0 1 Funcionamento normal

Flip-Flop, Registradores e Contadores

Aplicaes dos Flip-Flops

Com a utilizao dos flip-flops, podemo construir circuitos:

divisores de freqncia; registradores de deslocamento unidirecionais e bidirecionais e contadores assncronos e sncronos.

Comercialmente temos os CIs:

TTL 7476 (dual JK FF /sensvel a borda de descida 1->0) CMOS 4027 (dual JK FF/sensvel a borda de subida 0->1)

Flip-Flop, Registradores e Contadores

Flip-Flop, Registradores e Contadores

Usos: Armazenamento de informao. Construo de mquinas de estado finito. Contadores. Diviso de frequncia

Flip-Flop, Registradores e Contadores

Flip-Flop, Registradores e Contadores

Registradores

Flip-Flop, Registradores e Contadores

Registrador de Deslocamento

Flip-Flop, Registradores e Contadores

Flip-Flop, Registradores e Contadores

CLK RIGHT/LEFT Serial data in

Q0 Q1 Q2 Q3

Flip-Flop, Registradores e Contadores

Registrador de Deslocamento utilizado como DIVISOR POR 2 (shift-right)

Se deslocarmos o registrador uma casa direita e entrarmos com zero na entrada de Q3.

0 Q3

I3 Q2

I2

I1

Q1 Q0

Entrada Srie Clock

ES Ck

Flip-Flop, Registradores e Contadores

Flip-Flop, Registradores e Contadores

Registrador de Deslocamento utilizado como MULTIPLICADOR POR 2 (shift-left)

Se deslocarmos o registrador uma casa esquerda e entrarmos com zero na entrada Q0.

I2 Q3

I1 Q2

I0

Q1 Q0

Entrada Srie Clock

ES Ck

Flip-Flop, Registradores e Contadores

Flip-Flop, Registradores e Contadores

Registrador de Deslocamento

Flip-Flop, Registradores e Contadores

Registrador de Deslocamento Para ilustrar o funcionamento em paralelo dos dados de entrada, preencha as formas de onda da figura seguinte:

Flip-Flop, Registradores e Contadores

Potrebbero piacerti anche

- A3 Matrix 06x05Documento2 pagineA3 Matrix 06x05Antoniel BordinNessuna valutazione finora

- Como criar um infográfico em 10 passosDocumento3 pagineComo criar um infográfico em 10 passosAntoniel BordinNessuna valutazione finora

- Live DVD Gerds LinuxDocumento30 pagineLive DVD Gerds LinuxAntoniel BordinNessuna valutazione finora

- Concurso UEMT Docente Plano AulaDocumento1 paginaConcurso UEMT Docente Plano AulaCharles Da Silva CarvalhoNessuna valutazione finora

- Planejamento de aula sobre objetivos pedagógicosDocumento5 paginePlanejamento de aula sobre objetivos pedagógicosRodrigo Rodrigues VazNessuna valutazione finora

- Web ServiceDocumento12 pagineWeb ServiceAntoniel BordinNessuna valutazione finora

- 12 dicas para gravar vídeos com smartphonesDocumento12 pagine12 dicas para gravar vídeos com smartphonesAntoniel BordinNessuna valutazione finora

- Mini Curso PythonDocumento51 pagineMini Curso PythonAntoniel BordinNessuna valutazione finora

- Fluxogramas: representação gráfica de processosDocumento32 pagineFluxogramas: representação gráfica de processosEdvan LópezNessuna valutazione finora

- Como Criar ArtigoDocumento27 pagineComo Criar ArtigoFabio Mendes100% (2)

- Listadeexercicios Algoritmosresolvida 131215224348 Phpapp02 PDFDocumento12 pagineListadeexercicios Algoritmosresolvida 131215224348 Phpapp02 PDFDouglas RezendeNessuna valutazione finora

- Apostila AudacityDocumento6 pagineApostila AudacityVitório TeixeiraNessuna valutazione finora

- Como Estruturar Um Post de BlogDocumento3 pagineComo Estruturar Um Post de BlogsancrisxaNessuna valutazione finora

- Ideias InteresantesDocumento1 paginaIdeias InteresantesAntoniel BordinNessuna valutazione finora

- A21v15n1 PDFDocumento2 pagineA21v15n1 PDFAntoniel BordinNessuna valutazione finora

- Aula 05 - Qos VoipDocumento57 pagineAula 05 - Qos VoipAntoniel BordinNessuna valutazione finora

- Algoritmo PDFDocumento22 pagineAlgoritmo PDFAntoniel BordinNessuna valutazione finora

- UML Diagramas Projeto WebDocumento37 pagineUML Diagramas Projeto WebAntoniel BordinNessuna valutazione finora

- 10 truques matemáticosDocumento4 pagine10 truques matemáticosLuiz Felipe Muniz NascimentoNessuna valutazione finora

- Mega Listão Atualizado de Cursos GratuitosDocumento6 pagineMega Listão Atualizado de Cursos GratuitosAntoniel BordinNessuna valutazione finora

- Apostila-C - Básico2Documento42 pagineApostila-C - Básico2639818dnlmdkNessuna valutazione finora

- 64 Fontes de TrafegoDocumento1 pagina64 Fontes de Trafegoannie3581Nessuna valutazione finora

- Exercícios Linguagem CDocumento3 pagineExercícios Linguagem CAntoniel BordinNessuna valutazione finora

- html504 141130003814 Conversion Gate02Documento19 paginehtml504 141130003814 Conversion Gate02Antoniel BordinNessuna valutazione finora

- Java Aplicações GUIDocumento25 pagineJava Aplicações GUIAntoniel BordinNessuna valutazione finora

- Coletânia de Exercícios Resolvidos em Linguagem CDocumento66 pagineColetânia de Exercícios Resolvidos em Linguagem CRuben Soares50% (4)

- Criando e Consumindo Web Service Rest Com PHP e JsonDocumento24 pagineCriando e Consumindo Web Service Rest Com PHP e JsonWesley CarvalhoNessuna valutazione finora

- HashingDocumento46 pagineHashingAntoniel BordinNessuna valutazione finora

- Tutorial AssemblyDocumento66 pagineTutorial AssemblyÍris Andrade Dos SantosNessuna valutazione finora

- Modelagem E-R Exercícios VerificaçãoDocumento14 pagineModelagem E-R Exercícios VerificaçãoOrlando CawendeNessuna valutazione finora

- Por que estudar MicrocontroladoresDocumento42 paginePor que estudar MicrocontroladoresAugusto RodriguesNessuna valutazione finora

- Configurando o Udpcast para clonar HDs e partições via redeDocumento2 pagineConfigurando o Udpcast para clonar HDs e partições via redeEduardo CodtecNessuna valutazione finora

- Informatica IIDocumento204 pagineInformatica IIRodrigo Mello MelloNessuna valutazione finora

- Uma breve história da informática desde os primórdios até as máquinas de calcular mecânicasDocumento12 pagineUma breve história da informática desde os primórdios até as máquinas de calcular mecânicasMike LealNessuna valutazione finora

- Ebook - Fundamentos de TI - Hardware e SoftwareDocumento65 pagineEbook - Fundamentos de TI - Hardware e SoftwareLucas Ferreira Silva100% (1)

- Tutorial PortfólioDocumento3 pagineTutorial PortfólioRafael AlbuquerqueNessuna valutazione finora

- Instalação Redes TécnicoDocumento3 pagineInstalação Redes TécnicoJosé MacedoNessuna valutazione finora

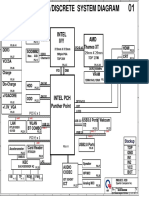

- Intel UMA/Discrete System DiagramDocumento43 pagineIntel UMA/Discrete System Diagramganyuan100% (1)

- Exercicios Hardware ComentadoDocumento18 pagineExercicios Hardware ComentadocapitulocontabilNessuna valutazione finora

- Manual SIAPE extrator dadosDocumento25 pagineManual SIAPE extrator dadoslfportoNessuna valutazione finora

- Manual de operação para medidor de stress térmico HiSeg TGD-1800Documento18 pagineManual de operação para medidor de stress térmico HiSeg TGD-1800Silvia Cristina Ribeiro do NascimentoNessuna valutazione finora

- Adicionando multi-tasking ao Arduino com FreeRTOSDocumento4 pagineAdicionando multi-tasking ao Arduino com FreeRTOSel cabonNessuna valutazione finora

- Usando o DBiDocumento3 pagineUsando o DBigustavonicolaumpNessuna valutazione finora

- Arquitetura computadoresDocumento5 pagineArquitetura computadoresEdlaine BatistaNessuna valutazione finora

- Devicenet e Controlnet ResumoDocumento21 pagineDevicenet e Controlnet ResumoRubensMoraisNessuna valutazione finora

- Manual Digistar XE-16BDocumento46 pagineManual Digistar XE-16BbrenotavaresNessuna valutazione finora

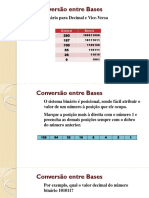

- Conversão entre Bases Binárias e DecimaisDocumento26 pagineConversão entre Bases Binárias e DecimaisFree FireNessuna valutazione finora

- Manual 3080br EspecificacoesDocumento2 pagineManual 3080br Especificacoeschristianoscooty1650Nessuna valutazione finora

- Minicurso Aquisio de Dados e Controle 2Documento14 pagineMinicurso Aquisio de Dados e Controle 2Jaime_LinharesNessuna valutazione finora

- Conhecendo o Programa Braille FácilDocumento27 pagineConhecendo o Programa Braille FácilEliane MacielNessuna valutazione finora

- MB Pegatron IPMH61R1Documento1 paginaMB Pegatron IPMH61R1Adriano Yonezawa50% (2)

- Cria Asteroides 2D no UnityDocumento15 pagineCria Asteroides 2D no UnityCícero FernandesNessuna valutazione finora

- Teste - Atividade Objetiva 3Documento4 pagineTeste - Atividade Objetiva 3valdenor britoNessuna valutazione finora

- x990 Verifone - Data Sheet - PTDocumento1 paginax990 Verifone - Data Sheet - PTPaulo LewisNessuna valutazione finora

- Memórias Compatíveis Com A Placa Mãe Gigabyte P5Q-E - QVLDocumento6 pagineMemórias Compatíveis Com A Placa Mãe Gigabyte P5Q-E - QVLaraujoalcaNessuna valutazione finora

- Uma abordagem sobre a evolução das linguagens de programaçãoDocumento5 pagineUma abordagem sobre a evolução das linguagens de programaçãoAdeylson LuizNessuna valutazione finora

- Apostila Debian AvançadoDocumento124 pagineApostila Debian AvançadomangelbNessuna valutazione finora

- Evolução Processadores Intel Parte 2 de 2Documento3 pagineEvolução Processadores Intel Parte 2 de 2Paulo ViegasNessuna valutazione finora

- Ciclo de Vida ThreadDocumento4 pagineCiclo de Vida ThreadBruno FigueredoNessuna valutazione finora

- 2023-04-26 Simulado 30 Questões Revisão (Questões)Documento32 pagine2023-04-26 Simulado 30 Questões Revisão (Questões)Valmir AlvarengaNessuna valutazione finora