Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Ilicore: 4-Ch Drive +power Controller For Portable CD D5901

Caricato da

vetchboyDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Ilicore: 4-Ch Drive +power Controller For Portable CD D5901

Caricato da

vetchboyCopyright:

Formati disponibili

Silicore

4-CH DRIVE +POWER CONTROLLER FOR PORTABLE CD

D5901

FEATURE Out line Drawing

z Four channel of H-bridge drivers are 14.0±0.3

10.0±0.3

contained.

33 23

z DC/DC converter control circuit is contained.

z Reset circuit. 34 22

z Reduced voltage detection circuit.

CHMC SXXX

14.0±0.3

z Battery charging circuit.

10.0±0.3

D5901

z General purpose operational a mplifier is

contained. 44 12

z Low power consumption.

1.2

1 11 0.2±0.1

z Thermal shutdown circuit.

2.15±0.1

z QFP44 package.

0.05

<H-bridge driver> 0.8 0.15

0.35±0.1

z Load drive voltage can be processed by PWM control th rough an external co mponent.

z Excellent gain can be obtained by a voltage feedback circuit.

z Mute function is disabled for ch1, ch2 and ch3/ch4 respectively.

<DC/DC converter control circuit>

z Starter and power off function.

z Soft-start function and short-circuit protection function.

z Self-advancing oscillation and clock synchronization are available.

<Reset circuit>

z Reset voltag e is in terlocked with the set voltage of DC/DC converter.

z Inversion output termi nal for reset output is available.

<Reduced voltage detection circuit>

z Battery charger and dry battery allow to switch “E mp ty” detection level.

<Battery charging circuit>

z Constant cu rrent battery charging system allows to vary current value throug h

resistance.

z It is separated from any other blocks and it can be operated independently.

z A charging power transistor is co ntained.

z Independent thermal shutdown circuit is contained.

SHAOXING SILICORE TECHNOLOGY CO.,LTD 1/16

www. Silicore. com. cn

CHMC

Silicore D5901

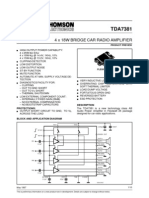

BLOCK DIAGRAM AND PIN CONNECTION

OUT1R OUT2R POWGND OUT3R

RCHG OUT1F OUT2F OUT3F OUT4F OUT4R BRAKE1

33 32 31 30 29 28 27 26 25 24 23

BRAKE 1

AMUTE 34 22 IN1

MUTE 1

EMP 35 21 MUTE2

HVc c 36 20 IN2

BTL BTL BTL BTL

MUTE 34

PSW 37 TSD - 19 MUTE34

Maximum +

De tec tion

CLK

CLK 38 - 18 IN4

+

START 39 -

+ - +

17 IN3

Powe r off

sta rter

-

OFF 40 + 16 VREF

Tria ngula r

wa ve

CHGVc c 41 TSD

Pre -drive power supply

15 VSYS2

Over voltage

SEL 42 14 OP+

+

-

+-

+

Control circuit

-

P ower supply

+

PREGND 43 13 OPOUT

B attery power supply

-

+- +

PWMFIL 44 12 VSYS1

+-

1 2 3 4 5 6 7 8 9 10 11

BSEN BATT RESET DEAD SW EO EI SPRT CT NC OP-

SHAOXING SILICORE TECHNOLOGY CO.,LTD 2/16

www. Silicore. com. cn

CHMC

Silicore D5901

TERMINAL DESCRIPTION

Pin NO. Pin Name Function Equivalent circuit diagram

BATT

16.5K

71K

Battery voltage

1 BSEN

monitor terminal 10K 19K

11.5K

Battery power supply

2 BATT Power unit power supply terminal

input termi n al

VSYS1 VSYS2

90K

Cassette detection

3 RESET

output terminal 3

VSYS1

18K

Dead-ti me setting

4 DEAD

terminal 4

65K

50K

BATT

BATT

Booster transistor

5 SW

drive termi n al 5

250

9K

SHAOXING SILICORE TECHNOLOGY CO.,LTD 3/16

www. Silicore. com. cn

CHMC

Silicore D5901

TERMINAL DESCRIPTION Continue

Pin NO. Pin Name Function Equivalent circuit diagram

VSYS1

VSYS1

Error a mp lifier output

6 EO

terminal 6

VSYS1

VSYS1

35K

Error a mp lifier input

7 EI 7

terminal

21K

VSYS1

VSYS1

Short-circuit protection

8 SPRT

setting terminal 8

220K

VSYS1 BATT

2K

Triangular wave output 9

9 CT

terminal

420K

20K

10 NC

VSYS1 VSYS1

Operational amplifi er

11 OP-

negative input terminal

14 11

Operational amplifi er

14 OP+ positive input terminal

SHAOXING SILICORE TECHNOLOGY CO.,LTD 4/16

www. Silicore. com. cn

CHMC

Silicore D5901

TERMINAL DESCRIPTION Continue

Pin NO. Pin Name Function Equivalent circuit diagram

Control circuit power

12 VSYS1 Control circuit power supply terminal

supply input terminal

VSYS1

VSYS1

Operational amplifi er

13 OP O U T

output terminal 13

Pre-driver power supply

15 VSYS2 Pre-driver power supply terminal

input termi n al

VSYS2

16

×4

15K

Reference power supply

30K

16 VREF

input termi n al

75K

CH3 control signal

17 IN3 VSYS2

input termi n al

CH4 control signal

18 IN4

input termi n al

11K

CH2 control signal 17

20 IN2

input termi n al

18

CH1 control signal 20

22 IN1 20PIN=7.5K

input termi n al

22

19 MUTE34 CH3/CH4 mute terminal VSYS2

21 MUTE2 CH2 mute terminal

75K

19

23 BRAKE1 CH1 brake terminal 21

75K

23

SHAOXING SILICORE TECHNOLOGY CO.,LTD 5/16

www. Silicore. com. cn

CHMC

Silicore D5901

TERMINAL DESCRIPTION Continue

Pin NO. Pin Name Function Equivalent circuit diagram

24 OUT4R CH4 negative ou tput 36

25 OUT4F CH4 positive ou tput

26 OUT3R CH3 negative ou tput

27 OUT3F CH3 positive ou tput

Power unit power

28 POWGND

supply ground 24 25

29 OUT2F CH2 positive ou tput 26 27

29

30 OUT2R CH2 negative ou tput 30

32 31

31 OUT1F CH1 positive ou tput

32 OUT1R CH1 negative ou tput

H-bridge po wer supp ly

36 HVcc

input termi n al 28

CHGVc c

Charging cu rrent setting 950

33 RCHG 33

terminal

BATT

BATT

Reset inversion output

34 AMUTE 34

terminal

95K

35

“E mp ty” detection

35 EMP

output terminal

BATT BATT

37

PWM transistor drive

37 PSW

terminal

54

SHAOXING SILICORE TECHNOLOGY CO.,LTD 6/16

www. Silicore. com. cn

CHMC

Silicore D5901

TERMINAL DESCRIPTION Continue

Pin NO. Pin Name Function Equivalent circuit diagram

VSYS1

VSYS1

2K

38

External clock

38 CLK synchronization input

terminal

51K

100K

BATT

BATT

390K

Boost DC/DC converter 200K

39 START

starting terminal 39

VSYS1

VSYS1

180K

Boost DC/DC converter

40 OFF

OFF terminal 40

30K

Charging circuit po wer

41 CHGVcc Charging circuit po wer supply terminal

supply input terminal

BATT

220K

“E mpty” detection level

42 SEL

switching terminal 68K

42

30K

Pre-unit power su pply

43 PREGND Pre-unit power supply ground terminal

ground terminal

VSYS1

2K

VSYS1

PWM phase

44 PWMFIL 44

co mpensation terminal

2K

SHAOXING SILICORE TECHNOLOGY CO.,LTD 7/16

www. Silicore. com. cn

CHMC

Silicore D5901

ABSOLUTE MAXIMUM RATINGS (Ta=25 °C)

Characteristic Symbol Value Unit

Supply Voltage Vcc 13.5 V

Drive output cu rrent Io 500 mA

Power dissipation Pd 625* mW

Operating te mperature range Topr -30~85 °C

Storage Temperature range Tstg -55~150 °C

* Reduced by 5 mW/°C for operation above Ta=25°C

RECOMMENDED OPERATING CONDITION

Parameter Symbol Min. Typ. Max. Unit

Control circuit power supply voltage VSYS1 2.7 3.2 5.5 V

Pre-driver power supply voltage VSYS2 2.7 3.2 5.5 V

H-bridge power supply voltage HVcc PWM BATT V

Power unit power supply voltage BATT 1.5 2.4 8.0 V

Charging circuit power supply voltage CHGVcc 3 .0 4.5 8.0 V

Ambient temperature Ta -10 25 70 °C

SHAOXING SILICORE TECHNOLOGY CO.,LTD 8/16

www. Silicore. com. cn

CHMC

Silicore D5901

ELECTRIC CHARACTERISTICS

(Unless specified particularly: Ta=2 5°C, BATT=2.4V V S Y S 1 =V S Y S 2 =3.2 V, V R E F =1.6V,

CHGVcc=0V, f C L K =88.2kHz)

Characteristics Symbol Test conditions Min Typ Max Unit

Co mmon section

B AT T s t a n d - b y c u r r e n t IST B AT T = 9 V V S Y S 1 = V S Y S 2 = V R E F = 0 V 0 3 µA

B AT T s u p p l y c u r r e n t at

I B AT H V c c = 0 . 4 5 V, M U T E 3 4 = 3 . 2 V 2.5 4.0 mA

no-load

VSYS1 supply current at H V c c = 0 . 4 5 V, M U T E 3 4 = 3 . 2 V,

ISYS1 3.3 4.5 mA

no-load EI=0V

VSYS2 supply current at

ISYS2 H V c c = 0 . 4 5 V, M U T E 3 4 = 3 . 2 V 4.1 5.5 mA

no-load

CHGVcc supply

ICHGVcc C H G V c c = 4 . 5 V, R O U T = O P E N 0.65 2.0 mA

current at no-load

H-bridge driver section

CH1,3,4 Gvc1,3,4 12 14 16

Vo l t a g e g a i n dB

CH2 Gvc2 21.5 23.5 24.5

Gain error by polarity ∆Gvc -2 0 2 dB

IN pin input CH1,3,4 RIN1,3,4 9 11 13

IN=1.7 and 1.8V kΩ

resistance CH2 RIN2 6 7.5 9

RL=8Ω, IN=0~3.2V

Maximum output voltage VOUT 1.9 2.1 V

H V c c = B AT T = 4 V,

Lower transistor

V S AT L Io=-300mA, IN=0 and 3.2V 240 400 mV

saturated voltage

Upper transistor

V S AT U Io=300mA, IN=0 and 3.2V 240 400 mV

saturated voltage

I n p u t o ff s e t v o l t a g e VOI -8 0 8 mV

Output o ff s e t CH1,3,4 VOO1,3,4 -50 0 50

VREF=IN=1.6V mV

voltage CH2 VOO2 -130 0 130

Dead zone VDS -10 0 10 mV

BRAKE1 ON threshold

VBRON IN1=1.8V 2.0 V

voltage

BRAKE1 OFF threshold

VBROFF IN1=1.8V 0.8 V

voltage

MUTE2 ON threshold

VM2ON IN2=1.8V 2.0 V

voltage

MUTE2 OFF threshold

VM2OFF IN2=1.8V 0.8 V

voltage

MUTE34 ON threshold

VM34ON IN3= IN4=1.8V 2.0 V

voltage

MUTE34 OFF threshold

VM34OFF IN3= IN4=1.8V 0.8 V

voltage

VREF ON threshold voltage VREFON IN1= IN2=IN3= IN4=1.8V 1.2 V

VREF OFF threshold voltage VREFOFF IN1= IN2=IN3= IN4=1.8V 0.8 V

BRAKE1 pin the current

BRAKE1 brake current IBRAKE 4 7 10 mA

d i ff e r e n c e b e t w e e n ‘ H ’ a n d ‘ L’

SHAOXING SILICORE TECHNOLOGY CO.,LTD 9/16

www. Silicore. com. cn

CHMC

Silicore D5901

ELECTRICAL CHARACTERISTICS

(Unless specified particularly: Ta=2 5°C, BATT=2.4V V S Y S 1 =V S Y S 2 =3.2 V, V R E F =1.6V,

CHGVcc=0V, f C L K =88.2kHz)

Characteristics Symbol Test conditions Min Typ Max Unit

PWM power supply driv ing section

PSW sink current IPSW IN1=2.1V 10 13 17 mA

HVcc level shift voltage VSHLF I N 1 = 1 . 8 V, H V c c - O U T 1 F 0.35 0.45 0.55 V

H V c c = 9 V,

HVcc leak current IHLK 0 5 µA

V S Y S 1 = V S Y S 2 = B AT T = 0 V

PWM amplifier transfer gain GPWM I N 1 = 1 . 8 V, H V c c = 1 . 2 V ~ 1 . 4 V 1/60 1/50 1/40 1/kΩ

DC/DC converter section

(Error a mpl ifier section)

VSYS1 pin threshold voltage VSITH 3.05 3.2 3.35 V

EO pin output voltage H VEOH E I = 0 . 7 V, I o = - 1 0 0 µ A 1.4 1.6 V

EO pin output voltage L VEOL E I = 1 . 3 V, I o = 1 0 0 µ A 0.3 V

(Short-circuit protection)

S P RT p i n v o l t a g e ( n o r m a l ) VSPR EI=1.3V 0 0.1 V

S P RT p i n c u r r e n t 1 E O = H ISPR1 EI=0.7V 6 10 16 µA

S P RT p i n c u r r e n t 2 O F F = L ISPR2 E I = 1 . 3 V, O F F = 0 V 12 20 32 µA

S P RT p i n c u r r e n t 3 ( o v e r- v o l t a g e ) ISPR3 E I = 1 . 3 V, B AT T = 9 . 5 V 12 20 32 µA

S P RT p i n i m p e d a n c e RSPR 175 220 265 kΩ

S P RT p i n t h r e s h o l d v o l t a g e VSPTH E I = 0 . 7 V, C T = 0 V 1.1 1.2 1.3 V

O v e r- v o l t a g e p r o t e c t i o n d e t e c t VHVPR BSEN pin voltage 8.0 8.4 9.0 V

(Transistor driving section)

B AT T = C T = 1 . 5 V, I o = - 2 m A , a t

SW pin output voltage 1H VSW1H 0.78 0.98 1.13 V

s t a r t e r, V S Y S 1 = V S Y S 2 = 0 V

C T = 0 V, I o = - 1 0 m A , E I = 0 . 7 V,

SW pin output voltage 2H VSW2H 1.0 1.5 V

S P RT = 0 V

SW pin output voltage 2L VSW2L C T = 2 V, I o = 1 0 m A 0.3 0.45 V

C T = 4 7 0 p F, V S Y S 1 = V S Y S 2 = 0 V,

SW pin oscillating frequency 1 fSW1 65 80 95 kHz

at starter

SW pin oscillating frequency 2 fSW2 C T = 4 7 0 p F, C L K = 0 V 60 70 82 kHz

SW pin oscillating frequency 3 fSW3 CT=470pF 88.2 kHz

C T = 4 7 0 p F,

SW pin minimum pulse width TSWMIN 0.01 0.6 usec

EO=0.5→0.7Vsweep

Pulse duty at start DSW1 C T = 4 7 0 p F, V S Y S 1 = V S Y S 2 = 0 V 40 50 60 %

E I = 0 . 7 V, C T = 4 7 0 p F,

Max. pulse duty at self-running DSW2 70 80 90 %

CLK=0V

Max. pulse duty at CLK

DSW3 E I = 0 . 7 V, C T = 4 7 0 p F 65 75 85 %

synchronization

SHAOXING SILICORE TECHNOLOGY CO.,LTD 10/16

www. Silicore. com. cn

CHMC

Silicore D5901

ELECTRICAL CHARACTERISTICS

(Unless specified particularly: Ta=2 5°C, BATT=2.4V V S Y S 1 =V S Y S 2 =3.2 V, V R E F =1.6V,

CHGVcc=0V, f C L K =88.2kHz)

Characteristics Symbol Test conditions Min Typ Max Unit

(Dead time section)

DEAD pin impedance RDEAD 52 65 78 kΩ

DEAD pin output voltage VDEAD 0.78 0.88 0.98 V

(Interface section)

VSYS1

OFF pin threshold voltage VOFFH EI=1.3V V

-2.0

OFF pin bias current IOFF OFF=0V 75 95 11 5 µA

S TA RT pin ON threshold B AT T

voltage V S TA R T 1 V S Y S 1 = V S Y S 2 = 0 V, C T = 2 V -1.0 V

S TA RT p i n O F F B AT T

V S TA R T 2 V S Y S 1 = V S Y S 2 = 0 V, C T = 2 V -0.3 V

threshold voltage

S TA RT p i n b i a s c u r r e n t I S TA R T S TA RT = 0 V 13 16 19 µA

CLK pin threshold

VCLKTHH 2.0 V

Vo l t a g e H

CLK pin threshold

VCLKTHL 0.8 V

Vo l t a g e L

CLK pin bias current ICLK CLK=3.2V 10 µA

(Starter circuit section)

V S Y S 1 = V S Y S 2 = 0 V → 3 . 2 V,

St a r t e r s w i t c h i n g v o l t a g e VSTNH 2.3 2.5 2.7 V

S TA RT = 0 V

St a r t e r switching hysteresis

VSNHS S TA RT = 0 V 130 200 300 mV

width

D i s c h a rg e r e l e a s e v o l t a g e VDIS 1.63 1.83 2.03 V

Empty detection section

Empty detection voltage 1 VEMPT1 VSEL=0V 2.1 2.2 2.3 V

Empty detection voltage 2 VEMPT2 ISEL=-2µA 1.7 1.8 1.9 V

Empty detection

VEMNS1 VSEL=0V 25 50 100 mV

Hysteresis width 1

Empty detection

VEMNS2 ISEL=-2µA 25 50 100 mV

Hysteresis width 2

EMP pin output voltage VEMP Io=1mA, BSEN=1V 0.5 V

EMPpin output leak current IEMPL BSEN=2.4V 1.0 µA

BSEN pin input resistance RBSEN VSEL=0V 17 23 27

BSEN pin input leak

IBSENL V S Y S 1 = V S Y S 2 = 0 V, B S E N = 4 . 5 V 1.0 µA

current

SEL pin detection voltage V S E LT H V S E LT N = B AT T- S E L , B S E N = 2 V 1.5 V

SEL pin detection current I S E LT -2 µA

SHAOXING SILICORE TECHNOLOGY CO.,LTD 11/16

www. Silicore. com. cn

CHMC

Silicore D5901

ELECTRICAL CHARACTERISTICS

(Unless specified particularly: Ta=2 5°C, BATT=2.4V V S Y S 1 =V S Y S 2 =3.2 V, V R E F =1.6V,

CHGVcc=0V, f C L K =88.2kHz)

Characteristics Symbol Test conditions Min Typ Max Unit

Reset circuit section

VSYS1 reset threshold Ratio of VSYS1 voltage and

H S RT 85 90 95 %

voltage ratio e r r o r- a m p t h r e s h o l d v o l t a g e

Reset detection

VRSTHS 25 50 100 mV

hysteresis width

RESET pin output voltage VRST Io=1mA, VSYS1=VSYS2=2.8V 0.5 V

RESET pin pull up resistance RRST 72 90 108 kΩ

B AT T

AMUTE pin output voltage 1 VAMT1 Io=-1mA, VSYS1=VSYS2=2.8V -0.4

B AT T V

I o = - 1 m A , V S Y S 1 = V S Y S 2 = 0 V, B AT T

AMUTE pin output voltage2 VAMT2 -0.4

B AT T V

S TA RT = 0 V

AMUTE pin pull down

RAMT 77 95 11 3 kΩ

resistance

Operational a mplifier section

Input bias current IBIAS 300 nA

I n p u t o ff s e t v o l t a g e VOIOP -5.5 0 5.5 mV

High level output voltage VOHOP RL=OPEN 3.0 V

Low level output voltage VOLOP RL=OPEN 0.2 V

Output drive current (source) ISOU Output short to GND by 50Ω -3 -1 mA

Output drive current (sink) ISIN Output short to VSYS by 50Ω 0.4 0.7 mA

Open loop voltage gain Gvo V I N = - 7 5 d B V, f = 1 k H z 70 dB

Slew rate SR 0.5 V/usec

Charging circuit section

RCHG pin bias voltage VRCHG C H G V c c = 4 . 5 V, R C H G = 1 . 8 k Ω 0.71 0.81 0.91 V

RCHG pin output C H G V c c = 4 . 5 V,

RRCHG 0.75 0.95 1.2 kΩ

resistance RCHG=0.5 and 0.6V

SEL pin leak current 1 ISELLK1 C H G V c c = 4 . 5 V, R C H G = O P E N 1.0 µA

SEL pin leak current 2 ISELLK2 C H G V c c = 0 . 6 V, R C H G = 1 . 8 k Ω 1.0 µA

C H G V c c = 4 . 5 V, RCHG=0Ω,

SEL pin saturated voltage VSELCO 0.45 1.0 V

Io=300mA

SHAOXING SILICORE TECHNOLOGY CO.,LTD 12/16

www. Silicore. com. cn

CHMC

Silicore D5901

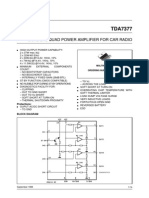

APPLICATION CIRCUIT

Tra ve rse Spindle Foc us Tric king

1.0K

M M

33 32 31 30 29 28 27 26 25 24 23

BRAKE 1

34 22

MUTE 1

35 21

33µ

36 20

0.1uF

BTL BTL BTL BTL

47uF

MUTE 34

37 TSD - 19

47 Maximum +

De tec tion

CLK

38 - 18

+

39 -

+ - +

17

Powe r off

0.1uF

sta rter

100K -

40 + 16

Tria ngula r

wa ve

41 TSD

Pre -drive power supply

15

Over voltage

42 14

+

-

+-

+ - Control circuit

P ower supply +

43 13

B attery power supply

-

--+

44 12

+-

2200pF 100K

10pF

1 2 3 4 5 6 7 8 9 10 11

Filter

0.1uF

0.1uF

470pF

6.2K

0.022uF

DC/DC

Converte r

a pplica tion

47uF

100uF

SHAOXING SILICORE TECHNOLOGY CO.,LTD 13/16

www. Silicore. com. cn

CHMC

Silicore D5901

OPERATING EXPLANATION

z H-bridge driver

(Gain setting)

Driver input resistance is 11 kΩ(typ.) for CH1,CH3 and CH4 and 7.5 kΩ(typ.)for CH2.

Calculate driver gain with the under-mentioned expression and set it.

CH1, CH3,CH4 Gv=20log|55k/(11k +R)| (dB)

CH2 Gv=20log|110k/(7.5k +R)| (dB)

R: External resistance

The power supply of drive output stage is HVcc termin al (36 pin) and th at of pre-drive

circuit is VSYS2 terminal (15 pin). Attach by-pass capacitor (approximately 0.1µF) to the

legs of this IC between the po wer supplies.

(Mute function)

Brake function and mu te function are assigned to CH1 and other channels of the four

channels respectiv ely.

When BRAKE1 terminal (23 pin) has been set to “H”, the output of CH1 becomes “L”

for both pin 31 and pin 32 and enters a Brake mode.

When MUTE2 terminal (21 pin) has been set to “H” , the output of CH2 is mu ted.

When MUTE34 terminal (19 pin)has been set to “L” th e output of CH3 and that of CH4

are muted si mu ltaneously.

(V R E F drop mute)

When the voltage impressed to V R E F terminal (16 pin) is 1.0V(typ .) or less, impedance

of driver output becomes “h igh”.

(Thermal shutdown)

When th e ch ip temp era ture has been 150°C(typ.) the ou tput current is cut.

When th e chip tempe rature has dropped to 120°C(typ.) the ou tput current begins to

flow.

z PWM power supply driv e un it

This unit detects a ma ximu m output level of drivers of four chan nels and performs the

PWM supply of load drive po wer supply (36 pin). This unit uses PNP transistor , coil,

Schottky diode and capacito r as ex ternal component.

SHAOXING SILICORE TECHNOLOGY CO.,LTD 14/16

www. Silicore. com. cn

CHMC

Silicore D5901

33µ

10pF

0.1uF

47uF

100K 47

2200pF

44 37 36

z DC/DC converter

(Output voltage)

Booster circuit of 3.2V(typ.) can be config ured with external co mponents. This voltage

varies depending on addition of external components. How to set the voltage is as

follows:

V S Y S 1 =1.2×{[(R1*R3)/(R1+R3)+(R2*R4)/(R2+R4)]/(R2* R4/(R2 +R4)}

R1=External re sistan

R2=External re sistan

12 R3=35KΩ

R4=21KΩ

R1 R3

R2 R4

1.2V

(Short-circuit protection function)

When th e ou tput (6 pin) of error amplifier is “H”, if the voltage of SPRT terminal (8

pin) has reached 1.2V(typ .) upon charging th e terminal, switching of SW terminal (5

pin) is disabled . Time to disable switching depend s on a capacitor of th e SPRT

terminal (8 pin) and it can be calculated by th e under- mentioned expression:

t=C S P RT ×(V T H /I S P RT ) (sec) (V T H =1.2V, I S P RT =10µA )

(Soft-start function)

the soft-start is functioned by putting a capacitor between DEAD terminal (4 pin) and

GND. MAX duty can be changed by attaching resistance to 4-pin.

t=C D E A D ×R (sec) (R=65kΩ)

SHAOXING SILICORE TECHNOLOGY CO.,LTD 15/16

www. Silicore. com. cn

CHMC

Silicore D5901

(Power-off operation)

SPRT terminal (8 pin) is charged by setting OFF terminal (40 pin) to “L”. Then,

switching of SW termi n al (5 pin) is terminated when the voltage of the SPRT terminal

(8 pin) has reached 1.2V(typ.). Time to disable switching depends on a capacitor of the

SPRT terminal (8 pin) and it can be calcu lated by the und er-mentioned expression:

t=C S P RT ×( V T H /I O F F ) (sec) (V T H =1.2V, I O F F =20µA)

(Over-voltage protection op eration)

When the voltage impressed to BSEN terminal (1 pin) has been 8.4V(typ .), SPRT

terminal (8 pin)is charged. Then, switching of SW termi n al (5 pin)is terminated when

the voltage of the SPRT terminal (8 pin) has reached 1.2V(typ.) Ti me to disable

switching depend s on a capacitor of the SPRT terminal (8 pin) an d it can be calculated

by the under-mentioned expression:

t=C S P RT ×( V T H /I H V ) (s ec) (V T H =1.2V, I H V =20 µA )

z “E mpty” detector unit

When the voltage impressed to BSEN termina l (1 pin) has been the detecting voltage is

2.2V or less, EMP terminal (35 pin) varies fro m “H” to “L” (open collector output).

Hysteresis of 50mV (t yp.) set to the detecting voltage to preven t th e output ch attering.

The detecting vo ltage varies depending on SEL terminal (42 pin) as follows:

SEL pin Detect voltage Return voltage

“L” 2.2V(typ.) 2.25V(typ.)

High-Z 1.8V(typ .) 1.85V(typ .)

z Reset circuit

Upon 90% (typ .) of DC/DC converter output voltage, RESET terminal (3 pin) varies

fro m “L” to “H” and AMUTE terminal (34 pin) changes fro m “H” to “L”. Hyste resis of

50mV (typ.) set to th e reset voltage to prevent the output chattering.

z Charging circuit

The power supply of the charging unit is CHGVcc terminal (41 pin) and it is

independent of any other circuits. Charging cu rrent is set by resistan ce between RCHG

ter minal (33 pin) and GND. The charging cu rrent takes constant current through SEL

terminal (42 pin)

This circuit has a private thermal shutdown circuit. When the chip temp e rature has

been 150°C (typ .), the charging current is cu t. When the chip temperature has dropped

to 120

SHAOXING SILICORE TECHNOLOGY CO.,LTD 16/16

www. Silicore. com. cn

CHMC

Potrebbero piacerti anche

- Industrial radiography A Complete Guide - 2019 EditionDa EverandIndustrial radiography A Complete Guide - 2019 EditionNessuna valutazione finora

- MTC Er70s 2Documento1 paginaMTC Er70s 2Mirza BaigNessuna valutazione finora

- Soft Magnetic Iron Parts Fabricated by Powder Metallurgy (P/M) TechniquesDocumento4 pagineSoft Magnetic Iron Parts Fabricated by Powder Metallurgy (P/M) TechniquesEduardoNessuna valutazione finora

- Mi3530 B1820401Documento1 paginaMi3530 B1820401abinayaNessuna valutazione finora

- ST 35.8 (Germany / DIN) : Material PropertiesDocumento3 pagineST 35.8 (Germany / DIN) : Material Propertiesmohammad zareiNessuna valutazione finora

- ASTM A-802 - Falhas de FundiçãoDocumento3 pagineASTM A-802 - Falhas de FundiçãoCristian RodeghelNessuna valutazione finora

- Grade Point Average CalculatorDocumento1 paginaGrade Point Average CalculatorRaquelNessuna valutazione finora

- TM0172 2015 Determining CorrosiveDocumento16 pagineTM0172 2015 Determining Corrosiveahmed sobhyNessuna valutazione finora

- JIS G3452 PipeDocumento0 pagineJIS G3452 PipefaridyeniNessuna valutazione finora

- Astm E407Documento21 pagineAstm E407Chan UeiNianNessuna valutazione finora

- AA0850126 Rev 02Documento10 pagineAA0850126 Rev 02Manish KumarNessuna valutazione finora

- Steel Wedge Gate Valves (Flanged and Butt-Welding Ends) For The Petroleum, Petrochemical and Allied IndustriesDocumento28 pagineSteel Wedge Gate Valves (Flanged and Butt-Welding Ends) For The Petroleum, Petrochemical and Allied IndustriesImed BenNessuna valutazione finora

- Is 5334 PDFDocumento7 pagineIs 5334 PDFNav TalukdarNessuna valutazione finora

- Specification For Seamless Red Brass Pipe, Standard SizesDocumento8 pagineSpecification For Seamless Red Brass Pipe, Standard SizesVCNessuna valutazione finora

- Api-582-2016-Welding-Guidelines-For-The-Chemical-Oil-And-Gas-Industries-Apiasme-Practice-Test Clause 11.3Documento4 pagineApi-582-2016-Welding-Guidelines-For-The-Chemical-Oil-And-Gas-Industries-Apiasme-Practice-Test Clause 11.3Ahmed ElsharkawNessuna valutazione finora

- ST 37Documento7 pagineST 37rendra.farisrNessuna valutazione finora

- E 310 - 99 - Rtmxma - PDFDocumento4 pagineE 310 - 99 - Rtmxma - PDFUpul Eranda AbeyrathnaNessuna valutazione finora

- Australian Standard®Documento10 pagineAustralian Standard®Syed Mahmud Habibur Rahman0% (1)

- Asme VDocumento1 paginaAsme VMohd AnsariNessuna valutazione finora

- Astm A106 Ts EnglDocumento4 pagineAstm A106 Ts EnglxaviereduardoNessuna valutazione finora

- Product Data: Hempadur Multi-Strength 35530Documento2 pagineProduct Data: Hempadur Multi-Strength 35530Vijayaraj KumarNessuna valutazione finora

- Supplier Document Requirement Listing (SDRL)Documento23 pagineSupplier Document Requirement Listing (SDRL)Nouredine KoufiNessuna valutazione finora

- B467Documento8 pagineB467odqm_25Nessuna valutazione finora

- Se 797Documento7 pagineSe 797donaldoguerreroNessuna valutazione finora

- F629 15Documento3 pagineF629 15masoudNessuna valutazione finora

- Jis G3101 1995Documento14 pagineJis G3101 1995TUAN NGUYEN VANNessuna valutazione finora

- Quality For WeldsDocumento9 pagineQuality For WeldsArturs StangainisNessuna valutazione finora

- Iso 7452 2013 en PDFDocumento8 pagineIso 7452 2013 en PDFfahmi aballiNessuna valutazione finora

- BS 2452 (1954)Documento30 pagineBS 2452 (1954)siswou100% (1)

- Epoch 650Documento8 pagineEpoch 650andrewgeorgecherianNessuna valutazione finora

- Thermo Fisher Scientific XL3 XL2 Hardware OverviewDocumento37 pagineThermo Fisher Scientific XL3 XL2 Hardware OverviewMAmar100% (1)

- Norsok Systems No7 August 2022Documento3 pagineNorsok Systems No7 August 2022angelito bernalNessuna valutazione finora

- Asme B31.3 2020Documento4 pagineAsme B31.3 2020Tuugii OtgooNessuna valutazione finora

- API 6D InterpretationDocumento6 pagineAPI 6D InterpretationRavi MhaskeNessuna valutazione finora

- Heat Input CalculatorDocumento2 pagineHeat Input CalculatorKiukStaksNessuna valutazione finora

- QW-451 Welding THK - June5Documento17 pagineQW-451 Welding THK - June5Raj SNessuna valutazione finora

- Indt QCP RT HJ 05NDocumento14 pagineIndt QCP RT HJ 05NAsad Bin Ala QatariNessuna valutazione finora

- Tigweldarc Alloys: Certification of TestsDocumento1 paginaTigweldarc Alloys: Certification of TestsArunNessuna valutazione finora

- Welding Research Council: BulletinDocumento28 pagineWelding Research Council: BulletinRogerio Tropia GranjaNessuna valutazione finora

- Carbon Arc Cutting PDFDocumento44 pagineCarbon Arc Cutting PDFMark InnesNessuna valutazione finora

- FDA and 1935 2004 DoC General Food Contact Regulations BU HFH Rev 008Documento15 pagineFDA and 1935 2004 DoC General Food Contact Regulations BU HFH Rev 008Gisela ViskaNessuna valutazione finora

- High-Strength Copper-Base and Nickel-Copper Alloy Castings: Standard Reference Radiographs ForDocumento5 pagineHigh-Strength Copper-Base and Nickel-Copper Alloy Castings: Standard Reference Radiographs ForSarita SharmaNessuna valutazione finora

- Mil STD 2219a PDFDocumento43 pagineMil STD 2219a PDFRaron1Nessuna valutazione finora

- Partial List of ISO SpecificationsDocumento4 paginePartial List of ISO Specificationsskynyrd75Nessuna valutazione finora

- Ws - No. C Si MN P S CR Mo Ni NB Ti Ws - No. DIN BS Astm / Aisi Gost % % % % % % % % % % Germany Great Britain USA RussiaDocumento1 paginaWs - No. C Si MN P S CR Mo Ni NB Ti Ws - No. DIN BS Astm / Aisi Gost % % % % % % % % % % Germany Great Britain USA RussiamengineeringNessuna valutazione finora

- Drop Weight Tear Testing of High Toughness Pipeline MaterialDocumento8 pagineDrop Weight Tear Testing of High Toughness Pipeline MaterialKK SinghNessuna valutazione finora

- Iso 7963-2022Documento16 pagineIso 7963-2022nanotech123Nessuna valutazione finora

- LS - prt.TUB.073 Residual Magnetic Inspection MethodDocumento6 pagineLS - prt.TUB.073 Residual Magnetic Inspection MethodAlphonse YACKAMAMBO DIBACKANessuna valutazione finora

- Final Draft IRS M-28-2020Documento34 pagineFinal Draft IRS M-28-2020Utsav UniyalNessuna valutazione finora

- Is 9902 2004 PDFDocumento11 pagineIs 9902 2004 PDFAgniva DuttaNessuna valutazione finora

- 4#600 Body RSSDocumento1 pagina4#600 Body RSSRavi patelNessuna valutazione finora

- ASTM E2884 13e1Documento7 pagineASTM E2884 13e1tkNessuna valutazione finora

- NDE-Penetrant TestDocumento2 pagineNDE-Penetrant TestCandy KendeeNessuna valutazione finora

- EGWDocumento2 pagineEGWpratishgnairNessuna valutazione finora

- IPC2022-87168 - A Transparent Asme B31.8-Based Strain Assessment Method Using 3D Measurement of Dent Morphology - FinalDocumento12 pagineIPC2022-87168 - A Transparent Asme B31.8-Based Strain Assessment Method Using 3D Measurement of Dent Morphology - FinalOswaldo MontenegroNessuna valutazione finora

- Dynamic Balancing MachineDocumento4 pagineDynamic Balancing Machine.x100% (1)

- U1CDocumento4 pagineU1CAdriana HernandezNessuna valutazione finora

- Silan Semiconductors: 4-Ch Driver + Power Controller For Portable CDDocumento28 pagineSilan Semiconductors: 4-Ch Driver + Power Controller For Portable CDvetchboyNessuna valutazione finora

- TB6564AHQ (THB6064AH) : PWM Chopper-Type Bipolar Stepping Motor Driver ICDocumento39 pagineTB6564AHQ (THB6064AH) : PWM Chopper-Type Bipolar Stepping Motor Driver ICTran Duc IOTNessuna valutazione finora

- TB6564AHQ (THB6064AH) : PWM Chopper-Type Bipolar Stepping Motor Driver ICDocumento39 pagineTB6564AHQ (THB6064AH) : PWM Chopper-Type Bipolar Stepping Motor Driver ICTran Duc IOTNessuna valutazione finora

- 2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsDocumento10 pagine2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsJosé VidalNessuna valutazione finora

- 4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionDocumento10 pagine4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionvetchboyNessuna valutazione finora

- Audio Tda8510j Spec enDocumento16 pagineAudio Tda8510j Spec envetchboyNessuna valutazione finora

- CD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)Documento16 pagineCD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)vetchboyNessuna valutazione finora

- TDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierDocumento9 pagineTDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierGerardo Moreno RenteriaNessuna valutazione finora

- Tda 7296Documento14 pagineTda 7296Mayra GonzálezNessuna valutazione finora

- Digital Controlled Stereo Audio Processor With Loudness: DescriptionDocumento14 pagineDigital Controlled Stereo Audio Processor With Loudness: DescriptionvetchboyNessuna valutazione finora

- Audio Tas5100a Spec enDocumento15 pagineAudio Tas5100a Spec envetchboyNessuna valutazione finora

- Dual Btl/Quad Power Amplifier For Car Radio: ProtectionsDocumento14 pagineDual Btl/Quad Power Amplifier For Car Radio: ProtectionsvetchboyNessuna valutazione finora

- Tda7294 PDFDocumento16 pagineTda7294 PDFRoger NunesNessuna valutazione finora

- 120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyDocumento13 pagine120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyvetchboyNessuna valutazione finora

- Tda 7265 2 x25 WDocumento12 pagineTda 7265 2 x25 WJavier CanaviriNessuna valutazione finora

- 30W Bridge Car Radio Amplifier: DescriptionDocumento10 pagine30W Bridge Car Radio Amplifier: DescriptionvetchboyNessuna valutazione finora

- TDA 2822M CircuitoDocumento11 pagineTDA 2822M CircuitoDATA24Nessuna valutazione finora

- 10W Car Radio Audio Amplifier: DescriptionDocumento11 pagine10W Car Radio Audio Amplifier: DescriptionvetchboyNessuna valutazione finora

- Description: Angus Electronics Company LimitedDocumento13 pagineDescription: Angus Electronics Company LimitedvetchboyNessuna valutazione finora

- TA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyDocumento18 pagineTA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyvetchboyNessuna valutazione finora

- Angus Electronics Company Limited: PT2323 DescriptionDocumento18 pagineAngus Electronics Company Limited: PT2323 DescriptionvetchboyNessuna valutazione finora

- LM124/224/324/324A/ SA534/LM2902: Low Power Quad Op AmpsDocumento12 pagineLM124/224/324/324A/ SA534/LM2902: Low Power Quad Op AmpsvetchboyNessuna valutazione finora

- pt2388 (v1Documento18 paginept2388 (v1vetchboy0% (1)

- 2-Channel Preamplifier For Car Stereo: Package Dimensions FeaturesDocumento7 pagine2-Channel Preamplifier For Car Stereo: Package Dimensions FeaturesvetchboyNessuna valutazione finora

- Features: Stereo 330mW Audio Power Amp With ShutdownDocumento9 pagineFeatures: Stereo 330mW Audio Power Amp With ShutdownvetchboyNessuna valutazione finora

- Description: Angus Electronics Company LimitedDocumento9 pagineDescription: Angus Electronics Company LimitedvetchboyNessuna valutazione finora

- Angus Electronics Company Limited: PreliminaryDocumento18 pagineAngus Electronics Company Limited: PreliminaryvetchboyNessuna valutazione finora

- 2-Channel Preamplifier For Car Stereo: Package Dimensions FeaturesDocumento7 pagine2-Channel Preamplifier For Car Stereo: Package Dimensions FeaturesvetchboyNessuna valutazione finora

- Dual Operational Amplifiers: Technical DataDocumento4 pagineDual Operational Amplifiers: Technical DatavetchboyNessuna valutazione finora

- Akira Dm-301p Service ManualDocumento11 pagineAkira Dm-301p Service ManualAvr Electronica ChileNessuna valutazione finora

- Aero Technology Easa Module 4 Electronic FundamentDocumento29 pagineAero Technology Easa Module 4 Electronic FundamentAnoop SinghNessuna valutazione finora

- Fail Kursus DEB1133 Fundemental of Electronic $ Circuit TheoryDocumento268 pagineFail Kursus DEB1133 Fundemental of Electronic $ Circuit TheoryAiman AmnNessuna valutazione finora

- PM Power Catalog Abacus 07-09-15Documento85 paginePM Power Catalog Abacus 07-09-15rafael quiaroNessuna valutazione finora

- The Basic Amplifier SystemDocumento6 pagineThe Basic Amplifier SystemNeelam KapoorNessuna valutazione finora

- A Fully Differential Chopper Circuit in 130nm CMOSDocumento10 pagineA Fully Differential Chopper Circuit in 130nm CMOSWala SaadehNessuna valutazione finora

- Scp250 Power Factor Instruction ManualDocumento40 pagineScp250 Power Factor Instruction ManualPhamVan CaNessuna valutazione finora

- Denon AVR-1905Documento2 pagineDenon AVR-1905turucNessuna valutazione finora

- Frequency ResponseDocumento97 pagineFrequency ResponseZhong Kiat TehNessuna valutazione finora

- Altec Lansing Voice of The Theater A7 ManualDocumento8 pagineAltec Lansing Voice of The Theater A7 ManualGlock20Nessuna valutazione finora

- Tda 8780Documento16 pagineTda 8780Andrey DolgovNessuna valutazione finora

- Unit II Radio ReceiversDocumento29 pagineUnit II Radio ReceiversecekluNessuna valutazione finora

- Icl7611 Icl764xDocumento26 pagineIcl7611 Icl764xNguyen ThangNessuna valutazione finora

- Fode Distance Learning: Department of Education Grade 12 Information Communication TechnologyDocumento101 pagineFode Distance Learning: Department of Education Grade 12 Information Communication TechnologymuheNessuna valutazione finora

- Active LoadsDocumento9 pagineActive LoadsGowndaManiNessuna valutazione finora

- Audio Spotlight TechnologyDocumento6 pagineAudio Spotlight TechnologyMose McneilNessuna valutazione finora

- Guitar Tuner With An Arduino: by EE421ACDCDocumento9 pagineGuitar Tuner With An Arduino: by EE421ACDCKerem AydınNessuna valutazione finora

- BEEE LessonPlanDocumento3 pagineBEEE LessonPlanShilpa SweetyNessuna valutazione finora

- Automotive Power Seat Reference Design: TI Designs: TIDA-020008Documento30 pagineAutomotive Power Seat Reference Design: TI Designs: TIDA-020008LiemNessuna valutazione finora

- Math ProblemsDocumento6 pagineMath ProblemsAlyssa May BautistaNessuna valutazione finora

- 1000 Life Safety System: FeaturesDocumento8 pagine1000 Life Safety System: FeaturesKarlaSampoNessuna valutazione finora

- SUB 708-AS II - Spec SheetDocumento3 pagineSUB 708-AS II - Spec SheetAndrea PaoNessuna valutazione finora

- Low Power Quad Operational Amplifiers Az324Documento13 pagineLow Power Quad Operational Amplifiers Az324AbdoNessuna valutazione finora

- All India Radio Training GwaliorDocumento18 pagineAll India Radio Training GwaliorBMLIVENessuna valutazione finora

- Operation & Maintenance: A160-Om-C-May15Documento66 pagineOperation & Maintenance: A160-Om-C-May15Gustavo PalaciosNessuna valutazione finora

- Ultrasonic Imaging SystemDocumento12 pagineUltrasonic Imaging SystemKiran Kumar100% (1)

- Ina 105Documento17 pagineIna 105amreshjha22Nessuna valutazione finora

- Panasonic WP1400 PDFDocumento69 paginePanasonic WP1400 PDFboroda2410Nessuna valutazione finora

- CXD1175AM/AP: 8-Bit 20MSPS Video A/D Converter (CMOS)Documento21 pagineCXD1175AM/AP: 8-Bit 20MSPS Video A/D Converter (CMOS)raviNessuna valutazione finora

- The Journeyman Electrician Exam Study Guide: Proven Methods for Successfully Passing the Journeyman Electrician Exam with ConfidenceDa EverandThe Journeyman Electrician Exam Study Guide: Proven Methods for Successfully Passing the Journeyman Electrician Exam with ConfidenceNessuna valutazione finora

- Multiplexed Networks for Embedded Systems: CAN, LIN, FlexRay, Safe-by-Wire...Da EverandMultiplexed Networks for Embedded Systems: CAN, LIN, FlexRay, Safe-by-Wire...Nessuna valutazione finora

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionDa EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionValutazione: 4.5 su 5 stelle4.5/5 (543)

- Electrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tDa EverandElectrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tValutazione: 4.5 su 5 stelle4.5/5 (27)

- A Mind at Play: How Claude Shannon Invented the Information AgeDa EverandA Mind at Play: How Claude Shannon Invented the Information AgeValutazione: 4 su 5 stelle4/5 (53)

- Conquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeDa EverandConquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeValutazione: 4.5 su 5 stelle4.5/5 (10)

- Power System Control and ProtectionDa EverandPower System Control and ProtectionB. Don RussellValutazione: 4 su 5 stelle4/5 (11)

- 2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersDa Everand2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersValutazione: 5 su 5 stelle5/5 (1)

- Guide to the IET Wiring Regulations: IET Wiring Regulations (BS 7671:2008 incorporating Amendment No 1:2011)Da EverandGuide to the IET Wiring Regulations: IET Wiring Regulations (BS 7671:2008 incorporating Amendment No 1:2011)Valutazione: 4 su 5 stelle4/5 (2)

- INCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesDa EverandINCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesValutazione: 5 su 5 stelle5/5 (1)

- Practical Electrical Wiring: Residential, Farm, Commercial, and IndustrialDa EverandPractical Electrical Wiring: Residential, Farm, Commercial, and IndustrialValutazione: 3.5 su 5 stelle3.5/5 (3)

- Programming the Raspberry Pi, Third Edition: Getting Started with PythonDa EverandProgramming the Raspberry Pi, Third Edition: Getting Started with PythonValutazione: 5 su 5 stelle5/5 (2)

- Hacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsDa EverandHacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsValutazione: 3.5 su 5 stelle3.5/5 (2)

- Digital Transformation: Survive and Thrive in an Era of Mass ExtinctionDa EverandDigital Transformation: Survive and Thrive in an Era of Mass ExtinctionValutazione: 4.5 su 5 stelle4.5/5 (9)

- Schaum's Outline of Basic Electricity, Second EditionDa EverandSchaum's Outline of Basic Electricity, Second EditionValutazione: 5 su 5 stelle5/5 (14)

- Retro Gaming with Raspberry Pi: Nearly 200 Pages of Video Game ProjectsDa EverandRetro Gaming with Raspberry Pi: Nearly 200 Pages of Video Game ProjectsNessuna valutazione finora

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionDa EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionValutazione: 4 su 5 stelle4/5 (331)

- Teach Yourself Electricity and Electronics, 6th EditionDa EverandTeach Yourself Electricity and Electronics, 6th EditionValutazione: 3.5 su 5 stelle3.5/5 (15)

- Build Your Own Electronics WorkshopDa EverandBuild Your Own Electronics WorkshopValutazione: 3.5 su 5 stelle3.5/5 (3)

- DIY Drones for the Evil Genius: Design, Build, and Customize Your Own DronesDa EverandDIY Drones for the Evil Genius: Design, Build, and Customize Your Own DronesValutazione: 3.5 su 5 stelle3.5/5 (3)

- Open Radio Access Network (O-RAN) Systems Architecture and DesignDa EverandOpen Radio Access Network (O-RAN) Systems Architecture and DesignNessuna valutazione finora

- Empires of Light: Edison, Tesla, Westinghouse, and the Race to Electrify the WorldDa EverandEmpires of Light: Edison, Tesla, Westinghouse, and the Race to Electrify the WorldValutazione: 4 su 5 stelle4/5 (87)