Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Different Types of Modeling

Caricato da

Agnus S Swarna LakshmiDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Different Types of Modeling

Caricato da

Agnus S Swarna LakshmiCopyright:

Formati disponibili

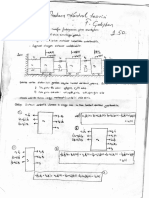

DIFFERENT TYPES OF MODELING & TEST BENCH MODELING IN VHDL: MODELING IN VHDL In VHDL, the term Modeling refers

rs to the type of description styles i.e. code that can be written on the basis of logical structure, functionality, behavior of the design or it can be a combination of these three styles. Hence on the basis of this there are different type of modeling in VHDL. DATAFLOW MODELING: DATAFLOW MODELING A dataflow modeling specifies the functionality of the entity without explicitly specifying its structure. This functionality shows the flow of information through the entity,which is expressed using concurrent signal assignment statements. An architecture body can contain any number of concurrent signal assignment statements. Conditional statement can also be used in dataflow modeling. e.g. WHEN conditional statement. Dataflow modeling is used when the user knows the exact expressions for the desired outputs. Statements are declared in the architecture after the keyword BEGIN. : Slide 5: Library IEEE; use IEEE.STD_LOGIC_1164. all ; entity halfadder is port ( A,B :in bit ;S,C :out bit ); end halfadder ; architecture ha_ar of ha_en is begin S <= A xor B; C <= A and B ; End architecture ha_ar ; Dataflow Code for 4:1 multiplexer using conditional statement WHEN: LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY mux4to1 IS port (I: in std_logic_vector(0 to 3); s:in std_logic)vector(0 to 1);y:out std_logic); END ENTITY mux4to1; ARCHITECTURE mux4to1 OF mux4to1 IS BEGIN Y<= I(0) when s=00 else Y<= I(1) when s=01 else Y<= I(2) when s=10 else Y<= I(3) when s=11 ; END ARCHITECTURE mux4to1; Dataflow Code for half adder without using conditional statement: ADVANTAGES OF DATAFLOW MODELING: ADVANTAGES OF DATAFLOW MODELING Does not need truth table or behavioral information. Does not need any structural information. Code become compressed for simple design. DISADVANTGES OF DATAFLOW MODELING Code become very lengthy for complex design. It will be difficult to write the dataflow code as the number of input and output increases. Sequential statements can not be used in data flow modeling .

STRUCTURAL MODELING: STRUCTURAL MODELING In structural style of modeling, the entity is described as a set of interconnected components. The component instantiation statement is the primary mechanism used for describing such a model of an entity. Implicit definition of I/O relationship is done through particular structure. There is no need of sequential or conditional statements in this type of modeling. A list of components and there connections in any language is used in this type of modeling which is also sometimes called netlist. The behavior of the entity is not explicitly apparent from its model In structural modeling architecture body is composed of two parts : : In structural modeling architecture body is composed of two parts : 1. Component declaration Component declaration is done after the keyword architecture and before the keyword begin. A component declaration declares the name and the interface of a component. The interface specifies the mode and the type of ports. e.g. of a two input nor gate as a component declaration: component nor_gate port (a,b: in bit; c: out bit); end component; Signals: signals are the interconnecting wires b/w two components that cannot be declared in entity as input port or output port. 2. Component instantiation A component instantiation statement defines a subcomponent of the entity in which it appears . It associates the signals in the entity with the port of that subcomponent. A format of a component instantiation statement is: Component-label: component-name[port map(association-list)]; Slide 9: library IEEE ; use IEEE . STD_LOGIC_1164 . all ; entity fa_en is port ( A , B , Cin : in bit ; SUM , CARRY : out bit ); end fa_en ; architecture fa_ar of fa_en is component ha_en port ( A , B : in bit ; S , C : out bit ); end component ; Component or2 Port( a,b:in bit: y: out bit); End component; signal C1 , C2 , S1 :bit ; begin HA1 : ha_en port map ( A , B , S1 , C1 ); HA2 : ha_en port map ( S1 , Cin , SUM , C2 ); o1:or2 port map (c1,c2,carry); end fa_ar ; VHDL code of full adder using two half adder and an OR gate using structural modeling: ADVANTAGES OF STRUCTURAL MODELING: ADVANTAGES OF STRUCTURAL MODELING Does not need truth table or behavioral information. Code become compressed for simple design. No need of

any logical equation. No need of sequential or conditional statements. DISADVANTGES OF STRUCTURAL MODELING It is difficult to write structural code for complex design. It is more time consuming as compare to other two types of modelings. Complete structure should be known to the user. BEHAVIORAL MODELING: The behavioral modeling specifies the behavior of an entity as a set of statements that are executed sequentially in the specified order. This set of sequential statements , which are specified inside a process statement , do not explicitly specify the structure of the entity but merely its functionality. Behavioral code cannot be written without a process statement. A process statement is a concurrent statement that can appear within an architecture body. Architecture body can have any number of processes . A process statement also has declarative part (before the keyword begin) and a statement part (between the keywords begin and end process ). The statements appearing within the process statement are sequential statements and executed sequentially. A variable is declared within the process statement unlike the signal which is declared outside. A variable is different from a signal in that it is always assigned a value instantaneously, and the assignment operator used is the:= compound symbol; contrast this with a signal that is assigned a value always after a certain delay. BEHAVIORAL MODELING PROCESS STATEMENT: PROCESS STATEMENT A process statement contains sequential statements that describe the functionality of a portion of an entity in sequential terms. Process statement is declared after a keyword architecture and before the keyword begin. All types of sequential statements can be used within the process statement. e.g. if-statement case-statement loop-statement etc. LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY mux4to1 IS port (I: in std_logic_vector(0 to 3); s:in std_logic)vector(0 to 1);y:out std_logic); END ENTITY mux4to1; ARCHITECTURE beh OF mux4to1 IS BEGIN Process ( s,I ) begin z<=((not s0)and(not s1)and I(0))or((not s0)and s1 and I(1))or(s0 and(not s1 )and I(2) )or (s0 and s1 and I(3)); END ARCHITECTURE beh ; Behavioral code for 4:1 multiplexer without any sequential statements Behavioral code for 4:2 priority encoder using if statement:

Behavioral code for 4:2 priority encoder using if statement LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY pr_encode IS port( I:in std_logic_vector(0 to 3);y:out std_logic_vector(0 to 1);v:out std_logic); END ENTITY pr_encode ; ARCHITECTURE pr_beh OF pr_encode IS BEGIN process (I) begin if I(0)='1 ' then y<="00" ; elsif I(1)='1' then y<="01" ; elsif I(2)='1' then y<="10"; else Y<="11"; end if; if I="0000" then v<='0'; else v<='1'; end if; end process; END ARCHITECTURE pr_beh ; LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY mux8x1_beh IS port (I: in std_logic_vector(0 to 7); s : in std_logic_vector(0 to 2); y : out std_logic); END ENTITY mux8x1_beh; ARCHITECTURE data_mux OF mux8x1_beh IS BEGIN process (I,S) begin case s is when "000" =>y<= I(0); when "001" =>y<= I(1); when "010" =>y<= I(2); when "011" =>y<= I(3); when "100" =>y<= I(4); when "101" =>y<= I(5); when "110" =>y<= I(6); when "111" =>y<= I(7); when others =>y<= I(0); end case; end process; END ARCHITECTURE data_mux ; Behavioral code for 8:1 multiplexer using case statement ADVANTAGES OF BEHAVIORAL MODELING: ADVANTAGES OF BEHAVIORAL MODELING Code become compressed for complex design. No need of any logical equation. Sequential or conditional statements can be used. No need of structural information. Less time consuming. User can write behavioral code for any design. It is fastest to simulate out of these three modelings. DISADVANTGES OF BEHAVIORAL MODELING Behavior of the design should be known to the user . Hence for industry purposes also behavioral modeling is best and mostly used also. MIXED MODELING: It is possible to mix the three modeling styles that we have seen so far in a single architecture body. Within an architecture body , we can use :- MIXED MODELING Here first d latch is declared as component i.e. using structural modeling. clock of second latch assigned value using dataflow modeling. And final output is achieved using behavioral modeling. component instantiation statements( that represent structure ), concurrent signal assignment (that represent dataflow) and process statements (that represent behavior). Example of a mixed modeling: ADVANTAGES OF MIXED MODELING: LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all ; ENTITY d_latch IS por t( d,clk:in std_logic;q1,q1b: out std_logic); END ENTITY d_latch ;

ARCHITECTURE latch OF d_latch IS Component latch1 Por t( d,c:in std_logic;q : inout std_logic); (structural modeling) End component ; BEGIN L1: latch1 port map (d, clk ,q); C1<=not clk ; (data flow modeling) process (d,c1) begin if (c1='1') then (behavioral modeling) q1<=d; q1b<= not (d); end if; end process; END ARCHITECTURE latch; Vhdl Code for master slave d-flip flop using mixed modeling ADVANTAGES OF MIXED MODELING Code become easier for complex design. Code can be written block wise.. Sequential or conditional statements can be used. Less time consuming.

Potrebbero piacerti anche

- A Reversible Design of BCD MultiplierDocumento6 pagineA Reversible Design of BCD MultiplierJournal of ComputingNessuna valutazione finora

- Microsemi Make Linear Mode WorkDocumento6 pagineMicrosemi Make Linear Mode WorkrauolNessuna valutazione finora

- Digital Signal Processors Architectures Implementations and ApplicationsDocumento17 pagineDigital Signal Processors Architectures Implementations and ApplicationsAbirami Kannan0% (3)

- DIGITAL CIRCUIT SimulationDocumento60 pagineDIGITAL CIRCUIT SimulationNidheesh KMNessuna valutazione finora

- Cadence Nclaunch LabDocumento86 pagineCadence Nclaunch Labsweety987Nessuna valutazione finora

- Migrating To Onsemi Network & CliosoftDocumento29 pagineMigrating To Onsemi Network & CliosoftRamakrishnaRao SoogooriNessuna valutazione finora

- IBM ASIC-SoC MethodologyDocumento12 pagineIBM ASIC-SoC Methodologyghatakp2069Nessuna valutazione finora

- Modelling Latches and FlipflopsDocumento9 pagineModelling Latches and Flipflopsmachnik1486624Nessuna valutazione finora

- LESSON 5 Floating PointDocumento11 pagineLESSON 5 Floating PointJཽᴇᴋᴋᴜ -sᴀᴍᴀNessuna valutazione finora

- PBG BCI RoboticsDocumento5 paginePBG BCI Roboticsbangalore2009Nessuna valutazione finora

- VLSI Implementation of Turbo Coder For LTE Using Verilog HDLDocumento5 pagineVLSI Implementation of Turbo Coder For LTE Using Verilog HDLSamreen FarhanaNessuna valutazione finora

- Mechatronics (2015) Unit IIDocumento38 pagineMechatronics (2015) Unit IIkishan100% (1)

- Lecture21 TimingDocumento16 pagineLecture21 TimingUtkarsh JainNessuna valutazione finora

- Lab #4Documento4 pagineLab #4Bryan Ricardo Boyer0% (1)

- Algorithm Design and AnalysisDocumento2 pagineAlgorithm Design and AnalysisCandy AngelNessuna valutazione finora

- Design of Double Precision IEEE-754 Floating-Point UnitsDocumento73 pagineDesign of Double Precision IEEE-754 Floating-Point UnitsMichael Kennedy100% (15)

- Ultrafast Soft Recovery Rectifier Diode: APT30D120B 1200V 30ADocumento4 pagineUltrafast Soft Recovery Rectifier Diode: APT30D120B 1200V 30AViktor RudanNessuna valutazione finora

- ADPLL Design and Implementation On FPGADocumento6 pagineADPLL Design and Implementation On FPGANavathej BangariNessuna valutazione finora

- Fast Fourier TransformsDocumento19 pagineFast Fourier Transformsapi-3837905Nessuna valutazione finora

- Me6702 Mechatronics Unit 4Documento23 pagineMe6702 Mechatronics Unit 4Niyas AhamedNessuna valutazione finora

- EC6711 Embedded Lab Student Manual 19-20 Odd Sem PDFDocumento142 pagineEC6711 Embedded Lab Student Manual 19-20 Odd Sem PDFJayamani KrishnanNessuna valutazione finora

- Experiment No:: To Design and Implement A 4-Bit Carry Look Ahead Adder Using VHDLDocumento7 pagineExperiment No:: To Design and Implement A 4-Bit Carry Look Ahead Adder Using VHDLVinay YadavNessuna valutazione finora

- 1501 - Introduction To Process Modeling MethodologyDocumento103 pagine1501 - Introduction To Process Modeling Methodologykotafi_atefNessuna valutazione finora

- Ecad & Vlsi LabDocumento98 pagineEcad & Vlsi LabbitseceNessuna valutazione finora

- Ec8562 DSP ManualDocumento86 pagineEc8562 DSP ManualN.S.Priyanga 33Nessuna valutazione finora

- Embedded Systems Lab ManualDocumento114 pagineEmbedded Systems Lab ManualPrasanth100% (1)

- Vlsi Verilog - Fir Filter Design Using VerilogDocumento5 pagineVlsi Verilog - Fir Filter Design Using VerilogNanda KumarNessuna valutazione finora

- Sequence Detector Application ExamplesDocumento7 pagineSequence Detector Application ExamplesXXX100% (2)

- Vlsi Front-End DesginDocumento40 pagineVlsi Front-End Desginvenkata satishNessuna valutazione finora

- Cheng Kdml07posterDocumento1 paginaCheng Kdml07posterWeiwei ChengNessuna valutazione finora

- Opamp (Ota) Design: The Design Process Involves Two Distinct Activities: - Architecture DesignDocumento87 pagineOpamp (Ota) Design: The Design Process Involves Two Distinct Activities: - Architecture DesignKumar GaneshNessuna valutazione finora

- Ans 7Documento3 pagineAns 7Md Shakir AlamNessuna valutazione finora

- Generate VHDL Code From Matlab Code: Bookmark This PageDocumento10 pagineGenerate VHDL Code From Matlab Code: Bookmark This PageAnonymous JnvCyu85Nessuna valutazione finora

- Modern Control TheoryDocumento17 pagineModern Control TheoryBurakApaydınNessuna valutazione finora

- Serial CommunicationDocumento52 pagineSerial CommunicationDr Narayana Swamy RamaiahNessuna valutazione finora

- Design and Implementation of A Fast Unsigned 32-Bit Multiplier Using VHDLDocumento4 pagineDesign and Implementation of A Fast Unsigned 32-Bit Multiplier Using VHDLAniruddh JainNessuna valutazione finora

- VLSI Lab ManualDocumento48 pagineVLSI Lab ManualMohib KhanNessuna valutazione finora

- BCD Lite Data SheetDocumento5 pagineBCD Lite Data SheetBenjamin DoverNessuna valutazione finora

- Execution Anomaly Detection in Distributed Systems Through Unstructured Log AnalysisDocumento10 pagineExecution Anomaly Detection in Distributed Systems Through Unstructured Log AnalysisredzgnNessuna valutazione finora

- STLDDocumento18 pagineSTLDGagan tej gowdNessuna valutazione finora

- Gaussian Random Number Generator Using Boxmuller MethodDocumento27 pagineGaussian Random Number Generator Using Boxmuller MethodAbhijeet Singh KatiyarNessuna valutazione finora

- UNIT-I Digital System DesignDocumento28 pagineUNIT-I Digital System DesignNarasimha Murthy YayavaramNessuna valutazione finora

- Design of 16 Bit Alu: Prepared By: - Chandana - Mamatha - Praneeth ReddyDocumento22 pagineDesign of 16 Bit Alu: Prepared By: - Chandana - Mamatha - Praneeth ReddyChandanaNessuna valutazione finora

- Intelligent InstrumentationDocumento1 paginaIntelligent InstrumentationAshish Arora25% (4)

- Industry Insights Blogs: Richard Goering (/members/rgoering)Documento5 pagineIndustry Insights Blogs: Richard Goering (/members/rgoering)hello860Nessuna valutazione finora

- 29-2 CDocumento8 pagine29-2 Canon_621618677Nessuna valutazione finora

- Dlda - M - 09Documento29 pagineDlda - M - 09babu100% (1)

- 2.1 Basic Design Concepts in TQMDocumento6 pagine2.1 Basic Design Concepts in TQMDr.T. Pridhar ThiagarajanNessuna valutazione finora

- MontecarloDocumento44 pagineMontecarloAnand Krishna GhattyNessuna valutazione finora

- ANN - Ch2-Adaline and MadalineDocumento29 pagineANN - Ch2-Adaline and MadalineMuhanad Al-khalisy100% (1)

- Problem Filter Design 1Documento22 pagineProblem Filter Design 1ShivMeenaNessuna valutazione finora

- 1 Lab Manual-Final-Control-System-1Documento35 pagine1 Lab Manual-Final-Control-System-1Shimalis RetaNessuna valutazione finora

- Eee.60-62Documento3 pagineEee.60-62skrtamilNessuna valutazione finora

- VHDL Modeling TypesDocumento5 pagineVHDL Modeling TypespdnkiranNessuna valutazione finora

- Vlsi Design - Final YearDocumento28 pagineVlsi Design - Final YearFLOWERNessuna valutazione finora

- Unit 5Documento49 pagineUnit 5madhuriNessuna valutazione finora

- Jaypee University of Engineering & Technology, Guna Deparment of Computer Science & EngineeringDocumento7 pagineJaypee University of Engineering & Technology, Guna Deparment of Computer Science & EngineeringAmit SharmaNessuna valutazione finora

- What Is VHDL?: Entity Is Port EndDocumento7 pagineWhat Is VHDL?: Entity Is Port EndsrvdharNessuna valutazione finora

- Project Report Arithmetic Logic Unit (ALU)Documento71 pagineProject Report Arithmetic Logic Unit (ALU)Hemant Sharma100% (1)

- Introduction To ConquestrDocumento7 pagineIntroduction To ConquestrWowser PlodsNessuna valutazione finora

- OS S2020 2140702 APY MaterialDocumento2 pagineOS S2020 2140702 APY MaterialPrince PatelNessuna valutazione finora

- OOP Exercises For Slot 456Documento4 pagineOOP Exercises For Slot 456Phu DaoNessuna valutazione finora

- Low Level Virtual Machine C# Compiler Senior Project Proposal PresentationDocumento38 pagineLow Level Virtual Machine C# Compiler Senior Project Proposal PresentationprabirshresthaNessuna valutazione finora

- Java Chapters 1-6Documento50 pagineJava Chapters 1-6Jennifer PolidanoNessuna valutazione finora

- Match Index and Match ReverseDocumento2 pagineMatch Index and Match ReverseHarish Kumar100% (1)

- Quarto Cheat SheetDocumento1 paginaQuarto Cheat SheetAbraham GarciaNessuna valutazione finora

- Configuring A DateDocumento23 pagineConfiguring A DateHarikrishnan MuthusamyNessuna valutazione finora

- What Is The Output of This ProgramDocumento5 pagineWhat Is The Output of This ProgramJasleen KaurNessuna valutazione finora

- Terayon v1.3.4.tplDocumento4 pagineTerayon v1.3.4.tplMd Hridoy HossainNessuna valutazione finora

- Examples of How To Use Some Utilities and FunctionobjectsDocumento33 pagineExamples of How To Use Some Utilities and FunctionobjectskosmitoNessuna valutazione finora

- MAS 1st Preboard With Answer Jan 2014Documento10 pagineMAS 1st Preboard With Answer Jan 2014Alyssah Grace EllosoNessuna valutazione finora

- Program To Reverse The Entered StringDocumento30 pagineProgram To Reverse The Entered StringPriyanka Rai100% (1)

- Excel QuestionsDocumento4 pagineExcel QuestionsSamsonNessuna valutazione finora

- Singly Linked List As Circular: ExampleDocumento18 pagineSingly Linked List As Circular: ExampleLeary John TambagahanNessuna valutazione finora

- CSCI235 W3 Lab - Fall2022Documento3 pagineCSCI235 W3 Lab - Fall2022Game - AnANessuna valutazione finora

- Index: - What Are Psets? - Creation of Psets. - What Is Analysis - Level Parameter?Documento16 pagineIndex: - What Are Psets? - Creation of Psets. - What Is Analysis - Level Parameter?Sathvik AdduriNessuna valutazione finora

- ABAP IQ by Arjun PDFDocumento9 pagineABAP IQ by Arjun PDFAnkur Jain100% (1)

- Programming LanguagesDocumento3 pagineProgramming LanguagesDilendra BhattNessuna valutazione finora

- Pega OwnDocumento102 paginePega OwnNag ReddyNessuna valutazione finora

- Sql-Basics-Cheat-Sheet-A3 (SQL Carte Mentale Des Requêtes)Documento1 paginaSql-Basics-Cheat-Sheet-A3 (SQL Carte Mentale Des Requêtes)Thy HuỳnhNessuna valutazione finora

- VFP Tutorial - Micorsoft Visual FoxproDocumento46 pagineVFP Tutorial - Micorsoft Visual FoxproLino CuestaNessuna valutazione finora

- Rexx in SDSFDocumento340 pagineRexx in SDSFViktor TrujilloNessuna valutazione finora

- Ds Assignment 3Documento6 pagineDs Assignment 3AshutoshSharmaNessuna valutazione finora

- Array and StringsDocumento4 pagineArray and StringstovilasNessuna valutazione finora

- stm32f4 Hal and Lowlayer DriversDocumento2.227 paginestm32f4 Hal and Lowlayer DriversMohamed DRISSINessuna valutazione finora

- Wave OSDR0 Developer ManualDocumento632 pagineWave OSDR0 Developer ManualOned GómezNessuna valutazione finora

- Module 3 Rts PDFDocumento19 pagineModule 3 Rts PDFHusna TajNessuna valutazione finora

- Key Takeaways - PDV - PRASADDocumento27 pagineKey Takeaways - PDV - PRASADDevi Vara PrasadNessuna valutazione finora

- EEX4465 - Data Structures and Algorithms 2020/2021: Tutor Marked Assignment - #2 Deadline OnDocumento2 pagineEEX4465 - Data Structures and Algorithms 2020/2021: Tutor Marked Assignment - #2 Deadline OnNawam UdayangaNessuna valutazione finora