Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

(EE476) (Lab 1) 09ece - Group8

Caricato da

Trung LyamDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

(EE476) (Lab 1) 09ece - Group8

Caricato da

Trung LyamCopyright:

Formati disponibili

5/6/2013

LABORATORY 1 EE 476

Lab 1: Introduced to the Cadence suit of IC design tools

GROUP 8 09ECE Danang University of Technology, Faculty of Electronics and Telecommunications, COE center

DESIGN CMOS INVERTER 1

Danang University of Technology, Faculty of Electronics and Telecommunications EE 476 Lab 1: Introduced to the Cadence suit of IC design tools TA. Vo Tuan Minh

MEMBER OF GROUP 8: L Mai Trung L Huy L Quang Tun

Table of Contents

A. Design CMOS Inverter

1. 2. 3. 4. CMOS inverter basics Design Layout in Cadence Results of Testbench Explanation

B. Design AND gate

1. Introduction the principle operation 2. Design Layout in Cadence 3. Results of Testbench

LABORATORY 1 EE 476

GROUP 8 09ECE

DESIGN CMOS INVERTER 2 A. DESIGN CMOS INVERTER

1. CMOS Inverter basics:

From Figure 1, a CMOS circuit is composed of two MOSFETs. The top FET (MP) is a PMOS type device while the bottom FET (MN) is an NMOS type. The body effect is not present in either device since the body of each device is directly connected to the devices source. Both gates are connected to the input line. The output line connects to the drains of both FETs. Take a look at the VTC in Figure 2. The curve represents the output voltage taken from node 3. We can easily see that the CMOS circuit functions as an inverter by noting that when VIN is five volts, VOUT is zero, and vice versa. Thus when inputting a high we get a low and when input a low we get a high as is expected for any inverter.

The active PMOS load device is a PMOS transistor, wherein the source of the PMOS transistor is connected to the power supply voltage and the drain of the PMOS transistor is connected to the amplifying unit wherein the second load device further comprises: a compensation unit which is connected to the negative feedback buffering unit and compensates for both a gain and a frequency characteristics in the high frequency range. The gate of the NMOS transistor of the negative feedback load buffering unit is connected to the drain of the PMOS transistor, the source of the NMOS transistor of the negative feedback load buffering unit is connected to the gate of the PMOS transistor, and the drain of the NMOS transistor is connected to the power supply voltage.

LABORATORY 1 EE 476 GROUP 8 09ECE

DESIGN CMOS INVERTER 3

2. Design Layout in Cadence: Inverter schematic:

- PMOS with W/L = 3um/100nm - NMOS with W/L = 1um /100 nm

LABORATORY 1 EE 476

GROUP 8 09ECE

DESIGN CMOS INVERTER 4

Sympol of the inverter:

Schematic of Inverters testbench:

Adding a 20f F Capacitor in the schematic of testbench.

LABORATORY 1 EE 476 GROUP 8 09ECE

DESIGN CMOS INVERTER 5

3. Results of testbench: Input is a Voltage pulse with period = 1us. Rise time = 100ns. Fall time = 100ns. Pulse width = 400ns Voltage peak to peak from 0 to 1V And voltage source VDC = 1V. Set up for 2u of simulation time. The result: Input and Output show in the same graph

LABORATORY 1 EE 476

GROUP 8 09ECE

DESIGN CMOS INVERTER 6

Only the output:

LABORATORY 1 EE 476

GROUP 8 09ECE

DESIGN CMOS INVERTER 7

The input and output show in the graph is opposite amplitude, because output and input is reverse. 4. Explanation: Changing the W/L on PMOS and CMOS to get a new output. 1. Design PMOS with W/L = 3um/100nm and NMOS with W/L = 1um /100 nm 2. PMOS with W/L = 6um/100nm and NMOS with W/L = 2um /100 nm 3. PMOS with W/L = 1.5um/100nm and NMOS with W/L = 0.5um /100 nm 1 Green line 2 Red line 3 Yellow line

LABORATORY 1 EE 476

GROUP 8 09ECE

DESIGN CMOS INVERTER 8

Let zoom in for more detail, at this time: 1 Redline 2 Yellow line Check the graph from low to high (raising era):

3 Blue line

At we can see, the yellow line (as known as PMOS with W/L = 6um/100nm and NMOS with W/L = 2um /100 nm) raises first then the red line (PMOS with W/L = 3um/100nm and NMOS with W/L = 1um /100 nm) and finally the blue line (PMOS with W/L = 1.5um/100nm and NMOS with W/L = 0.5um /100 nm). By the principle operation, PMOS has many holes and NMOS has many charges, charges from NMOS will go in PMOS to fulfill the holes. PMOS and NMOS have width increases that

LABORATORY 1 EE 476 GROUP 8 09ECE

DESIGN CMOS INVERTER 9

leads to the movement of charges increases. The inverter is more active, the delay time is smaller. We have

W/L is increase then tpLH decreases. Or the tpLH (Low to High) of output = 6um is lowest and tpLH of output = 1.5um is highest. Check the graph from high to low (falling era) 1 Redline 2 Yellow line

3 Blue line

LABORATORY 1 EE 476

GROUP 8 09ECE

DESIGN CMOS INVERTER 10

At this falling time, opposite to raising era, the blue line falls first then the red line and finally the yellow line. The increase width of gate increases the delay time from high to low. The greater width, the greater value of total capacitance (intrinsic capacitance plus load capacitance) is because width length in proportion to intrinsic capacitance. Thus, discharging time increases. This explain why increasing W, tphl (high to low) increases.

B. Design AND gate

1. Introduction the principle operation:

To create AND gate CMOS, we have to create NAND gate CMOS first then use INVERTER CMOS to fulfill the operation of AND gate CMOS.

LABORATORY 1 EE 476

GROUP 8 09ECE

DESIGN CMOS INVERTER 11

2. Design Layout in Cadence NAND GATE CMOS schematic

PMOS with W/L = 3um/100nm NMOS with W/L = 1um /100 nm

LABORATORY 1 EE 476

GROUP 8 09ECE

DESIGN CMOS INVERTER 12

Symbol of NAND gate CMOS:

Combining NAND gate CMOS and INVERTER CMOS to create AND gate CMOS

LABORATORY 1 EE 476

GROUP 8 09ECE

DESIGN CMOS INVERTER 13

Symbol of AND gate CMOS:

Schematic of testbench AND gate:

LABORATORY 1 EE 476

GROUP 8 09ECE

DESIGN CMOS INVERTER 14

3. Results of Testbench: Set up the period, rise time, fall time, delay time of the two inputs like the image below.

LABORATORY 1 EE 476

GROUP 8 09ECE

DESIGN CMOS INVERTER 15

LABORATORY 1 EE 476

GROUP 8 09ECE

DESIGN CMOS INVERTER 16

The results:

LABORATORY 1 EE 476

GROUP 8 09ECE

DESIGN CMOS INVERTER 17

The other results when setting up the different period, rise time, fall time, delay time of the two inputs.

Period: 2 us, rise time = fall time = 100n s, delay time = 0, pulse width = 400ns

LABORATORY 1 EE 476

GROUP 8 09ECE

DESIGN CMOS INVERTER 18

delay time = 500n s Period: 2 us, rise time = fall time = 100n s, delay time = 0, pulse width = 400ns

LABORATORY 1 EE 476

GROUP 8 09ECE

DESIGN CMOS INVERTER 19

Input A: delay time 500n s Period: 2 us, rise time = fall time = 100n s, delay time = 0, pulse width = 400ns

LABORATORY 1 EE 476

GROUP 8 09ECE

Potrebbero piacerti anche

- CMOS PortDocumento46 pagineCMOS PortZali100% (1)

- Laboratory No. 9:: Simple Calculator (Final Lab)Documento10 pagineLaboratory No. 9:: Simple Calculator (Final Lab)2017 01051Nessuna valutazione finora

- Linear Dynamic Systems and Signals 1Documento4 pagineLinear Dynamic Systems and Signals 1isma8070% (2)

- Multisim Unsolved Questions BITS PilaniDocumento2 pagineMultisim Unsolved Questions BITS Pilanimanish_genus100% (1)

- Chapter 13Documento56 pagineChapter 13mansoor.ahmed100Nessuna valutazione finora

- UMC 180nm MM RF FDK CDN Userguide VB04 PB 3Documento260 pagineUMC 180nm MM RF FDK CDN Userguide VB04 PB 3VLSISD36 Edwin DominicNessuna valutazione finora

- Self Biased High Performance Folded Cascode Cmos OpampDocumento6 pagineSelf Biased High Performance Folded Cascode Cmos OpampArvind MishraNessuna valutazione finora

- Shift Registers: Socketed 74LS164 8-Bit Shift Register ChipDocumento46 pagineShift Registers: Socketed 74LS164 8-Bit Shift Register Chipangelgalaxylife87Nessuna valutazione finora

- EE271 Lab1 Group06Documento9 pagineEE271 Lab1 Group06Lê Vương TháiNessuna valutazione finora

- Adders and MultipliersDocumento59 pagineAdders and Multipliersdbanbumani_501791840Nessuna valutazione finora

- DOST-ASTI Electric Manual PDFDocumento17 pagineDOST-ASTI Electric Manual PDFJB NavarroNessuna valutazione finora

- Introduction of Cadence ToolsDocumento18 pagineIntroduction of Cadence ToolsLeo AzNessuna valutazione finora

- (EE332) (09ECE) (Group13) Report ProjectDocumento23 pagine(EE332) (09ECE) (Group13) Report ProjectNgô ĐạtNessuna valutazione finora

- Introduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)Documento27 pagineIntroduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)TygerYashanshuNessuna valutazione finora

- Chapter SixDocumento5 pagineChapter Sixyunus memonNessuna valutazione finora

- Voltage ComparatorDocumento4 pagineVoltage ComparatorAmit RanjanNessuna valutazione finora

- REPORTLAB3 Ee271Documento12 pagineREPORTLAB3 Ee271Như TríNessuna valutazione finora

- Tanner EDA VLSI Project Lab 1Documento9 pagineTanner EDA VLSI Project Lab 1MohamedNessuna valutazione finora

- Syndrome DecodingDocumento4 pagineSyndrome DecodingStephenPengNessuna valutazione finora

- Derivation of The Threshold VoltageDocumento3 pagineDerivation of The Threshold VoltageRoobert01Nessuna valutazione finora

- Frequency Domain Filtering Image ProcessingDocumento24 pagineFrequency Domain Filtering Image ProcessingSankalp_Kallakur_402100% (1)

- Ecl 203 MCQDocumento3 pagineEcl 203 MCQresham k vNessuna valutazione finora

- Microprocessors & Interfacing Lab ManualDocumento30 pagineMicroprocessors & Interfacing Lab Manualjeravi84100% (1)

- Integrators, Differentiators, and Simple Filters: 6. PrelabDocumento15 pagineIntegrators, Differentiators, and Simple Filters: 6. PrelabMIn LeNessuna valutazione finora

- ECE 271 Lab 1 An Introduction To Modeling, Verilog, and Real World Digital PartsDocumento20 pagineECE 271 Lab 1 An Introduction To Modeling, Verilog, and Real World Digital PartsBin BinNessuna valutazione finora

- Vlsi Mini ProjectDocumento25 pagineVlsi Mini Projectjagadeesh100% (1)

- Cmos LayoutDocumento13 pagineCmos LayoutshastryNessuna valutazione finora

- Microprocessor All Experiment IT PDFDocumento22 pagineMicroprocessor All Experiment IT PDFSuraj KumarNessuna valutazione finora

- EMPro Workshop - Module1 - Introduction Version 2.0Documento11 pagineEMPro Workshop - Module1 - Introduction Version 2.0Jagan RajagopalanNessuna valutazione finora

- MPMC Lab Manual 15-11-2016Documento139 pagineMPMC Lab Manual 15-11-2016k padmavathiNessuna valutazione finora

- Basic Operations On Signals PDFDocumento8 pagineBasic Operations On Signals PDFNaveen DuraNessuna valutazione finora

- EE332 - Lab2 - Group 5 - Tang Anh TuanDocumento22 pagineEE332 - Lab2 - Group 5 - Tang Anh TuanTran TuNessuna valutazione finora

- 3 - CMOS InverterDocumento32 pagine3 - CMOS Inverterroxy8marie8chanNessuna valutazione finora

- Digital Communication Systems: ECE-4001 TASK-3Documento12 pagineDigital Communication Systems: ECE-4001 TASK-3Aniket SaxenaNessuna valutazione finora

- Vi Sem Ece Simulation Practical Lab Manual (Diploma "L" Scheme Lab Manual) S.No Name of The Experiment Page NoDocumento24 pagineVi Sem Ece Simulation Practical Lab Manual (Diploma "L" Scheme Lab Manual) S.No Name of The Experiment Page Nobiswajit7sarkarNessuna valutazione finora

- Eitf35: Introduction To Questasim: Steffen Malkowsky Steffen - Malkowsky@Eit - Lth.SeDocumento11 pagineEitf35: Introduction To Questasim: Steffen Malkowsky Steffen - Malkowsky@Eit - Lth.SeEswaran SamyNessuna valutazione finora

- BS Lab ManualDocumento76 pagineBS Lab ManualWasim100% (1)

- HDL Manual 2020 5th Sem E&CE 18ECL58Documento74 pagineHDL Manual 2020 5th Sem E&CE 18ECL58vishvakiranaNessuna valutazione finora

- Question Bank Fundamentals of CMOS VLSI-10EC56 15-16Documento10 pagineQuestion Bank Fundamentals of CMOS VLSI-10EC56 15-16Pranav KpNessuna valutazione finora

- Speed Control of DC Motor Using MicrocontrollerDocumento5 pagineSpeed Control of DC Motor Using MicrocontrollerVenkatesan SwamyNessuna valutazione finora

- What Are The Advantages and Disadvantages of The FinFET TechnologyDocumento3 pagineWhat Are The Advantages and Disadvantages of The FinFET TechnologySajan BeheraNessuna valutazione finora

- Tutorial 1 Drawing A Transistor Sensing CircuitDocumento7 pagineTutorial 1 Drawing A Transistor Sensing CircuitFernando ValenteNessuna valutazione finora

- Design and Implementation of FIR Filter Based On Dual Quality Compressor Based Multipliers With MFADocumento24 pagineDesign and Implementation of FIR Filter Based On Dual Quality Compressor Based Multipliers With MFAKushal MalhotraNessuna valutazione finora

- Reg - No:18BEC0175 ECE 3002 VLSI System Design Task. No: 05Documento11 pagineReg - No:18BEC0175 ECE 3002 VLSI System Design Task. No: 05Kotha Hemanth100% (1)

- Vlsi Lab ManualDocumento26 pagineVlsi Lab ManualAnirban Das DebNessuna valutazione finora

- Ece526manual F 2014Documento62 pagineEce526manual F 2014om007Nessuna valutazione finora

- Ec8361-Adc Lab ManualDocumento118 pagineEc8361-Adc Lab ManualmuminthajNessuna valutazione finora

- Fault Diagnosis OverviewDocumento54 pagineFault Diagnosis OverviewRASHMI RNessuna valutazione finora

- Ripple Carry Adder CircuitDocumento10 pagineRipple Carry Adder CircuitniteshNessuna valutazione finora

- 3 Pipelining and Parallel ProcessingDocumento34 pagine3 Pipelining and Parallel ProcessingRaghunandan KomandurNessuna valutazione finora

- PMOS, NMOS and CMOS Transmission Gate Characteristics.Documento13 paginePMOS, NMOS and CMOS Transmission Gate Characteristics.Prajwal KhairnarNessuna valutazione finora

- Solution Gates 2 SamplesDocumento9 pagineSolution Gates 2 SamplesluqmansulymanNessuna valutazione finora

- Vlsi Lab 1Documento11 pagineVlsi Lab 1Shawon karmokar JotyNessuna valutazione finora

- VLSI I - V CharacteristicsDocumento46 pagineVLSI I - V CharacteristicsMALATHI .LNessuna valutazione finora

- DSPAA Jan 2019 QP SolutionDocumento34 pagineDSPAA Jan 2019 QP SolutionAbhishek SinghNessuna valutazione finora

- 2 Bit Comparator PDFDocumento12 pagine2 Bit Comparator PDFSunith CkNessuna valutazione finora

- Amplitude Modulation and DemodulationDocumento3 pagineAmplitude Modulation and DemodulationRaj Mehra MeharNessuna valutazione finora

- ADC and DAC PDFDocumento23 pagineADC and DAC PDFMahendraLiyanageNessuna valutazione finora

- ECE429 Laboratory 2 Inverter Schematic: Prasanna Nalawar A20489739 21/09/2021Documento14 pagineECE429 Laboratory 2 Inverter Schematic: Prasanna Nalawar A20489739 21/09/2021Prasanna NalawarNessuna valutazione finora

- ECE429 Laboratory 3 Inverter Layout: Prasanna N A20489739 21/09/2021Documento14 pagineECE429 Laboratory 3 Inverter Layout: Prasanna N A20489739 21/09/2021Prasanna NalawarNessuna valutazione finora

- EE5311-Digital IC Design: Module 1 - The TransistorDocumento43 pagineEE5311-Digital IC Design: Module 1 - The TransistorAnmol SinhaNessuna valutazione finora

- CMOS Inverter: DC Analysis: by Dr.S.Rajaram, Thiagarajar College of EngineeringDocumento8 pagineCMOS Inverter: DC Analysis: by Dr.S.Rajaram, Thiagarajar College of EngineeringNIKHIL GOWDANessuna valutazione finora

- ps1 03 SolDocumento17 pagineps1 03 SolSeshareddy KatamNessuna valutazione finora

- Chapter 2Documento47 pagineChapter 2Hussein HasenNessuna valutazione finora

- Implement Logic Using Cmos GatesDocumento51 pagineImplement Logic Using Cmos GatesPranav DarganNessuna valutazione finora

- DRCDocumento16 pagineDRCdharma_panga8217Nessuna valutazione finora

- EL2043 L09 Rangkaian LogikaDocumento103 pagineEL2043 L09 Rangkaian LogikaDian Asfriany NurfalahNessuna valutazione finora

- Power Dissipation DerivationDocumento11 paginePower Dissipation DerivationHarshal AmbatkarNessuna valutazione finora

- Chap7-Complementary MOS (CMOS) Logic DesignDocumento54 pagineChap7-Complementary MOS (CMOS) Logic DesignMạnh Cường TrầnNessuna valutazione finora

- 4-45nm SRAM Technology Development and Technology Lead VehicleDocumento12 pagine4-45nm SRAM Technology Development and Technology Lead VehicleRohit BhelkarNessuna valutazione finora

- CMOS InverterDocumento24 pagineCMOS InverterM. Bilal NoorNessuna valutazione finora

- DelayDocumento31 pagineDelayvarun186Nessuna valutazione finora

- DEC50143 Cmos Ic Design & Fabrication: Department of Electrical EngineeringDocumento3 pagineDEC50143 Cmos Ic Design & Fabrication: Department of Electrical Engineeringnurul syahiraNessuna valutazione finora

- Inverter Design: Compiled By: Prof.R.K.LambaDocumento118 pagineInverter Design: Compiled By: Prof.R.K.LambaSamir TrivediNessuna valutazione finora

- Ese 570 Mos Inverters Static Characteristics: Kenneth R. Laker, University of Pennsylvania, Updated 13feb12 1Documento44 pagineEse 570 Mos Inverters Static Characteristics: Kenneth R. Laker, University of Pennsylvania, Updated 13feb12 1het shahNessuna valutazione finora

- Dec50143 - Cmos Integrated Circuit Design & FabricationDocumento54 pagineDec50143 - Cmos Integrated Circuit Design & FabricationKohilan VenugopalNessuna valutazione finora

- SRM Valliammai Engineering College: Department of Electronics and Communication EngineeringDocumento11 pagineSRM Valliammai Engineering College: Department of Electronics and Communication EngineeringRamaNessuna valutazione finora

- TelegramDocumento20 pagineTelegramVani telluriNessuna valutazione finora

- Dac PDFDocumento7 pagineDac PDFsanthoshNessuna valutazione finora

- Sample ThesisDocumento12 pagineSample ThesisPioNessuna valutazione finora

- The Cmos Inverter: Jayson C. LoretoDocumento9 pagineThe Cmos Inverter: Jayson C. LoretoBjun Curada LoretoNessuna valutazione finora

- Cadence Handout v3 (OTA)Documento34 pagineCadence Handout v3 (OTA)Minu PriyaNessuna valutazione finora

- A GmId Based Methodology For Designing Common Source AmplifierDocumento4 pagineA GmId Based Methodology For Designing Common Source Amplifierhuaguo wangNessuna valutazione finora

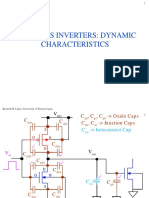

- Ee 560 Mos Inverters: Dynamic CharacteristicsDocumento41 pagineEe 560 Mos Inverters: Dynamic CharacteristicssallyNessuna valutazione finora

- 09 - Tan Hui ShanDocumento88 pagine09 - Tan Hui ShanMouawia ElazeebiNessuna valutazione finora

- CA5260, CA5260A: FeaturesDocumento7 pagineCA5260, CA5260A: FeaturesCharbel TadrosNessuna valutazione finora

- An On-Chip, Interconnect Capacitance Characterization Method With Sub-Femto-Farad ResolutionDocumento7 pagineAn On-Chip, Interconnect Capacitance Characterization Method With Sub-Femto-Farad ResolutionAlex WongNessuna valutazione finora

- Jothi2018 PDFDocumento32 pagineJothi2018 PDFAnonymous 9ADKGscJOqNessuna valutazione finora