Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

EE141 s09 Hw10 Solution

Caricato da

Ahmed AliCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

EE141 s09 Hw10 Solution

Caricato da

Ahmed AliCopyright:

Formati disponibili

UNIVERSITY OF CALIFORNIA College of Engineering Department of Electrical Engineering and Computer Sciences

Jan M. Rabaey Homework #10

(Optional)

EECS 141

Problem 1 Variable Block Carry Bypass Adder (from S06 HW)

Consider a 24-bit, 6 stage carry-bypass adder with the following delays: tsetup=4, tcarry=1, tsum=4, tbypass=2

a) Identify the critical path through the adder. List the delays for each block along the critical path and give the total delay. Assume that each stage bypasses the same number of bits. The critical path is through the setup of the first stage (specifically, the first bit of the first stage), through all four bits of the first stages carry chain, through the first five bypass multiplexers, three bits of the last stages carry chain, then through the final stages sum. The last carry bit of the final stage does not affect the sum, only the carry out. Carry out through the final multiplexer is not on the critical path as the sum is slower. The delays for each component of this are tsetup, 4tcarry, 3tbypass +2tbypass, 3tcarry, and tsum respectively. These add up to the expression given in equation 11.9 in the text, and substituting the given delays gives a total of 25. The critical path is grayed in figure 1114. b) Consider the setup delay and carry propagation of the second and third stages. These are not on the critical path and can be made slower without affecting performance. If we allow each stage to handle a different number of bits, what is the relationship between the number of bits per stage and the respective carry propagation delay? How many bits would you assign to each of the first three stages to minimize the delay from inputs to the carry output for the first 12 bits of the adder? The worst case delay from the first stages inputs through the setup, carry propagation and bypass to the start of the fourth stage is

tsetup + M0*tcarry + 3tbypass where M0 is the number of bits in the first stage. The delay for the second and third stages are similarly tsetup + M1*tcarry + 2tbypass and tsetup + M2*tcarry + tbypass Making all of these equal, we get that M1- M0 = M2 M1 = tbypass/tcarry = 2. Thus, the first, second, and third stages should add 2, 4 and 6 bits respectively. The original critical path is now 2 carries shorter, for a total delay of 23 at the final sum output (it is also acceptable to just give the delay to the end of the third stage carry being now 12 instead of 14). The second and third stages are now also critical paths as well, with the same delay. c) How many bits would you assign to each stage in the second half of the adder? What is/are the delays along the critical path(s) now? Same approach as for part b, except the critical paths are now from the carry in from the third stage, to the sum outputs. Delays for each path are: 2tbypass + (M5-1)tcarry + tsum tbypass + (M4-1)tcarry + tsum (M3-1)tcarry + tsum Making all of these equal, we get that M4- M5 = M3 M4 = tbypass/tcarry = 2. Thus, the fourth, fifth and sixth stages should add 6, 4 and 2 bits respectively. The critical path to the final stage sum output is now another 2 carries shorter, for a total delay of 21. The fourth and fifth stage outputs are now also critical paths. Note: parts a and c assumed that the sum logic for a bit has a delay of tsum from its carry in to the sum out. From the structure of the mirror adder, one might consider tsum to refer to the delay from the bits own carry to its output, in which case the critical path delays would have one extra tcarry. (M instead of M-1) This does not affect the choice of stage widths and is acceptable for the answers.

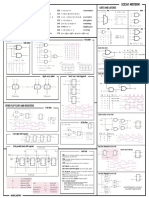

Problem 2 Conditional Sum Adder (from F06 HW)

Here is a neat adder structure called the conditional sum adder. Shown below is a 4-bit version of the circuit. Note that in the diagram, multiplexors are represented by switch-controlled arrows.

Using a pass-transistor implementation, the circuit schematic for each adder cell can be:

a)

Derive Boolean equations for the four outputs of the one-bit conditional adder cell

S0 = A B

C0 = AB

S1 = (A B) C1 = A + B

b) Derive an expression for the propagation delay of the adder as a function of the number of Bits, N. Assume that the delay through each conditional cell is tcell and that the delay of a MUX is tMUX.

Basically, we need an additional level of multiplexors every time we double the number of bits. Soin the worst-case critical path, we must pass the carry-out from the leastsignificant bit all the way to the most-significant bit, which means that we must go through each MUX level. # of levels = log2 N. On top of that, we always need to calculate C0/C1 and S0/S1, so we have one cell delay.

Delay = tcell + log2 N tMUX

Potrebbero piacerti anche

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (894)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- ICC Tutorial PDFDocumento21 pagineICC Tutorial PDFÆshok IncreĐible KingNessuna valutazione finora

- Digital Electronics - 2 Marks With Answers PDFDocumento40 pagineDigital Electronics - 2 Marks With Answers PDFMANJU C S100% (22)

- DIgital Electronics Lab Exam Viva QuestionsDocumento6 pagineDIgital Electronics Lab Exam Viva Questionsmehek saba100% (19)

- Microelectronics and Computer Systems Laboratory, Mcgill University 3480 University Street, Montreal, Quebec, Canada H3A 2A7Documento10 pagineMicroelectronics and Computer Systems Laboratory, Mcgill University 3480 University Street, Montreal, Quebec, Canada H3A 2A7Ahmed AliNessuna valutazione finora

- 1.9 GHZ OscillatorDocumento4 pagine1.9 GHZ OscillatorAhmed AliNessuna valutazione finora

- Verilog ADocumento170 pagineVerilog Aaminkhan83Nessuna valutazione finora

- A Methodology For The Offset-Simulation of ComparatorsDocumento7 pagineA Methodology For The Offset-Simulation of ComparatorsAhmed AliNessuna valutazione finora

- Directional CouplerDocumento4 pagineDirectional CouplerAhmed AliNessuna valutazione finora

- IQ MismacthDocumento6 pagineIQ MismacthAhmed AliNessuna valutazione finora

- 10 1 1 111Documento222 pagine10 1 1 111Rafael Della GiustinaNessuna valutazione finora

- Directional CouplersDocumento14 pagineDirectional CouplersAhmed AliNessuna valutazione finora

- Directional CouplerDocumento4 pagineDirectional CouplerAhmed AliNessuna valutazione finora

- Scaling Rules For Thin Film Optical Waveguide (Slab WG) PDFDocumento6 pagineScaling Rules For Thin Film Optical Waveguide (Slab WG) PDFAhmed AliNessuna valutazione finora

- Directional CouplerDocumento4 pagineDirectional CouplerAhmed AliNessuna valutazione finora

- University of Massachusetts Dept. of Electrical & Computer EngineeringDocumento26 pagineUniversity of Massachusetts Dept. of Electrical & Computer EngineeringAhmed AliNessuna valutazione finora

- TCL TutorialDocumento30 pagineTCL TutorialAhmed AliNessuna valutazione finora

- An Introduction To MEMSDocumento56 pagineAn Introduction To MEMSAhmed AliNessuna valutazione finora

- Cadence ManualDocumento51 pagineCadence Manualapi-27099960100% (4)

- ModelSim TutorialDocumento9 pagineModelSim TutorialShailesh Raj AryanNessuna valutazione finora

- 06ESL38 - Logic Design Lab1Documento76 pagine06ESL38 - Logic Design Lab1Sachin S ShettyNessuna valutazione finora

- FPGA Based System Design: Gate Level ModelingDocumento11 pagineFPGA Based System Design: Gate Level Modelingwaleed umerNessuna valutazione finora

- Low Power Logic StyleDocumento12 pagineLow Power Logic Stylergangadhar049236Nessuna valutazione finora

- DLC Unit 2Documento69 pagineDLC Unit 2kkr kkrNessuna valutazione finora

- ECE 279 Exp. 1 To Exp 10Documento29 pagineECE 279 Exp. 1 To Exp 10Shruti KumariNessuna valutazione finora

- AluDocumento10 pagineAluAbhishek PatraNessuna valutazione finora

- Arithmetic Circuits: Digital Electronics Bca Sem Ii JimsDocumento57 pagineArithmetic Circuits: Digital Electronics Bca Sem Ii Jimsdinesh sharmaNessuna valutazione finora

- EE331L Experiment #3 Adders and Subtractors: Written By: Shehab Alaa Ramadan Group: C University ID Number: 022180589Documento6 pagineEE331L Experiment #3 Adders and Subtractors: Written By: Shehab Alaa Ramadan Group: C University ID Number: 022180589Shehab RamadanNessuna valutazione finora

- Arithmetic Logic Unit (ALU) : CSE320 Lecture 6Documento5 pagineArithmetic Logic Unit (ALU) : CSE320 Lecture 6Richie ChanNessuna valutazione finora

- USM Digital Electronics - Adder and Flip-Flop CircuitsDocumento8 pagineUSM Digital Electronics - Adder and Flip-Flop CircuitsCogCoilNessuna valutazione finora

- Project DLDDocumento14 pagineProject DLDAhmed Razi UllahNessuna valutazione finora

- High Speed RNS-To-Binary Converter DesignDocumento6 pagineHigh Speed RNS-To-Binary Converter DesignAugus AngelNessuna valutazione finora

- ELL201 L10 9sep21 1631069415511Documento73 pagineELL201 L10 9sep21 1631069415511Keshav SinglaNessuna valutazione finora

- Designing of Alu Using Verilog HDLDocumento2 pagineDesigning of Alu Using Verilog HDLPriyanka KumariNessuna valutazione finora

- Efficient CVSL Based Full Adder Realizations: Kirti Gupta', Shrey Bagga2 and Neeta PandelDocumento5 pagineEfficient CVSL Based Full Adder Realizations: Kirti Gupta', Shrey Bagga2 and Neeta PandelsallyNessuna valutazione finora

- Design and Implementation of High Frequency 16-Bit Full Adder On FPGA FamiliesDocumento7 pagineDesign and Implementation of High Frequency 16-Bit Full Adder On FPGA Familiesnikhilreddy522002Nessuna valutazione finora

- VHDL Experiments ListDocumento1 paginaVHDL Experiments ListPankul BansalNessuna valutazione finora

- EPM240 DatasheetDocumento102 pagineEPM240 DatasheetLong VũNessuna valutazione finora

- CS3351 Unit WISE Question BankDocumento12 pagineCS3351 Unit WISE Question BankkaviyaNessuna valutazione finora

- ECE241 MIDTERM BOOLEAN ALGEBRA AND GATESDocumento2 pagineECE241 MIDTERM BOOLEAN ALGEBRA AND GATESNandini JayakumarNessuna valutazione finora

- DDE 1313 Digital Electronics 1 LODocumento6 pagineDDE 1313 Digital Electronics 1 LOAhmad FadzlyNessuna valutazione finora

- JSS Academy Technical Education Approximate Multiplier DesignDocumento28 pagineJSS Academy Technical Education Approximate Multiplier DesignSupriya GPNessuna valutazione finora

- MCQ Bank for Digital Logic & DesignDocumento19 pagineMCQ Bank for Digital Logic & DesignImran KhanNessuna valutazione finora

- Digital Fundamentals: FloydDocumento33 pagineDigital Fundamentals: FloydadilNessuna valutazione finora

- Ripple Carry Adder ExperimentDocumento10 pagineRipple Carry Adder ExperimentAnkit VermaNessuna valutazione finora

- 01 PM 072008002900001Documento78 pagine01 PM 072008002900001Om BhosaleNessuna valutazione finora

- Unit 1 and 2. DfaDocumento43 pagineUnit 1 and 2. DfaVanchima Devi0% (1)

- HCF4008Documento13 pagineHCF4008jnax101Nessuna valutazione finora