Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Lab3 SimpleMIPS

Caricato da

Tiến Thành0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

15 visualizzazioni3 pagineFor this lab3, you are to design a simple 32-bit MIPS Single-Cycle CPU. The CPU instructions to be implemented are LW, SW, J, JR, BNE, XORI, ADD, SUB, and SLT. To demonstrate that your CPU actually works, you will need to set things up so that all the registers used in the benchmarks are displayed at the end of the execution.

Descrizione originale:

Titolo originale

lab3_SimpleMIPS

Copyright

© Attribution Non-Commercial (BY-NC)

Formati disponibili

DOC, PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoFor this lab3, you are to design a simple 32-bit MIPS Single-Cycle CPU. The CPU instructions to be implemented are LW, SW, J, JR, BNE, XORI, ADD, SUB, and SLT. To demonstrate that your CPU actually works, you will need to set things up so that all the registers used in the benchmarks are displayed at the end of the execution.

Copyright:

Attribution Non-Commercial (BY-NC)

Formati disponibili

Scarica in formato DOC, PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

15 visualizzazioni3 pagineLab3 SimpleMIPS

Caricato da

Tiến ThànhFor this lab3, you are to design a simple 32-bit MIPS Single-Cycle CPU. The CPU instructions to be implemented are LW, SW, J, JR, BNE, XORI, ADD, SUB, and SLT. To demonstrate that your CPU actually works, you will need to set things up so that all the registers used in the benchmarks are displayed at the end of the execution.

Copyright:

Attribution Non-Commercial (BY-NC)

Formati disponibili

Scarica in formato DOC, PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 3

Computer Organization and Microprocessor Semester 2 2012-2013 Danang University of Technology, Faculty of Electronics and Telecommunications Department of Computer

Engineering Prepared by Ho Viet Viet, Pham Xuan Trung, TT Minh Hanh and Nguyen Van Hieu

Lab3: Design a MIPS 32-bit Single-Cycle CPU

Lab Objectives: For this lab3 you are to design a simple 32-bit MIPS Single-Cycle CPU. The CPU instructions to be implemented are LW, SW, J, JR, BNE, XORI, ADD, SUB, and SLT. Chapter 4 will give some examples of how architectures are put together, and will be useful as you design your own CPU. For this CPU, you will use your two previous lab projects (the register and the ALU) so you will need to have these fully functional before proceeding to work on your CPU. The data memory and instruction memory modules are provided in the files datamem.v and instrmem.v respectively. We also provide a bunch of test programs you can change the program loaded by editing the instr.dat string in instrmem.v. You are responsible for coming up with the top-level testbench for this assignment use previous labs testbenches as guidance. Please remember that the rules from lab1 are still in effect. Also, to demonstrate that your CPU actually works, you will need to set things up so that all the registers used in the benchmarks are displayed at the end of the execution. The easiest way to accomplish this is to look at the all lines inside your register file coming out of the DFF array in SignalScan (along with other relevant signals) and save a do-file. We strongly recommend this, even aside from the demonstration, as it will make debugging much simpler. Make sure that the clock in your testbench (1) is long enough so that all processing is done within this clock cycle (a VERY long clock is fine) (2) executes enough clock cycles for the program to finish. The control logic for your CPU can be done behaviorally. If you do this, you can show the control logic on your schematics as black boxes. You need to indicate how the control logic hooks to the rest of the CPU, but do not have to draw the logic for the control logic itself. Note that, although some of the benchmarks are particularly relevant to lab4, they ALL will run successfully on lab3, and you will be evaluated on whether your CPU works on any/all of them. Be sure to test ALL the benchmarks on your CPU. Instruction subset:

ADD rd, rs, rt: Reg[rd] = Reg[rs] + Reg[rt]. BNE rs, rt, imm16: if (Reg[rs] != Reg[rt]) PC = PC + 4 + Sign_ext(Imm16)<<2 else PC = PC + 4. For lab #4 (only) this instr. has a delay slot. J target: PC = { PC[31:28], target, 00 }. For lab #4 (only) this instr. has a delay slot. JR rs: PC = Reg[rs]. For lab #4 (only) this instr. has a delay slot. LW rt, imm16(rs): Reg[rt] = Mem[Reg[rs] + Sign_ext(Imm16)]. For lab #4 (only) the value in rt cannot be used in the next cycle. SLT rd, rs, rt: If (Reg[rs] < Reg[rt]) Reg[rd] = 0000000116 else Reg[rd] = 0000000016. SUB rd, rs, rt: Reg[rd] = Reg[rs] Reg[rt].

SW rt, imm16(rs): Mem[Reg[rs] + Sign_ext(Imm16)] = Reg[rt]. XORI rt, rs, imm16: Reg[rt] = Reg[rs] XOR Zero_ext(Imm16).

Page 2

Potrebbero piacerti anche

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Present Simple: SPEAKING: Interview Your Partner These QuestionsDocumento5 paginePresent Simple: SPEAKING: Interview Your Partner These QuestionsYen RitaNessuna valutazione finora

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Fce Writing Part 2 Short Stories ActivityDocumento7 pagineFce Writing Part 2 Short Stories Activityhenniebennie0% (1)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Shahmukhi To GrumkhiDocumento12 pagineShahmukhi To GrumkhiNasir Qayyum SarimNessuna valutazione finora

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- World Languages Committee BookletDocumento75 pagineWorld Languages Committee BookletmarthaNessuna valutazione finora

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Seminar 2Documento8 pagineSeminar 2Ульяна ХовановаNessuna valutazione finora

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- Latihan Narrative Text Kelas 9Documento2 pagineLatihan Narrative Text Kelas 9Dewi NurhaeniNessuna valutazione finora

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Wireless & Cellular Communication-18EC81: Prof - Priyanka L JCET Hubli ECEDocumento49 pagineWireless & Cellular Communication-18EC81: Prof - Priyanka L JCET Hubli ECEBasavaraj Raj100% (1)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Lesson Relative PronouneDocumento2 pagineLesson Relative Pronounedaloulasud30Nessuna valutazione finora

- Tintu Alphonsa Thomas Assistant Professor, CSE Amal Jyothi College of Engineering, KanjirappallyDocumento56 pagineTintu Alphonsa Thomas Assistant Professor, CSE Amal Jyothi College of Engineering, KanjirappallyalanjosephNessuna valutazione finora

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Exercise 7: Adverbs and AdjectivesDocumento12 pagineExercise 7: Adverbs and AdjectivesAnakpakcik AzizNessuna valutazione finora

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- MSFORMS Manual ENDocumento22 pagineMSFORMS Manual ENMayank AggarwalNessuna valutazione finora

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Adirs CFDS Aids (Ref.)Documento240 pagineAdirs CFDS Aids (Ref.)UditSharmaNessuna valutazione finora

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- Infografía Del P. Simple y ContinuoDocumento1 paginaInfografía Del P. Simple y ContinuoJorge Isaac Sánchez DíazNessuna valutazione finora

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- BGP Regular Expressions ExamplesDocumento2 pagineBGP Regular Expressions ExamplesSon Tran Hong NamNessuna valutazione finora

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- BC9180 Software Reference Guide (ENG)Documento56 pagineBC9180 Software Reference Guide (ENG)brasicanoNessuna valutazione finora

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Geographic, Linguistic, and Ethnic Dimensions of Philippine Literary HistoryDocumento26 pagineGeographic, Linguistic, and Ethnic Dimensions of Philippine Literary HistoryGemaris Laurenaria MercadoNessuna valutazione finora

- Quartiles in R PDFDocumento4 pagineQuartiles in R PDFwichastaNessuna valutazione finora

- Wonderware Alarm DB Logger Object For Wonderware Application Server User Guide Ver 1.x Rev 1.0 PR 00186Documento17 pagineWonderware Alarm DB Logger Object For Wonderware Application Server User Guide Ver 1.x Rev 1.0 PR 00186Dino PradanaNessuna valutazione finora

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- Macbeth Thesis GuiltDocumento4 pagineMacbeth Thesis Guiltfc47b206100% (1)

- Winitzki - No Distributional Limit For Delta Function of Complex ArgumentsDocumento2 pagineWinitzki - No Distributional Limit For Delta Function of Complex ArgumentswinitzkiNessuna valutazione finora

- 2012 - Fail-Over ClusteringDocumento34 pagine2012 - Fail-Over ClusteringAbdul KasimNessuna valutazione finora

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- Palmers Penmanship BudgetDocumento141 paginePalmers Penmanship BudgetVianney Rivera100% (1)

- CIGRE-130 Substation To Substation (Ss2ss) GOOSE Exchange For Critical Relay OperationsDocumento9 pagineCIGRE-130 Substation To Substation (Ss2ss) GOOSE Exchange For Critical Relay Operationsraghavendran raghuNessuna valutazione finora

- To Err Is Human To Forgive Is Divine EssayDocumento4 pagineTo Err Is Human To Forgive Is Divine Essayibnorvbaf100% (2)

- Sunil Gangopadhyay - Those Days - A Novel-Penguin Books LTD (2000) PDFDocumento668 pagineSunil Gangopadhyay - Those Days - A Novel-Penguin Books LTD (2000) PDFAbhijeet JhaNessuna valutazione finora

- 09 - Chapter2Documento81 pagine09 - Chapter2Kamalakkannan MuniappanNessuna valutazione finora

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Introduction de Mathura Meets VrindavanDocumento4 pagineIntroduction de Mathura Meets VrindavanCoco YogaNessuna valutazione finora

- How To Structure An English Literature EssayDocumento3 pagineHow To Structure An English Literature Essaymagician1050100% (1)

- Vocabulary in Context PowerpointDocumento47 pagineVocabulary in Context Powerpointhaneenlatif50% (2)

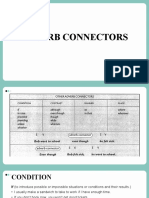

- Adverb ConnectorDocumento11 pagineAdverb ConnectorAges TiaraNessuna valutazione finora

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)