Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Multilevel Multiphase Space Vector PWM Algorithm Applied To Three-Phase Converters

Caricato da

Athiesh KumarDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Multilevel Multiphase Space Vector PWM Algorithm Applied To Three-Phase Converters

Caricato da

Athiesh KumarCopyright:

Formati disponibili

1

Multilevel Multiphase Space Vector PWM

Algorithm Applied to Three-Phase Converters

Oscar L opez, Jacobo

Alvarez, Jes us Doval-Gandoy, Francisco Freijedo, Andr es Nogueiras and Carlos M. Pe nalver

Electronics Technology Department

University of Vigo

Vigo, Spain ES-36210

Email: olopez@uvigo.es

AbstractMultilevel technology permits the achievement of

high power ratings with voltage limited devices. Recently a new

space vector pulse-width modulation algorithm for multilevel

multiphase voltage source converters with low computational

cost has been presented. This algorithm can be used with any

number of phases; therefore it can be also used with classical

three-phase topologies. In this paper, the multiphase algorithm

is particularized for three-phase converters and compared with

previous multilevel space vector modulation techniques. Finally,

the algorithm is implemented in a low cost FPGA and it is tested

in laboratory with a real prototype by using a neutral point

clamped inverter.

I. INTRODUCTION

Multilevel converters are becoming more and more popular

in power applications, thanks to their capability to meet the in-

creasing demand of power ratings and power quality associated

with reduced harmonic distortion and lower electromagnetic

interference. Voltage source multilevel inverter topologies [1],

[2] synthesize a voltage waveform from several voltage levels,

typically obtained from several capacitors or dc sources. By

increasing the number of levels in the inverter, the output

voltages have more steps generating a staircase waveform,

which has a reduced harmonic distortion. However, a larger

number of levels increase the number of devices that must be

controlled, and consequently the modulation complexity.

In order to solve the multilevel modulation problem various

pulse-width modulation (PWM) strategies have been devel-

oped and studied in detail such as multilevel sinusoidal PWM,

multilevel selective harmonic elimination and space vector

modulation. Among these strategies, the space vector PWM

(SVPWM) stands out because it offers signicant exibility to

optimize switching waveforms and it is well suited for digital

implementation. Complexity and computational cost of tradi-

tional SVPWM techniques increase with the number of levels

of the converter, and most of them use trigonometric functions

or precomputed tables [3], [4]. In [5], a two-dimensional (2D)

SVPWM algorithm that calculates the switching vectors and

the switching times without using angles, trigonometric func-

tions or precomputed tables was proposed. A tree-dimensional

(3D) SVPWM algorithm that generalizes this 2D algorithm for

This work was supported by the Spanish Ministry of Education and Science

under the project number ENE2006-02930.

systems with neutral wire was presented in [6]. Due to their

low computational cost both techniques are suitable for real-

time hardware implementation in low cost-devices [7]. In [8], a

generalized direct PWM method in which the switching states

and the pulse-width of each phase are directly determined in

terms of the normalized reference voltage vector is proposed.

It is proved that the modulation outputs of the direct algorithm

and the previous 3D SVPWM generalized algorithm [6] are

equivalent.

Recently, in [9], a new multiphase SVPWM technique

with low computational complexity, that makes it suitable for

real-time implementation in low-cost devices, was presented.

This new technique can be used with the standard multilevel

topologies such us diode-clamped, ying capacitor, cascaded

full-bridge or even hybrid converters. That new modulation

algorithm is valid for any number of phases and consequently

it can be applied to three-phase converters.

In this paper, the multilevel multiphase SVPWM algorithm

presented in [9] is particularized for three-phase converters.

The resulting algorithm is compared with previous space

vector modulation techniques. Finally, it is implemented in a

eld-programmable gate array (FPGA) and it is tested by using

a neutral point clamped (NPC) inverter feeding and induction

motor.

II. MULTILEVEL MULTIPHASE SVPWM ALGORITHM

In multiphase converters the space vector PWM is a mul-

tidimensional problem where the vector selection can be

carried out directly in a multidimensional space. In [9], the

modulation problem of a P-phase converter is formulated in a

P-dimension space and it is solved for multilevel topologies in

which the output level of every phase is an integer multiple of a

xed voltage step V

dc

, such as ying capacitor, diode-clamped,

cascaded full-bridge or hybrid converters. The solution is an

algorithm based on a displacement plus a two-level multiphase

SVPWM modulator that is valid for any number of levels

and phases. This multiphase modulation technique is able to

handle all switching states of the inverter, without discard any

one, and it provides a sorted switching vector sequence that

minimizes the number of switchings. In addition, the algorithm

proves suitable for real-time implementation due to its low

computational complexity.

2

Since the switching states of any power converter topology

stay at discrete states, the multilevel multiphase SVPWM

technique is used to synthesize a reference voltage vector V

r

by means of a sequence of space vectors during each modu-

lation cycle. Each space vector v

sj

must be applied during an

interval t

j

in accordance with the following modulation law:

v

r

=

P+1

j=1

v

sj

t

j

where

P+1

j=1

t

j

= 1 (1)

in which

v

r

=

V

r

V

dc

= [v

r

1

, v

r

2

, . . . , v

r

P

]

T

(2)

is the normalized reference vector, which belongs to the P-

dimension real space R

P

, v

sj

= [v

s

1

j

, v

s

2

j

, . . . , v

s

P

j

]

T

are the

switching vectors, which belongs to the integer space Z

P

, and

t

j

are the normalized switching times that correspond to each

switching vector.

If expressions in (1) are rewritten in matrix format the

following system of linear equations, which must be solved

by the multilevel multiphase SVPWM algorithm, is obtained:

_

_

1

v

r

1

v

r

2

.

.

.

v

r

P

_

_

=

_

_

1 1 . . . 1

v

s

1

1

v

s

1

2

. . . v

s

1

P+1

v

s

2

1

v

s

2

2

. . . v

s

2

P+1

.

.

.

.

.

.

.

.

.

.

.

.

v

s

P

1

v

s

P

2

. . . v

s

P

P+1

_

_

_

_

t

1

t

2

.

.

.

t

P+1

_

_

. (3)

The modulation problem solving requires searching a set of

integer numbers for the coefcients matrix that permit to solve

the linear system in order to calculate the switching times.

As Fig. 1 shows, if the reference vector, v

r

, is decomposed

in the sum of an integer, v

i

, and a fractional part, v

f

, as

v

i

= integ(v

r

) Z

P

(4)

v

f

= v

r

v

i

R

P

(5)

then the modulation law in (3) can be solved by means of a

two-level multiphase modulator where the reference vector is

v

f

:

_

_

1

v

f

1

v

f

2

.

.

.

v

f

P

_

_

=

_

_

1 1 . . . 1

v

d

1

1

v

d

1

2

. . . v

d

1

P+1

v

d

2

1

v

d

2

2

. . . v

d

2

P+1

.

.

.

.

.

.

.

.

.

.

.

.

v

d

P

1

v

d

P

2

. . . v

d

P

P+1

_

_

_

_

t

1

t

2

.

.

.

t

P+1

_

_

. (6)

The solution of this new system of equations is the sequence of

displaced switching vectors, v

dj

= [v

d

1

, v

d

2

, . . . , v

d

P

]

T

, that

approximate the reference v

f

. The elements of the multilevel

switching sequence, v

sj

, can be obtained from this two-level

switching sequence by adding the integer part of the reference

to the displaced vectors:

v

sj

= v

i

+v

dj

. (7)

The switching times t

j

of the multilevel algorithm are the

same as the switching times of the two-level algorithm.

SVPWM

two-levels

P-phases

SVPWM

N-levels

P-phases

integ

Fig. 1. Block diagram of the multilevel multiphase SVPWM.

SVPWM

2-levels

P-phases

Fig. 2. Block diagram of the two-level multiphase SVPWM.

Fig. 2 shows the block diagram of the two-level multiphase

space vector PWM algorithm. This algorithm searches a

coefcient matrix

D =

_

_

1 1 . . . 1

v

d

1

1

v

d

1

2

. . . v

d

1

P+1

v

d

2

1

v

d

2

2

. . . v

d

2

P+1

.

.

.

.

.

.

.

.

.

.

.

.

v

d

P

1

v

d

P

2

. . . v

d

P

P+1

_

_

(8)

that permits to solve the linear system in (6) in order to

calculate the switching times. This matrix can be calculated

by means of

D = P

T

D (9)

where

D =

_

_

1 1 1 . . . 1

1 1 . . . 1

.

.

.

.

.

.

.

.

.

.

.

.

1

0 1

_

_

(10)

and P is a permutation matrix that sorts the elements of the

reference vector v

f

in descending order:

P

_

1

v

f

_

=

_

1

v

f

_

(11)

where v

f

= [ v

f

1

, v

f

2

, . . . , v

f

P

]

T

is the sorted vector in which

1 > v

f

1

v

f

k1

v

f

k

v

f

P

0. (12)

3

Decompose

the reference

Generate

trigger signals

Normalize

the reference

Sort the fractional

part of the reference

Rearrage columns

of the matrix D

Extract displaced

switching vectors

Calculate

switching vectors

Calculate

switching times

SVPWM

2-levels

P-phases

SVPWM

N-levels

P-phases

Fig. 3. Multilevel multiphase SVPWM algorithm ow chart.

Finally, the switching times can be calculated from v

f

as

t

j

=

_

_

1 v

f

1

, if j = 1

v

f

j1

v

f

j

, if 2 j P

v

f

P

, if j = P + 1.

(13)

The steps of this algorithm, which are summarized in the

ow chart in Fig. 3, are:

1) Calculate normalized reference, v

r

, from the reference

voltage vector using the expression in (2).

2) Decompose the normalized reference into the sum of its

integer part, v

i

, and its fractional part, v

f

, by means of

(4) and (5) respectively.

3) Calculate the permutation matrix P that sorts the vector

v

f

in descending order in accordance with (11) and (12).

4) Rearrange the rows of the triangular matrix

D in order

to obtain the matrix D by means of (9).

5) Extract the displaced switching vectors, v

dj

, from the

matrix D by taking into account the expression in (8).

6) Obtain the nal switching vectors, v

sj

, by adding the

integer part of the reference, v

i

, to the displaced switch-

ing vectors v

dj

according to (7).

7) Calculate the time corresponding to each switching

vector from components of the vector v

f

by means of

expression in (13).

Finally, trigger signals have to be generated from the switching

vectors and the switching times. The relationship between

switching states and the particular trigger signals of transistors

depends on the multilevel topology [10].

III. ALGORITHM APPLICATION TO THREE-PHASE

CONVERTERS

The modulation algorithm for three-phase systems is ob-

tained making P = 3 in the multiphase algorithm. Therefore,

in three-phase converters, the modulation problem is formu-

lated in a three-dimension space and the switching states are

three-dimension integer vectors:

v

s

= [v

s

a

, v

s

b

, v

s

c

]

T

Z

3

. (14)

And taking into account (2), the normalized voltage reference,

v

r

, is the three-dimension real vector:

v

r

=

V

r

V

dc

= [v

r

a

, v

r

b

, v

r

c

]

T

R

3

(15)

where V

dc

is the voltage step of the multilevel converter.

In accordance with (4) and (2), the integer and fractional

parts of the reference vector are

v

i

= integ(v

r

) = [v

i

a

, v

i

b

, v

i

c

]

T

Z

3

(16)

v

f

= v

r

v

i

= [v

f

a

, v

f

b

, v

f

c

]

T

R

3

. (17)

From v

f

, the permutation matrix, P, can be determined by

testing the following three logical conditions:

C

ab

= [v

f

a

v

f

b

]

C

bc

= [v

f

b

v

f

c

]

C

ca

= [v

f

c

v

f

a

].

(18)

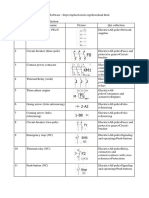

Table I shows the relationship between the results of these

three conditions and the permutation matrix P. Cases 000 and

111 are not coherent, therefore there are only six different

situations that must be taken into account.

Next, the matrix D is calculated from the upper triangular

matrix

D by means of (9) as

D = P

T

_

_

1 1 1 1

0 1 1 1

0 0 1 1

0 0 0 1

_

_

. (19)

The sequence of displaced vectors {v

d1

, v

d2

, v

d3

, v

d4

} is

extracted from the matrix Dtaking into account the expression

in (8):

D =

_

_

1 1 1 1

v

d

a

1

v

d

a

2

v

d

a

3

v

d

a

4

v

d

b

1

v

d

b

2

v

d

b

3

v

d

b

4

v

d

c

1

v

d

c

2

v

d

c

3

v

d

c

4

_

_

(20)

From (7), the nal switching sequence is calculated adding

the integer part of the reference to the vectors of the displaced

switching sequence:

v

s1

= v

i

+v

d1

v

s2

= v

i

+v

d2

v

s3

= v

i

+v

d3

v

s4

= v

i

+v

d4

.

Finally, the time corresponding to each switching vector is

calculated directly from the components of v

f

by means of

4

TABLE I

PERMUTATION MATRIX

C

ab

C

bc

C

ca

Ordered vector v

f

Matrix P

0 0 1

v

f

a

= v

f

c

v

f

b

= v

f

b

v

f

c

= v

f

a

_

_

1 0 0 0

0 0 0 1

0 0 1 0

0 1 0 0

_

_

0 1 0

v

f

a

= v

f

b

v

f

b

= v

f

a

v

f

c

= v

f

c

_

_

1 0 0 0

0 0 1 0

0 1 0 0

0 0 0 1

_

_

0 1 1

v

f

a

= v

f

b

v

f

b

= v

f

c

v

f

c

= v

f

a

_

_

1 0 0 0

0 0 1 0

0 0 0 1

0 1 0 0

_

_

1 0 0

v

f

a

= v

f

a

v

f

b

= v

f

c

v

f

c

= v

f

b

_

_

1 0 0 0

0 1 0 0

0 0 0 1

0 0 1 0

_

_

1 0 1

v

f

a

= v

f

c

v

f

b

= v

f

a

v

f

c

= v

f

b

_

_

1 0 0 0

0 0 0 1

0 1 0 0

0 0 1 0

_

_

1 1 0

v

f

a

= v

f

a

v

f

b

= v

f

b

v

f

c

= v

f

c

_

_

1 0 0 0

0 1 0 0

0 0 1 0

0 0 0 1

_

_

(13) as

t

1

= 1 v

f

a

t

2

= v

f

a

v

f

b

t

3

= v

f

b

v

f

c

t

4

= v

f

c

.

If the modulation problem is solved in all the six possible

cases in Table I then the results shown in Table II are obtained.

This table proves the application of the multiphase algorithm

to a three-phase system is very simple. After normalize the

reference vector, it only requires three comparison operations

and a few simple additions in order to evaluate the switching

vectors and its corresponding switching times.

The simplicity of the new algorithm is here shown by means

of an example. Let us consider a three-phase drive where the

voltage reference for each phase is purely sinusoidal:

V

r

= A

_

_

sin(wt)

sin(wt + 2/3)

sin(wt 2/3)

_

_

.

If a voltage amplitude A = 285 V and a speed w = 2 50 rd/s

are considered, the instantaneous reference when t = 9 ms is

V

r

= [88, 279, 191]

T

V.

From (2), if voltage step of the converter is V

dc

= 150 V then

TABLE II

VECTOR SEQUENCE AND SWITCHING TIMES

C

ab

C

bc

C

ca

Vector sequence v

sj

Switching times t

j

0 0 1

v

s1

= v

i

+ [0, 0, 0]

T

v

s2

= v

i

+ [0, 0, 1]

T

v

s3

= v

i

+ [0, 1, 1]

T

v

s4

= v

i

+ [1, 1, 1]

T

t

1

= 1 v

f

c

t

2

= v

f

c

v

f

b

t

3

= v

f

b

v

f

a

t

4

= v

f

a

0 1 0

v

s1

= v

i

+ [0, 0, 0]

T

v

s2

= v

i

+ [0, 1, 0]

T

v

s3

= v

i

+ [1, 1, 0]

T

v

s4

= v

i

+ [1, 1, 1]

T

t

1

= 1 v

f

b

t

2

= v

f

b

v

f

a

t

3

= v

f

a

v

f

c

t

4

= v

f

c

0 1 1

v

s1

= v

i

+ [0, 0, 0]

T

v

s2

= v

i

+ [0, 1, 0]

T

v

s3

= v

i

+ [0, 1, 1]

T

v

s4

= v

i

+ [1, 1, 1]

T

t

1

= 1 v

f

b

t

2

= v

f

b

v

f

c

t

3

= v

f

c

v

f

a

t

4

= v

f

a

1 0 0

v

s1

= v

i

+ [0, 0, 0]

T

v

s2

= v

i

+ [1, 0, 0]

T

v

s3

= v

i

+ [1, 0, 1]

T

v

s4

= v

i

+ [1, 1, 1]

T

t

1

= 1 v

f

a

t

2

= v

f

a

v

f

c

t

3

= v

f

c

v

f

b

t

4

= v

f

b

1 1 0

v

s1

= v

i

+ [0, 0, 0]

T

v

s2

= v

i

+ [1, 0, 0]

T

v

s3

= v

i

+ [1, 1, 0]

T

v

s4

= v

i

+ [1, 1, 1]

T

t

1

= 1 v

f

a

t

2

= v

f

a

v

f

b

t

3

= v

f

b

v

f

c

t

4

= v

f

c

1 0 1

v

s1

= v

i

+ [0, 0, 0]

T

v

s2

= v

i

+ [0, 0, 1]

T

v

s3

= v

i

+ [1, 0, 1]

T

v

s4

= v

i

+ [1, 1, 1]

T

t

1

= 1 v

f

c

t

2

= v

f

c

v

f

a

t

3

= v

f

a

v

f

b

t

4

= v

f

b

normalized voltage reference is

v

r

=

V

r

V

dc

= [0.59, 1.86, 1.27]

T

.

By means of (4) and (5), this vector is decomposed into an

integer and a fractional part:

v

i

= integ(v

r

) = [0, 2, 1]

T

v

f

= v

r

v

i

= [0.59, 0.14, 0.27]

T

.

If the conditions in (18) are calculated the results are

C

ab

= [v

f

a

v

f

b

] = 1

C

bc

= [v

f

b

v

f

c

] = 0

C

ca

= [v

f

c

v

f

a

] = 0.

The case 100 of Table II provides the following switching

sequence:

v

s1

= v

i

+ [0, 0, 0]

T

= [0, 2, 1]

T

v

s2

= v

i

+ [1, 0, 0]

T

= [1, 2, 1]

T

v

s3

= v

i

+ [1, 0, 1]

T

= [1, 2, 2]

T

v

s4

= v

i

+ [1, 1, 1]

T

= [1, 1, 2]

T

.

together with their corresponding switching times:

t

1

= 1 v

f

a

= 0.41

t

2

= v

f

a

v

f

c

= 0.32

t

3

= v

f

c

v

f

b

= 0.13

t

4

= v

f

b

= 0.14.

5

It is important to remark that consecutive vectors of the

sequence are adjacent. Therefore, the number of switchings

is minimized.

IV. COMPARISON WITH PREVIOUS ALGORITHM

Although the nomenclature is different

1

, if the new three-

phase algorithm is compared with the 3D SVPWM generalized

algorithm then it notices that the Table II here presented is

the same as the table that details the states sequences and the

switching times in [6]. In fact, the six cases corresponding to

the six tetrahedrons in each subcube of the paper are equivalent

to the six cases derived from the three comparison operations

of this work. In particular, the cases 1.1, 1.2, 1.3, 2.1, 2.2 and

2.3 are respectively equivalent to the cases 100, 101, 001 ,011,

010 and 110 in this paper.

Even though, the comparison operations in both algorithms

are not identical, the differences are in the boundaries of the

tetrahedrons where two or more components of the fractional

part of the reference are equal. In such cases both algorithm

provide different switching sequences, but the switching vec-

tors that are different in those sequences have a zero switching

time so they are not executed and the modulation output is

identical in both algorithms.

As a consequence, the multiphase algorithm particularized

the three-phase systems in this paper is nearly the same as the

3D SVPWM generalized algorithm presented in [6]. Fig. 4

shows the modulation output of both modulation techniques

when a balanced three-phase reference with a normalized

amplitude of 1.9 is considered. A low switching frequency

(twenty times the fundamental) has been selected in order

to make the comparison easier. In both cases the modulation

output is identical, even in the sixth sampling period, when

v

r

= [1.9, 0.95, 0.95]

T

, in which the fractional parts of the

phases b and c are equal. In this particular case the multilevel

algorithm particularized for three-phase systems presented

in this paper provides the following switching vectors and

switching times (case 110):

v

s1

= [1, 1, 1]

T

t

1

= 0.10

v

s2

= [2, 1, 1]

T

t

2

= 0.85

v

s3

= [2, 0, 1]

T

t

3

= 0.00

v

s4

= [2, 0, 0]

T

t

4

= 0.05

whereas the 3D generalized SVPWM algorithm in [6] provides

the following results (case 1.1):

v

s1

= [1, 1, 1]

T

t

1

= 0.10

v

s2

= [2, 1, 1]

T

t

2

= 0.85

v

s3

= [2, 1, 0]

T

t

3

= 0.00

v

s4

= [2, 0, 0]

T

t

4

= 0.05.

Both switching sequences differ in their third output vector.

Nevertheless, those vectors has assigned a zero switching time

so nally none of them must be generated by the inverter and

the trigger signals are identical in both cases.

1

The terms [S

j

a

, S

j

b

, S

j

c

], [a, b, c], [u

a

, u

b

, u

c

] and d

j

in [6] are respec-

tively the same as the terms [v

s

a

j

, v

s

b

j

, v

s

c

j

], [v

i

a

, v

i

b

, v

i

c

], [v

r

a

, v

r

b

, v

r

c

]

and t

j

in this paper.

0 0.5 1

2

1

0

1

2

V

o

l

t

a

g

e

(

p

.

u

.

)

Normalized reference voltage

a

b

c

0 0.5 1

2

1

0

1

2

O

u

t

p

u

t

v

o

l

t

a

g

e

(

p

.

u

.

)

New threephase SVPWM algorithm

0 0.5 1

2

1

0

1

2

O

u

t

p

u

t

v

o

l

t

a

g

e

(

p

.

u

.

)

3D SVPWM generalized algorithm

0 0.5 1

1

0.5

0

0.5

1

Time (p.u.)

D

i

f

f

.

(

%

)

Ouputvoltage difference between both algoritms

Fig. 4. Simulation Results.

Since both algorithms are nearly same then all considera-

tions made in other works about the 3D SVPWM generalized

algorithm also applies to this algorithm [7]. Hence, it can

be considered as an extension of the 2D algorithms [6].

It is also equivalent to the 3D direct generalized algorithm

proposed in [8]. It can be used as a modulation algorithm in all

applications needing a three-dimension control vector such as

active lters with four-wire and single-phase distorting loads

which generate large neutral currents, where the conventional

2D space vector modulation can not be used.

Since the algorithm is a the particularization of the multi-

level multiphase space vector PWM in [9] it inherits some

features such as it minimizes the number of switchings,

it does not need trigonometric functions, look-up tables or

memories to store predened switching sequences and it has

low computational cost. Hence, the algorithm is well suited

for real time implementation in low cost devices.

V. HARDWARE IMPLEMENTATION

The SVPWM algorithm was described for a three-level

inverter with the very high speed integrated circuit hardware

description language (VHDL) and it was implemented by

6

TABLE III

RESOURCES SUMMARY

Target Device : xc3s200

Number of Slice Flip Flops: 2,179 out of 3,840 56%

Number of 4 input LUTs: 2,282 out of 3,840 59%

Number of occupied Slices: 1,669 out of 1,920 86%

Total Number 4 input LUTs: 2,450 out of 3,840 63%

Number of bonded IOBs: 63 out of 173 36%

IOB Flip Flops: 39

Number of Block RAMs: 0 out of 12 0%

Number of MULT18X18s: 0 out of 12 0%

Number of GCLKs: 8 out of 8 100%

Number of Startups: 1 out of 1 100%

Total equivalent gate count for design: 32,174

1 Phase a:

Phase b:

Phase c:

1 0 0 0 0 0

0 0 0 0 1 1 1

1 1 1 1 1 1 0

T

Dead time

Fig. 5. Trigger signals.

using a Digilent S3 board. This board hosts a XC3S200

FPGA from Xilinx, which has 4.320 logic cells, each one

constituted by two 16 1 look-up tables and two ip-ops.

This FPGA also has twelve 18 18 hardware multipliers, as

well as twelve 18 kb block random access memories (BRAM).

Table III shows a summary of the resources used by our

implementation. It is important to remark that the BRAMs and

the multipliers available in the FPGA were not used because

the algorithm does not need data storage or multiplication

operations.

Fig. 5 shows the FPGA output waveforms that correspond

to the trigger signals in the case v

r

= [0.16, 0.52, 0.77]

T

.

The needed dead time in complementary trigger signals was

implemented by delaying the rising edges.

The new algorithm was tested with a three-level NPC in-

verter driving a star connected induction motor. A 220/380 V,

1.420 r.p.m., 1.35 kW rated motor was used. According with

the motor characteristics a dc bus of 300 V was selected.

Fig. 6 shows a diagram and a photograph of the experimental

setup used in tests. It includes the power converter, the FPGA

board and a personal computer with a DSPACE DS1103 PPC

Controller Board.

A reference voltage with 50 Hz fundamental frequency

and a 10 kHz output switching frequency were considered.

Fig. 7 shows the inverter output voltage, besides the low-

order voltage harmonics, in the cases of sinusoidal reference

with and without third harmonic injection. Channels one and

three of the oscilloscope show the phase and the phase-to-

phase inverter output waveforms. Channels two and four are

Control SVPWM

NPC

inverter

150 V

150 V

Trigger

signals

DSPACE FPGA

Motor

Optical

link

(a)

DSPACE

FPGA

Motor

NPC inverter

Optical

link

dc bus

(b)

Fig. 6. Experimental test setup. (a) Diagram. (b) Photograph.

(a)

(b)

Fig. 7. Phase a inverter output voltage. Ch1: phase voltage, Ch2: ltered

phase voltage, Ch3: phase-to-phase voltage, Ch4: ltered phase-to-phase

voltage. (a) Without harmonic injection. (b) With third harmonic injection.

the same signals after been ltered. Fig. 7a shows the case

of purely sinusoidal reference with a normalized amplitude of

0.9 p.u.. In this case the low-order harmonics are low and

the total harmonic distortion (THD) is 4.8%. Fig. 7b shows

the case where a third harmonic of amplitude 0.4 p.u. was

added to the reference. In this case the high THD obtained

corresponds mainly to the injected harmonic.

7

VI. CONCLUSION

In this paper the recent SVPWM algorithm for multilevel

multiphase converters is particularized for three-phase sys-

tems. This particularized algorithm provides a sorted switching

vector sequence that minimizes the number of switchings. It

can be used with the standard multilevel topologies with any

number of levels. In addition, the proposed SVPWM algorithm

proves suitable for real-time implementation due to its low

computational complexity.

The particularized algorithm is demonstrated that is nearly

the same as the classical 3D space vector modulation gener-

alized algorithm for multilevel converters.

The three-level version of the new algorithm was imple-

mented in a low-cost FPGA and it was successfully tested by

using a neutral point clamped inverter.

REFERENCES

[1] J. Rodriguez, J. Lai, and F. Z. Peng, Multilevel inverters: a survey

of topologies, controls, and applications, IEEE Trans. Ind. Electron.,

vol. 49, no. 4, pp. 724738, Aug. 2002.

[2] K. Corzine and S. Lu, Comparison of hybrid propulsion drive schemes,

in Electric Ship Technologies Symposium, 2005 IEEE, 25-27 July 2005,

pp. 355362.

[3] J.-H. Youm and B.-H. Kwon, An effective software implementation of

the space-vector modulation, IEEE Trans. Ind. Electron., vol. 46, no. 4,

pp. 866868, Aug. 1999.

[4] A. Gupta and A. Khambadkone, A space vector PWM scheme for

multilevel inverters based on two-level space vector PWM, IEEE Trans.

Ind. Electron., vol. 53, no. 5, pp. 16311639, Oct. 2006.

[5] N. Celanovic and D. Boroyevich, A fast space-vector modulation

algorithm for multilevel three-phase converters, IEEE Trans. Ind. Appl.,

vol. 37, no. 2, pp. 637641, Mar. 2001.

[6] M. M. Prats, L. G. Franquelo, J. I. Leon, R. Portillo, E. Galvan, and

J. M. Carrasco, A 3-D space vector modulation generalized algorithm

for multilevel converters, IEEE Power Electronics Letters, vol. 1, no. 4,

pp. 110114, Dec. 2003.

[7] O. L opez, J.

Alvarez, J. Doval-Gandoy, and F. D. Freijedo, Comparison

of the FPGA implementation of two multilevel space vector PWM

algorithms, IEEE Trans. Ind. Electron., vol. 55, no. 4, Apr. 2008.

[8] N.-Y. Dai, M.-C. Wong, Y.-H. Chen, and Y.-D. Han, A 3-D gener-

alized direct PWM algorithm for multilevel converters, IEEE Power

Electronics Letters, vol. 3, no. 3, pp. 8588, Sep. 2005.

[9] O. L opez, J.

Alvarez, J. Doval-Gandoy, and F. D. Freijedo, Multilevel

multiphase space vector PWM algorithm, IEEE Trans. Ind. Electron.,

vol. 55, no. 5, May. 2008.

[10] O. L opez, J. Doval-Gandoy, C. M. Pe nalver, J. Rey, and F. D. Frei-

jedo, Redundancy and basic switching rules in multilevel converters,

International Review of Electrical Engineering, vol. 0, no. 0, pp. 6673,

Jan.Feb. 2006.

Potrebbero piacerti anche

- Stepping Motors and Their Microprocessor Controls (1984)Documento252 pagineStepping Motors and Their Microprocessor Controls (1984)Athiesh Kumar100% (2)

- Hitopadesha Choice of Other FriendsDocumento36 pagineHitopadesha Choice of Other FriendsAthiesh Kumar100% (3)

- MATLAB Link For Code Composer StudioDocumento326 pagineMATLAB Link For Code Composer StudioAthiesh KumarNessuna valutazione finora

- 980h CatDocumento4 pagine980h CatFreddy Villegas100% (4)

- Circuit Theory Notes PDFDocumento147 pagineCircuit Theory Notes PDFSaNdeepNessuna valutazione finora

- Three-Dimensional Space-Vector Modulation Algorithm For Four-Leg Multilevel Converters Using CoordinatesDocumento9 pagineThree-Dimensional Space-Vector Modulation Algorithm For Four-Leg Multilevel Converters Using CoordinatesBao Duong TranNessuna valutazione finora

- FPGA Implementation of Simplified SVPWM Algorithm For Three Phase Voltage Source InverterDocumento8 pagineFPGA Implementation of Simplified SVPWM Algorithm For Three Phase Voltage Source InverterVenkata Krishna AndeyNessuna valutazione finora

- A Novel Space-Vector PWM Computations For A Dual Three-Level T-Type Converter Applied To An Open End-Winding Induction MachineDocumento6 pagineA Novel Space-Vector PWM Computations For A Dual Three-Level T-Type Converter Applied To An Open End-Winding Induction MachineHieu VuNessuna valutazione finora

- A General Space Vector PWM Algorithm For Multilevel Inverters, Including Operation in OvermodulationDocumento10 pagineA General Space Vector PWM Algorithm For Multilevel Inverters, Including Operation in OvermodulationxuanthamdhqnNessuna valutazione finora

- IET - KCJ - Performance Evaluation of A General SVPWMDocumento9 pagineIET - KCJ - Performance Evaluation of A General SVPWMKartick JanaNessuna valutazione finora

- Simulation of A Space Vector PWM Controller For A Five-Level Voltage-Fed Inverter Motor DriveDocumento7 pagineSimulation of A Space Vector PWM Controller For A Five-Level Voltage-Fed Inverter Motor DriveIOSRjournalNessuna valutazione finora

- An Optimum PWM Strategy For 5-Level Active NPC (ANPC) Converter Based On Real-Time Solution For THD MinimizationDocumento7 pagineAn Optimum PWM Strategy For 5-Level Active NPC (ANPC) Converter Based On Real-Time Solution For THD MinimizationBrittany JohnsonNessuna valutazione finora

- THD Reduction in Multilevel Inverters Using Real-Time AlgorithmDocumento12 pagineTHD Reduction in Multilevel Inverters Using Real-Time AlgorithmInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- FPGA Realisation of SVPWMDocumento5 pagineFPGA Realisation of SVPWMsrfmlpNessuna valutazione finora

- 17 120920231241 Phpapp02 PDFDocumento9 pagine17 120920231241 Phpapp02 PDFPhani PhaniNessuna valutazione finora

- Switching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor DriveDocumento6 pagineSwitching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor Drivevinay kumarNessuna valutazione finora

- Digital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveDocumento7 pagineDigital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveijsretNessuna valutazione finora

- SVM Algorithm of Three-Level NPC Inverter: Shanmei Cheng and Yajun Liu Bing WuDocumento5 pagineSVM Algorithm of Three-Level NPC Inverter: Shanmei Cheng and Yajun Liu Bing WumücahitNessuna valutazione finora

- Implementation of SVPWM Based Three Phase Inverter Using 8 Bit MicrocontrollerDocumento5 pagineImplementation of SVPWM Based Three Phase Inverter Using 8 Bit MicrocontrollermitulNessuna valutazione finora

- Durgasukumar 2011Documento6 pagineDurgasukumar 2011aditya317crazyNessuna valutazione finora

- Identification of Optimal SVPWM Technique For MLI Fed Induction Motor DriveDocumento6 pagineIdentification of Optimal SVPWM Technique For MLI Fed Induction Motor DriveManu ThomasNessuna valutazione finora

- CIGRE-107 Fault Location in Extra Long HVDC Transmission Lines Using Discrete Wavelet TransformDocumento9 pagineCIGRE-107 Fault Location in Extra Long HVDC Transmission Lines Using Discrete Wavelet TransformkamuikNessuna valutazione finora

- InvertersDocumento7 pagineInverterslohitashriyaNessuna valutazione finora

- Psim SVMDocumento9 paginePsim SVMNarendra ReddyNessuna valutazione finora

- 3) Implementation of Equal Areas-PWM in Multilevel Inverters - Split - IREE - VOL - 11 - N - 6Documento9 pagine3) Implementation of Equal Areas-PWM in Multilevel Inverters - Split - IREE - VOL - 11 - N - 6Fpat PaterNessuna valutazione finora

- Inverter and SV-PWMDocumento5 pagineInverter and SV-PWMcoep05Nessuna valutazione finora

- International Journal of Engineering Research and DevelopmentDocumento5 pagineInternational Journal of Engineering Research and DevelopmentIJERDNessuna valutazione finora

- Generalized Rail Clamping Sequences Based PWM (GRCPWM) Algorithm For Direct Torque Controlled Induction Motor DriveDocumento22 pagineGeneralized Rail Clamping Sequences Based PWM (GRCPWM) Algorithm For Direct Torque Controlled Induction Motor DriveHari ReddyNessuna valutazione finora

- 2004 A Carrier-Based PWM Method For Three-Phase Four-LegDocumento10 pagine2004 A Carrier-Based PWM Method For Three-Phase Four-LegTài Nguyễn Minh NhậtNessuna valutazione finora

- Design and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerDocumento12 pagineDesign and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerHaider NeamaNessuna valutazione finora

- Fast-Predictive Optimal Control of NPC Multilevel ConvertersDocumento9 pagineFast-Predictive Optimal Control of NPC Multilevel Converterskanda71Nessuna valutazione finora

- Simplified SVPWM Algorithm For VectorDocumento4 pagineSimplified SVPWM Algorithm For VectorPrudhvi RajNessuna valutazione finora

- Space Vector PWM - 1Documento5 pagineSpace Vector PWM - 1guanitouNessuna valutazione finora

- A Simple and Ultra-Fast DSP-Based Space Vector PWM Algorithm andDocumento6 pagineA Simple and Ultra-Fast DSP-Based Space Vector PWM Algorithm andShiviAroraNessuna valutazione finora

- Harmonic and Loss Analysis of Space-Vector Modulated ConvertersDocumento6 pagineHarmonic and Loss Analysis of Space-Vector Modulated Convertersahmet ozturkNessuna valutazione finora

- Three-Level Inverter Performance Using Adaptive Neuro-Fuzzy Based Space Vector ModulationDocumento14 pagineThree-Level Inverter Performance Using Adaptive Neuro-Fuzzy Based Space Vector ModulationiisteNessuna valutazione finora

- A Method Based On Imperialist Competitive Algorithm (ICA), Aiming To Mitigate Harmonics in Multilevel InvertersDocumento6 pagineA Method Based On Imperialist Competitive Algorithm (ICA), Aiming To Mitigate Harmonics in Multilevel InvertersHamid Reza KaboliNessuna valutazione finora

- Simplifi Ed SVPWM Based Hybrid PWM For Induction Motor Drives For The Reduction of Torque RipplesDocumento6 pagineSimplifi Ed SVPWM Based Hybrid PWM For Induction Motor Drives For The Reduction of Torque RipplesKoukou AmkoukouNessuna valutazione finora

- Space Vector Based Generalized DPWM Algorithms For Vsi Fed Induction Motor DriveDocumento8 pagineSpace Vector Based Generalized DPWM Algorithms For Vsi Fed Induction Motor DriveSherif M. DabourNessuna valutazione finora

- Implementation of A Fuzzy PI Controller For Speed Control of Induction Motors Using FPGADocumento7 pagineImplementation of A Fuzzy PI Controller For Speed Control of Induction Motors Using FPGABharati RajaNessuna valutazione finora

- A Comparison of Multicarrier PWM Strategies For Cascaded and Neutral Point Clamped Multilevel InvertersDocumento6 pagineA Comparison of Multicarrier PWM Strategies For Cascaded and Neutral Point Clamped Multilevel InvertersKanna Thanga RajNessuna valutazione finora

- Hysteresis ControllerDocumento9 pagineHysteresis ControllerengrarNessuna valutazione finora

- Exp 10 Transient Stability AnalysisDocumento6 pagineExp 10 Transient Stability AnalysisPuduru BharathiNessuna valutazione finora

- Karampuri 2016Documento6 pagineKarampuri 2016Kill MongerNessuna valutazione finora

- Harmonic Reduction Technique For A Cascade Multilevel InverterDocumento5 pagineHarmonic Reduction Technique For A Cascade Multilevel InverterAdrian Alexandru MoldovanNessuna valutazione finora

- A Novel Space Vector Modulation (SVM) Controlled Inverter For Adjustable Speed Drive ApplicationsDocumento9 pagineA Novel Space Vector Modulation (SVM) Controlled Inverter For Adjustable Speed Drive ApplicationsInternational Journal of Engineering Inventions (IJEI)Nessuna valutazione finora

- Space Vector Pulse Width Modulation Schemes For Two-Level Voltage Source InverterDocumento5 pagineSpace Vector Pulse Width Modulation Schemes For Two-Level Voltage Source InverterIDESNessuna valutazione finora

- A Novel Implementation SVPWM Algorithm and Its Application To Three-Phase Power ConverterDocumento4 pagineA Novel Implementation SVPWM Algorithm and Its Application To Three-Phase Power ConverterRanjit SinghNessuna valutazione finora

- Analysis of An Asymmetric Modulation Method For Cascaded Multilevel InvertersDocumento12 pagineAnalysis of An Asymmetric Modulation Method For Cascaded Multilevel InvertersJoshua RealsteelNessuna valutazione finora

- Fujimoto - 2007Documento6 pagineFujimoto - 2007Ariana Ribeiro LameirinhasNessuna valutazione finora

- 06125602Documento6 pagine06125602Ahmad Sadam SyaeroziNessuna valutazione finora

- Space Vector PWM Control of Dual Inverter Fed Open-End Winding Induction MotorDocumento7 pagineSpace Vector PWM Control of Dual Inverter Fed Open-End Winding Induction MotorGanesh ChallaNessuna valutazione finora

- Low Cost Digital Signal Generation For Driving Space Vector PWM InverterDocumento12 pagineLow Cost Digital Signal Generation For Driving Space Vector PWM InverterJunaid AhmadNessuna valutazione finora

- A Study of Comparative Analysis of Different PWMDocumento6 pagineA Study of Comparative Analysis of Different PWMwilliam chaconNessuna valutazione finora

- Comparison of Three SVPWM StrategiesDocumento5 pagineComparison of Three SVPWM Strategiesఅనిల్ కుమార్ రాజగిరిNessuna valutazione finora

- 2013 A Simple Carrier-Based Modulation For The SVM of The Matrix ConverterDocumento10 pagine2013 A Simple Carrier-Based Modulation For The SVM of The Matrix ConverterTran Quoc HoanNessuna valutazione finora

- A Novel Space Vector Modulation Control Strategy For Three-Leg Four-WireDocumento10 pagineA Novel Space Vector Modulation Control Strategy For Three-Leg Four-WireakankshiNessuna valutazione finora

- FPGA Implementation On SVPWM MLIDocumento5 pagineFPGA Implementation On SVPWM MLISheetal VermaNessuna valutazione finora

- Evaluation of Current Ripple Amplitude in Three-Phase PWM Voltage Source InvertersDocumento6 pagineEvaluation of Current Ripple Amplitude in Three-Phase PWM Voltage Source InvertersluanleNessuna valutazione finora

- Research PaperDocumento10 pagineResearch PaperVikas PatelNessuna valutazione finora

- WaveletsDocumento32 pagineWaveletshareesh.makesuNessuna valutazione finora

- DC-Bus Utilisation in Series-Connected Multi-Phase Machines Supplied From A VSI With A Composite Phase NumberDocumento6 pagineDC-Bus Utilisation in Series-Connected Multi-Phase Machines Supplied From A VSI With A Composite Phase NumberSherif M. DabourNessuna valutazione finora

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsDa EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsNessuna valutazione finora

- Spline and Spline Wavelet Methods with Applications to Signal and Image Processing: Volume III: Selected TopicsDa EverandSpline and Spline Wavelet Methods with Applications to Signal and Image Processing: Volume III: Selected TopicsNessuna valutazione finora

- SSQW 054Documento8 pagineSSQW 054praveen_warneNessuna valutazione finora

- MATLAB-Simulink Implementation and Analysis of Three Pulse-WidthDocumento102 pagineMATLAB-Simulink Implementation and Analysis of Three Pulse-WidthLeonardo LimaNessuna valutazione finora

- Non Teaching Application FormDocumento3 pagineNon Teaching Application FormAthiesh KumarNessuna valutazione finora

- Npe 001Documento10 pagineNpe 001Athiesh KumarNessuna valutazione finora

- Recruitment Notification Non Teaching June2014 PDFDocumento4 pagineRecruitment Notification Non Teaching June2014 PDFAthiesh KumarNessuna valutazione finora

- Design and Implementation of Switched Mode Power Supply Using PWM ConceptsDocumento49 pagineDesign and Implementation of Switched Mode Power Supply Using PWM ConceptsAndre Amorim100% (2)

- Birbal To The RescueDocumento36 pagineBirbal To The RescueAthiesh KumarNessuna valutazione finora

- Comparison of Power Quality Improvement Techniques in AC-DC Cuk ConverterDocumento5 pagineComparison of Power Quality Improvement Techniques in AC-DC Cuk ConverterAthiesh KumarNessuna valutazione finora

- Paper 02Documento8 paginePaper 02Athiesh KumarNessuna valutazione finora

- IntroDocumento12 pagineIntroAthiesh KumarNessuna valutazione finora

- FFT Matlab TutorialDocumento6 pagineFFT Matlab Tutorialichwan13Nessuna valutazione finora

- The Indian War of Independence 1857Documento400 pagineThe Indian War of Independence 1857anuraggupta74@gmail.comNessuna valutazione finora

- State Space Averaging Model of Boost ConvDocumento60 pagineState Space Averaging Model of Boost ConvBharti Thakur100% (1)

- Fee Structure in House Students PDFDocumento2 pagineFee Structure in House Students PDFAthiesh KumarNessuna valutazione finora

- Adi ShankaraDocumento34 pagineAdi ShankaraAthiesh Kumar100% (3)

- Prezentace 09 1106Documento140 paginePrezentace 09 1106Athiesh KumarNessuna valutazione finora

- SosthenesDocumento396 pagineSosthenesAthiesh KumarNessuna valutazione finora

- VSIAcademia PDFDocumento12 pagineVSIAcademia PDFAthiesh KumarNessuna valutazione finora

- RajaniDocumento69 pagineRajaniChaitanya ChaNessuna valutazione finora

- A Voltage-Controlled PFC Cuk Converter-BasedDocumento7 pagineA Voltage-Controlled PFC Cuk Converter-BasedAthiesh KumarNessuna valutazione finora

- A Voltage-Controlled PFC Cuk Converter-BasedDocumento7 pagineA Voltage-Controlled PFC Cuk Converter-BasedAthiesh KumarNessuna valutazione finora

- <!DOCTYPE HTML PUBLIC "-//W3C//DTD HTML 4.01 Transitional//EN" "http://www.w3.org/TR/html4/loose.dtd"> <HTML><HEAD><META HTTP-EQUIV="Content-Type" CONTENT="text/html; charset=iso-8859-1"> <TITLE>ERROR: The requested URL could not be retrieved</TITLE> <STYLE type="text/css"><!--BODY{background-color:#ffffff;font-family:verdana,sans-serif}PRE{font-family:sans-serif}--></STYLE> </HEAD><BODY> <H1>ERROR</H1> <H2>The requested URL could not be retrieved</H2> <HR noshade size="1px"> <P> While trying to process the request: <PRE> TEXT http://www.scribd.com/titlecleaner?title=Simulation+of+power+Electronics-MB.Patil.pdf HTTP/1.1 Host: www.scribd.com Proxy-Connection: keep-alive Accept: */* Origin: http://www.scribd.com X-CSRF-Token: 8620b1f488022a7b4012914aab897e4b25338c55 User-Agent: Mozilla/5.0 (Windows NT 6.1) AppleWebKit/537.31 (KHTML, like Gecko) Chrome/26.0.1410.64 Safari/537.31 X-Requested-With: XMLHttpRequest Referer: http://www.scribd.com/upload-document?archive_doc=Documento164 pagine<!DOCTYPE HTML PUBLIC "-//W3C//DTD HTML 4.01 Transitional//EN" "http://www.w3.org/TR/html4/loose.dtd"> <HTML><HEAD><META HTTP-EQUIV="Content-Type" CONTENT="text/html; charset=iso-8859-1"> <TITLE>ERROR: The requested URL could not be retrieved</TITLE> <STYLE type="text/css"><!--BODY{background-color:#ffffff;font-family:verdana,sans-serif}PRE{font-family:sans-serif}--></STYLE> </HEAD><BODY> <H1>ERROR</H1> <H2>The requested URL could not be retrieved</H2> <HR noshade size="1px"> <P> While trying to process the request: <PRE> TEXT http://www.scribd.com/titlecleaner?title=Simulation+of+power+Electronics-MB.Patil.pdf HTTP/1.1 Host: www.scribd.com Proxy-Connection: keep-alive Accept: */* Origin: http://www.scribd.com X-CSRF-Token: 8620b1f488022a7b4012914aab897e4b25338c55 User-Agent: Mozilla/5.0 (Windows NT 6.1) AppleWebKit/537.31 (KHTML, like Gecko) Chrome/26.0.1410.64 Safari/537.31 X-Requested-With: XMLHttpRequest Referer: http://www.scribd.com/upload-document?archive_doc=Athiesh KumarNessuna valutazione finora

- A Systematic Approach To Synthesizing Multi-Input DC-DC Converters PDFDocumento12 pagineA Systematic Approach To Synthesizing Multi-Input DC-DC Converters PDFAthiesh KumarNessuna valutazione finora

- Illumination EnggDocumento171 pagineIllumination EnggMELVINNessuna valutazione finora

- Organization of Intel 8085Documento6 pagineOrganization of Intel 8085Athiesh KumarNessuna valutazione finora

- Sinusoidal Pulse Width Modulation: 24.437 Power ElectronicsDocumento8 pagineSinusoidal Pulse Width Modulation: 24.437 Power ElectronicsTakul Sudah BishaNessuna valutazione finora

- Littlebits Arduino Coding Kit Invention GuideDocumento32 pagineLittlebits Arduino Coding Kit Invention GuideDavid Badosa PuigNessuna valutazione finora

- Bhel-5 Forces ModelDocumento3 pagineBhel-5 Forces ModelAvanindra Nayak100% (1)

- Sistema Eléctrico 4RCDocumento2 pagineSistema Eléctrico 4RCAlejandro HcNessuna valutazione finora

- Schneider Distribution Transformer1Documento44 pagineSchneider Distribution Transformer1STEVE58100% (3)

- Applied Applied Applied Applied Physics Laboratory Manual Physics Laboratory Manual Physics Laboratory Manual Physics Laboratory ManualDocumento26 pagineApplied Applied Applied Applied Physics Laboratory Manual Physics Laboratory Manual Physics Laboratory Manual Physics Laboratory ManualTony TheoNessuna valutazione finora

- Ultra-Small, Low-Power, 16-Bit Analog-to-Digital Converter With Internal ReferenceDocumento36 pagineUltra-Small, Low-Power, 16-Bit Analog-to-Digital Converter With Internal ReferenceSteven FlorezNessuna valutazione finora

- 3RD PresentatiOn AcceptedDocumento19 pagine3RD PresentatiOn AcceptedZeeshan KhanNessuna valutazione finora

- EC6401 Electronics Circuits II - Notes - AnnaunivupdatesDocumento96 pagineEC6401 Electronics Circuits II - Notes - Annaunivupdatesmanimangai100% (2)

- Alstom's ECO 100 PlatformDocumento23 pagineAlstom's ECO 100 Platformopzz_opzz100% (1)

- Chapter 13Documento24 pagineChapter 13Noer DianNessuna valutazione finora

- Communications PDFDocumento12 pagineCommunications PDFChester Kyles ColitaNessuna valutazione finora

- Manual Eng 10-01-01Documento19 pagineManual Eng 10-01-01EASY TECHNessuna valutazione finora

- Job Card Cable Pulling PDFDocumento6 pagineJob Card Cable Pulling PDFHERWIN SEPTIYANNessuna valutazione finora

- Qelectrotech ElementDocumento2 pagineQelectrotech ElementAnggy Anggraini UsmanNessuna valutazione finora

- Zenith E-Series ESP Gauge Technical Data SheetDocumento2 pagineZenith E-Series ESP Gauge Technical Data SheetMustafa LaghaNessuna valutazione finora

- GE 489 ManualDocumento314 pagineGE 489 ManualNav Kalidas100% (1)

- Module Description HDI-050-XXS MP40 1.1Documento9 pagineModule Description HDI-050-XXS MP40 1.1felipebdNessuna valutazione finora

- Process Automation Factory Automation Terminal AutomationDocumento4 pagineProcess Automation Factory Automation Terminal AutomationRitaban R. BanerjeeNessuna valutazione finora

- Zero Delay USB Encoder True Analog Joystick ModifiDocumento16 pagineZero Delay USB Encoder True Analog Joystick ModifiIroquois PliskinNessuna valutazione finora

- IPD3005C DatasheetDocumento3 pagineIPD3005C DatasheetAscenten TechnologiesNessuna valutazione finora

- 7145 7222 7228 7235SM PDFDocumento448 pagine7145 7222 7228 7235SM PDFevpsasaNessuna valutazione finora

- Rukovodstvo Po Jekspluatacii Chillerov CWFL 800 CWFL 1000 CWFL 1500 SA Angl. Kit.Documento28 pagineRukovodstvo Po Jekspluatacii Chillerov CWFL 800 CWFL 1000 CWFL 1500 SA Angl. Kit.ABDERRAHMAN BENIFFOUNessuna valutazione finora

- 18PYB103J Lesson PlanDocumento6 pagine18PYB103J Lesson PlanMohammed JavidhNessuna valutazione finora

- MNPDocumento3 pagineMNPsrkNessuna valutazione finora

- MicPreamp Print PubDocumento2 pagineMicPreamp Print Pubapi-12922547100% (1)

- Wind Up Torch Hand Cranked, Dynamo, LED AmendDocumento9 pagineWind Up Torch Hand Cranked, Dynamo, LED AmendMarius DanilaNessuna valutazione finora

- VdivDocumento12 pagineVdivmehralsmenschNessuna valutazione finora

- Be1-Flex (Uub)Documento2 pagineBe1-Flex (Uub)Eliyanto E BudiartoNessuna valutazione finora