Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

VLSI Board Manual

Caricato da

Nazmul HussainCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

VLSI Board Manual

Caricato da

Nazmul HussainCopyright:

Formati disponibili

Emblitz VLSI Board

Manual

Author: Priyesh Baby

Version: V1.0

VLSI Kit features

1. 100,000 gate Xilinx Spartan 3E FPGA

2. JTAG programming port

3. XCF04S Xilinx Platform Flash ROM to store FPGA

configurations

4. Large collection of I/Os including eight LEDs and four slide

switches

5. LCD and 7 segment displays

6. 3 bit, 8 color VGA port

7. 9 pin RS232 serial port

8. Ethernet port with physical layer controller

9. User-selectable oscillator , plus a socket for a second oscillator

10. 100 pin user I/O and peripheral module connection

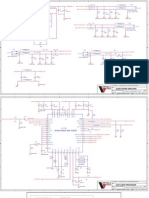

Block diagram of Emblitz VLSI kit

FPGA features

1. 100k gates.

2. 108 I/Os

3. 72k Block RAM

4. 15k Distributed RAM

5. 240 CLBs

6. 4 multiplexers

7. 2 Digital clock managers (DCM)

Kit Contents

1. VLSI Board

2. LCD

3. JTAG Cable

4. USB Cable

5. VLSI Kit CD

6. Extra Jumpers

Functional Description

The Emblitz VLSI board provides an inexpensive, robust, and easy-to-use

platform that anyone can use to gain experience with FPGA devices and

modern design methods. It is centered on the Spartan 3E FPGA, and it

contains all needed support circuits so designs can get up and running

quickly. The large collection of on-board I/O devices allow many designs

to be completed without the need for any other hardware, making the this

board an ideal introductory platform for experimenting with new designs

or learning about FPGAs and tools. The Emblitz VLSI board works with

all versions of the Xilinx ISE tools, including the free Web Pack tools. It

ships with a USB cable for power supply and programming cable, so

designs can be implemented immediately without the need for any

additional hardware.

Power Supply

This board can be powered from USB cable or 5v-9v DC adapter. There

is a voltage regulation section it will produce 4 different voltages (5v,

3.3v, 2.5v, 1.2v). These voltages are also available in connector J9. 3.3v,

2.5v, 1.2v are used for FPGA and other peripherals. 5v is only for LCD.

SW2 is power on switch, when ever sw2 is on then LED LD13 will glow.

Oscillators

This board includes a primary, user-settable silicon oscillator (connected

to GCLK4-p122) that produces 25MHz, 50MHz, or 100MHz based on

the position of the clock select jumper at J8( 1&2- 25 MHz, 2 &3

100MHz, no jumper 50 MHz). A socket for a second oscillator

(connected to GCLK5-p123) is also provided at U4 (the U4 socket can

accommodate any 3.3V CMOS oscillator in a half-size DIP package).

There is a third oscillator (connected to GCLK6-p125) option with

50MHz SG8002JA silicon oscillator. All clock inputs can drive the clock

synthesizer DLL on the Spartan 3E, allowing for a wide range if internal

frequencies, from 4 times the input frequency to any integer divisor of the

input frequency.

Slide Switches and LEDs

There are 4 slid switches for giving inputs and 8 LEDs for getting output.

The pin connection of LEDs and switches with FPGA is shown below.

LCD display and 7 segment display

This board having 2X16 LCD module and a 7 segment display are

connected directly to the FPGA. The pin connections are given.

LED

Fpga Pin

no:

LD5 p2

LD6

p3

LD7

p4

LD8

p5

LD9

p7

LD10

p8

LED\sw

Fpga Pin

no:

LD11

p25

LD12

p26

S1

p6

S2

p10

S3

p12

S4

p18

7 segment connections

LCD display connections

7seg/LCD

Fpga Pin

no:

B0

p14

B1

p15

B2

p16

B3

p17

B4

p20

B5

p21

B6

p22

B7

p23

D0

p124

D1

p132

7seg/LCD

Fpga Pin

no:

D2

p112

D3

p113

D4

p116

D5

p117

D6

p134

D7

p135

RW

p139

RS

p142

E

p140

8 color VGA port

This board having a VGA port with 3 bits(r, g, b), ie one bit each color.

These 3 bits will provide eight color combinations in the display. There

are two other pins horizontal sync and vertical sync also given to VGA

port from FPGA. So totally 5 pins are connected from FPGA to VGA

port shown below.

Different color combinations and VGA port pin connections

RS232 serial port

This Board having a 9 pin female RS 232 connector which is connected

to the 33 and 34 pins (TX and RX of serial port) of FPGA. The

connections are given in the below block diagram.

FPGA configurations settings

This board providing two types of configuration modes. In both modes

MODE 1, 2, 3 jumpers (J4, 5, 6) are closed.

1. FPGA configuration from PC through JTAG

No jumper in J2

2. FPGA configuration from XCF04S Xilinx Platform Flash ROM.

Put jumper in J2 (2&3).

Ethernet port with MAC layer

This board providing Ethernet port with a RTL 8019A controller, this

controller having the in built MAC and physical layer. So there is no need

to implement Mac layer in the FPGA side. There is 18 lines are connected

from RTL 8019 chip to FPGA in that 8 data lines 5 address lines and 5

control lines.

More details of RTL8019A you can get it from data sheet of 8019A chip.

Ethernet

pins

FPGA

Pin no:

Ethernet

pins

FPGA

Pin no:

Ethernet

pins

FPGA

Pin no:

D0 P81 D6 P91 A4 P54

D1

P82

D7

P92

CS

P70

D2

P85

A0

P50

IRQ

P74

D3

P86

A1

P51

RST

P75

D4

P87

A2

P52

WR

P76

D5

p88

A3

P53

RD

P77

References:

www.xilinx.com/support/mysupport.htm

www.emblitz.com

Everesl lrlocor Pvl. Lld.

#Z38/33, 12

lr

ra|r, 3

rd

8|oc|, Rajaj|ragar 8arga|ore-50010, lrd|a

Prore: 91-80-23110311 / 2311 229, Voo||e: 91 99852Z33

Era||: order_ero||lz.cor, supporl_ero||lz.cor, WWW.ero||lz.cor, WWW.e||aoz.cor,

WWW.everesl|rlo.|r

Potrebbero piacerti anche

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Analog Ic Layout 1 1385Documento54 pagineAnalog Ic Layout 1 1385v4vktryNessuna valutazione finora

- Stick Diagrams: Chapter 1 IntroductionDocumento1 paginaStick Diagrams: Chapter 1 IntroductionCarlos SaavedraNessuna valutazione finora

- Dspic33Fj16Gs504 Pim Information SheetDocumento4 pagineDspic33Fj16Gs504 Pim Information SheettiendungNessuna valutazione finora

- Lab2a - RGB LED PDFDocumento18 pagineLab2a - RGB LED PDFjavier0% (1)

- Beep CordsDocumento2 pagineBeep Cordsapi-3727667Nessuna valutazione finora

- Dynamic Logic CircuitsDocumento61 pagineDynamic Logic Circuitsbirla_sNessuna valutazione finora

- PH 22Documento35 paginePH 22Janosi ParaNessuna valutazione finora

- Tda 7540Documento7 pagineTda 7540Bảo Bình100% (1)

- Advantages and Disadvantages of Totem Pole OutputDocumento3 pagineAdvantages and Disadvantages of Totem Pole OutputSiva Guru50% (2)

- d865gbf PDFDocumento98 pagined865gbf PDFJuris Dela Rosa UrbanoNessuna valutazione finora

- Logic Gates: Learning ObjectivesDocumento16 pagineLogic Gates: Learning ObjectiveskalyanNessuna valutazione finora

- Vertex 2 Pro SchematicsDocumento38 pagineVertex 2 Pro SchematicsSyed Hassan Raza Naqvi100% (1)

- Retentive Timer On (RTO) : InstructionDocumento3 pagineRetentive Timer On (RTO) : InstructionAgil Dwy CahyoNessuna valutazione finora

- Intel CPUs Explained - What Are E-Cores and P-Cores1Documento24 pagineIntel CPUs Explained - What Are E-Cores and P-Cores1Ajay MaluNessuna valutazione finora

- M.E.VLSI DesignDocumento43 pagineM.E.VLSI DesignThahsin ThahirNessuna valutazione finora

- PIC16F716: PIC16F716 Rev. A Silicon/Data Sheet ErrataDocumento6 paginePIC16F716: PIC16F716 Rev. A Silicon/Data Sheet ErrataAnderson Ricardo PradoNessuna valutazione finora

- Customer Stancil RecorderDocumento21 pagineCustomer Stancil RecorderGS MeenaNessuna valutazione finora

- Low Voltage Translation For SPI, UART, RGMII, JTAG InterfacesDocumento15 pagineLow Voltage Translation For SPI, UART, RGMII, JTAG InterfacesspotNessuna valutazione finora

- CCSP 1987 06Documento311 pagineCCSP 1987 06zkovaNessuna valutazione finora

- Multi-GPU FAQDocumento2 pagineMulti-GPU FAQBogdan RuxandaNessuna valutazione finora

- Fundamentals of Quantitative Design and Analysis: A Quantitative Approach, Fifth EditionDocumento54 pagineFundamentals of Quantitative Design and Analysis: A Quantitative Approach, Fifth Editionmwangilaureen493Nessuna valutazione finora

- ACA Notes Diginotes PDFDocumento283 pagineACA Notes Diginotes PDFPrakhyath JainNessuna valutazione finora

- Huawei Tecal RH2285 Rack ServerDocumento4 pagineHuawei Tecal RH2285 Rack ServerAhmed Khiry RamadanNessuna valutazione finora

- B.Tech - ECE - Study Scheme Syllabus Upto - 8th Sem. 2018 Onwards Updated On 8th - July - 2022Documento89 pagineB.Tech - ECE - Study Scheme Syllabus Upto - 8th Sem. 2018 Onwards Updated On 8th - July - 2022Anurag DavesarNessuna valutazione finora

- A1sj61bt11 CC Link MasterDocumento280 pagineA1sj61bt11 CC Link MasterTetsusaigaNessuna valutazione finora

- 4.6.3 SCSI BusDocumento15 pagine4.6.3 SCSI Buskollavivek_534195858100% (1)

- Study and Simulation of Five-Story Elevator Controller Using VHDLDocumento4 pagineStudy and Simulation of Five-Story Elevator Controller Using VHDLHemanth S.NNessuna valutazione finora

- Samsung SCX 1150 MFP Service ManualDocumento66 pagineSamsung SCX 1150 MFP Service ManualwcualumniNessuna valutazione finora

- Experiment 12 Timer Programming in 8051: 12.1. Aim(s) / Objective(s) / PurposeDocumento2 pagineExperiment 12 Timer Programming in 8051: 12.1. Aim(s) / Objective(s) / Purposepraveenembd1Nessuna valutazione finora

- Assembler Directives of 8085Documento19 pagineAssembler Directives of 8085sureshgurujiNessuna valutazione finora