Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Capitulo 8 USART

Caricato da

rickypinaDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Capitulo 8 USART

Caricato da

rickypinaCopyright:

Formati disponibili

Capitulo 8 USART

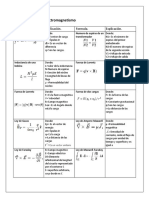

8.0 Introduccin La comunicacin serial es un proceso de envo de mltiples bits de datos sobre un solo alambre. Es una reminiscencia del telgrafo original, en el cual los bits fueron los puntos y las rayas del cdigo Morse. Los bits de un byte serial estn separados en tiempo tal que el dispositivo receptos puede determinar los niveles lgicos de cada bit. El USART es empleado para comunicarse del microcontrolador a varios otros dispositivos. Ejemplos de estos dispositivos incluyen la herramienta terminal del Code Vision (empleado para los problemas y la depuracin de los problemas de los programas), otros microcontroladores que requieren comunicarse con otros microcontroladores para efectuar un trabajo. La forma regular de comunicacin serial, y la forma que se discutir aqu, es comunicacin serial asncrona. La cual es asncrona en el sentido que la seal de reloj comn no se requiere tanto en la transmisin como en la recepcin para la sincronizacin de la deteccin de los datos. Comunicacin serial asncrona emplea un bit de arranque y un bit de fin de transmisin agregados al byte de datos para permitir al receptor la determinacin del tiempo de cada bit. En la siguiente figura se muestra los elementos del byte de la comunicacin serial asncrona. Esta figura muestra la definicin de cada bit de la palabra serial. El mensaje inicia con una espera estando en alto y pasando a bajo para iniciar el mensaje. El bit de arranque o inicio toma el valor de un bit completo y es seguido por los ocho bits de l byte de dato que se muestra sobre una lnea serial en un orden inverso, esto es, el bit menos significativo aparece primero y el bit ms significativo aparece al ltimo. El bit de fin de mensaje sigue al bit mas significativo corresponde a un uno lgico, el mismo valor para el bit de espera.

St (n) P Sp Idle

bit de inicio siempre en cero lgico. bits de datos (0 a 8) Bit de paridad. Puede ser par o impar. bit de fin de mensaje. Siempre en uno lgico bit de espera. No existe transferencia de datos sobre la lnea de comunicacin

El flanco de bajada inicia la secuencia de transmisin en el receptor serial. Iniciando desde el flanco de bajada del bit de inicio, el receptor espera 1.5 bits antes de muestrear la linea receptora. Despues de eso, el receptor espera 1 bit por cada bit, por lo tanto se muestrea cada bit de dato sucesivo en el centro del periodo para maxima eficiencia. Afortunadamente, todo el tiempo del formateo del byte serial, el muetreo de los bits seriales, y la suma del bit de inico y el bit de fin de transmisin son manejados automaticamente por el universal synchronous asynchronous receiver transmitter (USART). 8.1 USART El transmisn y receptor serial asincrono y sincrono universal (USART) es una unidad de comunicacin periferica muy flexible, que en le microcntrolador atemga8 permite entre otras funciones. Operacin full dplex (se puede enviar y recibir datos simultneamente) Operacin sncrona y asncrona Operacin en modo maestro esclavo con reloj sncrono Soporta frames de 5,6,7,8 y 9 datos y 1 o 2 de parada Generador de paridad par o impar Deteccin de errores (sobre flujo de datos, error en el frame) Filtrado de ruido (inicio falso, filtro digital) Generacin de interrupciones por transmisin completa, por recepcin completa o por registro de datos de transmisin vaca Comunicacin entre multiprocesadores Doblador de velocidad modo de comunicacin asncrona

8.2 Norma RS 232 La interfaz RS-232 est diseada para distancias cortas, de hasta 15 metros segn la norma, y para velocidades de comunicacin bajas, de no ms de 20 Kilobytes/segundo. A pesar de ello, muchas veces se utiliza a mayores velocidades con un resultado aceptable. La interfaz puede trabajar en comunicacin asncrona o sncrona y tipos de canal simplex, half duplex o full duplex. En un canal simplex los datos siempre viajarn en una direccin, por ejemplo desde DCE a DTE. En un canal half duplex, los datos pueden viajar en una u otra direccin, pero slo durante un determinado periodo de tiempo; luego la lnea debe ser conmutada antes que los datos puedan viajar en la otra direccin. En un canal full duplex, los datos pueden viajar en ambos sentidos simultneamente. Las lneas de handshaking de la RS-232 se usan para resolver los problemas asociados con este modo de operacin, tal como en qu direccin los datos deben viajar en un instante determinado. Si un dispositivo de los que estn conectados a una interfaz RS-232 procesa los datos a una velocidad menor de la que los recibe deben de conectarse las lneas handshaking que permiten realizar un control de flujo tal que al dispositivo ms lento le d tiempo de procesar la informacin. Las lneas de "hand shaking" que permiten hacer este control de flujo son las lneas

RTS y CTS. Los diseadores del estndar no concibieron estas lneas para que funcionen de este modo, pero dada su utilidad en cada interfaz posterior se incluye este modo de uso. La norma RS 232 es un protocolo de comunicacin serial que define la transmisin fsica entre la terminal DTE (Data terminal equipment) y un modem DCE(Data comunication equipment). Este protocolo define un uno lgico como una seal comprendida en el intervalo de -5 volts a -15 volts y un cero lgico como una seal comprendida en el intervalo de +5 volts a +15 volts. Bajo esta terminologa, la primera transmisin de 1 a 0o lgico, define un bit de inicio, bit de arranque, a la que le siguen 5,6,7 u 8 bits de datos. El octavo biy se emplea como bit de paridad, mecanismo de deteccin de errores; al final de la transmisin, la seal debe regresar al valor lgico cero, el cual se define como bit de fin de transmisin, que se puede configurar como uno o dos bits. El conector normalizado para este protocolo es el conector V24, de 25 terminales, sin embargo, en equipos de cmputo es ms utilizado el conector DB9 de 9 terminales, las terminales de este conector se muestran en la siguiente tabla.

Numero 1 2

Nombre CD RXD

Funcin Deteccin de portadora Recepcin de dato

3 4 5 6 7 8 9 8.3 Configuracin de la USART

TXD DTR GND DSR RST CTS Ri

Transmisin de dato Dato en la terminal listo Tierra del sistema Conjunto de datos listo Solicitud para envi Limpiar para envi Timbre

8.3.1 Registro de entrada/salida de datos de la USART, UDR

Es el registro donde se escriben los datos a transmitir (TXB) y donde se leen los datos recibidos (RXB), slo se pueden escribir en este registro cuando el bit UDRE del registro del registro UCSRA est en uno. 8.3.2 Registro de control y estado de la USART, UCSRA

Bit 7- RXC, recepcin completa. Este bit se activa cuando existen datos no ledos en el buffer de recepcin. Bit 6- TXC, transmisin completa. Este bit se activa cuando se han enviado todos los datos del buffer de transmisin. Bit 5 UDRE, registro de datos de la USART vacio. Indica que el buffer UDR esta listo para recibir nuevos datos. Bit 4- FE, error en el frame. Se activa cuando existe un error en el frame de datos recibidos. Bit 3- DOR, data overrun. Si el buffer de recepcin esta lleno y se detecta un nuevo bit de inicio. Bit 2- PE, error de paridad. Si se activo una revisin de paridad (UPM=1) y existe un error de paridad en la transmisin, este bit se activa. Bit 1- U2X, doblador de velocidad USART. Slo tiene efecto en modo asncrono, reduce el divisor de baud rate, razn de velocidad, de 16 a 8, lo que ocasiona que se duplique la velocidad de transmisin. Bit 0- MPCM, modo de comunicacin multiprocesador. Activa el modo de comunicacin multiprocesador, todos los frames recibidos que no contengan informacin de direccin, ,sern ignorados.

8.3.3 Registro de control y estado B de la USART, UCSRB.

Bit 7- RXCIE. Habilitacin de interrupcin por recepcin completa. Bit6- TXCIE. Habilitacin de interrupcin por transmisin completa. Bit5- UDRIE. Habilitacin de interrupcin por registro de datos de USART vacio. Bit4- RCEN. Habilita el receptor del USART. Bit3- TXEN. Habilita el transmisor de la USART. Bit2- UCSZ2. En conjunto con UCSZ1:0, establecen el tamao de bits de datos a utilizar. Bit1- RXB8. Si se escogi un frame de 9 bits de datos, aqu se ubica el noveno bit recibido y debe ser ledo antes de leer los ocho restantes. Bit0- TXB8. Si se escogi un frame de 9 bits de datos, aqu se debe escribir el noveno bit de datos y debe escribirse antes de los ocho restantes.

8.3.4 Registro de control C de la USART, UCSRC.

Bit7-URSEL. Este bit selecciona si se accede al registro UCSRC (URSEL=1) o se selecciona UBRRRH (URSEL=0). Bit6- UMSEL. Modo de operacin de la USART, cero en este bit de la USART opera en modo asncrono, con un uno en este bit opera en forma sncrona. Bit5:4- UPM1:UPM0. Modo de paridad. Las posibles combinaciones para el modo de operacin con paridad se muestran en la siguiente tabla.

UPM1 UPM0 Modo de paridad 0 0 Desactivada 0 1 Reservada 1 0 Activada, paridad par 1 1 Activada, paridad impar Bit 3- USBS. Seleccin de bits de parada. 0=1 bit de parad, 1=2 bits de parada. Bit 2:1- UCSZ1:UCSZ0. En conjunto con UCSZ2, establecen el tamao de bits de datos, de acuerdo a la siguiente tabla. UCSZ2 UCSZ1 UCSZ0 Tamao de datos 0 0 0 5 bits

0 0 0 1 1 1 1

0 1 1 0 0 1 1

1 0 1 0 1 0 1

6 bits 7 bits 8 bits Reservado Reservado Reservado 9 bits

Bit 0- UCPOL. Polaridad de reloj. Slo aplica en modo sncrono y determina la relacin entre el cambio en la salida de datos y la entrada de datos y el reloj de sincrona (XCK); de acuerdo a la siguiente tabla.

UCPOL Cambio de transmisin (TXD) Muestreo de recepcin (RXD) 0 Flanco de subida en XCK Flanco de bajada en XCK 1 Flanco de bajada en XCK Flanco de subida de XCK 8.3.5 Registros de seleccin de baud rate, UBRRH Y UBRRL.

Bit 11:0 UBRR11:UBRR0. Registro de baud rate de la USART.

8.4 Practica del USART 8.4.1 Objetivo Conocer el funcionamiento y los registros que intervienen en la configuracin del USART.

Potrebbero piacerti anche

- 100 circuitos de shields para arduino (español)Da Everand100 circuitos de shields para arduino (español)Valutazione: 3.5 su 5 stelle3.5/5 (3)

- Comunicacion SerialDocumento15 pagineComunicacion SerialFátima Daniela González MateoNessuna valutazione finora

- Práctica 2 Microprocesadores Ii UsartDocumento6 paginePráctica 2 Microprocesadores Ii UsartArturo72Nessuna valutazione finora

- Prácticas de redes de datos e industrialesDa EverandPrácticas de redes de datos e industrialesValutazione: 4 su 5 stelle4/5 (5)

- Protocolo rs232Documento18 pagineProtocolo rs232Jonathan Camacho100% (1)

- 3.5 - CP - CALCULO DE VENTILACION DE SUBESTACION - Rev0Documento3 pagine3.5 - CP - CALCULO DE VENTILACION DE SUBESTACION - Rev0Bruno Figueroa100% (1)

- Comunicacion SerialDocumento6 pagineComunicacion SerialJuan Carlos100% (1)

- Keb Manual en Castellano de La Serie f4c de KebDocumento104 pagineKeb Manual en Castellano de La Serie f4c de Kebeves5100% (1)

- Planeacion y Cotizacion de Una Red LanDocumento41 paginePlaneacion y Cotizacion de Una Red LanMaria Huaman del Aguila78% (9)

- Manual de Instalacion Recloser SchneiderDocumento96 pagineManual de Instalacion Recloser Schneideroscar100% (1)

- ADC en Un AVR - Present PDFDocumento18 pagineADC en Un AVR - Present PDFrickypinaNessuna valutazione finora

- Modulo UsartDocumento37 pagineModulo UsartEduardo GarciaNessuna valutazione finora

- Recepción Serial RS-232 Con PicDocumento31 pagineRecepción Serial RS-232 Con PicDaniel Angelo Alfaro Rodriguez100% (2)

- Pic Comunicación SerialDocumento27 paginePic Comunicación SerialbiomedikarmandoNessuna valutazione finora

- Protocolo I2C DefinicionDocumento9 pagineProtocolo I2C DefinicionNAHUEL IGLESIAS100% (1)

- UARTDocumento24 pagineUARTEduuard Fraa DedrickNessuna valutazione finora

- Capitulo 8 USARTDocumento12 pagineCapitulo 8 USARTfercho2373Nessuna valutazione finora

- Capitulo 8 USARTDocumento20 pagineCapitulo 8 USARTLilia MendozaNessuna valutazione finora

- Comunicación SerialDocumento39 pagineComunicación SerialArom DenimNessuna valutazione finora

- Dimer CadenasDocumento66 pagineDimer CadenasGustavo Adolfo Ramirez PiedrahitaNessuna valutazione finora

- Descripcion Detallada Del Puerto Usart Pic 169f877aDocumento8 pagineDescripcion Detallada Del Puerto Usart Pic 169f877aWillims PonceNessuna valutazione finora

- Protocolo de Comunicación UARTDocumento17 pagineProtocolo de Comunicación UARTJuan PachonNessuna valutazione finora

- Practica 8Documento9 paginePractica 8Isaac Tonatiuh Ayala PérezNessuna valutazione finora

- Use RS232Documento6 pagineUse RS232Gräce Mäggüiie PicöNessuna valutazione finora

- Sesion11-Comunicación Serial 2021-n Sesion11Documento39 pagineSesion11-Comunicación Serial 2021-n Sesion11Johan Christhofer Armas ValenciaNessuna valutazione finora

- Ejemplo de Comunicacion Entre PicsDocumento12 pagineEjemplo de Comunicacion Entre PicsDanielNessuna valutazione finora

- Descripción Del CircuitoDocumento7 pagineDescripción Del CircuitoJavier SarangoNessuna valutazione finora

- Módulo 5 Comunicacion Serial AsincronaDocumento11 pagineMódulo 5 Comunicacion Serial AsincronaMishell Sanchez GuevaraNessuna valutazione finora

- Uart EsDocumento29 pagineUart EsRonal Alexander MontenegroNessuna valutazione finora

- 4 El Puerto Serie USART PICDocumento39 pagine4 El Puerto Serie USART PICjpazmiño_25Nessuna valutazione finora

- Comunicaciones PDFDocumento27 pagineComunicaciones PDFJuan Carlos Lizana FloresNessuna valutazione finora

- El Puerto Serial RS232 2022ADocumento16 pagineEl Puerto Serial RS232 2022AMonse MorenoNessuna valutazione finora

- Comunicación Serial RS232 PIC16F877ADocumento6 pagineComunicación Serial RS232 PIC16F877AEduardohrdz HernandezNessuna valutazione finora

- Basico Serial LeeerDocumento43 pagineBasico Serial LeeerLuis VilchizNessuna valutazione finora

- Previo8 VLSIDocumento3 paginePrevio8 VLSIJosé André Rosario VázquezNessuna valutazione finora

- Uart y UsartDocumento5 pagineUart y UsartMdmrNessuna valutazione finora

- Descripción PIC 16F887Documento47 pagineDescripción PIC 16F887mongongoNessuna valutazione finora

- Puerto Serie y ParaleloDocumento7 paginePuerto Serie y ParaleloYordael BoescheNessuna valutazione finora

- Rs 232Documento20 pagineRs 232Manuel RangelNessuna valutazione finora

- Apuntes AVRDocumento9 pagineApuntes AVRirving_asNessuna valutazione finora

- 09 UsartDocumento46 pagine09 UsartKevin René Alarcón CalderónNessuna valutazione finora

- Configuración Del Módulo de Comunicación SerieDocumento19 pagineConfiguración Del Módulo de Comunicación SerieRonny TituanaNessuna valutazione finora

- RS232Documento8 pagineRS232Luis FernandoNessuna valutazione finora

- La Comunicación SerieDocumento41 pagineLa Comunicación SerieTocho VanegasNessuna valutazione finora

- Comunicacion Serial Con Atmega32Documento6 pagineComunicacion Serial Con Atmega32Daniel GutierrezNessuna valutazione finora

- Puerto SerialDocumento17 paginePuerto SerialCarlos TurrizaNessuna valutazione finora

- Tarea 5. SEDocumento5 pagineTarea 5. SEAldo Sebastián Bustamante JoséNessuna valutazione finora

- 12.el Modulo EUSART PDFDocumento28 pagine12.el Modulo EUSART PDFStephania AlvaradoNessuna valutazione finora

- Comunicación Serial Arduino Diana TorresDocumento10 pagineComunicación Serial Arduino Diana TorresNey Fernando AucapiñaNessuna valutazione finora

- TEMA5Documento21 pagineTEMA5Pablo Limache PeñalozaNessuna valutazione finora

- P10 Comunicacion Serial RS232Documento8 pagineP10 Comunicacion Serial RS232Ans Shel Cardenas YllanesNessuna valutazione finora

- Equipo-6-Trabajo de equpo-USART, EIA232, EIA485, Circuito de Interconexion, Programas de Aplicacion-24 Abril 2020 PDFDocumento43 pagineEquipo-6-Trabajo de equpo-USART, EIA232, EIA485, Circuito de Interconexion, Programas de Aplicacion-24 Abril 2020 PDFRoger VelazquezNessuna valutazione finora

- Todo Sobre El PUERTO SERIE RS 232Documento24 pagineTodo Sobre El PUERTO SERIE RS 232tuco3Nessuna valutazione finora

- Capítulo VI - Comunicación SerialDocumento42 pagineCapítulo VI - Comunicación SerialMoises MezaNessuna valutazione finora

- Lab 7Documento53 pagineLab 7Ern SantosNessuna valutazione finora

- RS232Documento14 pagineRS232Andy FloresNessuna valutazione finora

- USART AVR Comunicación SerialDocumento27 pagineUSART AVR Comunicación SerialMario Mtz Waffles100% (1)

- Tipos de SincroniaDocumento27 pagineTipos de Sincronialuis fuentesNessuna valutazione finora

- La Transmisión Síncrona Es Una Técnica Que Consiste en El Envío de Una Trama de DatosDocumento1 paginaLa Transmisión Síncrona Es Una Técnica Que Consiste en El Envío de Una Trama de DatosПэньялоса СипактлиNessuna valutazione finora

- Usart DspicDocumento28 pagineUsart DspicjairoNessuna valutazione finora

- 4.6 El Puerto Serie Del Microcontrolador 8051 Comunicación SerieDocumento7 pagine4.6 El Puerto Serie Del Microcontrolador 8051 Comunicación SerieCarlos BaezNessuna valutazione finora

- USART (Universal Synchronous Asynchronous Receiver Transmitter)Documento22 pagineUSART (Universal Synchronous Asynchronous Receiver Transmitter)Edson AguirreNessuna valutazione finora

- Comunica C I On SerialDocumento39 pagineComunica C I On SerialMabel Lorena Ochoa ContrerasNessuna valutazione finora

- El Puerto Serie - Uart 8250Documento12 pagineEl Puerto Serie - Uart 8250Sara GuzmannNessuna valutazione finora

- La Comunicación SerieDocumento38 pagineLa Comunicación Seriepereira26Nessuna valutazione finora

- Altezor Arquit CR ContemporaneaDocumento26 pagineAltezor Arquit CR ContemporanearickypinaNessuna valutazione finora

- IT Essentials PC Hadware y Software 4.0 CiscoDocumento34 pagineIT Essentials PC Hadware y Software 4.0 Ciscothe_coolboysNessuna valutazione finora

- Informe Grúa MagnéticaDocumento37 pagineInforme Grúa MagnéticaFercita VásquezNessuna valutazione finora

- Control - JFrame, JDialog, JPanelDocumento3 pagineControl - JFrame, JDialog, JPanelHernan MendozaNessuna valutazione finora

- Frecuencia Respiratoria PDFDocumento12 pagineFrecuencia Respiratoria PDFrickypinaNessuna valutazione finora

- Programacion en C 2da ParteDocumento10 pagineProgramacion en C 2da ParterickypinaNessuna valutazione finora

- Capitulo 3 Interrupciones ExternasDocumento7 pagineCapitulo 3 Interrupciones Externasrickypina0% (1)

- Manejo de Temporizadores AVR Parte 2Documento5 pagineManejo de Temporizadores AVR Parte 2rickypinaNessuna valutazione finora

- Manejo de Temporizadores AVRDocumento17 pagineManejo de Temporizadores AVRrickypina0% (1)

- Capitulo 4 Temporizador ContadorDocumento11 pagineCapitulo 4 Temporizador ContadorcoraztoNessuna valutazione finora

- Ecuaciones de ElectromagnetismoDocumento2 pagineEcuaciones de ElectromagnetismoEnrique NuelNessuna valutazione finora

- Apuntes de Estructura de ComputadoresDocumento406 pagineApuntes de Estructura de ComputadoresA Liz Marjorie T. TineoNessuna valutazione finora

- 6301sp HFP-11Documento4 pagine6301sp HFP-11ogautierNessuna valutazione finora

- Disposición de La Instalación EléctricaDocumento6 pagineDisposición de La Instalación Eléctricaoskar50% (2)

- Fox-Eleyman: Control de AscensorDocumento87 pagineFox-Eleyman: Control de AscensorByron AguilarNessuna valutazione finora

- LUCES GUÍA LED 1W, 2W, 3W y 4W 69-100-LED-2W-30K 65-104-LED-2W-30K 65-103-LED-4W-30K 65-101-LED-3W-30K 65-117-LED-2W-30K Y 05-508-LED-1W-30K - 2Documento1 paginaLUCES GUÍA LED 1W, 2W, 3W y 4W 69-100-LED-2W-30K 65-104-LED-2W-30K 65-103-LED-4W-30K 65-101-LED-3W-30K 65-117-LED-2W-30K Y 05-508-LED-1W-30K - 2Luis VillegasNessuna valutazione finora

- Reporte de FallaDocumento3 pagineReporte de FallaalfredoNessuna valutazione finora

- Utilidad de Los Cables Crossover Rollover1Documento4 pagineUtilidad de Los Cables Crossover Rollover1Kenock FacioNessuna valutazione finora

- Laboratorio 2 Lab Elt 250 DIAGRAMA CIRCULARDocumento15 pagineLaboratorio 2 Lab Elt 250 DIAGRAMA CIRCULARabrahamNessuna valutazione finora

- Tarea 1Documento6 pagineTarea 1santiago romero nopeNessuna valutazione finora

- 8 Cap. 6 Osciladores RFDocumento14 pagine8 Cap. 6 Osciladores RFWinder TorresNessuna valutazione finora

- Circuitos ElectricosDocumento68 pagineCircuitos ElectricosJorge Marres NavarroNessuna valutazione finora

- Practica 2 Diseño de Esquema de Principio para Instalacion FrigorificaDocumento1 paginaPractica 2 Diseño de Esquema de Principio para Instalacion FrigorificaDeuda PendienteNessuna valutazione finora

- Qué Es Una UPSDocumento4 pagineQué Es Una UPSjose205367Nessuna valutazione finora

- Informe Previo 1 EE644N Diseño Lógico DigitalDocumento9 pagineInforme Previo 1 EE644N Diseño Lógico DigitalFRANCK DAVID SORIA PINEDONessuna valutazione finora

- Trabajo de PerforacionDocumento23 pagineTrabajo de PerforacionAlexsander CatuntaNessuna valutazione finora

- Probador de SCRDocumento3 pagineProbador de SCRargenis velasquezNessuna valutazione finora

- Sistema de Encendido - Motores de Combustion InternaDocumento11 pagineSistema de Encendido - Motores de Combustion InternaMarcelo Abel Ramírez CaveroNessuna valutazione finora

- 1 - Distribucion Electrica SchneiderDocumento32 pagine1 - Distribucion Electrica SchneiderWalter Chavez100% (1)

- MEMORIASDocumento51 pagineMEMORIASIsrael JmpNessuna valutazione finora

- Practica 8Documento12 paginePractica 8Denisse García GarcíaNessuna valutazione finora

- Informe ReflexRefracLuz Grupo5 ERDocumento17 pagineInforme ReflexRefracLuz Grupo5 ERBrayan VillamizarNessuna valutazione finora

- CC 20capitulo2aplicacionesDocumento6 pagineCC 20capitulo2aplicacionesErasmo GómezNessuna valutazione finora

- Lab01-C16A-Manejo de Instrumentos Aplicados A La MedicionDocumento10 pagineLab01-C16A-Manejo de Instrumentos Aplicados A La MedicionSteven Dave QRNessuna valutazione finora

- Practica Conta V 2016Documento146 paginePractica Conta V 2016Angel Saul CabreraNessuna valutazione finora

- PIF Circuitos Eléctricos 2Documento4 paginePIF Circuitos Eléctricos 2Diego Alexander Calderon AmayaNessuna valutazione finora