Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Fast Fourier Transform: VLSI Architectures: Vladimir Stojanović

Caricato da

Tharun ThampanTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Fast Fourier Transform: VLSI Architectures: Vladimir Stojanović

Caricato da

Tharun ThampanCopyright:

Formati disponibili

Fast Fourier Transform:

VLSI Architectures

Lecture 10

Vladimir Stojanovi

6.973 Communication System Design Spring 2006

Massachusetts Institute of Technology

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

Pipelined FFT architectures

Examples Radix-2

8 C2 BF2 4 C2

4 BF2 2 C2

2 BF2 j 1 C2

BF2

(1) . R2MDC(N-16)

8 4 BF2 2 BF2 j 1 BF2

BF2

multi-path delay commutator single-path delay feedback single-path delay feedback multi-path delay commutator single-path delay commutator

C4

(2) . R25DF(N-16)

2B4E8F

3X64

3X16 BF4

3X4 BF4

3X1

BF4

BF4

Radix-4

(3) . R4SDF(N-256)

192 128 64 48 32 16 12 8 4 3 2 1

BF4

16 32 48

C4

BF4

4 8 12

C4

BF4

1 2 3

C4

BF4

(4) . R4MDC(N-256)

DC6X64

BF4

DC6X16

BF4

DC6X4

BF4

DC6X1

BF4

(5) . R4SDC(N-256)

Figure by MIT OpenCourseWare.

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

Radix-2 Multi-path Delay Commutator

8 C2 BF2 4 C2 4 BF2 2 C2 2 BF2 j 1 C2 1 BF2

Figure by MIT OpenCourseWare.

The most classical approach for pipeline implementation of radix-2 FFT Input sequence broken into two parallel data streams flowing forward with correct distance between data elements entering the butterfly scheduled by proper delays Both butterflies and multipliers are in 50% utilization

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

Radix-2 Single-path Delay Feedback

8 4 2 1

BF2

BF2

BF2

BF2

Figure by MIT OpenCourseWare.

[Wold & Despain 84]

Uses registers more efficiently

Both as input and the output of the butterfly

A single data stream goes through the multiplier at every stage Multiplier utilization is also 50%

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

Radix-4 Single-path Delay Feedback

[Despain74]

3 X4 3X1

x0 x4 x8 x12 x15

DFT 4

DFT 4 DFT 4 DFT 4 DFT 4

X0 X12 X1 X13 X2 X14 X3 X15

BF4

BF4

Figure by MIT OpenCourseWare. Figure by MIT OpenCourseWare.

x(n) N ) 4 N ) 2

j -1 -j

WN

n

y(n) N ) 4 N ) 2

x(n+

Utilization of multipliers 75%

-j -1 -1 -1

WN

2n

y(n+

x(n+

WN

y(n+

By storing 3 BF4 outputs Butterfly fairly complicated

3N x(n+ ) 4

WN

3n

3N y(n+ ) 4

Radix-4 butterfly utilization only 25%

Figure by MIT OpenCourseWare.

At least 8 complex adders

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

Figure by MIT OpenCourseWare.

6.973 Communication System Design

Radix-4 Multi-path Delay Commutator

[Swartzlander84]

12 C4 8 4 BF4 1 2 3

Figure by MIT OpenCourseWare.

x0

3 C4 2 1 BF4

x4 x8 x12 x15

DFT 4 DFT 4 DFT 4 DFT 4 DFT 4

X0 X12 X1 X13 X2 X14 X3 X15

What is the utilization of

Butterflies? Multipliers?

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

+++

Figure by MIT OpenCourseWare.

x(n) N ) 4 N ) 2

j -1 -j

WN

n

y(n) N ) 4 N ) 2

x(n+

-j -1 -1 -1

WN

2n

y(n+

x(n+

WN

y(n+

3N x(n+ ) 4

WN

3n

3N y(n+ ) 4

Figure by MIT OpenCourseWare.

6.973 Communication System Design

Radix-4 Single-path Delay Commutator

[Bi & Jones 89]

x0

stage 1 stage 2

DFT 4 DFT 4 DFT 4 DFT 4 DFT 4

X0 X12 X1 X13 X2 X14 X3 X15

x4 x8 x12 x15

input

commutator

butterfly element

commutator

butterfly element

c1 c2 c3

c4 c5 c6

coefficient

Figure by MIT OpenCourseWare.

x(n) N ) 4 N ) 2

Figure by MIT OpenCourseWare.

WN

n

y(n) N ) 4 N ) 2

Modified radix-4 algorithm Programmable radix-4 BF 75% utilization Used to build one of the largest single-chip FFTs (8192pts) [Bidet95]

x(n+

-j -1

WN

2n

y(n+

x(n+

-1

WN

-1

y(n+

3N x(n+ ) 4

j -1

-j

WN

3n

3N y(n+ ) 4

Figure by MIT OpenCourseWare.

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

R4SDC commutator and butterfly details

input Nt Nt Nt Nt Nt Nt

1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 5 4 3 2 1 0 15 14 13

1 0

2 1 0 15 14 13 12 11 10 9 8 7 6

T

5 4 3 2 1 0 15 14 13

x(n) input

Time

t'+16T

t'

2:1 multiplexers

mt 0 1 2 3

c1 1 0 0 0

c2 c3 1 1 1 1 0 1 0 0

2 1 0 15 14 13 12 11 10 9 8 7 6

Time

14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 15 14 13 12 11 10 9

Figure by MIT OpenCourseWare.

Outputs from commutator at stage 1

10 9 8 7 6 5 4

3 2 1 0 15 14 13 12 11 10 9 8 7

6 5

6 5 4 3 2 1 0 15 14 13 12 11 10 9

8 7

6 5 4

3 2 1

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 stage 1

0 0 0 0 1 1 1 1 2 2 2 2 3 3 3 3

0 0 0 0 0 1 2 3 0 2 4 6 0 3 6 9 stage 2

0 1 2 3 0 1 2 3 0 1 2 3 0 1 2 3

0 4 8 12 1 5 9 13 2 6 10 14 3 7 11 15

t'+2 8 T m =3 1 m1= 2 m1= 1

t'+12T m1= 0

Figure by MIT OpenCourseWare.

re (0) im (0) re (1) im (1) re (2) im (2) re (3) im (3)

add/sub add/sub add/sub D add/sub add/sub add/sub Im Re

mt 0 1 2 3

c4 0 1 0 1

c5 0 0 1 1

c6 (0 = addition, 1 = subtraction) 0 1 1 0

Figure by MIT OpenCourseWare.

Figure by MIT OpenCourseWare.

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

Some conclusions

Delay feedback approaches are always more efficient than corresponding delay-commutator approaches

In terms of memory utilization

Since butterfly outputs share same storage with its inputs

Pipeline architectures require FFT algorithms to be formulated in a hardware-oriented form

Where spatial regularity is preserved in a signal-flow graph (SFG) So that arithmetic operations can be tightly scheduled for efficient hardware utilization

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

Decomposition a review

Twiddle factor is Nth primitive root of unity

With exponent evaluated modulo N

Most fast algorithms share same general strategy

Map one-dimensional transform int a two or multidimensional representation

Exploit congruence property of coefficients to simplify computation

Unlike traditional step-by-step decomposition of twiddle factors

Cascading the twiddle factor decomposition leads to new forms of FFT with high-spatial regularity

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

10

Radix 22 approach

Start by classical divide-and-conquer radix-2 DIF indexing

But, consider the first two steps of decomposition together

[Shouseng and Torkelson 1996]

Compute directly in standard radix-2 approach New idea is to proceed to shorter DFTs cascading the twiddle factor WN(N/4n2+n3)k1

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

11

A 16pt example

Get radix-4-like mulitplier complexity with radix-2 butterfly structures (radix-22)

N/4 DFT

(k1=0, k2=0) W0 W2 W4 W6 W0 W1 W2 W3 W0 W3 W W9 BF II

6

x(0) x(1) x(2) x(3) x(4) x(5) x(6) x(7) x(8) x(9) x(10) x(11) x(12) x(13) x(14) x(15) BF I

X(0) X(8) X(4) X(12) X(2) X(10) X(6) X(14) X(1) X(9) X(5) X(13) X(3) X(11) X(7) X(15)

N/4 DFT

(k1=0, k2=1)

N/4 DFT

(k1=1, k2=0)

-j -j -j -j

N/4 DFT

(k1=1, k2=1)

x(0) x(1) x(2) x(3) x(4) x(5) x(6) x(7) x(8) x(9) x(10) x(11) x(12) x(13) x(14) x(15) BF I

X(0) X(8) -j W2 W4 W6 W1 W2 W3 -j -j -j -j BF II W3 W6 W9 BF III -j BF IV -j X(4) X(12) X(2) X(10) X(6) X(14) X(1) X(9) X(5) X(13) X(3) X(11) X(7) X(15)

-j

Figure by MIT OpenCourseWare.

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

12

A 64pt radix-22 example

Image removed due to copyright restrictions.

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

13

Radix-22 (R22SDF) architecture

N=256

x(n)

clk

128 BF2I

X

64 BF2II

t

X

32 BF2I

X

16 BF2II

t

X

8 BF2I

X

4 BF2II

2 BF2I

1 BF2II

t

X

X(k)

W1(n)

7 6 5 4

W2(n)

3 2

W3(n)

1 0

Figure by MIT OpenCourseWare.

0 + + + + + 1 0 1 1 0 1 0

xr(n) xi(n) xr(n+N/2) xi(n+N/2)

+ +

0 1 0 1 1 0 1 0 x

xr(n) xi(n) xr(n+N/2) xi(n+N/2)

zr(n+N/2) zi(n+N/2) zr(n) zi(n)

-+ -+ (i). BF2I

Similar to R2SDF

Reduced number of multipliers

Figure by MIT OpenCourseWare.

(ii). BF2II

t x

Need two types of butterflies

One identical to that in R2SDF The other contains the logic for trivial twiddle factor multiplication (with j) Just a log2N binary counter

Figure by MIT OpenCourseWare.

Synchronization control very simple due to spatial regularity

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

14

Radix-22 architecture Sync control

log2N-bit binary counter

On first N/2 cycles, 2-to-1 mux in BF1 switch to 0

Synchronization controller Address counter for twiddle factor reading in each stage Butterfly is idle (input data directed to shift registers) Butterfly computes a 2pt DFT with incoming data and data stored in the shift registers Output Z1(n) sent to twiddle multiplier Output Z1(n+N/2) sent back to the shift register to be multiplied in next N/2 cycles, when the first half of the next frame is loaded in

128 64 BF2II

t

X

On next N/2 cycles, muxes in BF1 switch to 1

32 BF2I

X

16 BF2II

t

X

8 BF2I

X

4 BF2II

2 BF2I

1 BF2II

t

X

x(n)

clk

BF2I

X

X(k)

W1(n)

7 6 5 4

Operation of BF2 is similar, except the distance of butterfly input sequence is just N/4 and the trivial multiply logic Utilization of the multiplier is 75% Next frame can be computed w/o pausing due to the pipelined processing in each stage Pipeline register can be inserted between each multiplier and BF stage to improve the performance

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

W2(n)

3 2

W3(n)

1 0

Figure by MIT OpenCourseWare.

15

Arithmetic complexity

multiplier #

R2MDC R2SDF R4SDF R4MDC R4SDC R22SDF 2(log4 N - 1) 2(log4 N - 1) log4 N - 1 3(log4 N - 1) log4 N - 1 log4 N - 1

adder #

4 log4 N 4 log4 N 8 log4 N 8 log4 N 3 log4 N 4 log4 N

memory size

3N/2 - 2 N-1 N-1 5N/2 - 4 2N - 2 N-1

control

simple simple medium simple complex simple

Figure by MIT OpenCourseWare.

R22SDF has reached minimum requirement for both multiplier and storage Only R4SDC better in terms of adder usage R22SDF well suited for VLSI implementations of pipeline FFT processors

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

16

Memory issues

The area/power consumption in the pipeline architectures dominated by the

FIFO register files at each stage Complex multipliers at each (or every other stage)

To diminish the unnecessary data moving in the FIFO need to reconstruct the storage

A known approach is to use FIFO with 2-port RAM

With read and write addresses displaced by a constant 2-port RAM cells 33% more area of the 1-port RAM cell

Use two N/2 1-port RAMs

b D(n) a

E E E

D(n-N)

D(n)

lxN 2-port RAM

D(n-N)

Read and write interleaved Each active every other cycle

R/W

N/2-1 RAM N/2-1 RAM Addr.

W-addr. W R

R-addr.

Figure by MIT OpenCourseWare.

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

Figure by MIT OpenCourseWare.

6.973 Communication System Design

17

Single stage hardware example

x[0] x[1] x[2] x[3] x[4] x[5] x[6] x[7] W -1 -1

3

W -1

W -1

W -1

X[0] X[4]

S/P & Bit reverse N/r Butterflies

W -1 W

W -1

W -1

X[2] X[6]

W -1 W -1

W -1

X[1] X[5]

W -1

X[3] X[7]

Coeff ROM Counter Control Circuits

N TFFT = r . logrN .Tr,PE Where, N/r = No. of butterfly per stage logrN = No. of stage Tr,PE = Time to calculate one butterfly

Figure by MIT OpenCourseWare.

Figure by MIT OpenCourseWare.

Fold stages onto each other

[Sadat2001]

Need constant geometry signal flow graph Big price in area for parallelism (within each stage)

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

18

P/S

Radix-8 Pipelined/Parallel implementation

A 64pt FFT example for 802.11a

[Excerpted from Maharatna et al 2004]

Two dimensional structure of 8pt FFTs

The number of nontrivial complex multiplications is 49 (7x7)

Since the first twiddle is always 1

The number of nontrivial complex multiplications for radix-2 FFT is 66 Radix-4 (or 22) FFTs need only 52 multiplies

Important to note that for 8pt FFT (DIT) no need for multiplies

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

19

8pt DIT FFT

Figure from Maharatna, K., E. Grass, and U. Jagdhold. "A 64-point Fourier Transform Chip for High-speed Wireless LAN Application Using OFDM." Solid-State Circuits 39 (2004): 484-493. Copyright 2004 IEEE. Used with permission.

The only nontrivial multiply is with 1/sqrt(2)

Easily realize using hardwired shift-and-add

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

20

Block diagram of the FFT unit

Figure from Maharatna, K., E. Grass, and U. Jagdhold. "A 64-point Fourier Transform Chip for High-speed Wireless LAN Application Using OFDM." Solid-State Circuits 39 (2004): 484-493. Copyright 2004 IEEE. Used with permission.

Two-stages are pipelined

Fully parallel in each stage (radix-2 8pt FFT, single clk cycle) Large number of global wires resulting from the multiplexing of complex data to the 8-point FFTs Construction of the multiplier unit to attain the required speed with minimal silicon are is not trivial

Two performance bottlenecks

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

21

Input unit

Hard wired outputs and data shifting

To the 8pt FFT Reduce de-muxing Reduce global wires Multiplier cannot finish Extend latency

Cannot shift every clk

Temporary registers 1,2,3

Figure from Maharatna, K., E. Grass, and U. Jagdhold. "A 64-point Fourier Transform Chip for High-speed Wireless LAN Application Using OFDM." Solid-State Circuits 39 (2004): 484-493. Copyright 2004 IEEE. Used with permission.

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

22

Multiplier unit

49 multiplies

Only nine sets unique (cos,sin)

hard-wired constant

Significantly less storage space

for coefficients

Turn multiplies into shift&add

Figure from Maharatna, K., E. Grass, and U. Jagdhold. "A 64-point Fourier Transform Chip for High-speed Wireless LAN Application Using OFDM." Solid-State Circuits 39 (2004): 484-493. Copyright 2004 IEEE. Used with permission.

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

23

Multiplier unit and scheduling

Figures from Maharatna, K., E. Grass, and U. Jagdhold. "A 64-point Fourier Transform Chip for High-speed Wireless LAN Application Using OFDM." Solid-State Circuits 39 (2004): 484-493. Copyright 2004 IEEE. Used with permission.

Some of the coefficients requested concurrently by different FFT outputs

~50% less power and area than 8 standard complex multipliers Buffer unit similar to input unit, just w/o temporary registers

Solve by adding temp registers in the input unit

Outputs also hardwired with distance of 8

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

24

Output unit

A mirror of input unit

Just w/o temporary registers 5-bit counter

Control/sync is simple

Starts counting when in put full Local counters control Input Intermediate Output units

Figure from Maharatna, K., E. Grass, and U. Jagdhold. "A 64-point Fourier Transform Chip for High-speed Wireless LAN Application Using OFDM." Solid-State Circuits 39 (2004): 484-493. Copyright 2004 IEEE. Used with permission.

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 C ommunication System Design

25

Readings

[1] H.e. Shousheng and M. Torkelson "A new approach to pipeline FFT processor," Parallel Processing Symposium, 1996., Proceedings of IPPS '96, The 10th International no. SN -, pp. 766-770, 1996.

[3] H.e. Shousheng and M. Torkelson "Designing pipeline FFT processor for OFDM (de)modulation," Signals, Systems, and Electronics, 1998. ISSSE 98. 1998 URSI International Symposium on no. SN -, pp. 257-262, 1998.

[2] E. Wold and Alvin M. Despain "Pipeline and Parallel-Pipeline FFT Processors for VLSI Implementations," IEEE Trans. Computers vol. 33, no. 5, pp. 414-426, 1984. [3] G. Bi and E.V. Jones "A pipelined FFT processor for word-sequential data," Acoustics, Speech, and Signal Processing [see also IEEE Transactions on Signal Processing], IEEE Transactions on vol. 37, no. 12 SN - 0096-3518, pp. 1982-1985, 1989. [4] K. Maharatna, E. Grass and U. Jagdhold "A 64-point Fourier transform chip for highspeed wireless LAN application using OFDM," Solid-State Circuits, IEEE Journal of vol. 39, no. 3 SN - 0018-9200, pp. 484-493, 2004. Interesting DIT&F algorithm

[4] C. Chiu, W. Hui, T.J. Ding and J.V. McCanny "A 64-point Fourier transform chip for video motion compensation using phase correlation," Solid-State Circuits, IEEE Journal of vol. 31, no. 11 SN 0018-9200, pp. 1751-1761, 1996.

Power-performance estimation

[2] S. Hong, S. Kim, M.C. Papaefthymiou and W.E. Stark "Power-complexity analysis of pipelined VLSI FFT architectures for low energy wireless communication applications," Circuits and Systems, 1999. 42nd Midwest Symposium on vol. 1, no. SN -, pp. 313-316 vol. 1, 1999. [3] K. Pagiamtzis and P.G. Gulak "Empirical performance prediction for IFFT/FFT cores for OFDM systems-on-a-chip," Circuits and Systems, 2002. MWSCAS-2002. The 2002 45th Midwest Symposium on vol. 1, no. SN -, pp. I-583-6 vol.1, 2002.

Cite as: Vladimir Stojanovic, course materials for 6.973 Communication System Design, Spring 2006. MIT OpenCourseWare (http://ocw.mit.edu/), Massachusetts Institute of Technology. Downloaded on [DD Month YYYY].

6.973 Communication System Design

26

Potrebbero piacerti anche

- Cd300m Parts BreakdownDocumento10 pagineCd300m Parts BreakdownAmanda FitzgeraldNessuna valutazione finora

- Wind Load Analysis For Open StructureDocumento3 pagineWind Load Analysis For Open Structurehitesh gandhiNessuna valutazione finora

- TCAD SimulationDocumento46 pagineTCAD SimulationmahdichiNessuna valutazione finora

- S211-7-2020 Operator's Manual (English) PDFDocumento119 pagineS211-7-2020 Operator's Manual (English) PDFDiego Castañeda SantaNessuna valutazione finora

- Desktop Publishing Advertisement RubricDocumento1 paginaDesktop Publishing Advertisement Rubricapi-364316996Nessuna valutazione finora

- Section 2 Airwothiness of Civil Aviation RequirementsDocumento21 pagineSection 2 Airwothiness of Civil Aviation Requirementssuryaame67% (3)

- Phạm Lê Ngọc Sơn - 2051185 - - DSP - LAB3 - - FINALDocumento25 paginePhạm Lê Ngọc Sơn - 2051185 - - DSP - LAB3 - - FINALNgọc Khánh100% (1)

- Integer Optimization and its Computation in Emergency ManagementDa EverandInteger Optimization and its Computation in Emergency ManagementNessuna valutazione finora

- Communication System DesignDocumento39 pagineCommunication System Designsriblue7Nessuna valutazione finora

- Digital Signal ProcessingDocumento7 pagineDigital Signal ProcessingJagadeesh KumarNessuna valutazione finora

- Instructions For Running PrepVLF and Inv2DVLF 2 DDocumento12 pagineInstructions For Running PrepVLF and Inv2DVLF 2 Dpro100% (2)

- A Novel Architecture of RNS Based Lifting Integer Wavelet Transform (Iwt) and Comparative Study With Other Binary and Non-Binary DWTDocumento9 pagineA Novel Architecture of RNS Based Lifting Integer Wavelet Transform (Iwt) and Comparative Study With Other Binary and Non-Binary DWTAnonymous e4UpOQEPNessuna valutazione finora

- RK4 MethodDocumento6 pagineRK4 MethodfurqanhamidNessuna valutazione finora

- SOLDSPX06Documento16 pagineSOLDSPX06Shafayet UddinNessuna valutazione finora

- Lab#4 ReportDocumento14 pagineLab#4 ReportShameen MazharNessuna valutazione finora

- Question Paper Code:: Reg. No.Documento3 pagineQuestion Paper Code:: Reg. No.DhariniJeevanandamNessuna valutazione finora

- Power SystemDocumento17 paginePower Systemprachi singhNessuna valutazione finora

- Yogendra Singh Rajpoot (1883930050) DSP FILEDocumento42 pagineYogendra Singh Rajpoot (1883930050) DSP FILEYogendra Singh RajpootNessuna valutazione finora

- PSpice Quick Guide and TutorialDocumento5 paginePSpice Quick Guide and TutorialchikiiduckNessuna valutazione finora

- Applications of Adjoint TheoryDocumento18 pagineApplications of Adjoint TheoryaliNessuna valutazione finora

- HST.582J / 6.555J / 16.456J Biomedical Signal and Image ProcessingDocumento3 pagineHST.582J / 6.555J / 16.456J Biomedical Signal and Image ProcessingShafayet UddinNessuna valutazione finora

- A Pipelined 8x8 2-D Forward DCT Hardware Architecture For H.264/AVC High Profile EncoderDocumento11 pagineA Pipelined 8x8 2-D Forward DCT Hardware Architecture For H.264/AVC High Profile EncoderAnil KumarNessuna valutazione finora

- Applied SciencesDocumento23 pagineApplied SciencesSindhu KamathNessuna valutazione finora

- SKMM 1013 Sem I 2013/14: Faculty of Mechanical Engineering Universiti Teknologi MalaysiaDocumento8 pagineSKMM 1013 Sem I 2013/14: Faculty of Mechanical Engineering Universiti Teknologi MalaysiaWan Abdul HadiNessuna valutazione finora

- Symbolic Analysis of Continuous Beams: Husain Jubran Al-GahtaniDocumento9 pagineSymbolic Analysis of Continuous Beams: Husain Jubran Al-GahtaniSç-č AbabiiNessuna valutazione finora

- Digital Signal Processing (Old) April2013Documento1 paginaDigital Signal Processing (Old) April2013avinashavi93Nessuna valutazione finora

- HST.582J / 6.555J / 16.456J Biomedical Signal and Image ProcessingDocumento16 pagineHST.582J / 6.555J / 16.456J Biomedical Signal and Image ProcessingShafayet UddinNessuna valutazione finora

- Efficient Hardware Implementation of Hybrid Cosine-Fourier-Wavelet Transforms On A Single FPGADocumento4 pagineEfficient Hardware Implementation of Hybrid Cosine-Fourier-Wavelet Transforms On A Single FPGANj NjNessuna valutazione finora

- B.Tech (EC, VI SEM) : Ii) All Questions Carry Equal MarksDocumento2 pagineB.Tech (EC, VI SEM) : Ii) All Questions Carry Equal MarksRajNessuna valutazione finora

- Digital Control Tutorial No 2Documento10 pagineDigital Control Tutorial No 2Mary DunhamNessuna valutazione finora

- r05320201 Digital Signal ProcessingDocumento8 paginer05320201 Digital Signal ProcessingBharath LudiNessuna valutazione finora

- Error Tolerant AdderDocumento21 pagineError Tolerant AdderGnrajesh RajeshNessuna valutazione finora

- Design and Implementation of A High-Speed, Low-Power VLSI Chip For The DCT TransformDocumento34 pagineDesign and Implementation of A High-Speed, Low-Power VLSI Chip For The DCT TransformEric DharanNessuna valutazione finora

- 338 Power Systems Electromagnetic Transients Simulation: Figure A.7 PSCAD/EMTDC Ow ChartDocumento14 pagine338 Power Systems Electromagnetic Transients Simulation: Figure A.7 PSCAD/EMTDC Ow ChartkjfenNessuna valutazione finora

- DSPQNANSDocumento16 pagineDSPQNANSEmmanuel Aron JoshuaNessuna valutazione finora

- Model Exam DSPDocumento2 pagineModel Exam DSPChristoNessuna valutazione finora

- Flobaroid PDFDocumento11 pagineFlobaroid PDFAyman DamounNessuna valutazione finora

- Efficient Implementation of A Pseudorandom Sequence Generator For High-Speed Data CommunicationsDocumento8 pagineEfficient Implementation of A Pseudorandom Sequence Generator For High-Speed Data CommunicationsRekhaPadmanabhanNessuna valutazione finora

- Submitted To: Dr. Tushar Kanti Roy Associate Professor Dept. of ETE, RUET Submitted By: Name: Aminur Rahman Bahar Roll: 1704033 Year: 3 Year (ODD) Submission Date: 23-08-21Documento6 pagineSubmitted To: Dr. Tushar Kanti Roy Associate Professor Dept. of ETE, RUET Submitted By: Name: Aminur Rahman Bahar Roll: 1704033 Year: 3 Year (ODD) Submission Date: 23-08-21mbchNessuna valutazione finora

- Fpga Implementation of FFT Algorithm For Ieee 802.16E (Mobile Wimax)Documento7 pagineFpga Implementation of FFT Algorithm For Ieee 802.16E (Mobile Wimax)soumyaNessuna valutazione finora

- EE223-Signals & Systems: Remote Final Exam Total Time: 03 Hours Total Marks: 100 Course InstructorDocumento4 pagineEE223-Signals & Systems: Remote Final Exam Total Time: 03 Hours Total Marks: 100 Course InstructorMuhammad AbdullahNessuna valutazione finora

- Ece603 Unified Electronics Laboratory Lab ManualDocumento39 pagineEce603 Unified Electronics Laboratory Lab ManualSuneel JaganNessuna valutazione finora

- Cours Formation Math CommDocumento27 pagineCours Formation Math CommsamvipNessuna valutazione finora

- Experimental Modal Analysis: Gaetan Kerschen - Jean-Claude GolinvalDocumento24 pagineExperimental Modal Analysis: Gaetan Kerschen - Jean-Claude Golinvalthrust123Nessuna valutazione finora

- DE PaperDocumento4 pagineDE Paperbhaveshgupta098Nessuna valutazione finora

- MATLAB Programs, For 7th Sem CSE Students - Tushar KantDocumento4 pagineMATLAB Programs, For 7th Sem CSE Students - Tushar KantJámès KõstãNessuna valutazione finora

- Gate-Level Minimization: M.ShoaibDocumento61 pagineGate-Level Minimization: M.ShoaibShoaib MushtaqNessuna valutazione finora

- DSP Lab QP 12 Final ExamDocumento11 pagineDSP Lab QP 12 Final ExamAdarsh AmruthNessuna valutazione finora

- Vlsidsp Chap4 PDFDocumento33 pagineVlsidsp Chap4 PDFgaru1991Nessuna valutazione finora

- Code - No: 07A6EC01: HN Eun HT e Btut HT Te Ut HN e UnDocumento8 pagineCode - No: 07A6EC01: HN Eun HT e Btut HT Te Ut HN e UnSai SivaNessuna valutazione finora

- 2011-The Matlab Reservoir Simulation ToolboxDocumento29 pagine2011-The Matlab Reservoir Simulation ToolboxJoydogNessuna valutazione finora

- DSP Objective Type QuestionsDocumento15 pagineDSP Objective Type QuestionsAdnan Zahid67% (3)

- Huynh Khac TuanDocumento12 pagineHuynh Khac TuanfredyNessuna valutazione finora

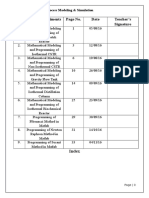

- Process Modeling & Simulation FileDocumento37 pagineProcess Modeling & Simulation FileJagjit SinghNessuna valutazione finora

- CS 294-73 Software Engineering For Scientific Computing Lecture 13: Homework 3 Final ProjectDocumento47 pagineCS 294-73 Software Engineering For Scientific Computing Lecture 13: Homework 3 Final ProjectEdmund ZinNessuna valutazione finora

- DSP1Documento6 pagineDSP1Santosh BanNessuna valutazione finora

- Low-Cost Design of Serial-Parallel Multipliers Over GF (2) Using Hybrid Pass-Transistor Logic (PTL) and CMOS LogicDocumento4 pagineLow-Cost Design of Serial-Parallel Multipliers Over GF (2) Using Hybrid Pass-Transistor Logic (PTL) and CMOS LogicRamadasu PoornimaNessuna valutazione finora

- r05320201 Digital Signal ProcessingDocumento8 paginer05320201 Digital Signal ProcessingSri LalithaNessuna valutazione finora

- Digital Basic - 1 PDFDocumento6 pagineDigital Basic - 1 PDFjeravi84Nessuna valutazione finora

- Chapter 4 Exercise and H.W. AssignmentDocumento76 pagineChapter 4 Exercise and H.W. AssignmentMuhammad HasSanNessuna valutazione finora

- Analytical Modeling of Wireless Communication SystemsDa EverandAnalytical Modeling of Wireless Communication SystemsNessuna valutazione finora

- A Survey of Computational Physics: Introductory Computational ScienceDa EverandA Survey of Computational Physics: Introductory Computational ScienceNessuna valutazione finora

- Performance Evaluation by Simulation and Analysis with Applications to Computer NetworksDa EverandPerformance Evaluation by Simulation and Analysis with Applications to Computer NetworksNessuna valutazione finora

- S3F94xx BatteryCharger An REV000 060109-0Documento40 pagineS3F94xx BatteryCharger An REV000 060109-0Jack ChanNessuna valutazione finora

- How To Install Openbravo ERP On Debian LennyDocumento4 pagineHow To Install Openbravo ERP On Debian LennyfromemNessuna valutazione finora

- ADPDocumento165 pagineADPmohhizbarNessuna valutazione finora

- Legend: Add Subject Remove Subject: Student Number Name of StudentDocumento32 pagineLegend: Add Subject Remove Subject: Student Number Name of StudentJake ChesterphilNessuna valutazione finora

- Calculating The Volume of A Stainless Steel WeldDocumento6 pagineCalculating The Volume of A Stainless Steel WeldOkayNessuna valutazione finora

- J Fluids Engineering 2009 Vol 131 N4Documento120 pagineJ Fluids Engineering 2009 Vol 131 N4Нильва АлександрNessuna valutazione finora

- Falcon BMS Keyfile Manual PDFDocumento37 pagineFalcon BMS Keyfile Manual PDFAlessandro MigliardiNessuna valutazione finora

- Command Configure v41 Install Guide en UsDocumento26 pagineCommand Configure v41 Install Guide en Us733Nessuna valutazione finora

- Road Geometry & Transition CurveDocumento8 pagineRoad Geometry & Transition CurveNann Kay Thari KyawNessuna valutazione finora

- IRFP240Documento8 pagineIRFP240Hugo JimenezNessuna valutazione finora

- NexstarcommprotDocumento8 pagineNexstarcommprotskirmixNessuna valutazione finora

- Saskatchewan Drivers HandbookDocumento175 pagineSaskatchewan Drivers HandbookdrivershandbooksNessuna valutazione finora

- SE160 e BrochureDocumento2 pagineSE160 e BrochureAprilia KrisnawatiNessuna valutazione finora

- Artikel 7Documento8 pagineArtikel 7Andri PratamaNessuna valutazione finora

- 7-Strengthening Mechanisms - SlidesDocumento74 pagine7-Strengthening Mechanisms - SlidesRyan TorresNessuna valutazione finora

- Civil & Environmental Engineering: Dept. Report October 2002Documento40 pagineCivil & Environmental Engineering: Dept. Report October 2002Leonardo HernandezNessuna valutazione finora

- Icom en YcivDocumento124 pagineIcom en YcivDavid Lemos SanchezNessuna valutazione finora

- Parts Guide ER-A150VM ER-A170VM: ModelDocumento11 pagineParts Guide ER-A150VM ER-A170VM: ModelmohammedNessuna valutazione finora

- Google Gender Pay LawsuitDocumento31 pagineGoogle Gender Pay LawsuitUSA TODAYNessuna valutazione finora

- High Precision Ball Berings GMNDocumento72 pagineHigh Precision Ball Berings GMNSilvio Busdraghi AmorosoNessuna valutazione finora

- TSI 271210 GHH Two-Stage Compressor Repair InstructionsDocumento18 pagineTSI 271210 GHH Two-Stage Compressor Repair InstructionsMax HudsonNessuna valutazione finora

- Zahvalnica Bla BlaDocumento2 pagineZahvalnica Bla BlaBiljanaJanjušević100% (1)

- 11 - Hashing PDFDocumento24 pagine11 - Hashing PDFKealeboga Duece ThoboloNessuna valutazione finora

- Rockwell Automation TechED 2018 - SY10 - Lab Manual - Integrating CENTERLINE® Motor Control Centers With Studio 5000® and IntelliCENTER® SoftwareDocumento23 pagineRockwell Automation TechED 2018 - SY10 - Lab Manual - Integrating CENTERLINE® Motor Control Centers With Studio 5000® and IntelliCENTER® SoftwareAlex RivasNessuna valutazione finora

- C426Documento5 pagineC426Rufo CascoNessuna valutazione finora