Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

EE214 OTA Design Project

Caricato da

Ibrahim MuhammedDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

EE214 OTA Design Project

Caricato da

Ibrahim MuhammedCopyright:

Formati disponibili

EE214 Autumn 06/07 B.

Murmann

Page 1 of 6

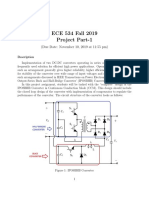

DESIGN PROJECT (Due: Friday, December 8, 2006, 5pm PT) 1. Overview You are to design a fully differential OTA for a switched capacitor circuit application. Figure 1 shows a model of the overall circuit in the relevant phase of operation. The following target specifications apply:

Parameter Technology Operating Temperature VDD Power Dissipation CL Cs Cf Current Mirror Ratios1 Pole/Zero cancellation and left half plane zeros CMFB Circuit Reference Current Dynamic Range Settling Time2 Static Settling Error Dynamic Settling Error Specification EE214 0.35m CMOS, Nominal Corner 25C 3V Minimize 2pF 4pF 0.5Cs 20 Forbidden Ideal, as in homework 6 Single ideal current source of arbitrary value, with positive node tied to VDD or negative node tied to GND 86dB 10ns 0.1% 0.05%

Cf CL Cs + Vsd Cs CL Cf Vid Vod +

Figure 1

Diode connected devices cannot drive more than the specified number of same-size unit devices. Measured for a differential input step that transitions from 0V at t=0 to the maximum input voltage of the circuit in 0.5ns. The maximum input corresponds to the maximum output voltage used in the dynamic range calculation, divided by the closed loop gain.

2

Last modified 11/6/2006 11:07:00 AM

EE214 Autumn 06/07 B. Murmann

Page 2 of 6

Key choices to be made in this design problem include: o o o o Amplifier topology Output signal range Input and output common mode levels Device sizes and bias currents

In addition to the design at nominal specifications indicated above, you will conclude this project by running two additional sets of simulations at worst case process and temperature corners fast devices operated at 0C, and slow devices at 125C. For simplicity in this short project, you are not required to meet the specifications at these conditions. The purpose of this addition is to give you a feel for the impact of temperature and process variations. In practice, you would overdesign your circuit such that the given specs are met across all corners and conditions. You may work on this project alone or in teams of two. Each team must submit one copy of the deliverables specified below. You are encouraged to discuss the design problem with other teams, but your design must be unique. Under no circumstances should you exchange computer files with other teams; this would constitute a gross violation of the honor code. 2. Suggested Design Flow As you might find out, this problem has many more degrees of freedom than any problem you have dealt with so far. Hence, we suggest that you organize your time and work e.g. as follows a) Read this entire handout thoroughly. b) Find a project partner (if you havent already done so). c) Download the starter file project_example.zip or copy the files available in /usr/class/ee214/project/ into your working directory. Examine and understand the included files, run the various included simulations on the provided example circuit. d) Familiarize yourself with the design example presented in lecture 20. Try to duplicate the results and/or modify the specs to meet some of the requirements of this project (e.g. dynamic range). e) Pay special attention to lectures 18-23; this material will provide you with the last few pieces of information needed to complete this assignment. f) Decide about the circuit architecture and begin the design. In the spirit of the design example presented in class, develop a spreadsheet or Matlab script that allows you to optimize your design iteratively without repetitive Spice monkeying. You may want to begin with a small-signal based design (as done in class), and later include transient settling considerations. g) Begin to write your project report (see below) at least several days before the deadline. Your grade will strongly depend on the quality of your write-up, and not just the achieved power dissipation. Finally, and this is important: DONT WAIT UNTIL THE LAST MINUTE TO START. This project involves a great deal of just plain old labor; it takes significant amounts of time to determine suitable design choices, run all the necessary simulations and document your work. Also, the instructional computers and printers have been known to slow down and even go down

Last modified 11/6/2006 11:07:00 AM

EE214 Autumn 06/07 B. Murmann

Page 3 of 6

at the worst possible times, to say nothing of license availability problems. We will be largely unsympathetic to pleas for extensions arising from such problems. 3. Deliverables a) Electronic Submission of Circuit Netlist You are required to submit an electronic copy of your final design netlist. Details regarding this submission and subtleties of file formatting will be communicated to you in a separate handout. b) Project Report You are required to prepare a hardcopy report with the following format (a hand-written report is just fine). In case you decide to submit a computer generated report, make sure to use font sizes greater than 10. Be sure to follow the format instructions below EXACTLY: Page 0: Cover Page Page 1: Outline of your design, justifications of key design decisions; comparison with alternatives. Page 2: Schematic diagram of final design, with component values and bias currents clearly labeled. Show component values right next to the components, and currents next to the branches (i.e., absolutely, positively do not make us refer to a look-up table). Annotate all transistors with the chosen gm/ID value. Pages 3-5: Calculation of key design parameters, such as transconductances, bias currents, etc. Be sure to include a calculation of the circuits settling time. Compare hand calculated values with final HSpice values in a table and discuss discrepancies. Make sure to include the total power dissipation of your design (calculation and HSpice). This is one of the most important sections of your report! The lowest power designs will not automatically score the highest grades. The methodology you used to justify your design choices and component values is far more important (see section on point distribution below). Page 6: Bode plot of T(j), phase and magnitude. Clearly annotate the achieved low frequency loop gain, the loop crossover frequency and the phase margin. Page 7: Plots the simulated settling transient of Vod (no zoom, show the entire waveform). In a separate subplot, show the % error of the differential output voltage relative to the ideal output voltage. Zoom into the relevant region of the settling, i.e. clearly demonstrate that your design settles within spec. Annotate the achieved settling time and static settling error. For simplicity, we use the error at t=30ns as an estimate of the static settling error. Page 8: Plot the common mode output voltage versus time during transient settling of the circuit. In separate subplots each, also show the differential output current of the OTA, and the differential input to the OTA (Vid in Figure 1). Page 9: Plot of the noise power spectral density at the OTA output (Vod) and noise integral. Annotate the total integrated noise value and the achieved dynamic range. Page 10: Output range. Simulation plot showing the differential open loop DC gain Vod/Vid of the amplifier. Mark the differential output voltage at which the gain has dropped by 30%. This value should be larger than the peak output voltage used in your dynamic range calculation. Page 11-12: Results of corner simulations. Tabulate your circuits performance for the slow/hot and fast/cold corner. Include settling time, static error, and any other parameter that you find noteworthy. Include the %-changes with respect to nominal conditions in your table. In case the

Last modified 11/6/2006 11:07:00 AM

EE214 Autumn 06/07 B. Murmann

Page 4 of 6

circuit is non-functional in these corners, investigate and explain the problem (no need to fix the circuit). Include selected interesting plots documenting corner performance and/or issues. Page 13: Comments and Conclusion. Here, you can convey issues you may have had, or things youve learned/not learned in this project. 4. HSpice Testbench We will use the testbench provided as part of the starter files to evaluate your design in HSpice. The testbench is illustrated schematically in Figure 2 below. The 10gig helper resistors are needed to properly initialize capacitor charges in the operating point of the circuit (Note that in practice, this will be accomplished using dedicated switches in the final switched capacitor circuit).

10gig Cs Vsp Y Vsm Cs 10gig

Differential Looptest

CL Cf Vom X Vop Cf CL

Vsc Vsd

Diffdrive

Vsp Vsm Vop Vom

Diffsense

Vod Voc

s Figure 2

The testbench file contains the proper simulation setup to carry out the following analyses needed in this project: o o Loop gain AC simulation. Sets Vsd=0V and activates the ac sources in the Differential Looptest block to find the circuits loop gain vs. frequency. Noise simulation.

Last modified 11/6/2006 11:07:00 AM

EE214 Autumn 06/07 B. Murmann

Page 5 of 6

o o

Transient simulation. Applies the specified input transient step. The amplitude is determined by a parameter set in your submitted netlist (see example design netlist). Open-loop DC gain simulation. Applies a (small) DC-sweep to Vsd. Note that this DC simulation will be unaffected by the presence of all capacitors and the Differential Looptest block.

Note: The testbench will run properly with HSpice version 2004 or later (e.g. the 2006 version setup for this course. This is due to the RUNLVL option (see application note in handouts/spice section on eeclass) that were using to improve transient accuracy and simulation time.

5. Grading 1. Design Flow and Insight 2. Documentation 3. Specs and Practicality 4. Discussion/documentation of corner performance 5. Power Dissipation 20 points 10 points 10 points 5 points 15 points

1.

Aspect Design Flow

CMFB

Excellent Well structured, clear and reasonable decisions Proper design based on stability constraints Well explained and/or within reasonable bounds None

Not that great Well structured, but unjustified decisions No mention of stability considerations, randomly chosen CMFB transconductance

Poor Unclear how design point was reached Unstable

Discrepancies between hand analysis and simulations Misconceptions

Minor

No discussion of discrepancies and potential sources Not clear if students understand their design

Creativity

2.

Schematics & annotation Plots

Tried something new and interesting, e.g. based on a literature search Clearly labeled Clear, good zoom and annotation

Basic design

Somewhat unclear Somewhat sloppy, e.g. no zoom, no labels.

Unreadable schematics Some plots missing or unreadable.

Last modified 11/6/2006 11:07:00 AM

EE214 Autumn 06/07 B. Murmann

Page 6 of 6

3.

Design constraints/Practicality

All satisfied

Somewhat impractical, e.g. violating Mfactors, tail current source in triode region,

Impractical design, e.g. pole zero cancellation

Netlist Specs

4.

Corner performance

5.

Power dissipation

Not functional 1 specification More barely not met, specifications results agree with missed or design our sim does not work Well Not clear if documented, all corner issues simulations were explained run, inconsistent data without proper interpretation Computed based on ranking (015 points)

Simulated OK All met and results agree with our sim

Last modified 11/6/2006 11:07:00 AM

Potrebbero piacerti anche

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsDa EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsNessuna valutazione finora

- Digital LED Thermometer with Microcontroller AVR ATtiny13Da EverandDigital LED Thermometer with Microcontroller AVR ATtiny13Valutazione: 5 su 5 stelle5/5 (1)

- AIC Project PDFDocumento6 pagineAIC Project PDFuam22Nessuna valutazione finora

- Lab3.Design Project - Ee140.s12.v1Documento4 pagineLab3.Design Project - Ee140.s12.v1frankongNessuna valutazione finora

- Frequency Response of A CMOS Common-Source Amplifier: Experiment # 5Documento10 pagineFrequency Response of A CMOS Common-Source Amplifier: Experiment # 5Md. Sadique SheikhNessuna valutazione finora

- Design Report Format BSCS KfueitDocumento16 pagineDesign Report Format BSCS KfueitMaryam AsadNessuna valutazione finora

- RTL2GDSFLOWDocumento23 pagineRTL2GDSFLOWAbhishek Gupta0% (1)

- Lab 5 Multisim TutorialDocumento9 pagineLab 5 Multisim TutorialMuhammad UbaidNessuna valutazione finora

- PTI Section 9 Analog DigitalDocumento14 paginePTI Section 9 Analog Digitalchrist9088Nessuna valutazione finora

- Computer-Aided Design of a Core Type Power TransformerDocumento26 pagineComputer-Aided Design of a Core Type Power TransformersellysaidiNessuna valutazione finora

- You Should Try To MinimizeDocumento5 pagineYou Should Try To MinimizeSunwoo LeeNessuna valutazione finora

- EE 214 Design Project: 1 Problem Definition and Design GoalsDocumento5 pagineEE 214 Design Project: 1 Problem Definition and Design GoalsSeda ToyNessuna valutazione finora

- Digital-to-Analogue Conversion: PHY 406F - Microprocessor Interfacing TechniquesDocumento14 pagineDigital-to-Analogue Conversion: PHY 406F - Microprocessor Interfacing TechniquesMalou Ruiz DenolanNessuna valutazione finora

- Eecs311 Lab06 PDFDocumento28 pagineEecs311 Lab06 PDFGwenShepherdNessuna valutazione finora

- Low Power ThesisDocumento6 pagineLow Power Thesistiffanybarbermobile100% (2)

- Cw1 (Part1) BriefDocumento3 pagineCw1 (Part1) Briefoussama sadkiNessuna valutazione finora

- DSPACE Procedure With MPPT ExampleDocumento21 pagineDSPACE Procedure With MPPT ExampleSri SriNessuna valutazione finora

- ECE 534 Project 1 F19Documento6 pagineECE 534 Project 1 F19JAY CHHEDANessuna valutazione finora

- Computer Modeling and Simulation of PWM Converter CircuitsDocumento27 pagineComputer Modeling and Simulation of PWM Converter CircuitsAshok KumarNessuna valutazione finora

- 01 Project 01 PDFDocumento2 pagine01 Project 01 PDFmarcjoseph.hufanciaNessuna valutazione finora

- 06 CSL38 Manual LDDocumento68 pagine06 CSL38 Manual LDSwathi N SudarshanNessuna valutazione finora

- Hydraulic Modeling of Water Systems with EPA-NETDocumento27 pagineHydraulic Modeling of Water Systems with EPA-NETcasaeanNessuna valutazione finora

- EE-312L Power Electronics Lab ProjectsDocumento7 pagineEE-312L Power Electronics Lab ProjectsHassan AliNessuna valutazione finora

- Lecture 24 Computer Modeling and Simulation of PWM Converter CircuitsDocumento6 pagineLecture 24 Computer Modeling and Simulation of PWM Converter Circuitslenovo1986Nessuna valutazione finora

- Flash ADC Design in ElectricDocumento22 pagineFlash ADC Design in ElectricNagaraj HegdeNessuna valutazione finora

- Computer Modeling and Simulation of PWM Converter CircuitsDocumento27 pagineComputer Modeling and Simulation of PWM Converter CircuitsskrtamilNessuna valutazione finora

- ICC 201012 LG 06 FinishingDocumento14 pagineICC 201012 LG 06 FinishingAparna TiwariNessuna valutazione finora

- Lab 1 - HandoutDocumento38 pagineLab 1 - HandoutShivam ChaturvediNessuna valutazione finora

- Class AbDocumento7 pagineClass Abdemos2011Nessuna valutazione finora

- Session 2: Basic Operation and Analysis of A DC/DC ConverterDocumento10 pagineSession 2: Basic Operation and Analysis of A DC/DC ConverterSanty LeónNessuna valutazione finora

- ADVD Analog Assignment - 2023ssDocumento36 pagineADVD Analog Assignment - 2023ssNimit JainNessuna valutazione finora

- Massachusetts Institute of Technology Department of Electrical Engineering and Computer ScienceDocumento7 pagineMassachusetts Institute of Technology Department of Electrical Engineering and Computer ScienceFernando Sánchez HernándezNessuna valutazione finora

- EE240 Proj2Documento2 pagineEE240 Proj2SaliiKiruosiNessuna valutazione finora

- Maxim MAX5072/3 Buck/Boost Converter Configuration ToolDocumento13 pagineMaxim MAX5072/3 Buck/Boost Converter Configuration ToolJc Jayamanikandan BNessuna valutazione finora

- Lab 1 Introduction and Top-SPICE DemoDocumento10 pagineLab 1 Introduction and Top-SPICE Demochrisdp23Nessuna valutazione finora

- Last Modified On September 3, 2004 by Stanley Wang and Henry JenDocumento3 pagineLast Modified On September 3, 2004 by Stanley Wang and Henry JenThomas GeorgeNessuna valutazione finora

- Ee141 HW5 2Documento3 pagineEe141 HW5 2Vidhya DsNessuna valutazione finora

- (ECEN 4797 and ECEN 5797) Two-Transistor Forward Converter: Modeling, Design and SimulationsDocumento2 pagine(ECEN 4797 and ECEN 5797) Two-Transistor Forward Converter: Modeling, Design and SimulationsMaharshiGohelNessuna valutazione finora

- Using Advanced Design System To Design An Mmic Amplifier: Agilent Eesof EdaDocumento40 pagineUsing Advanced Design System To Design An Mmic Amplifier: Agilent Eesof EdaAgilentcomNessuna valutazione finora

- Lab 3 - HandoutDocumento7 pagineLab 3 - HandoutohmprakashNessuna valutazione finora

- 1 2 6 P Understandinganalogdesign rng-2Documento5 pagine1 2 6 P Understandinganalogdesign rng-2api-287488010Nessuna valutazione finora

- Geo CleaningDocumento34 pagineGeo CleaningNanaNessuna valutazione finora

- Final Project (1) of PowerDocumento2 pagineFinal Project (1) of PowerLea Jean ConsigoNessuna valutazione finora

- Turbulent Flow Through an Asymmetric DiffuserDocumento18 pagineTurbulent Flow Through an Asymmetric DiffuserVinod Kumar PatelNessuna valutazione finora

- Gmid RuidaDocumento7 pagineGmid Ruida謝政谷Nessuna valutazione finora

- Massachusetts Institute of Technology Department of Electrical Engineering and Computer Science 6.776 High Speed Communications Circuits Spring 2005Documento29 pagineMassachusetts Institute of Technology Department of Electrical Engineering and Computer Science 6.776 High Speed Communications Circuits Spring 2005adi3443Nessuna valutazione finora

- Fall 2011 Lab332a8Documento4 pagineFall 2011 Lab332a8Allen 艾倫 EgarNessuna valutazione finora

- Cadence Basic SimulationDocumento10 pagineCadence Basic SimulationLarry FredsellNessuna valutazione finora

- Thesis On Pipeline AdcsDocumento6 pagineThesis On Pipeline Adcsamyholmesmanchester100% (2)

- Measuring Power in Cadence SpectreDocumento7 pagineMeasuring Power in Cadence SpectrenikunjNessuna valutazione finora

- Analog Design Assignment: Analog and Digital VLSI Design - EEE C443 February 1, 2012Documento9 pagineAnalog Design Assignment: Analog and Digital VLSI Design - EEE C443 February 1, 2012srishaharidasNessuna valutazione finora

- Isscc2022 000023CLDocumento17 pagineIsscc2022 000023CLdashuai huaNessuna valutazione finora

- Low Power Techniques For VLSI DesignDocumento6 pagineLow Power Techniques For VLSI DesignjainatinNessuna valutazione finora

- Isscc2022 000002CLDocumento16 pagineIsscc2022 000002CLdashuai huaNessuna valutazione finora

- Download H64RFP project file and start ADS designDocumento15 pagineDownload H64RFP project file and start ADS designakeedtheNessuna valutazione finora

- Intel Processor Power Delivery DesignDocumento13 pagineIntel Processor Power Delivery DesignE.I.OSENessuna valutazione finora

- Microwave Amplifier Design and Smith Chart Utility For Z Matching Network Using ADSDocumento29 pagineMicrowave Amplifier Design and Smith Chart Utility For Z Matching Network Using ADSZeeshan AhmedNessuna valutazione finora

- Introduction To Multisim 12Documento11 pagineIntroduction To Multisim 12Madhuri RoyNessuna valutazione finora

- Manual Calculadora ElectricaDocumento68 pagineManual Calculadora Electrica12345Nessuna valutazione finora

- Power Systems Laboratory User Manual: Revised: July 22, 2008Documento40 paginePower Systems Laboratory User Manual: Revised: July 22, 2008prakashkmrrNessuna valutazione finora

- Asic 02Documento5 pagineAsic 02Ibrahim MuhammedNessuna valutazione finora

- Lecture01 Intro 2upDocumento11 pagineLecture01 Intro 2uptarungupta79Nessuna valutazione finora

- 02-ECE612-S14-CMOS Inverter PDFDocumento46 pagine02-ECE612-S14-CMOS Inverter PDFIbrahim MuhammedNessuna valutazione finora

- Lecture01 Intro 2upDocumento11 pagineLecture01 Intro 2uptarungupta79Nessuna valutazione finora

- Daniel Proj 1997 Transcond AmpDocumento15 pagineDaniel Proj 1997 Transcond AmpIbrahim MuhammedNessuna valutazione finora

- Lesson 2 CMOS Op Amp DesignDocumento36 pagineLesson 2 CMOS Op Amp DesignIbrahim MuhammedNessuna valutazione finora

- Allen Practice AnalogDocumento23 pagineAllen Practice AnalogvarunjothishNessuna valutazione finora

- Sure Cross DXM1000-B2 Wireless Controller: DatasheetDocumento8 pagineSure Cross DXM1000-B2 Wireless Controller: DatasheetLeo VazquezNessuna valutazione finora

- (Drone in Tourism) - VietnamDocumento29 pagine(Drone in Tourism) - Vietnamnguyennhuquynh130823Nessuna valutazione finora

- Ebook Crafting and Executing Strategy 19Th Edition Thompson Solutions Manual Full Chapter PDFDocumento34 pagineEbook Crafting and Executing Strategy 19Th Edition Thompson Solutions Manual Full Chapter PDFclasticsipperw8g0100% (7)

- Attach-3a ABB Ability™ System 800xa - OPERATOR NOTEDocumento3 pagineAttach-3a ABB Ability™ System 800xa - OPERATOR NOTEAnandharaja RajamohanNessuna valutazione finora

- Sg825866ben E00 Brochure Stella Sepcos 10-2021Documento12 pagineSg825866ben E00 Brochure Stella Sepcos 10-2021Marcos AlbinoNessuna valutazione finora

- Syllabus-7 Middle School Business and Computer Science (Grade 7) 8-4-15 - Website and Orange For SigDocumento2 pagineSyllabus-7 Middle School Business and Computer Science (Grade 7) 8-4-15 - Website and Orange For Sigapi-260421647Nessuna valutazione finora

- Project Report Bba 6TH SemDocumento104 pagineProject Report Bba 6TH SemSahil rajNessuna valutazione finora

- Nikolaos MesaritesDocumento87 pagineNikolaos MesaritesleipsanothikiNessuna valutazione finora

- Lab Manual For All WeeksDocumento6 pagineLab Manual For All WeeksAryan KhanNessuna valutazione finora

- South NTS362R10Documento2 pagineSouth NTS362R10RodrigoNessuna valutazione finora

- Annexure 1 - PSPCL Tender SpecificationsDocumento73 pagineAnnexure 1 - PSPCL Tender Specificationsmanish anandNessuna valutazione finora

- Understanding Blockchain Technology and How To Get Involved: July 2018Documento17 pagineUnderstanding Blockchain Technology and How To Get Involved: July 2018PemetaanPendidikanNessuna valutazione finora

- Final R20 M.Tech AI - ML SyllabusDocumento50 pagineFinal R20 M.Tech AI - ML SyllabusPrasanna KumarNessuna valutazione finora

- Laptop Battery Replacement ListingDocumento2 pagineLaptop Battery Replacement ListingPeter Sergio Mantari HuaytaNessuna valutazione finora

- Network Infrastructure and Directory Services Source 2Documento6 pagineNetwork Infrastructure and Directory Services Source 2John Llucastre CortezNessuna valutazione finora

- Dividing by A Monomial Learning Objective(s) : Example Proble MDocumento5 pagineDividing by A Monomial Learning Objective(s) : Example Proble Mrolea denioNessuna valutazione finora

- Eegame LogcatDocumento24 pagineEegame LogcatBINXX훼 VNessuna valutazione finora

- Z:/windchill/codebase Z:/windchill/codebaseDocumento3 pagineZ:/windchill/codebase Z:/windchill/codebaseamalNessuna valutazione finora

- Unit - I: Introduction To Embedded SystemsDocumento47 pagineUnit - I: Introduction To Embedded SystemsaishwaryaNessuna valutazione finora

- xc3000 Logic Cell Array FamilyDocumento8 paginexc3000 Logic Cell Array FamilyRemo NamNessuna valutazione finora

- Base Station OMCH Self-Recovery (SRAN16.1 - 01)Documento31 pagineBase Station OMCH Self-Recovery (SRAN16.1 - 01)VVLNessuna valutazione finora

- TCP2101 Algorithm Design and Analysis Lab02 - HashTablesDocumento4 pagineTCP2101 Algorithm Design and Analysis Lab02 - HashTableshusnazk.workNessuna valutazione finora

- Disassembly HP Thinclient T530Documento10 pagineDisassembly HP Thinclient T530Hagop NaguibNessuna valutazione finora

- Citrix Netscaler Data SheetDocumento12 pagineCitrix Netscaler Data SheetEnrique Ferrando BarbenaNessuna valutazione finora

- Using OSINT To Investigate School ShootersDocumento33 pagineUsing OSINT To Investigate School ShootersojanathottoNessuna valutazione finora

- S2ORC: The Semantic Scholar Open Research CorpusDocumento15 pagineS2ORC: The Semantic Scholar Open Research CorpusNull PointerNessuna valutazione finora

- Defibrillators, External, Automated Semiautomated - 030223112503Documento105 pagineDefibrillators, External, Automated Semiautomated - 030223112503CLAUDIA PAOLA HOLGUIN VELEZNessuna valutazione finora

- 10 Big Data Companies & Their SolutionsDocumento6 pagine10 Big Data Companies & Their SolutionsShuvro DasNessuna valutazione finora

- Package Management Basic Help: Zypper NR 3 UpdDocumento2 paginePackage Management Basic Help: Zypper NR 3 Updlupin2186Nessuna valutazione finora

- Rukmini College of Management & Commerce: Ameerpet, Hyderabad. Important Questions For 2 Semester ExaminationDocumento7 pagineRukmini College of Management & Commerce: Ameerpet, Hyderabad. Important Questions For 2 Semester Examinationshiva kumarNessuna valutazione finora