Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Datasheet Fairchild UC3843

Caricato da

Tina JohnsonDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Datasheet Fairchild UC3843

Caricato da

Tina JohnsonCopyright:

Formati disponibili

www.fairchildsemi.

com

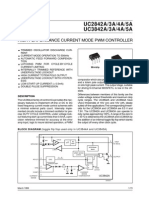

UC3842/UC3843/UC3844/UC3845

SMPS Controller

Features

Low Start up Current Maximum Duty Clamp UVLO With Hysteresis Operating Frequency up to 500KHz

Description

The UC3842/UC3843/UC3844/UC3845 are fixed frequencycurrent-mode PWM controller. They are specially designed for Off-Line and DC to DC converter applications with minimum external components. These integrated circuits feature a trimmed oscillator for precise duty cycle control, a temperature compensated reference, high gain error amplifier, current sensing comparator and a high current totempole output for driving a Power MOSFET. The UC3842 and UC3844 have UVLO thresholds of 16V (on) and 10V (off). The UC3843 and UC3845 are 8.5V(on) and 7.9V (off). The UC3842 and UC3843 can operate within 100% duty cycle. The UC3844 and UC3845 can operate with 50% duty cycle.

8-DIP 8-SOP

14-SOP

Internal Block Diagram

* NORMALLY 8DIP/8SOP PIN NO. * ( ) IS 14SOP PINNO. * TOGGLE FLIP FLOP USED ONLY IN UC3844, UC3845

Rev. 1.0.1

2002 Fairchild Semiconductor Corporation

UC3842/UC3843/UC3844/UC3845

Absolute Maximum Ratings

Parameter Supply Voltage Output Current Analog Inputs (Pin 2.3) Error Amp Output Sink Current Power Dissipation at TA25C (8DIP) Power Dissipation at TA25C (8SOP) Power Dissipation at TA25C (14SOP) Storage Temperature Range Lead Temperature (Soldering, 10sec) Symbol VCC IO V(ANA) ISINK (E.A) PD(Note1,2) PD(Note1,2) PD(Note1,2) TSTG TLEAD Value 30 1 -0.3 to 6.3 10 1200 460 680 -65 ~ +150 +300 Unit V A V mA mW mW mW C C

Note: 1. Board Thickness 1.6mm, Board Dimension 76.2mm 114.3mm, (Reference EIA / JSED51-3, 51-7) 2. Do not exceeed PD and SOA (Safe Operation Area)

Power Dissipation Curve

1200 8DIP 1100 POWER DISSIPATION (mW) 1000 900 800 700 600 500 400 300

0 10 20 30 40 50 60 70 80 90 100 110 120 130 140 150

14SOP

8SOP

AMBIENT TEMPERATURE ()

Thermal Data

Characteristic Thermal Resistance Junction-ambient Symbol Rthj-amb(MAX) 8-DIP 100 8-SOP 265 14-SOP 180 Unit C/W

Pin Array

8DIP,8SOP 14SOP

COMP 1

VREF

COMP 1

14 VREF

VFB 2

VCC

N/C

13

N/C

CURRENT SENSE

OUTPUT

VFB 3

12

VCC

RT/ CT 4

5 GND

N/C 4

11 PWR VC

CURRENT SENSE

10 OUTPUT

N/C

GND

RT/C T 7

PWR GND

UC3842/UC3843/UC3844/UC3845

Electrical Characteristics

(VCC=15V, RT=10k, CT=3.3nF, TA= 0C to +70C, unless otherwise specified) Parameter REFERENCE SECTION Reference Output Voltage Line Regulation Load Regulation Short Circuit Output Current OSCILLATOR SECTION Oscillation Frequency Frequency Change with Voltage Oscillator Amplitude ERROR AMPLIFIER SECTION Input Bias Current Input Voltage Open Loop Voltage Gain Power Supply Rejection Ratio Output Sink Current Output Source Current High Output Voltage Low Output Voltage CURRENT SENSE SECTION Gain Maximum Input Signal Power Supply Rejection Ratio Input Bias Current OUTPUT SECTION Low Output Voltage High Output Voltage Rise Time Fall Time Start Threshold Min. Operating Voltage (After Turn On) VOL ISINK = 20mA ISINK = 200mA VOH tR tF ISOURCE = 20mA ISOURCE = 200mA TJ = 25C, CL= 1nF (Note 3) TJ = 25C, CL= 1nF (Note 3) UC3842/UC3844 UC3843/UC3845 UC3842/UC3844 UC3843/UC3844 13 12 14.5 7.8 8.5 7.0 0.08 1.4 13.5 13.0 45 35 16.0 8.4 10.0 7.6 0.4 2.2 150 150 17.5 9.0 11.5 8.2 V V V V ns ns V V V V GV VI(MAX) PSRR IBIAS (Note 1 & 2) Vpin1 = 5V(Note 1) 12V VCC 25V (Note 1,3) 2.85 0.9 3 1 70 -3 3.15 1.1 -10 V/V V dB A IBIAS VI(E>A) GVO PSRR ISINK ISOURCE VOH VOL Vpin1 = 2.5V 2V VO 4V (Note3) 12V VCC 25V (Note3) Vpin2 = 2.7V, Vpin1 = 1.1V Vpin2 = 2.3V, Vpin1 = 5V Vpin2 = 2.3V, RL = 15k to GND Vpin2 = 2.7V, RL = 15k to Pin 8 2.42 65 60 2 -0.6 5 -0.1 2.50 90 70 7 -1.0 6 0.8 -2 2.58 1.1 A V dB dB mA mA V V f f/VCC VOSC TJ = 25C 12V VCC 25V 47 52 0.05 1.6 57 1 kHz % VP-P VREF VREF VREF ISC TJ = 25C, IREF = 1mA 12V VCC 25V 1mA IREF 20mA TA = 25C 4.90 5.00 6 6 -100 5.10 20 25 -180 V mV mV mA Symbol Conditions Min. Typ. Max. Unit

UNDER-VOLTAGE LOCKOUT SECTION VTH(ST) VOPR(MIN)

UC3842/UC3843/UC3844/UC3845

Electrical Characteristics (Continued)

(VCC=15V, RT=10k, CT=3.3nF, TA= 0C to +70C, unless otherwise specified) Parameter PWM SECTION Max. Duty Cycle Min. Duty Cycle TOTAL STANDBY CURRENT Start-Up Current Operating Supply Current Zener Voltage IST ICC(OPR) VZ ICC = 25mA Vpin3=Vpin2=ON 30 0.45 14 38 1 17 mA mA V D(Max) D(Max) D(MIN) UC3842/UC3843 UC3844/UC3845 95 47 97 48 100 50 0 % % % Symbol Conditions Min. Typ. Max. Unit

Adjust VCC above the start threshould before setting at 15V

Note: 1. Parameter measured at trip point of latch 2. Gain defined as: V pin1 A = ----------------- ,0 Vpin3 0.8V V pin3 3. These parameters, although guaranteed, are not 100 tested in production.

UC3842

Figure 1. Open Loop Test Circuit

High peak currents associated with capacitive loads necessitate careful grounding techniques Timing and bypass capacitors should be connected close to pin 5 in a single point ground. The transistor and 5k potentiometer are used to sample the oscillator waveform and apply an adjustable ramp to pin 3.

UC3842/UC3843/UC3844/UC3845

UC3842/44 UC3843/45

Figure 2. Under Voltage Lockout

During Under-Voltage Lock-Out, the output driver is biased to a high impedance state. Pin 6 should be shunted to ground with a bleeder resistor to prevent activating the power switch with output leakage current.

Figure 3. Error Amp Configuration

Figure 4. Current Sense Circuit

Peak current (IS) is determined by the formula:

1.0V I S ( MAX ) = ----------RS

A small RC filter may be required to suppress switch transients.

UC3842/UC3843/UC3844/UC3845

Figure 5. Oscillator Waveforms and Maximum Duty Cycle

Oscillator timing capacitor, CT, is charged by VREF through RT and discharged by an internal current source. During the discharge time, the internal clock signal blanks the output to the low state. Selection of RT and CT therefore determines both oscillator frequency and maximum duty cycle. Charge and discharge times are determined by the formulas: tc = 0.55 RT CT

0.0063RT 2.7 t D = R T C T I n --------------------------------------- 0.0063R T 4

Frequency, then, is: f=(tc + td)-1

1.8 ForRT > 5K ,f = -------------RT CT

Figure 6. Oscillator Dead Time & Frequency

Figure 7. Timing Resistance vs Frequency

(Deadtime vs CT RT > 5k)

Figure 8. Shutdown Techniques

UC3842/UC3843/UC3844/UC3845

Shutdown of the UC3842 can be accomplished by two methods; either raise pin 3 above 1V or pull pin 1 below a voltage two diode drops above ground. Either method causes the output of the PWM comparator to be high (refer to block diagram). The PWM latch is reset dominant so that the output will remain low until the next clock cycle after the shutdown condition at pins 1 and/or 3 is removed. In one example, an externally latched shutdown may be accomplished by adding an SCR which will be reset by cycling VCC below the lower UVLO threshold. At this point the reference turns off, allowing the SCR to reset.

UC3842/UC3843

Figure 9. Slope Compensation

A fraction of the oscillator ramp can be resistively summed with the current sense signal to provide slope compensation for converters requiring duty cycles over 50%. Note that capacitor, CT, forms a filter with R2 to suppress the leading edge switch spikes.

Temperature (C) Figure 10. Temperature Drift (Vref)

Temperature (C) Figure 11. Temperature Drift (Ist)

Temperature (C) Figure 12. Temperature Drift (Icc)

Potrebbero piacerti anche

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- 110 Waveform Generator Projects for the Home ConstructorDa Everand110 Waveform Generator Projects for the Home ConstructorValutazione: 4 su 5 stelle4/5 (1)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDa EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsValutazione: 3.5 su 5 stelle3.5/5 (6)

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsDa EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Valutazione: 2.5 su 5 stelle2.5/5 (3)

- Low Z Differential Relay Protection SettingsDocumento7 pagineLow Z Differential Relay Protection SettingsharrisvasNessuna valutazione finora

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetDa EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetNessuna valutazione finora

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDa EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNessuna valutazione finora

- Blade Service ManualDocumento185 pagineBlade Service ManualDiego Alejandro Gomez80% (5)

- Analog Circuit Design Volume Three: Design Note CollectionDa EverandAnalog Circuit Design Volume Three: Design Note CollectionValutazione: 3 su 5 stelle3/5 (2)

- E-Globe G2 User Guide S-63 1.1Documento23 pagineE-Globe G2 User Guide S-63 1.1krupa kumar100% (1)

- Isolated Flyback Switching Regulator W - 9V OutputDocumento16 pagineIsolated Flyback Switching Regulator W - 9V OutputCasey DialNessuna valutazione finora

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Da EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Valutazione: 4.5 su 5 stelle4.5/5 (3)

- GPON TrainingDocumento36 pagineGPON TrainingJurist Anthony B. Canguilan80% (5)

- Floor Mounted Tube Stand: Operator and Service ManualDocumento66 pagineFloor Mounted Tube Stand: Operator and Service ManualALISON GREGORIO DE SOUZANessuna valutazione finora

- Current Mode PWM Controller: Features DescriptionDocumento9 pagineCurrent Mode PWM Controller: Features DescriptionJozo ĆurčićNessuna valutazione finora

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetDa EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetValutazione: 2 su 5 stelle2/5 (1)

- ABB Transformers Protection CourseDocumento56 pagineABB Transformers Protection Coursejha100% (3)

- IEC 60079-18 - 2009 - Encapsulated Protection - Ex M PDFDocumento35 pagineIEC 60079-18 - 2009 - Encapsulated Protection - Ex M PDFRadu Babau100% (1)

- UC3843 DatasheetDocumento13 pagineUC3843 DatasheetBigbrain99Nessuna valutazione finora

- UC3845Documento13 pagineUC3845roozbehxoxNessuna valutazione finora

- Uc284xa Uc384xaDocumento16 pagineUc284xa Uc384xayusufwpNessuna valutazione finora

- UC3845ANDocumento15 pagineUC3845ANMiloud ChouguiNessuna valutazione finora

- UC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerDocumento16 pagineUC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerCortés BernaNessuna valutazione finora

- UC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllerDocumento15 pagineUC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllertoajuiceNessuna valutazione finora

- Uc3842 Monitor Power Supply Regulator IcDocumento7 pagineUc3842 Monitor Power Supply Regulator IcJoseph Sidhom SnadaNessuna valutazione finora

- 8205Documento16 pagine8205sonytinNessuna valutazione finora

- Uc3844 DDocumento16 pagineUc3844 DankurmalviyaNessuna valutazione finora

- Uc3842b 3843BDocumento10 pagineUc3842b 3843Bbob75Nessuna valutazione finora

- Lm555 555c TimerDocumento12 pagineLm555 555c TimerAlexis Orellana VediaNessuna valutazione finora

- Uc3844 DDocumento16 pagineUc3844 DFaisalMalikNessuna valutazione finora

- LMC555 CMOS Timer: General Description FeaturesDocumento10 pagineLMC555 CMOS Timer: General Description FeaturesJeremy ObriotNessuna valutazione finora

- KA3842BDocumento12 pagineKA3842BLucio Sortija LuqueNessuna valutazione finora

- IC 3842 para FonteDocumento8 pagineIC 3842 para FonteTomNedscNessuna valutazione finora

- Transition-Mode PFC Controller: 1 FeaturesDocumento17 pagineTransition-Mode PFC Controller: 1 Featuresadriancho66Nessuna valutazione finora

- LM555 Timer: General Description FeaturesDocumento12 pagineLM555 Timer: General Description FeaturesMark J A. OkyoNessuna valutazione finora

- Mc1455-d Timer IcDocumento11 pagineMc1455-d Timer IcDecker JamesNessuna valutazione finora

- LM555 Timer: Literature Number: SNAS548BDocumento14 pagineLM555 Timer: Literature Number: SNAS548BKenly WallNessuna valutazione finora

- SG3524 SMPS Control Circuit: Description Pin ConfigurationDocumento5 pagineSG3524 SMPS Control Circuit: Description Pin ConfigurationNiko OlnicasaNessuna valutazione finora

- MC1648 DataSheetDocumento11 pagineMC1648 DataSheetKWojtekNessuna valutazione finora

- MC34063AMDocumento16 pagineMC34063AMSajjad4434Nessuna valutazione finora

- LMC555 CMOS Timer: General Description FeaturesDocumento12 pagineLMC555 CMOS Timer: General Description FeaturesNicolas FontanaNessuna valutazione finora

- MC34063ADocumento15 pagineMC34063AAlfredo Valencia RodriguezNessuna valutazione finora

- CD4047Documento9 pagineCD4047Haryadi VjNessuna valutazione finora

- L 6565Documento17 pagineL 6565tatatabuchoNessuna valutazione finora

- MC1455Documento13 pagineMC1455eduardolsNessuna valutazione finora

- MC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorsDocumento13 pagineMC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorszocanNessuna valutazione finora

- CA3059, CA3079: Description FeaturesDocumento12 pagineCA3059, CA3079: Description FeaturesMiltongrimi GrimilNessuna valutazione finora

- Precision Waveform Generator/Voltage Controlled Oscillator FeaturesDocumento12 paginePrecision Waveform Generator/Voltage Controlled Oscillator FeaturesCharles Tineo0% (1)

- S Feature D Escriptio: LTC1261 Switched Capacitor Regulated Voltage InverterDocumento16 pagineS Feature D Escriptio: LTC1261 Switched Capacitor Regulated Voltage InverterFer CurtinoNessuna valutazione finora

- SG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorDocumento10 pagineSG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorJayesh SuryavanshiNessuna valutazione finora

- DatasheetDocumento9 pagineDatasheetnipunkhatriNessuna valutazione finora

- Thb7128 InstructionsDocumento9 pagineThb7128 InstructionsanhxcoNessuna valutazione finora

- Fan 7314Documento14 pagineFan 7314Kamal NonekNessuna valutazione finora

- MC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorsDocumento14 pagineMC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorsVũ TưởngNessuna valutazione finora

- 3842 Ic DatasheetDocumento13 pagine3842 Ic DatasheetEngr Khalid IqbalNessuna valutazione finora

- Data SheetDocumento14 pagineData SheetGavril GiurgiNessuna valutazione finora

- Secondary or Machining ProcessDocumento49 pagineSecondary or Machining ProcessHar QuinNessuna valutazione finora

- Water Quality Monitoring and Notification System U PDFDocumento4 pagineWater Quality Monitoring and Notification System U PDFMukund KumarNessuna valutazione finora

- Sm-A750fn Common Evapl 3Documento2 pagineSm-A750fn Common Evapl 3J Carlos Menacho SNessuna valutazione finora

- Lab 6 Mux and DecoderDocumento6 pagineLab 6 Mux and DecoderRifah Shanjida MomoNessuna valutazione finora

- Storageworks Msa1000Documento52 pagineStorageworks Msa1000Hari RamadhaniNessuna valutazione finora

- Selection Guide Fluid Coupling NewDocumento34 pagineSelection Guide Fluid Coupling NewIsaac Montero Barrera100% (1)

- Manual Service LG SonidoDocumento266 pagineManual Service LG SonidoManuel PradoNessuna valutazione finora

- Samsung TV LCD Ltm1525xDocumento100 pagineSamsung TV LCD Ltm1525xJuan SanchezNessuna valutazione finora

- Toshiba Satellite E55 ZRMAA Compal LA-A481P Rev1.0 SchematicDocumento55 pagineToshiba Satellite E55 ZRMAA Compal LA-A481P Rev1.0 SchematicdataNessuna valutazione finora

- Iec 60076 24 2020Documento11 pagineIec 60076 24 2020Fardhani RozakNessuna valutazione finora

- 2 B&G+1BL003LF+Install+ManualDocumento4 pagine2 B&G+1BL003LF+Install+Manualazul_281808Nessuna valutazione finora

- Intelligent Provisioning 2.30 (Updated 12:2015)Documento6 pagineIntelligent Provisioning 2.30 (Updated 12:2015)Sahatma SiallaganNessuna valutazione finora

- ECE357 Course InformationDocumento7 pagineECE357 Course InformationVictor HughesNessuna valutazione finora

- Avanti Fridge Instructions Manual (Model FF993W)Documento20 pagineAvanti Fridge Instructions Manual (Model FF993W)oxotnicNessuna valutazione finora

- E Jac ManualDocumento10 pagineE Jac ManualJhon Elier Arango TrillosNessuna valutazione finora

- Paragon 8000 Series English DEROST TIMERDocumento4 pagineParagon 8000 Series English DEROST TIMERRomanko100% (1)

- DRA - Transformers KSADocumento16 pagineDRA - Transformers KSAAhmet TosunNessuna valutazione finora

- Sony BDP-BX37 S270 S370 S373 S470 Ver 1.4 2010.05 Reproductor Blu-Ray Manual de ServicioDocumento118 pagineSony BDP-BX37 S270 S370 S373 S470 Ver 1.4 2010.05 Reproductor Blu-Ray Manual de ServicioRonald Castellar100% (1)

- 975 Helukabel Cables-Wires 2012-2013Documento125 pagine975 Helukabel Cables-Wires 2012-2013AbdelRhman ElfkyNessuna valutazione finora

- Hewlett Packard 5305B Service, User ID4961Documento48 pagineHewlett Packard 5305B Service, User ID4961cesarmayhemNessuna valutazione finora

- MOS Device CharacterizationDocumento5 pagineMOS Device CharacterizationKiran SomayajiNessuna valutazione finora

- BTE Student Performance Checklist by Courses - UpdatedDocumento2 pagineBTE Student Performance Checklist by Courses - UpdatedazizNessuna valutazione finora