Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

10NK80

Caricato da

Abubakar SidikDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

10NK80

Caricato da

Abubakar SidikCopyright:

Formati disponibili

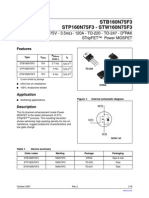

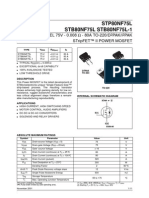

STP10NK80ZFP STP10NK80Z - STW10NK80Z

N-channel 800V - 0.78 - 9A - TO-220/FP-TO-247 Zener-protected superMESHTM MOSFET

General features

Type STP10NK80Z STW10NK80Z STP10NK80ZFP

VDSS 800V 800V 800V

RDS(on) <0.90 <0.90 <0.90

ID 9A 9A 9A

Pw 160 W 160 w 40 W TO-220

1 2 3

3 1 2

TO-220FP

Extremely high dv/dt capability 100% avalanche tested Gate charge minimized Very low intrinsic capacitances Very good manufacturing repeability

TO-247

Description

The SuperMESH series is obtained through an extreme optimization of STs well established strip-based PowerMESH layout. In addition to pushing on-resistance significantly down, special care is taken to ensure a very good dv/dt capability for the most demanding applications.

Internal schematic diagram

Applications

Switching application

Order codes

Part number STP10NK80Z STP10NK80ZFP STW10NK80Z Marking P10NK80Z P10NK80ZFP W10NK80Z Package TO-220 TO-220FP TO-247 Packaging Tube Tube Tube

July 2006

Rev 6

1/15

www.st.com 15

Contents

STP10NK80ZFP - STP10NK80Z - STW10NK80Z

Contents

1 2 Electrical ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.1 Electrical characteristics (curves) ............................. 6

3 4 5

Test circuit

................................................ 9

Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2/15

STP10NK80ZFP - STP10NK80Z - STW10NK80Z

Electrical ratings

Electrical ratings

Table 1.

Symbol VDS VDGR VGS ID ID IDM(2) PTOT

Absolute maximum ratings

Value Parameter TO-220/ TO-247 Drain-source voltage (VGS = 0) Drain-gate voltage (RGS = 20K) Gate-source voltage Drain current (continuous) at TC = 25C Drain current (continuous) at TC=100C Drain current (pulsed) Total dissipation at TC = 25C Derating Factor 9 6 36 160 1.28 4 4.5 --55 to 150 2500 800 800 30 9(1) 6(1) 36(1) 40 0.32 TO-220FP V V V A A A W W/C KV V/ns V C Unit

Vesd(G-S) G-S ESD (HBM C=100pF, R=1.5k) dv/dt

(3)

Peak diode recovery voltage slope Insulation withstand voltage (DC) Operating junction temperature Storage temperature

VISO TJ Tstg

1. Limited only by maximum temperature allowed 2. Pulse width limited by safe operating area 3. ISD di/dt 9A, 200A/s,VDD V(BR)DSS, Tj TJMAX

Table 2.

Symbol Rthj-case Rthj-a Tl

Thermal data

Value Parameter TO-220 TO-220FP Thermal resistance junction-case Max Thermal resistance junction-ambient Max Maximum lead temperature for soldering purpose 0.78 62.5 300 3.1 TO-247 0.78 50 C/W C/W C Unit

Table 3.

Symbol IAS EAS

Avalanche characteristics

Parameter Avalanche current, repetitive or not-repetitive (pulse width limited by Tj Max) Single pulse avalanche energy (starting Tj=25C, Id=Iar, Vdd=50V) Value 9 290 Unit A mJ

3/15

Electrical characteristics

STP10NK80ZFP - STP10NK80Z - STW10NK80Z

Electrical characteristics

(TCASE=25C unless otherwise specified) Table 4.

Symbol V(BR)DSS IDSS IGSS VGS(th) RDS(on)

On/off states

Parameter Drain-source breakdown voltage Zero gate voltage drain current (VGS = 0) Gate body leakage current (VDS = 0) Gate threshold voltage Static drain-source on resistance Test condictions ID = 1mA, VGS= 0 VDS = Max rating, VDS = Max rating @125C VGS = 20V VDS= VGS, ID = 100A VGS= 10V, ID= 4.5A 3 3.75 0.78 Min. 800 1 50

10

Typ.

Max.

Unit V A A nA V

4.5 0.9

Table 5.

Symbol gfs (1) Ciss Coss Crss

Dynamic

Parameter Forward transconductance Input capacitance Output capacitance Reverse transfer capacitance Test condictions VDS =15V, ID = 4.5A Min. Typ. 9.6 2180 205 38 105 72 12.5 37 Max. Unit S pF pF pF pF nC nC nC

VDS =25V, f=1 MHz, VGS=0

Coss eq(2). Equivalent output capacitance Qg Qgs Qgd Total gate charge Gate-source charge Gate-drain charge

VGS=0, VDS =0V to 640V VDD=640V, ID = 9A VGS =10V (see Figure 19)

1. Pulsed: pulse duration=300s, duty cycle 1.5% 2. Coss eq. is defined as a constant equivalent capacitance giving the same charging time as Coss when VDS inceases from 0 to 80% VDSS

4/15

STP10NK80ZFP - STP10NK80Z - STW10NK80Z

Electrical characteristics

Table 6.

Symbol td(on) tr td(off) tf

Switching times

Parameter Turn-on Delay Time Rise Time Test condictions VDD=400 V, ID=4.5A, RG=4.7, VGS=10V (see Figure 20) VDD=400 V, ID=4.5A, RG=4.7, VGS=10V (see Figure 20) Min. Typ. 30 20 Max. Unit ns ns

Turn-off Delay Time Fall Time

65 17

ns ns

Table 7.

Symbol

Gate-source zener diode

Parameter Test condictions Igs=1mA (Open Drain) Min. 30 Typ. Max. Unit V

BVGSO(1) Gate-Source Breakdown Voltage

1. The built-in back-to-back Zener diodes have specifically been designed to enhance not only the devices ESD capability, but also to make them safely absorb possible voltage transients that may occasionally be applied from gate to source. In this respect the Zener voltage is appropriate to achieve an efficient and cost-effective intervention to protect the devices integrity. These integrated Zener diodes thus avoid the usage of external components.

Table 8.

Symbol ISD ISDM(1) VSD(2) trr Qrr IRRM

Source drain diode

Parameter Source-drain current Source-drain current (pulsed) Forward on voltage Reverse recovery time Reverse recovery charge Reverse recovery current ISD=9A, VGS=0 ISD=9A, di/dt = 100A/s, VDD=45V, Tj=150C 645 6.4 20 Test condictions Min Typ. Max 9 36 1.6 Unit A A V ns C A

1. Pulse width limited by safe operating area 2. Pulsed: pulse duration=300s, duty cycle 1.5%

5/15

Electrical characteristics

STP10NK80ZFP - STP10NK80Z - STW10NK80Z

2.1

Figure 1.

Electrical characteristics (curves)

Safe operating area for TO-220 Figure 2. Thermal impedance for TO-220

Figure 3.

Safe operating area for TO-220FP

Figure 4.

Thermal impedance for TO-220FP

Figure 5.

Safe operating area for TO-247

Figure 6.

Thermal impedance for TO-247

6/15

STP10NK80ZFP - STP10NK80Z - STW10NK80Z Figure 7. Output characterisics Figure 8.

Electrical characteristics Transfer characteristics

Figure 9.

Transconductance

Figure 10. Static drain-source on resistance

Figure 11. Gate charge vs gate-source voltage Figure 12. Capacitance variations

7/15

Electrical characteristics Figure 13. Normalized gate threshold voltage vs temperature

STP10NK80ZFP - STP10NK80Z - STW10NK80Z Figure 14. Normalized on resistance vs temperature

Figure 15. Source-drain diode forward characteristics

Figure 16. Normalized BVDSS vs temperature

Figure 17. Maximum avalanche energy vs temperature

8/15

STP10NK80ZFP - STP10NK80Z - STW10NK80Z

Test circuit

Test circuit

Figure 19. Gate charge test circuit

Figure 18. Switching times test circuit for resistive load

Figure 20. Test circuit for inductive load Figure 21. Unclamped Inductive load test switching and diode recovery times circuit

Figure 22. Unclamped inductive waveform

Figure 23. Switching time waveform

9/15

Package mechanical data

STP10NK80ZFP - STP10NK80Z - STW10NK80Z

Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK packages. These packages have a Lead-free second level interconnect . The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com

10/15

STP10NK80ZFP - STP10NK80Z - STW10NK80Z

Package mechanical data

TO-220 MECHANICAL DATA

DIM. A b b1 c D E e e1 F H1 J1 L L1 L20 L30 mm. MIN. 4.40 0.61 1.15 0.49 15.25 10 2.40 4.95 1.23 6.20 2.40 13 3.50 16.40 28.90 3.75 2.65 3.85 2.95 0.147 0.104 TYP MAX. 4.60 0.88 1.70 0.70 15.75 10.40 2.70 5.15 1.32 6.60 2.72 14 3.93 MIN. 0.173 0.024 0.045 0.019 0.60 0.393 0.094 0.194 0.048 0.244 0.094 0.511 0.137 0.645 1.137 0.151 0.116 inch TYP. MAX. 0.181 0.034 0.066 0.027 0.620 0.409 0.106 0.202 0.052 0.256 0.107 0.551 0.154

P

Q

11/15

Package mechanical data

STP10NK80ZFP - STP10NK80Z - STW10NK80Z

TO-220FP MECHANICAL DATA

mm. MIN. 4.4 2.5 2.5 0.45 0.75 1.15 1.15 4.95 2.4 10 16 28.6 9.8 2.9 15.9 9 3 30.6 10.6 3.6 16.4 9.3 3.2 1.126 .0385 0.114 0.626 0.354 0.118 TYP MAX. 4.6 2.7 2.75 0.7 1 1.7 1.7 5.2 2.7 10.4 MIN. 0.173 0.098 0.098 0.017 0.030 0.045 0.045 0.195 0.094 0.393 0.630 1.204 0.417 0.141 0.645 0.366 0.126 inch TYP. MAX. 0.181 0.106 0.108 0.027 0.039 0.067 0.067 0.204 0.106 0.409

DIM. A B D E F F1 F2 G G1 H L2 L3 L4 L5 L6 L7

L3 L6 L7

F1 F

G1 H

F2

L2 L5

E

1 2 3

L4

12/15

STP10NK80ZFP - STP10NK80Z - STW10NK80Z

Package mechanical data

TO-247 MECHANICAL DATA

mm. MIN. 4.85 2.20 1.0 2.0 3.0 0.40 19.85 15.45 5.45 14.20 3.70 18.50 3.55 4.50 5.50 3.65 5.50 0.140 0.177 0.216 14.80 4.30 0.560 0.14 0.728 0.143 0.216 TYP MAX. 5.15 2.60 1.40 2.40 3.40 0.80 20.15 15.75 MIN. 0.19 0.086 0.039 0.079 0.118 0.015 0.781 0.608 0.214 0.582 0.17 inch TYP. MAX. 0.20 0.102 0.055 0.094 0.134 0.03 0.793 0.620

DIM. A A1 b b1 b2 c D E e L L1 L2 P R S

13/15

Revision history

STP10NK80ZFP - STP10NK80Z - STW10NK80Z

Revision history

Table 9.

Date 08-Sep-2005 10-Mar-2006 28-Sep-2005

Document revision history

Revision 4 5 6 Complete document Inserted ecopack indication New template, no content change Changes

14/15

STP10NK80ZFP - STP10NK80Z - STW10NK80Z

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (ST) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice. All ST products are sold pursuant to STs terms and conditions of sale. Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN STS TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USERS OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

2006 STMicroelectronics - All rights reserved STMicroelectronics group of companies Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America www.st.com

15/15

Potrebbero piacerti anche

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- 110 Waveform Generator Projects for the Home ConstructorDa Everand110 Waveform Generator Projects for the Home ConstructorValutazione: 4 su 5 stelle4/5 (1)

- Wireless Semiconductor SolutionsDocumento1.630 pagineWireless Semiconductor SolutionsAbubakar SidikNessuna valutazione finora

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDa EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNessuna valutazione finora

- Benq r55 Quanta Tw3aDocumento48 pagineBenq r55 Quanta Tw3aAbubakar SidikNessuna valutazione finora

- Gateway W350DI.Documento44 pagineGateway W350DI.Abubakar SidikNessuna valutazione finora

- Fault Detection ClassificationDocumento210 pagineFault Detection ClassificationAnonymous GRb9L95LwzNessuna valutazione finora

- Scully ST-47C Groundhog Technical ManualDocumento32 pagineScully ST-47C Groundhog Technical ManualOscar Moreno100% (1)

- Ics 61800 2Documento7 pagineIcs 61800 2Hung Vu0% (1)

- Stp7Nk80Z - Stp7Nk80Zfp STB7NK80Z - STB7NK80Z-1Documento18 pagineStp7Nk80Z - Stp7Nk80Zfp STB7NK80Z - STB7NK80Z-1queequeg73Nessuna valutazione finora

- STW21NM50N MosfetDocumento16 pagineSTW21NM50N MosfetrigowNessuna valutazione finora

- Go P20NM60FP PDFDocumento15 pagineGo P20NM60FP PDFHenry HenriquezNessuna valutazione finora

- Stb160N75F3 Stp160N75F3 - Stw160N75F3: N-Channel 75V - 3.5M - 120A - To-220 - To-247 - D Pak Stripfet™ Power MosfetDocumento16 pagineStb160N75F3 Stp160N75F3 - Stw160N75F3: N-Channel 75V - 3.5M - 120A - To-220 - To-247 - D Pak Stripfet™ Power MosfetmoabdolyNessuna valutazione finora

- Stp6Nk60Z - Stp6Nk60Zfp STB6NK60Z - STB6NK60Z-1Documento13 pagineStp6Nk60Z - Stp6Nk60Zfp STB6NK60Z - STB6NK60Z-1servitecolorNessuna valutazione finora

- P120NF10Documento15 pagineP120NF10marpre1983Nessuna valutazione finora

- STP55NF06 - Mosfet N 60v 50ADocumento18 pagineSTP55NF06 - Mosfet N 60v 50AJuan Carlos González FragueiroNessuna valutazione finora

- P6NK90ZDocumento13 pagineP6NK90ZVictor ChangNessuna valutazione finora

- STP75NF75 ST MicroelectronicsDocumento16 pagineSTP75NF75 ST MicroelectronicsAloisio RibeiroNessuna valutazione finora

- STP9NK65ZFPDocumento16 pagineSTP9NK65ZFPJacson FagundesNessuna valutazione finora

- STB130NS04ZB 1Documento12 pagineSTB130NS04ZB 1quemasda quiensoyNessuna valutazione finora

- P 4 NK 80 ZDocumento18 pagineP 4 NK 80 ZMalik Farhan ShabirNessuna valutazione finora

- Stx30N65M5: N-Channel 650 V, 0.130, 21 A, Mdmesh™ V Power Mosfet D Pak, I Pak, To-220Fp, To-220, To-247Documento15 pagineStx30N65M5: N-Channel 650 V, 0.130, 21 A, Mdmesh™ V Power Mosfet D Pak, I Pak, To-220Fp, To-220, To-247Oscar PortelaNessuna valutazione finora

- STB7NK80Z, STB7NK80Z-1 STP7NK80ZFP, STP7NK80ZDocumento17 pagineSTB7NK80Z, STB7NK80Z-1 STP7NK80ZFP, STP7NK80ZsionyNessuna valutazione finora

- STB80NF55-08 STP80NF55-08 - STW80NF55-08Documento15 pagineSTB80NF55-08 STP80NF55-08 - STW80NF55-08Carlos SoaresNessuna valutazione finora

- 10NK80-Data SheetDocumento11 pagine10NK80-Data Sheetsensat1onNessuna valutazione finora

- FQB8N60C / FQI8N60C: 600V N-Channel MOSFETDocumento9 pagineFQB8N60C / FQI8N60C: 600V N-Channel MOSFETemelchor57Nessuna valutazione finora

- P 9 NC 60 FPDocumento9 pagineP 9 NC 60 FPJulian PascuNessuna valutazione finora

- Stp8Nc50 - Stp8Nc50Fp Stb8Nc50-1: N-Channel 500V - 0.7 - 8A To-220/To-220Fp/I2Pak Powermesh Ii MosfetDocumento11 pagineStp8Nc50 - Stp8Nc50Fp Stb8Nc50-1: N-Channel 500V - 0.7 - 8A To-220/To-220Fp/I2Pak Powermesh Ii Mosfetmiguel angel jaramilloNessuna valutazione finora

- Fet 60NF06Documento9 pagineFet 60NF06Anh Nguyễn HoàngNessuna valutazione finora

- T40n03g PDFDocumento7 pagineT40n03g PDFsandor9116Nessuna valutazione finora

- FQPF17P06: 60V P-Channel MOSFETDocumento8 pagineFQPF17P06: 60V P-Channel MOSFETMahmoued YasinNessuna valutazione finora

- FQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETDocumento10 pagineFQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETJavier Ayerdis NarváezNessuna valutazione finora

- STP80NF75L STB80NF75L STB80NF75L-1: N-CHANNEL 75V - 0.008 - 80A TO-220/D Pak/I PAK Stripfet™ Ii Power MosfetDocumento11 pagineSTP80NF75L STB80NF75L STB80NF75L-1: N-CHANNEL 75V - 0.008 - 80A TO-220/D Pak/I PAK Stripfet™ Ii Power MosfetAna Luiza BallesteroNessuna valutazione finora

- IRF610Documento8 pagineIRF610gtranNessuna valutazione finora

- Mosfet p7nc70zfpDocumento13 pagineMosfet p7nc70zfptheodoru2014Nessuna valutazione finora

- FQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETDocumento9 pagineFQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETsoweloNessuna valutazione finora

- Mosfet 10NM60NDocumento19 pagineMosfet 10NM60NRicardo Misael Torres0% (1)

- IRF630 IRF630FP: N - CHANNEL 200V - 0.35 - 9A - TO-220/FP Mesh Overlay MosfetDocumento10 pagineIRF630 IRF630FP: N - CHANNEL 200V - 0.35 - 9A - TO-220/FP Mesh Overlay MosfetAlex OreNessuna valutazione finora

- 4NK60ZFP DatasheetDocumento16 pagine4NK60ZFP DatasheetrpaqrvNessuna valutazione finora

- Obsolete Product(s) - Obsolete Product(s) Obsolete Product(s) - Obsolete Product(s)Documento8 pagineObsolete Product(s) - Obsolete Product(s) Obsolete Product(s) - Obsolete Product(s)bagaswaraarieNessuna valutazione finora

- Strh80P6Fsy3: P-Channel 60V - 0.021 - To-254Aa Rad-Hard Low Gate Charge Stripfet™ Power MosfetDocumento12 pagineStrh80P6Fsy3: P-Channel 60V - 0.021 - To-254Aa Rad-Hard Low Gate Charge Stripfet™ Power MosfetNegru P. PlantatieNessuna valutazione finora

- Datasheet - FQA10N80Documento9 pagineDatasheet - FQA10N80cmyguelNessuna valutazione finora

- SM4833NSK PDFDocumento10 pagineSM4833NSK PDFsike1977100% (1)

- W15NB50Documento9 pagineW15NB50G Ivan Torres RNessuna valutazione finora

- 13 NM 60 NDocumento21 pagine13 NM 60 Nmarquitos550bNessuna valutazione finora

- STD17NF03Documento9 pagineSTD17NF03VeronicaNessuna valutazione finora

- N - Channel 500V - 0.22 - 20A - To-247 Powermesh Mosfet: Stw20Nb50Documento8 pagineN - Channel 500V - 0.22 - 20A - To-247 Powermesh Mosfet: Stw20Nb50La Tienda del PatínNessuna valutazione finora

- FDS4435BZDocumento6 pagineFDS4435BZCornel PislaruNessuna valutazione finora

- Fds8958A: Dual N & P-Channel Powertrench MosfetDocumento11 pagineFds8958A: Dual N & P-Channel Powertrench MosfetbyronzapetaNessuna valutazione finora

- STH15NA50/FI STW15NA50: N - Channel Enhancement Mode Fast Power Mos TransistorDocumento11 pagineSTH15NA50/FI STW15NA50: N - Channel Enhancement Mode Fast Power Mos Transistoras135qNessuna valutazione finora

- Qfet Qfet Qfet Qfet: FQP55N10Documento8 pagineQfet Qfet Qfet Qfet: FQP55N10andreanuovoNessuna valutazione finora

- STB120N10F4, STP120N10F4Documento18 pagineSTB120N10F4, STP120N10F4quemasda quiensoyNessuna valutazione finora

- Fqa5n90900v N-Channel MosfetDocumento8 pagineFqa5n90900v N-Channel MosfetbmmostefaNessuna valutazione finora

- Stp2Nc60 Stp2Nc60Fp: N-Channel 600V - 7 - 1.9A - To-220/To-220Fp Powermesh™Ii MosfetDocumento9 pagineStp2Nc60 Stp2Nc60Fp: N-Channel 600V - 7 - 1.9A - To-220/To-220Fp Powermesh™Ii MosfetHorvat NorbertNessuna valutazione finora

- Irfr3707Zpbf Irfu3707Zpbf: V R Max QGDocumento11 pagineIrfr3707Zpbf Irfu3707Zpbf: V R Max QGJared RobisonNessuna valutazione finora

- STP55NE06 STP55NE06FP: N - Channel Enhancement Mode " Single Feature Size " Power MosfetDocumento9 pagineSTP55NE06 STP55NE06FP: N - Channel Enhancement Mode " Single Feature Size " Power MosfetLiliana Nadia MarchisNessuna valutazione finora

- Fqa6n70700v N-Channel MosfetDocumento8 pagineFqa6n70700v N-Channel MosfetbmmostefaNessuna valutazione finora

- W9NK90ZDocumento16 pagineW9NK90ZmecanicoloocianniNessuna valutazione finora

- STB11NK50Z - STP11NK50ZFP STP11NK50ZDocumento16 pagineSTB11NK50Z - STP11NK50ZFP STP11NK50ZPepe PecasNessuna valutazione finora

- APM9932/C: Pin Description FeaturesDocumento13 pagineAPM9932/C: Pin Description Featuresawong_911374Nessuna valutazione finora

- IRFZ48NDocumento8 pagineIRFZ48NLuay IssaNessuna valutazione finora

- FQP6N60C/FQPF6N60C: 600V N-Channel MOSFETDocumento10 pagineFQP6N60C/FQPF6N60C: 600V N-Channel MOSFETBiswajit SarkarNessuna valutazione finora

- N - Channel 800V - 1.8 - 5A - To-220/To-220Fp Powermesh MosfetDocumento10 pagineN - Channel 800V - 1.8 - 5A - To-220/To-220Fp Powermesh MosfetHerpadianaNessuna valutazione finora

- STB9NK60Z, STP9NK60Z, STP9NK60ZFPDocumento19 pagineSTB9NK60Z, STP9NK60Z, STP9NK60ZFPyokonakagimaNessuna valutazione finora

- Mosfet Irlb 8743Documento9 pagineMosfet Irlb 8743Karan ArjunNessuna valutazione finora

- High Current 13.8V Power SupplyDocumento7 pagineHigh Current 13.8V Power SupplyAbubakar SidikNessuna valutazione finora

- Thyristor PDFDocumento10 pagineThyristor PDFMihir HembramNessuna valutazione finora

- 12V - 230V 50Hz Square Wave Inverter With IR2153Documento3 pagine12V - 230V 50Hz Square Wave Inverter With IR2153Abubakar SidikNessuna valutazione finora

- BT138Documento6 pagineBT138Abubakar SidikNessuna valutazione finora

- Bro MateDocumento4 pagineBro MateAbubakar SidikNessuna valutazione finora

- C122B SCRDocumento4 pagineC122B SCRAbubakar SidikNessuna valutazione finora

- 12V - 230V 50Hz Square Wave Inverter With 555Documento2 pagine12V - 230V 50Hz Square Wave Inverter With 555Abubakar SidikNessuna valutazione finora

- NP x06 PCB DiagramDocumento63 pagineNP x06 PCB DiagramAbubakar SidikNessuna valutazione finora

- Samsung NP R60 SchematicsDocumento48 pagineSamsung NP R60 SchematicsSaemundrSigfussonNessuna valutazione finora

- NP M70Documento71 pagineNP M70Abubakar SidikNessuna valutazione finora

- Samsung Np-r410 PCB DiagramDocumento48 pagineSamsung Np-r410 PCB DiagrammichaleangeloNessuna valutazione finora

- NP x20 x25 PCB DiagramDocumento95 pagineNP x20 x25 PCB DiagramAbubakar SidikNessuna valutazione finora

- NP r25 Plus PCB DiagramDocumento53 pagineNP r25 Plus PCB DiagramAbubakar SidikNessuna valutazione finora

- Fujitsu p7230Documento68 pagineFujitsu p7230Nicu LiviuNessuna valutazione finora

- NP r50 PCB DiagramDocumento55 pagineNP r50 PCB DiagramAbubakar SidikNessuna valutazione finora

- NP q70 PCB DiagramDocumento54 pagineNP q70 PCB DiagramAbubakar SidikNessuna valutazione finora

- NP Q40 PCB DiagramDocumento46 pagineNP Q40 PCB Diagramvinhphuoc_computerNessuna valutazione finora

- NP r20 PCB DiagramDocumento48 pagineNP r20 PCB DiagramAbubakar SidikNessuna valutazione finora

- СхемаDocumento51 pagineСхемаrenok3075Nessuna valutazione finora

- g332 1 4 01 r2Documento32 pagineg332 1 4 01 r2Abubakar SidikNessuna valutazione finora

- HP Compaq Evo n620c - Inventec Fenway 3.0Documento53 pagineHP Compaq Evo n620c - Inventec Fenway 3.0Togorean MariaNessuna valutazione finora

- Acer Aspire 6530 ZK3Documento43 pagineAcer Aspire 6530 ZK3Jose A LachiondoNessuna valutazione finora

- Acer Aspire-5510 Schematic DiagramDocumento40 pagineAcer Aspire-5510 Schematic DiagramAbubakar SidikNessuna valutazione finora

- Acer Aspire 6935 Invetec Kilimanjaro 2.0 - Rev - A02 - SCHDocumento58 pagineAcer Aspire 6935 Invetec Kilimanjaro 2.0 - Rev - A02 - SCHCaptain444Nessuna valutazione finora

- AS7100Documento52 pagineAS7100Abubakar SidikNessuna valutazione finora

- Aspire 5670 (Quanta ZB1) SchematicsDocumento50 pagineAspire 5670 (Quanta ZB1) SchematicsjeanpellNessuna valutazione finora

- As 6920 KilimanjaroDocumento59 pagineAs 6920 KilimanjaroAlfonso ZamudioNessuna valutazione finora

- Brochure Nellcor N600Documento4 pagineBrochure Nellcor N600Wolaé Mathurin Edmond AmegandjinNessuna valutazione finora

- QDocumento27 pagineQHassanAhmedNessuna valutazione finora

- Samsung - UA32EH4003M CHASIS U8BApdfDocumento40 pagineSamsung - UA32EH4003M CHASIS U8BApdfRoberto PompaNessuna valutazione finora

- SATIP-P-103-01 Rev 6Documento30 pagineSATIP-P-103-01 Rev 6VISAKHNessuna valutazione finora

- Matchbox MicrophoneDocumento21 pagineMatchbox Microphonecesar tiamsonNessuna valutazione finora

- CHM 101 Material On ElectrolysisDocumento7 pagineCHM 101 Material On Electrolysisbalikisolayemi2005Nessuna valutazione finora

- LPWAN Research PaperDocumento17 pagineLPWAN Research PaperthijsNessuna valutazione finora

- IEEE Reliability Test SystemDocumento8 pagineIEEE Reliability Test Systemgforti100% (1)

- Sample Igat Ee 20xxDocumento11 pagineSample Igat Ee 20xxDr-Ali AlbakryNessuna valutazione finora

- LM5118 Evaluation BoardDocumento16 pagineLM5118 Evaluation BoardAnonymous oyUAtpKNessuna valutazione finora

- Intrerupatoare - Pagini de CatalogDocumento124 pagineIntrerupatoare - Pagini de CatalogClaudiu GheorgheNessuna valutazione finora

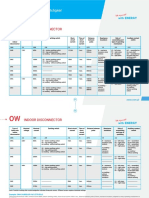

- Order Specification OWDocumento3 pagineOrder Specification OWdabyvjxpNessuna valutazione finora

- Thesis For Electronics Engineering StudentDocumento7 pagineThesis For Electronics Engineering Studentjennysmithportland100% (2)

- Balluff BES 516-325-S4-C BES01C8Documento2 pagineBalluff BES 516-325-S4-C BES01C8celsocarneiroNessuna valutazione finora

- 2600T Sensor TechnologyDocumento23 pagine2600T Sensor TechnologycemsavantNessuna valutazione finora

- CSC 326 ManualDocumento10 pagineCSC 326 ManualRamesh BurhadeNessuna valutazione finora

- Design of A Cost Effective Micro Hydro Power Generation System Using The Discharge Water of The Central Steam Power PlantDocumento159 pagineDesign of A Cost Effective Micro Hydro Power Generation System Using The Discharge Water of The Central Steam Power PlantNobel Engzen Du BermoyNessuna valutazione finora

- Product Specifications: CharacteristicsDocumento3 pagineProduct Specifications: Characteristicseslam salmonyNessuna valutazione finora

- Ec 930Documento2 pagineEc 930Amit Garg100% (1)

- FLEX I-O Digital Input Modules PDFDocumento22 pagineFLEX I-O Digital Input Modules PDFsamuelborgesNessuna valutazione finora

- A Simple Method To Measure Unknown InductorsDocumento4 pagineA Simple Method To Measure Unknown InductorsDiogo CarvalhoNessuna valutazione finora

- Manual Instalacion RTUDocumento25 pagineManual Instalacion RTUlmbkn2013Nessuna valutazione finora

- MPX5700Documento11 pagineMPX5700mardonioandradeNessuna valutazione finora

- Prac1 For Egb120Documento10 paginePrac1 For Egb120Tam NguyenNessuna valutazione finora

- Advisory On E - RegistrationDocumento60 pagineAdvisory On E - RegistrationSaugato MondalNessuna valutazione finora

- 11 12 Automatic Tension Control BTS VFDDocumento2 pagine11 12 Automatic Tension Control BTS VFDGioj MejNessuna valutazione finora

- DC TESLA COIL Construction and ApllicatiDocumento5 pagineDC TESLA COIL Construction and ApllicatiwoodNessuna valutazione finora