Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Jyothi Engineering College: Lab Manual

Caricato da

tmsbharadwajDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Jyothi Engineering College: Lab Manual

Caricato da

tmsbharadwajCopyright:

Formati disponibili

Lab manual-2010 Lab

Microprocessors & Microcontrollers

JYOTHI ENGINEERING COLLEGE

CHERUTHURUTHY, THRISSUR- 679 531

DEPARTMENT OF ELECTRONICS & COMMUNICATION

MICROPROCESSORS AND MICROCONTROLLERS

LAB MANUAL

PREPARED BY FACULTY ECE DEPT- 2010

Jyothi Engineering College, Cheruthuruthy. 1

Lab manual-2010 Lab

Microprocessors & Microcontrollers

EXPERIMENT NO. : 1 FAMILIARIZATION OF MICRO 8086 LCD TRAINER KIT

AIM: To familiarize the 8086 trainer kit.

THEORY: 8086 is a 16-bit microprocessor. M-86/88 is a 8086 trainer kit with LCD display. The block diagram of Intel 8086 microprocessor is shown in fig. 1. Intel 8086 microprocessor is a 40-pin chip having Dual In-line Package (DIP) and its pin details is shown in fig. 2.

Jyothi Engineering College, Cheruthuruthy. 2

Lab manual-2010 Lab

Microprocessors & Microcontrollers

Fig. 1: Block diagram of Intel 8086 microprocessor.

Fig. 2 : Pin diagram of Intel 8086 microprocessor.

The hardware and software facilities available on M 86/88 LCD Trainer Kit is explained below. SPECIFICATIONS HARDWARE SPECIFICATIONS:

1.

CPU PROCESSOR AND CLOCK FREQUENCY:

Jyothi Engineering College, Cheruthuruthy. 3

Lab manual-2010 Lab

Microprocessors & Microcontrollers

Intel 8086/8088 CPU at 5/4.77 M Hz clock rate [optionally 8 M Hz]

2.

MEMORY: MONITOR EPROM EPROM EXPANSION SYSTEM RAM SYSTEM RAM EXPANSION INTERRUPT VECTORS STACK/ DATA AREA ( MONITOR, ASM/DSM, EDITOR) : : : F000:0000-3FFF for 16K F000:0000-1FFF for 64K 0000:1000-3FFF for 16K

: :

0000:1000-FFFF for 64K 0000:0000-03FF

0000:0400-0FFF

3.

PERIPHERALS: PARALLEL I/O SERIAL : : 48 I/O lines using two numbers of 8255 One number of RS232C- Serial Interface using 8251A USART

TIMER

3 channel 16 bit programmable timer 8253 Channel 0 used as baud rate generator for the serial port

4.

DISPLAY: 16X2 LCD DISPLAY [ with back light provision]

KEYBOARD: IBM PC- AT KEYBOARD

5. 6.

AUDIO CASSETTE INTERFACE with file management ON- BOARD BATTERY BACKUP: (Optional) On board battery backup facility is optionally provided for RAM (U2 & U4)

Jyothi Engineering College, Cheruthuruthy. 4

Lab manual-2010 Lab

Microprocessors & Microcontrollers

POWER CONSUMPTION: + 5V : 1.5 Amps

7.

POWER SUPPLY SPECIFICATIONS: Mode 1 Mains Input Output : : : : SMPS-01 230V AC at 50 Hz 230V AC at 50Hz 1) +5V, 3A regulated 1. +12V, 250mA regulated 2. -12V, 250mA regulated 3. +30V, 250mA unregulated

8.

PHYSICAL CHARACTERISTICS: M- 86/88 LCD trainer PCB : 830 mm X 680 mm

9.

BUS EXPANSION : A new concept of VXT_Bus has been incorporated in M-86/88 LCD trainer which facilitates addition of extra hardware on to M- 86/88 LCD trainer. An unlimited number of Add- On Boards can be add to this Expansion Bus. All buffered address, data and control signals are brought out to this bus. The trainer provision for one VXT_Bus connectors.

SOFTWARE SPECIFICATIONS M-86/88 LCD trainer contains a high performance 16K monitor program. It is designed to respond to user input, RS232 communications, printer interface, parallel port interface and so on. The simple description of the command functions supported by this monitor is as follows:

COMMAND KEY FUNCTION MEMORY: RES

Jyothi Engineering College, Cheruthuruthy. 5

Lab manual-2010 Lab

Microprocessors & Microcontrollers

The RES key allows the user to terminate any activity and return the M 86/88 LCD trainer to an initialized state. When pressed, the Vi Microsystems Pvt. Ltd message appears in the display for a few seconds and then the monitor will come to the command prompt TECH 8086. Only after this prompt is displayed, the commands will be accepted. INT

The INT key allows the user to interrupt any activity and return to the command prompt. HARDWARE DETAILS: The hardware description of M 86/88 LCD trainer provided in this chapter, highlights on all technical aspects including memory allocation, peripheral interfacing and power supply. FUNCTIONAL BLOCK DIAGRAM DESCRIPTION : The functional block diagram of M 86 / 88 LCD trainer is given in Fig. 3. Referring to that fig. the following explanations outlines the working of the trainer as a complete system. 1. INPUTS AND OUTPUTS OF THE CPU

The CPU gets the clock from the clock generator 8284 which uses a crystal at 15 or 14.318 M Hz and if it is an 8 M Hz trainer, 24 M Hz. The reset, interrupt lines and data lines are also inputs to the CPU. The CPU outputs comprise the address lines, data lines and control lines. 2. ADDRESS AND DATA BUS

The 16 bit 8086 bi-directional multiplexed address/data lines and the higher order 4 address lines are brought to latches and buffers. The address lines are latched using ALE and thus de-multiplexed from the data lines. The data lines are buffered through octal transceivers. The outputs of these ICs comprise the 20 bit address and 16/8 bit data bus as the case may be. The direction of data transfer is decided by the direction select input of the transceiver which is the DT/R* output of the CPU. 3. CONTRL BUS

The other bus is the control bus. The control signals required for proper operation of the system are the IOR* (I/O read), IOW* (I/O write), MR* (memory read) and MW*

Jyothi Engineering College, Cheruthuruthy. 6

Lab manual-2010 Lab

Microprocessors & Microcontrollers

(memory write). The peripherals on the trainer are all I/O mapped and hence to input from or output to a peripheral, IOR* and IOW* are utilized. The memory read and memory write signals are used to output enable and an EPROM and RAM and write into a RAM respectively. These signals are generated from the IO/M* or M/IO* and WR*, RD* signals in minimum mode operation. 4. CHIP SELECT LOGIC

The selection of any peripheral or memory device requires a CS* (chip select) to enable that particular device. This requires address decoding, both memory and I/O where in decoding is separately achieved for EPROM, RAM and I/O devices. All the above signals address, data, control and chip selected are routed to all the peripherals and memory devices in the trainer. 5. KEYPAD AND DISPLAY

The block diagram shows a AT keyboard and LCD display. This is the unit with which the user communicates with the system 16 x 2 LCD module is used for displaying the command and data. IBM PC AT keyboard is used for entering data and control commands. 6. MEMORY

The block diagram shows two sockets for RAM both odd and even in the case of 8086 and 2 RAM sockets for contiguous locations in memory in the case of 8088. two sockets are provided for RAM expansion. The basic EPROM capacity available is 16KB arranged as odd and even bands in the case of 8086 and continuous locations in the case of 8088. the remaining EPROM capacity which is 16 KB can be availed as an optional facility. Each of the EPROM sockets can support either 8/16/32 KB memory devices and the RAM sockets 8/32 KB devices. 7. PERIPHERALS

The peripherals depicted in the block diagram include a) 8253 timer for baud clock generation b) 8251A USART for RS232C serial communication with associated drivers c) 8259 Programmable Interrupt Controller d) Audio Cassette Interface e) 8255 PPI for parallel TTL I/O System expansion is facilitated by the expansion slots available on the board. The data bus to the expansion slots is sent through a second layer of buffering, the buffers being

Jyothi Engineering College, Cheruthuruthy. 7

Lab manual-2010 Lab

Microprocessors & Microcontrollers

degated for addresses of all devices present on board.

COMPONENT LAYOUT AND FUNCTION BLOCK DIAGRAM The Fig. 3 shows the functional block diagram for Micro-86 LCD trainer. The functional block diagram provides the complete system design in blocks. Have a careful look at the components layout for the exact location for the connectors, ICs and so on.

MEMORY CONFIGURATION This section explains the memory mapping facilities available on Micro-86/88 LCD trainer. Fig. 3 shows the complete memory allocation of Micro-86/88 LCD trainer. As shown in Fig. 3 the monitor reserves some portion of total memory capacity of CPU for its internal use and some for the user interface. The remaining portion is left for the user for their own development. This is indicated in the diagram as LEFT FOR USER DEVELOPMENT.

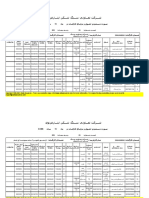

I/O ALLOCATION The complete I/O allocation table of the peripherals of M-86/88 LCD trainer is given in Fig 4. As seen from the table, the peripherals occupy I/O addresses from 0000 to 0060. the I/O addresses from 0081H to 00FFH are used for Add-On Boards. Apart from these reserved addresses, the rest are available to the users for their own development purpose. The following sections briefly describe the various peripherals and interfaces available on M-86/88 LCD trainer, emphasizing on the component used, its features, the connector termination and addresses. The Connector Pin Assignments can be had from the chapter CONNECTOR DETAILS.

TIMER INTERFACE ( U17) i. ii. Device used : Intel 8253 Programmable Interval Timer Key features of 8253

Jyothi Engineering College, Cheruthuruthy. 8

Lab manual-2010 Lab

Microprocessors & Microcontrollers

a. 3 independent 16 bit counters. b. Programmable counter modes c. Input clock up to 2 MHz. d. Programmable count from 2 to 216 iii. iv. System mapping Channel 0 Input clock Output clock Used for Channel 1 & 2 Input clock : : : : : I/O mapped I/O 1.25/1.19 MHz or user input clock TTL levels and frequency less than 2 MHz 153 KHz if using system clock. Baud rate generation for serial port. TTL level clock of rate less than 2 MHz can be by the user. User determined. Available for user development. given

v.

vi.

Output clock : Used for : I/O mapped I/O Address

FUNCTION Control register Channel 0 Channel 1 Channel 2

ADDRESS 0016H 0010H 0012H 0014H

SOCKET NUMBER U17 U17 U17 U17

RS 232C SERIAL INTERFACE : (U27), (U26) i. Device used : Intel 8251A UNIVERSAL SYNCHRONOUS / ASYNCHRONOUS RECEIVER / TRANSMITTER (USART) ii. Key Features of 8251A a. Both synchronous and Asynchronous operations b. Full duplex, double buffered, transmitter and receiver. c. Parity, Overrun and framing error detection. iii. iv. v. System Mapping Input clock Baud Clock : : : : I/O mapped I/O 2.5 / 2.35 M Hz Baud Clock for the 8251A (U26) provided by channel 0 of 8253 (U17) 9600 baud rate, 8 data bits, 1 stop bit and no parity

vi. Initialized to

Jyothi Engineering College, Cheruthuruthy. 9

Lab manual-2010 Lab

Microprocessors & Microcontrollers

vii. Driver Used viii. Connector termination

upon power ON. Max 232 (U27) for RS232C serial transmission and reception. : The RTS*, CTS*, RXD and TXD lines are the connector P3 and the connector is an AMPHENOL STANDARD 9 PIN D TYPE MALE. CONNECTOR NO. P3 P3 SOCKET NO. U26 U26

ix. I/O mapped I/O address: FUNCTION ADDRESS 8251A CONTROL / 000AH STATUS 8251A DATA 0008H

PARALLEL INTERFACE: (U31, U30) i. ii. Device Used : Intel 8255 Programmable Peripheral Interface

Key features of 8255 a. 24 programmable I/O lines configured as three 8- bit ports. b. Direct bit SET/RESET capability. c. Three modes of operation BASIC I/O STROBED I/O BIDIRCTIONAL BUS System mapping : I/O mapped I/O 8255 Port 1 (U30) 8255 Port 2 (U31) : : All 24 I/O lines are available to users All 24 I/O lines are available to users

iii. iv. v.

vi.. Connector termination

The 48 TTL I/O lines of both the 8255 ICs, U30 & U 31 are terminated at the two 26 pin IDC Connectors P7 (U30) and P8 (U30) respectively. All these terminations are as per the Dio bus std.

CONNECROR DETAILS: P1 Power connector. P2 Bus expansion connector

Jyothi Engineering College, Cheruthuruthy. 10

Lab manual-2010 Lab

Microprocessors & Microcontrollers

P3 Serial port connector. P4 Ear input (audio). P5 MIC output (audio interface) P6 VXT Bus connector. P7 & P8 Parallel port connectors P9 IBM keyboard and LCD interface.

RESULT: 8086 LCD trainer kit is familiarized.

Jyothi Engineering College, Cheruthuruthy. 11

Potrebbero piacerti anche

- 0 - MPMC Lab Manual A.Y. 2020-21 R-18Documento53 pagine0 - MPMC Lab Manual A.Y. 2020-21 R-18Karthik BoggarapuNessuna valutazione finora

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationDa EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNessuna valutazione finora

- Microprocessor FileDocumento93 pagineMicroprocessor FileHarshal AmbatkarNessuna valutazione finora

- 8086 Kit ManualDocumento107 pagine8086 Kit Manualatik al mustahidNessuna valutazione finora

- Active Disturbance Rejection Control for Nonlinear Systems: An IntroductionDa EverandActive Disturbance Rejection Control for Nonlinear Systems: An IntroductionNessuna valutazione finora

- 8086 Microprocessor For ScientistDocumento21 pagine8086 Microprocessor For ScientistRam Kishore RoyNessuna valutazione finora

- Zxevo User Manual Revc EngDocumento19 pagineZxevo User Manual Revc EngConrad RussoNessuna valutazione finora

- 8086 Trainer Kit User and Technical Reference Manual PDFDocumento71 pagine8086 Trainer Kit User and Technical Reference Manual PDFJohn Johnston0% (1)

- 8086 ManualDocumento79 pagine8086 ManualHari Ram KNessuna valutazione finora

- Mda 8086Documento3 pagineMda 8086Shuvro Chowdhury0% (1)

- MC 10ESL47 Lab ManualDocumento87 pagineMC 10ESL47 Lab ManualAmbika NarayanNessuna valutazione finora

- 8086 ManualDocumento45 pagine8086 ManualGarima SinghalNessuna valutazione finora

- Important Instructions To Examiners:: (Autonomous)Documento29 pagineImportant Instructions To Examiners:: (Autonomous)Rohit Shinde RSNessuna valutazione finora

- Mpi 11002Documento21 pagineMpi 11002alkesh.eng0% (1)

- Circuit TodayDocumento30 pagineCircuit TodayBrian GiriNessuna valutazione finora

- Ilovepdf MergedDocumento430 pagineIlovepdf MergedYuvraj ChhabraNessuna valutazione finora

- Interfacing Prgrammable Keyboard and Display Controller - 8279Documento3 pagineInterfacing Prgrammable Keyboard and Display Controller - 8279senthilvlNessuna valutazione finora

- Audio Player Using The PIC32, MCP4822, microSD Card and The MDDFS LibraryDocumento9 pagineAudio Player Using The PIC32, MCP4822, microSD Card and The MDDFS Librarytahmidmc100% (2)

- CSE-232 LAB ManualDocumento23 pagineCSE-232 LAB ManualMuhammad UsmanNessuna valutazione finora

- RP Jain Adc DacDocumento27 pagineRP Jain Adc DacAnand SinghNessuna valutazione finora

- Microcontroller 8051 - 1Documento83 pagineMicrocontroller 8051 - 1muradhabib786Nessuna valutazione finora

- Interfacing Programs For 8085Documento37 pagineInterfacing Programs For 8085archankumarturagaNessuna valutazione finora

- 8279 Keyboard and Display ControllerDocumento33 pagine8279 Keyboard and Display Controllergutzz0079197100% (1)

- 8051 PPT For MSCDocumento138 pagine8051 PPT For MSCvikash sharmaNessuna valutazione finora

- Z80 User ManualDocumento308 pagineZ80 User ManualLaFlibusteNessuna valutazione finora

- MP 8086 Lab Manual TRAINER KITDocumento70 pagineMP 8086 Lab Manual TRAINER KITKavitha Subramaniam100% (1)

- Lab 5 Binary ArithmeticDocumento5 pagineLab 5 Binary ArithmeticRifah Shanjida Momo100% (1)

- ARM OverviewDocumento16 pagineARM OverviewNaagaraaju AaraadhyulaNessuna valutazione finora

- Advanced Microprocessor PDFDocumento1 paginaAdvanced Microprocessor PDFAmish Tankariya50% (2)

- CAN Bus in PSoC Report210Documento16 pagineCAN Bus in PSoC Report210Marcos Antonio EstremoteNessuna valutazione finora

- ADC Program For LPC2138Documento8 pagineADC Program For LPC2138hypernuclide100% (1)

- 8284 ManualDocumento82 pagine8284 ManualTecer Tecer50% (2)

- MDA-Win8086 ManualDocumento107 pagineMDA-Win8086 ManualRinalyn-Oscar Gamboa MagtibayNessuna valutazione finora

- ESA 86-88 ManualDocumento97 pagineESA 86-88 Manualwasto37Nessuna valutazione finora

- The 80386 MicroprocessorsDocumento24 pagineThe 80386 MicroprocessorsSourcecode BeeNessuna valutazione finora

- SYNAPSE Techno Design Innovation PVT LTDDocumento47 pagineSYNAPSE Techno Design Innovation PVT LTDcobalt_1223Nessuna valutazione finora

- Training Report of Industrial Interaction in Cetpa Infotech PDFDocumento40 pagineTraining Report of Industrial Interaction in Cetpa Infotech PDFmjdj1230% (1)

- Ldmicro ChangesDocumento4 pagineLdmicro ChangesPandu Milik MuNessuna valutazione finora

- Metering Application ReportDocumento428 pagineMetering Application ReportRené PereiraNessuna valutazione finora

- Training Report On AVRDocumento30 pagineTraining Report On AVRishantkathuria100% (1)

- Understanding The Modbus ProtocolDocumento7 pagineUnderstanding The Modbus ProtocolAshok Kumar100% (1)

- STM32 RS-485Documento12 pagineSTM32 RS-485mail87523Nessuna valutazione finora

- MPMC Unit4Documento61 pagineMPMC Unit4Nandhini ShreeNessuna valutazione finora

- PIC Microcontroller IntroductionDocumento81 paginePIC Microcontroller Introductionpnlinh2850% (2)

- Temperature Sensing/Monitoring Using Lm35 & Atmega8Documento6 pagineTemperature Sensing/Monitoring Using Lm35 & Atmega8Suket75% (4)

- Microprocessor Lab Manual SEM IV 2013Documento58 pagineMicroprocessor Lab Manual SEM IV 2013Abir DuttaNessuna valutazione finora

- Metrodyne Microsystem Corp: MPS-2100 SeriesDocumento3 pagineMetrodyne Microsystem Corp: MPS-2100 SeriesAhmed ShadeedNessuna valutazione finora

- Spi Bascom AvrDocumento7 pagineSpi Bascom AvrYarisSyahmidanNessuna valutazione finora

- Pic18 Serial CommunicationDocumento25 paginePic18 Serial Communicationadamwaiz100% (3)

- Experiment 09 Interfacing Keypad and LCD With PIC18F452 ObjectiveDocumento11 pagineExperiment 09 Interfacing Keypad and LCD With PIC18F452 Objectivehira NawazNessuna valutazione finora

- Chapter 3: Intel 8086Documento135 pagineChapter 3: Intel 8086singhrps8483% (6)

- Interfacing ADC With 8051Documento15 pagineInterfacing ADC With 8051Pavan Kumar N100% (1)

- Features of 8086Documento31 pagineFeatures of 8086Ngaa SiemensNessuna valutazione finora

- AVR Microcontroller: Prepared By: Eng. Ashraf DarwishDocumento19 pagineAVR Microcontroller: Prepared By: Eng. Ashraf DarwishHectorLopez100% (2)

- Design of Programmable Logic Controller and I/O ExpansionsDocumento5 pagineDesign of Programmable Logic Controller and I/O ExpansionsRanjan JlNessuna valutazione finora

- Manual M 86-01Documento79 pagineManual M 86-01Abvolt IndiaNessuna valutazione finora

- MP and MC 2015Documento150 pagineMP and MC 2015Mani Kandan KNessuna valutazione finora

- Solved Tutorial With Tiny Bugs27-8-12Documento24 pagineSolved Tutorial With Tiny Bugs27-8-12WondosenEshetieNessuna valutazione finora

- EISKO-Readme Louise VFX Datapack Rig CC-BYNCND License PDFDocumento2 pagineEISKO-Readme Louise VFX Datapack Rig CC-BYNCND License PDFSerban UngureanuNessuna valutazione finora

- Ucm61xx CDR Rec API GuideDocumento29 pagineUcm61xx CDR Rec API GuideEmilio I Wilde100% (1)

- Datacolor QTX File SpecificationDocumento8 pagineDatacolor QTX File SpecificationJubaidurRahmanNessuna valutazione finora

- DSA With Java - Unit 9Documento25 pagineDSA With Java - Unit 9Sabin MaharjanNessuna valutazione finora

- SL10496 Basic Concepts For NetApp ONTAP 9.4-NAS Services-CLI Edition-V2.0.0 PDFDocumento45 pagineSL10496 Basic Concepts For NetApp ONTAP 9.4-NAS Services-CLI Edition-V2.0.0 PDFZawed AlamNessuna valutazione finora

- RaspbianInstaller - RaspbianDocumento6 pagineRaspbianInstaller - Raspbianclaudiu72Nessuna valutazione finora

- HW 6Documento3 pagineHW 6Eneet Singh RanaNessuna valutazione finora

- Awt MCQDocumento29 pagineAwt MCQAbhinav Daksha100% (1)

- Master 2012Documento91 pagineMaster 2012PAUL BALLARTANessuna valutazione finora

- CS6612 - RejinpaulDocumento64 pagineCS6612 - Rejinpaulvenkatarangan rajuluNessuna valutazione finora

- Tt-Tiger Term GuideDocumento88 pagineTt-Tiger Term GuidejaimeherzNessuna valutazione finora

- 5G - InterviewDocumento10 pagine5G - InterviewnaeemansNessuna valutazione finora

- Java Exam Answer SheetDocumento12 pagineJava Exam Answer SheetRaghav AdhikariNessuna valutazione finora

- Cimplicity SecureDeploymentGuide v2 PDFDocumento70 pagineCimplicity SecureDeploymentGuide v2 PDFMOHAMMADNessuna valutazione finora

- ActiveReports DocumentDocumento5 pagineActiveReports DocumentHaha ZazaNessuna valutazione finora

- Day 5.3 Configuration of RouterDocumento13 pagineDay 5.3 Configuration of RouterGorvam SaddarNessuna valutazione finora

- RMDLLProgrammers GuideDocumento389 pagineRMDLLProgrammers GuideANGEL GABRIEL MAMANI SULLCANINessuna valutazione finora

- Project 3 ReportDocumento40 pagineProject 3 Reportapi-355421942Nessuna valutazione finora

- VSAN Failure TestingDocumento28 pagineVSAN Failure TestingLawes ChanNessuna valutazione finora

- Barangay SystemDocumento8 pagineBarangay Systempetemabait56% (9)

- 12 The EBIOSDocumento4 pagine12 The EBIOSxavi2975Nessuna valutazione finora

- Create Dynamic Selection ScreenDocumento5 pagineCreate Dynamic Selection ScreenGoutam MahatoNessuna valutazione finora

- Part BDocumento3 paginePart BPrince DaveNessuna valutazione finora

- Quiz Time!!!Documento13 pagineQuiz Time!!!Souvik PaulNessuna valutazione finora

- Arduino Wifi ManualDocumento7 pagineArduino Wifi ManualCix XidNessuna valutazione finora

- LoadersDocumento59 pagineLoadersRohan RayNessuna valutazione finora

- Unix Pocket GuideDocumento2 pagineUnix Pocket GuidevisuhaiNessuna valutazione finora

- SQL Tutorial DBMS LabDocumento10 pagineSQL Tutorial DBMS LabAkhilesh KumarNessuna valutazione finora

- Duraid Project ProposalDocumento9 pagineDuraid Project ProposalDuraid AliNessuna valutazione finora

- Profisafe Communication: Reference GuideDocumento18 pagineProfisafe Communication: Reference GuideKamilNessuna valutazione finora

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsDa EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsValutazione: 5 su 5 stelle5/5 (4)

- CompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Da EverandCompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Valutazione: 5 su 5 stelle5/5 (2)

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionDa EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionValutazione: 4.5 su 5 stelle4.5/5 (543)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyDa EverandChip War: The Quest to Dominate the World's Most Critical TechnologyValutazione: 4.5 su 5 stelle4.5/5 (229)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Da EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Valutazione: 5 su 5 stelle5/5 (4)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Da EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Valutazione: 5 su 5 stelle5/5 (2)

- INCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesDa EverandINCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesValutazione: 5 su 5 stelle5/5 (1)

- Chip War: The Fight for the World's Most Critical TechnologyDa EverandChip War: The Fight for the World's Most Critical TechnologyValutazione: 4.5 su 5 stelle4.5/5 (82)

- Electrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tDa EverandElectrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tValutazione: 4.5 su 5 stelle4.5/5 (27)

- Multiplexed Networks for Embedded Systems: CAN, LIN, FlexRay, Safe-by-Wire...Da EverandMultiplexed Networks for Embedded Systems: CAN, LIN, FlexRay, Safe-by-Wire...Nessuna valutazione finora

- The Journeyman Electrician Exam Study Guide: Proven Methods for Successfully Passing the Journeyman Electrician Exam with ConfidenceDa EverandThe Journeyman Electrician Exam Study Guide: Proven Methods for Successfully Passing the Journeyman Electrician Exam with ConfidenceNessuna valutazione finora

- Conquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeDa EverandConquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeValutazione: 4.5 su 5 stelle4.5/5 (10)

- Cyber-Physical Systems: Foundations, Principles and ApplicationsDa EverandCyber-Physical Systems: Foundations, Principles and ApplicationsHoubing H. SongNessuna valutazione finora

- A Mind at Play: How Claude Shannon Invented the Information AgeDa EverandA Mind at Play: How Claude Shannon Invented the Information AgeValutazione: 4 su 5 stelle4/5 (53)

- Practical Electrical Wiring: Residential, Farm, Commercial, and IndustrialDa EverandPractical Electrical Wiring: Residential, Farm, Commercial, and IndustrialValutazione: 3.5 su 5 stelle3.5/5 (3)

- Power System Control and ProtectionDa EverandPower System Control and ProtectionB. Don RussellValutazione: 4 su 5 stelle4/5 (11)

- Programming the Raspberry Pi, Third Edition: Getting Started with PythonDa EverandProgramming the Raspberry Pi, Third Edition: Getting Started with PythonValutazione: 5 su 5 stelle5/5 (2)

- Teach Yourself Electricity and Electronics, 6th EditionDa EverandTeach Yourself Electricity and Electronics, 6th EditionValutazione: 3.5 su 5 stelle3.5/5 (15)

- 2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersDa Everand2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersValutazione: 5 su 5 stelle5/5 (1)

- Hacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsDa EverandHacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsValutazione: 3.5 su 5 stelle3.5/5 (2)

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-1-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1715431191?v=1)