Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Diseño Logico Secuencial Con VHDL

Caricato da

ENIC-AITCGCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Diseño Logico Secuencial Con VHDL

Caricato da

ENIC-AITCGCopyright:

Formati disponibili

INSTITUTO TECNOLOGICO DE CIUDAD GUZMAN

CAPITULO 4

DISEO LGICO SECUENCIAL CON VHDL

INTEGRANTES: DAVID GOMEZ GOMEZ. F. XAVIER JAVIER GALVAN.

INTRODUCCIN

Los circuitos digitales que hemos manejado con anterioridad han sido de tipo combinacional es decir, son circuitos que dependen por completo de los valores que se encuentran en sus entradas, en determinado tiempo. Si bien un sistema secuencial puede tener tambi n uno o m s elementos combi nacionales, la mayor a de los sistemas que se encuentran en la pr ctica incluyen elementos de memoria, los cuales requieren que el sistema se describa en t rminos de lgica secuencial.. : En este captulo se describen algunos de los circuitos secuenciales m s utilizados en la pr ctica, como flip-flops, contadores, registros, etc., .adem s se desarrollan ejercicios para aprender la programaci n de circuitos secuenciales en los que se integran los conceptos adquiridos en los captulos anteriores.

4.1 DISEO LGICO SECUENCIAL Un sistema secuencial est formado por un circuito combinacional y un elemento de memoria encargado de almacenar de forma temporal la historia del sistema. . En esencia, la salida de un sistema secuencial no slo depende del valor presente de las entradas, sino tambin de la historia del sistema, segn se observa en la figura 4.1.

B sicamente hay dos tipos de sistemas secuenciales: s ncronos y as ncronos; el 'comportamiento de los primeros se encuentra' sincronizado mediante el pulso de reloj del sistema, mientras que el funcionamiento de los sistemas asncronos depende del orden y momento en el cual se aplican sus se ales de entrada, por lo que no requieren un pulso de reloj para sincronizar sus acciones.

4.2 Flip flops El elemento de memoria utilizado indistintamente en el diseo de los sistemas sncronos o asncronos se conoce como flip_flop o celda binaria. La caracterstica principal de un flip-flop es mantener o almacenar un bit de manera indefinida hasta que a travs de un pulso' o una seal cambie de estado. Los flip-flops ms conocidos son los tipos SR, JK, T y D. En la figura 4.2 se presenta cada upo de estos elementos y la tabla de verdad que describe su comportamiento.

Es importante recordar el significado de la notacin Q y Q(t+ 1): Q = estado presente o actual Qt+ 1 = estado futuro o siguiente Por ejemplo, consideremos la tabla de verdad que describe el funcionamiento del flip-flop tipo D, mostrado en la figura 4.2c) y que se muestra de nuevo en la figura 4.3a).

Cuando el valor de la entrada D es igual al, figura 4.3b) , la salida Qt+ 1 adopta el valor de 1: Qt+l := 1 siempre y cuando se genere un pulso de re - loj Es importante resaltar que el valor actual en la entrada D es transferido a la salida Qt+ 1 sin importar cu l sea el valor previo que haya tenido la salida Q en el estado presente. En el diseo secuencial con VHDL las declaraciones lf-then-else son las ms utilizadas; por ejemplo, el programa del listado 4.1 usa estas declaraciones. La ejecuci n del proceso es sensible a los cambios en clk (pulso de reloj); esto es, cuando clk cambia de valor de una transicin de O a 1 (clk = 1), el valor de D se asigna a Q y se conserva hasta que se genera un nuevo pulso. A la inversa, si clk no presenta dicha transicin, el valor de Q se mantiene igual. Esto puede observarse con claridad en la simulacin del circuito, fig. 4.4.

Listado 4.1 descripcin de un flip-flop disparado por flanco positivo

library ieee: use ieee.std_logic_1164.all; entity ffd is port( D,clk: in std_logic; Q:out std_logic); end ffd; architecture arg_ffd of ffd is begin process (clk) begin if (clk'event and clk='l') then Q <= D; end if; end process; end arg_ffd;

Notemos que la salida Q toma el valor de la entrada D s lo cuando la transicin del pulso de reloj es de O a 1 y se mantiene hasta que se ejecuta de nuevo el cambio de valor de la entrada clk. Atributo' event i I En el lenguaje VHDL los atributos sirven para definir caracter sticas que se pueden asociar con cualquier tipo de datos, objeto o entidades. El atributo event 1 (evento) se utiliza para describir un hecho u ocurrencia de una seal en particular. En el cdigo del listado 4.1 podemos observar que la condicin if clk ' event es cierta s lo cuando ocurre un cambio de valor; es decir, un suceso (event) de la se al clk. Como se puede apreciar, en la declaracin (if_then) no maneja la condicin else, debido a que el compilador mantiene el valor de Q hasta que no exista un cambio de valor en la seal clk

EJEMPLO 4.1 Escriba un programa que describa el funcionamiento de un flip-flop SR con base en la siguiente tabla de verdad. Solucin La tabla de verdad del flip-flop SR muestra qu cuando la entrada S es igual a 1 y la entrada R es igual a O, la salida Qt+ 1 toma valores lgicos de 1. Por otro lado, cuando S = O y R= 1, la salida Q t+ 1 = O; en el caso de que S y R sean ambas igual a 1 l gico, la salida Qt+l queda indeterminada; es decir, no es posible precisar su valor y ste puede adoptar el O o 1 lgico. Por ltimo, cuando no existe cambio en las entradas S y R es decir, son igual a O, el valor de Qt+ 1 mantienes su estado actual Q. Con base en el an lisis anterior, el programa en VHDL puede realizarse utilizando instrucciones condicionales y un nuevo tipo de datos: valores no importa (', , ), los cuales permiten adoptar' un valor de O o 1 lgico de manera indistinta (Listado 4.2).

Listado 4.2codigo VHDL de un registro de 8 bits

1 library ieee; 2 use ieee.std_logic_1164.all; 3 entity ffsr is port ( 4 S,R,c1k: in std_logic; 5 Q, Qn: inout std_logic); 6 end ffsr; 7 architecture a_ffsr of ffsr is 8 begin 9 process (clk, S, R) 11 begin 10 if (clk'event and clk ='1')then 11 if (s ='O' and R = '1') 12 Q<='O'; 13 Qn <= '1'; 14 elsif (s = '1' and R = 'O') 15 Q<='l'; 16 Qn <= 'O'; 17 elsif (s = 'O' and R = 'O') then 18 Q <= Q; 19 Qn<=Qn; 20 else 21 Q <= '--'-; 22 Qn <='-'; 23 end if; 24 end if; 25 end process; 26 end a ffsr;

then

then

4.3 Registros En la figura 4.5 se presenta la estructura de un registro de 8 bits con entrada y salida de datos en paralelo. El diseo es muy similar al flipflop anterior, la diferencia radica en la utilizacin de vectores de bits en lugar de un solo bit como se observa en el listado 4.2. 0[0:7] Figura 4.5 Registro paralelo de 8 bit".

library ieee; use ieee.std_logic_1164.all; entity reg is port ( D: in std_logic_vector (O to 7); clk: in std_logic; Q: out std_logic_vector(O to 7)); end reg; architecture arqreg of reg is begin process (clk) begin . if (clk 'event and clk=' 1') then Q <= D; end if; end process; end arqreg; Listado 4.2 Cdigo VHDL de un registro de 8 bits

EJEMPLO 4.2 Escriba un programa de un registro de 4 bits, como el que se muestra en la figura E4.2. Realice el diseo utilizando instrucciones if,then,else y procesos.

Figura E4.2

Solucin Como puede observarse en la tabla que describe el comportamiento del circuito, si CLR = O, las salidas Q adoptan el valor de O; pero si CLR = 1, toman el valor de las entradas DO, DI, D2 y D3.

El cdigo del programa se observa en el siguiente listado. 1 library ieee; 2 use ieee.std_logic_1164.all; 3 entity reg4 is port( 4 D: in std_logic_vector(3 downto O); 6 Q,Qn: inout std_logic_vector(3 downto O)); 7 end reg4; 8 architecture a_reg4 of reg4 is 9 begin 10 process (CLK,CLR) begin 11 if (CLK'event and CLK;='l') then 12 if (CLR = '1' )then 13 Q <= D; 14 Qn <= not Q; 15 else 16 Q <= "0000"; 17 Qn <= "1111"; 18 end if; 19 end if; 20 end process; 21 end a_reg4;

Las variables sensitivas que determinan el comportamiento del circuito se encuentran dentro del proceso (CLR y CLK). Para transferir los datos de entrada hacia la salida es necesario, segn se expuso, generar un pulso de reloj a travs del atributo event (CLK revent and CLK = '1 ')

4.4 Contadores Los contadores son entidades muy utilizadas en el dise o lgico. La forma usual para describirlos en VHDL es mediante operaciones de incremento, decremento de datos o ambas. Como ejemplo veamos la figura 4.6 que representa un contador ascendente de 4 bits, as como el diagrama de tiempos que muestra su funcionamiento

Figura 4.6 Contador binario de cuatro bits.

Listado 4.3 Cdigo que describe un contador de 4 bits Cabe mencionar que la presentacin del diagrama de tiempos de este circuito tiene la finalidad de ilustrar el procedimiento que se sigue en la programaci n. ya que puede observarse con claridad el incremento que presentan las salidas cuando se aplica un pulso de reloj a la entrada (listado 4.3). library ieee; use ieee.std_logic_1164.all; use work.std_arith.all; entity cont4 is port( clk: in std_logic; Q: inout std_logic_vector(3 downto O)); end cont4; architecture arqcont of cont4 is begin process (clk) begin If (clk'event and clk=1)then Q <= Q + 1; end if; end process; end arqcont;

Cuando requerimos la retroalimentacin de una seal (Q < = Q+ 1), ya sea dentro o fuera de la entidad, utilizamos el modo inout (Vea seccin de Modos en Captulo 2). En nuestro caso el puerto correspondiente a Q se maneja como tal, debido a que la se al se retroalimenta en cada pulso de reloj. Notemos tambin el uso del paquete std_arith que, como ya se mencion, permite usar el operador + con el tipo std_logic _vector. El funcionamiento del contador se define b sicamente en un proceso, en el cual se llevan a cabo los eventos que determinan el comportamiento del circuito. Al igual que en los otros programas, una transicin de O a 1 efectuada por el pulso de reloj provoca que se ejecute el proceso, lo cual incrementa en 1 el valor asignado a la variable Q. Cuando esta salida tiene el valor de 15 ("1111") y si el pulso de reloj se sigue aplicando, el programa empieza a contar nuevamente de O. EJEMPLO: Elabore un programa que describa el funcionamiento de un contador de 4 bits. Realice en el dise o una se al de control (Up/Down) que determine el sentido del conteo: ascendente o descendente (Fig. E4.3).

Solucin La seal de control UpDown permite definir si el conteo se realiza en sentido ascendente o descendente. En nuestro caso, un cero aplicado a esta seal determina una cuenta ascendente: del O al 15. De esta forma, el funcionamiento del circuito queda determinado por dos seales: el pulso de reloj (clk) y la seal UpDown, como se ve en el siguiente programa.

library ieee; use ieee.std_logic_1164.all; use work.std_arith.all; entity contador is port ( clk: in std_logic; UP:in std_logic; Q: inout std_logic_vector(3 downto O)); end contador; architecture a_contador of contador is begin

process (UP, clk) begin if (clk'event and clk ='l') then if (UP = '0') then Q <= Q+l; else Q <= Q-l; end if; end if; end process; end a_contador;

Listado E4.3.

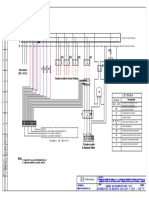

CONTADOR CON RESET Y CARGA EN PARALELO (load) La entidad de dise o que aparece en la figura 4.7a) es un ejemplo de un circuito contador s ncrono de 4 bits. Este contador tiene varias caracter sticas adicionales respecto al anterior. Su funcionamiento se encuentra predeterminado por los valores que se hallan en la tabla de la figura 4. 7b). Como se puede observar, este contador posee las entradas de control Enp y Load y seg n el valor lgico que tengan en sus terminales realizarn cualesquiera de las operaciones rese adas en la tabla. Note que la se al de Reset se activa en nivel alto de forma as ncrona por ltimo, el circuito tiene cuatro entradas en paralelo declaradas como P3, P2, P1 y PO.

a) Contador binario de 4 bits

b)tabla de funcionamiento

El propsito de describir este ejemplo radica en subrayar el uso de varias condiciones, de tal manera que no sea posible evaluar una instruccin si la(s) condicin(es) predeterminada(s) no se cumple(n). Por ejemplo, observemos el listado 4.4, donde la lnea 11 presenta la lista sensitiva de las variables que intervienen en el proceso (clk, ENP, LOAD, RESET). Ntese que no importa el orden en que se declaran. En la lnea 12 se indica que si RESET = 1, las salidas Q toman el valor de O; si no es igual a l, se pueden evaluar las siguientes condiciones (es importante resaltar que la primera condicin debe ser RESET). En la lnea 15 se observa el proceso de habilitar una carga en paralelo, por lo que si LOAD = O y ENP es una condicin de no importa ('-') que puede tomar el valor de O o 1 (segn la tabla 4.7b), las salidas Q adoptarn el valor que se halle en las entradas P (P3, P2, P1, PO). Este ejemplo muestra de forma didctica el uso de la declaracin elsif (si no-si).

1 library ieee; 2 use ieee.std_logic_1164.all; 3 use work.std_arith.all; 4 entity cont is port( 5 P: in std_logic_vector(3 downto O); 6 clk,LOAD,ENP,RESET: in std_logic; 7 Q: inout std_logic_vector(3 downto O)); 8 end cont; 9 architecture arq_cont of cont is 10 begin 11 process (clk, RESET,LOAD, ENP) begin 12 If (RESET = '1') then 13 Q <=0000; 14 elsif (clk'event and clk = '1') then 15 if (LOAD = 'O' and ENP = '-') then 16 Q <= P; 17 elsif (LOAD ='1' and ENP = '0') then 18 Q <=Q; 19 elsif (LOAD = '1' and ENP = '1') then 20 Q <= Q + 1; 21 end if; 22 end if; 23 end process; 24 end arq_cont;

4.5 Diseo de sistemas secuenciales sncronos Como ya se mencion , la estructura de los sistemas secuenciales s ncronos basa su funcionamiento en los elementos de memoria conocidos "como flip-flops. La palabra sincrona se refiere a que cada uno de estos elementos de memoria que interact an en un sistema se encuentran conectados a la misma seal de reloj, de forma tal que slo se producir un cambio de estado en el sistema cuando ocurra un flanco de disparo o un pulso en la seal de reloj. Existe una divisi n en el dise o de los sistemas secuenciales que se refiere al momento en que se producir la salida del sistema. * En la estructura de Mealy (Fig. 4.8) las seales de salida dependen. ,tanto , del estado en que se encuentra el sistema, como de la entrada que se aplica en determinado momento. * En la estructura de Moore (Hg. 4.9) la seal de salida slo depende del estado en que se encuentra..

figura 4.8 Arquitectura secuencial de Mealy.

figura 4.9 arquitectura secuencial de Moore

Un sistema secuencial se desarrolla a travs de una serie de pasos generalizados que comprenden el enunciado del problema, diagrama de estados, tabla de estados, asignacin de estados, ecuaciones de entrada a los elementos de memoria y diagrama electrnico del circuito. Como ejemplo consideremos el diseo del siguiente sistema secuencial (fig, 4.10), en el cual se emite un pulso de salida Z (Z= 1) cuando en la lnea de entrada (X) se reciben cuatro unos en forma consecutiva; en caso contrario, la salida Z es igual a cero.

Detector de secuencia.

Diagramas de estado El uso de diagramas de estados en la l gica programable facilita de manera significativa la descripci n de un dise o secuencia!, ya que no es necesario seguir la metodologa tradicional de diseo. En VHDL se puede utilizar un modelo funcional en que s lo se indica la. transici n que siguen los estados y las condiciones que controlarn el proceso. De acuerdo con nuestro ejemplo (fig. 4.12), vemos que el sistema secuencial se puede representar por medio del diagrama de estados de la figura 4.12a): arquitectura Mealy. En este diagrama se advierte que el sistema cuenta con una se al de entrada denominada X y una se al de salida Z. En la figura 4.12b) se muestra la tabla de estados que describe el comportamiento del circuito. Cuando se est en el estado d0 y la seal de entrada X es igual a uno, se avanza al estado dl y la salida Z durante esta transicin es igual a cero; en caso contrario, cuando la entrada X es igual a cero, el circuito se mantiene en el estado d0 y la salida tambin es cero (Fig. 4.11).

Con un poco de lgica se puede intuir el comportamiento del diagrama de estados. Observe como slo la secuencia de cuatro unos consecutivos provoca que la salida Z = 1.

a) Diagrama de estado

b)

tabla de estado

Este diagrama se puede codificar con facilidad mediante una descripci n de alto nivel en VHDL. Esta descripci n supone el uso de declaraciones case-when las cuales determinan, en un caso particular, el valor que tomar el siguiente estado. Por otro lado, la transici n entre estados se realiza por medio de declaraciones if-then-else, de tal forma que stas se encargan de establecer la l gica que seguir el programa para realizar la asignacin del estado. Como primer paso en nuestro diseo, consideremos los estados d0, dI, d2 y d3. Para poder representados en cdigo VHDL, hay que definidos dentro de un tipo de datos enumerado2 (apndice C) mediante la declaracin type. Observemos la forma en que se listan los identificadores de los estados, as como las seales utilizadas para el estado actual (edo_presente) y siguiente (edo_futuro):

type estados is (dO, dl, d2, d3) ; signal edo_presente, edo_futuro': estados; El siguiente paso consiste en la declaraci n del proceso que definir el comportamiento del sistema. En ste debe considerarse que el edo_futuro depende del valor del edo_presente y de la entrada X. De esta manera la lista sensitiva del proceso quedara de la siguiente forma: procesol: process (edo_presente, X) Dentro del proceso se describe la transicin del edo_presente al edo_futuro. Primero se inicia con la declaracin case que especifica el primer estado que se va a evaluar, en nuestro caso consideremos que el anlisis comienza en el estado d0 (when d0), donde la salida Z siempre es cero sin importar el valor de X. Si la entrada X es igual a 1 el estado futuro es d1; en caso contrario, es d0. De este modo, la declaracin del proceso quedara de la siguiente manera:

proceso1: process (edo_presente,X) begin case edo-presente is when dO => Z<= 'O'; if X ='1' then edo_futuro <= dl; else edo_futuro <= dO; end if;

Ntese que en cada estado debe indicarse el valor de la salida (Z < = O) despus de la condicin when, siempre y cuando la variable Z no cambie de valor. En el listado 4.5 se muestra la definici n completa del c digo explicado. Como podemos observar, en el programa se utilizan dos procesos. En el primero, proceso l (lnea 11) se describe la transicin que sufren los estados y las condiciones necesarias que determinan dicha transicin. En el segundo, proceso2 (lnea 42) se lleva a cabo de manera sncrona la asignacin del estado futuro al estado presente, de suerte que cuando se aplica un pulso de reloj, el proceso se ejecuta. En la lnea 31 se describe la forma de programar la salida Z en el estado d3 cuando sta obtiene el valor de O o 1, segn el valor de la entrada X.

1 library ieee: 2 use ieee.std_logic_1164.all; 3 entity diagrama ls port( 4 clk,X: in std_logic; 5 Z: out std_logic); 6 end diagrama; 7 architecture arq_diagrama of diagrama is 8 type estados is (d0, d1, d2, d3); 9 signal edo_presente, edo_futuro: estados; 10 begin 11 proceso1: process (edo_presente, X) begin 12 case edo_presente is 13 when d0 => Z <=0; 14 if X ='1 then 15 edo_futuro <= d1; 16 else 17 edo_futuro <= d0; 18 end if; 19 when d1 => Z <='0'; 20 if X='1' then 21 edo_futuro <= d2; 22 else 23 edo_futuro <= d1; 24 end if; 25 when d2 = > Z < = 0; 26 If X ='l' then 27 edo_futuro <= d3; 28 else 29 edo_futuro <=, d0; 30 end if;

31 when d3 => Z <='0'; 32 if X='l' then 33 edo_futuro <= d0; 34 Z <='l' ; 35 else 36 edo_futuro <= d3; 37 Z <= '0'; 38 end if; 39 end case; 40 end process procesol; 41 42 proceso2: process(clk) begin 43 if (clk'event and clk='l') then 44 edo_presente <= edo_futuro; 45 end if; 46 end process proceso2; 47 end arq_diagrama;

Listado 4.5 Diseo de un diagrama de estados

Ejemplo 4.4 Se requiere programar el diagrama de estados de la figura E4.4.

Figura E4.4 Diagrama de estados

Solucin Por ejemplo, en la figura E4.4 notamos que el circuito pasa al estado q1 con el primer 1 de entrada y al estado q2 con el segundo. Las salidas asociadas con estas dos entradas son O, segn se seala. La tercera entrada consecutiva de 1 genera un 1 en la salida y hace que el circuito pase al estado q3. Una vez que se encuentra en q3. el circuito permanecer en este estado, emitiendo salidas 0.

En lo que respecta a la programaci n en VHDL, este ejemplo sigue la misma metodologa que el ejercicio anterior (fig. 4.12), la cual consiste en usar estructuras casewhen y tipo de datos enumerado, que en este caso contiene los cinco estados (q0, q1, q2, q3 y q4) que componen el diagrama. El listado correspondiente al programa se encuentra a continuacin listado E4.4.

library ieee; use ieee.std_logic_1164.all; entity diag is port( clk,x: in std_logic; z: out std_logic); end diag; architecture arq_diag of diag is type estados is (q0,q1,q2,q3,q4); signal edo_pres, edo_fut: estados; begin proceso1: process (edo_pres,x) begin case edo_pres is when q0 => z <= 0; if x = 0 then edo_fut <= q4; else edo_fut <= q1; end if; when ql => z <= 0

if x = 0 then edo_fut <= q4; else edo_fut <= q2; end if; when q2 => z <= 0; if x = 0 then edo_fut <= q4; z <= 0; else edo_fut <= q3; z <= 1; end if; when q3 => z <= 0; if x = 0 then edo_fut <= q3; else edo_fut <= q3; end if;

when q4 => z <= 0; if x = 0 then edo_fut <= q4; else edo_fut <= ql; end if; end case; end process procesol; proceso2: process (clk) begin if (clkevent and clk=l) then edo_pres <= edo_fut; end if; end process proceso2; end arq_diag;

FIN DE DIAPOSITIVAS

Potrebbero piacerti anche

- Contadores y RegistrosDocumento19 pagineContadores y RegistrosElymar91Nessuna valutazione finora

- Diseno SecuencialDocumento28 pagineDiseno SecuencialJacqueline Ponce Pinos100% (4)

- Modeladoy SimulacionDocumento36 pagineModeladoy Simulacionanblor71Nessuna valutazione finora

- Trabajo Final1 - VHDLDocumento7 pagineTrabajo Final1 - VHDLElyel Surco M0% (1)

- Aplicaciones Con VHDLDocumento6 pagineAplicaciones Con VHDLViny Pazmiño50% (2)

- Reporte Practica Flip FlopsDocumento18 pagineReporte Practica Flip FlopsChamín AlcántaraNessuna valutazione finora

- Conversión de Código Gray A 7 SegmentoDocumento8 pagineConversión de Código Gray A 7 SegmentoValentina RoyeroNessuna valutazione finora

- Los PLDSDocumento38 pagineLos PLDSLuisMateoNessuna valutazione finora

- Tarea 1investigación - Operaciones LógicasDocumento6 pagineTarea 1investigación - Operaciones Lógicasroberto roblesNessuna valutazione finora

- Timer 555Documento15 pagineTimer 555oconer51Nessuna valutazione finora

- Sistema de Automatizacion S7 200Documento478 pagineSistema de Automatizacion S7 200Jhonny Zambrano SaavedraNessuna valutazione finora

- Conversión de Una Función de Transferencia A Un Circuito Eléctrico Con OpAmps.Documento11 pagineConversión de Una Función de Transferencia A Un Circuito Eléctrico Con OpAmps.Dulce Rivsan83% (6)

- Historia Del Control de Clásico A Moderno, Concepto de Control y Diferencias Entre Control y Automatización.Documento11 pagineHistoria Del Control de Clásico A Moderno, Concepto de Control y Diferencias Entre Control y Automatización.LogicTutosNessuna valutazione finora

- Trabajo Practico Flip-Flops y Circuitos Secuenciales PDFDocumento10 pagineTrabajo Practico Flip-Flops y Circuitos Secuenciales PDFDonaldo Leonel Vargas AnguloNessuna valutazione finora

- Practica 4 Moc3011..Documento19 paginePractica 4 Moc3011..JOSSSG0750% (2)

- Modelado de Circuitos ElectricosDocumento30 pagineModelado de Circuitos Electricosjlola100% (1)

- Modelo Matematico de AmortiguadorDocumento9 pagineModelo Matematico de AmortiguadorLenny Rayssa Huayllas CalaniNessuna valutazione finora

- Ejemplo Resuelto Comp Ens Adores LGRDocumento3 pagineEjemplo Resuelto Comp Ens Adores LGRFreddy Israel Peñaloza Rangel0% (1)

- Parte 12 VHDL Lenguaje de Descripcion de Hardware EnviarDocumento110 pagineParte 12 VHDL Lenguaje de Descripcion de Hardware Enviarhoola100% (2)

- Transmisiones y Reductores PDFDocumento26 pagineTransmisiones y Reductores PDFcirilo martinezNessuna valutazione finora

- Tiristores y Dispositivos de ConmutacionDocumento19 pagineTiristores y Dispositivos de Conmutacionricardo gomezNessuna valutazione finora

- Reporte Pract1 EmbebidosDocumento15 pagineReporte Pract1 Embebidosfedexin_40Nessuna valutazione finora

- Flip-Flops (Electronica Digital)Documento24 pagineFlip-Flops (Electronica Digital)apolo yisusNessuna valutazione finora

- Registros Del 8088Documento7 pagineRegistros Del 8088José ArturoNessuna valutazione finora

- Fpga y PLD, VHDL y VerilogDocumento6 pagineFpga y PLD, VHDL y VerilogLuis PintadoNessuna valutazione finora

- Diseño de Controlador Tipo PIDDocumento10 pagineDiseño de Controlador Tipo PIDJorge CarpioNessuna valutazione finora

- Proyecto Final. Levitador de AireDocumento7 pagineProyecto Final. Levitador de AireDaniela RochaNessuna valutazione finora

- Manual de Lookout A DistanciaDocumento10 pagineManual de Lookout A DistanciaFranklinNessuna valutazione finora

- Respuesta de Sistemas de Primer y Segundo OrdenDocumento10 pagineRespuesta de Sistemas de Primer y Segundo OrdenJhona CervantesNessuna valutazione finora

- Informe 6 Vicente AlvarezDocumento17 pagineInforme 6 Vicente AlvarezVicente AlvarezNessuna valutazione finora

- Que Es CoDeSysDocumento7 pagineQue Es CoDeSysFsaul Lazaro YarangaNessuna valutazione finora

- Teorema Del Muestreo y El Problema Del Enmascaramiento de SeñalesDocumento4 pagineTeorema Del Muestreo y El Problema Del Enmascaramiento de SeñalesJesus Antonio Mtz100% (2)

- Los Bits de La Palabra de EstadoDocumento6 pagineLos Bits de La Palabra de Estadonazaeth_10Nessuna valutazione finora

- Observador de Estados para Un Motor DCDocumento9 pagineObservador de Estados para Un Motor DCJoseph Manuel Chamochumbi IndaraNessuna valutazione finora

- Sistema MecatrónicoDocumento5 pagineSistema Mecatrónicoprestige23Nessuna valutazione finora

- Control de Fase ArduinoDocumento8 pagineControl de Fase ArduinoLuis FherNessuna valutazione finora

- Criterio de RouthDocumento9 pagineCriterio de RouthFabio SplendorNessuna valutazione finora

- Controladores Digitales de Señales 2003Documento26 pagineControladores Digitales de Señales 2003phillamxNessuna valutazione finora

- Contador Gray VHDLDocumento5 pagineContador Gray VHDLIsraelDeLaRosaNessuna valutazione finora

- Informe 1 Microporcesadores 1Documento4 pagineInforme 1 Microporcesadores 1Rodrigo CoriaNessuna valutazione finora

- Informe ProyectoDocumento6 pagineInforme ProyectoJorge ZambranoNessuna valutazione finora

- Semaforo Con VHDLDocumento7 pagineSemaforo Con VHDLTuMacho Castigador0% (1)

- Modelo, Pendulo InvertidoDocumento9 pagineModelo, Pendulo InvertidoJose VillamizarNessuna valutazione finora

- Contador DijitalDocumento10 pagineContador Dijitaltomkito100% (1)

- Tipos y Características de RobotsDocumento32 pagineTipos y Características de RobotsGray Kwon Fullbuster100% (1)

- Contador Con Flip-FlopDocumento19 pagineContador Con Flip-FlopMiguel Angel CasiqueNessuna valutazione finora

- 14 y 15 Analisis Del Controlador PID y Repaso LGR BODEDocumento85 pagine14 y 15 Analisis Del Controlador PID y Repaso LGR BODEMIJAELNessuna valutazione finora

- Modelado en El Espacio de EstadosDocumento3 pagineModelado en El Espacio de EstadosstvanNessuna valutazione finora

- Criterios de Estabilidad JURYDocumento13 pagineCriterios de Estabilidad JURYDavid NietoNessuna valutazione finora

- Fuentes Internas y Externas Del Pic 16f877aDocumento4 pagineFuentes Internas y Externas Del Pic 16f877aAndres BasantesNessuna valutazione finora

- Control de Un Motor DC Mediante Realimentación de EstadosDocumento2 pagineControl de Un Motor DC Mediante Realimentación de EstadosAndres AndradeNessuna valutazione finora

- Como Hacer Reloj DigitalDocumento9 pagineComo Hacer Reloj DigitalSusy VillafanNessuna valutazione finora

- Control de Posicion de Un Motor de CD Con EncoderDocumento6 pagineControl de Posicion de Un Motor de CD Con EncoderDewi Hdez GlezNessuna valutazione finora

- Estructura de Un Sistema SecuencialDocumento80 pagineEstructura de Un Sistema SecuencialOvanio MolinaNessuna valutazione finora

- Clase14 - VHDL - Diagrama Maquinas EstadoDocumento14 pagineClase14 - VHDL - Diagrama Maquinas EstadoMylo AlfonsoNessuna valutazione finora

- 3 - Diseno Logico Secuencial Con VHDLDocumento16 pagine3 - Diseno Logico Secuencial Con VHDLBryan ToapaxiNessuna valutazione finora

- Capitulo 11Documento12 pagineCapitulo 11Oscar SierraNessuna valutazione finora

- Diseño Lògico Secuencial Con VHDLDocumento23 pagineDiseño Lògico Secuencial Con VHDLjuanjnv2Nessuna valutazione finora

- Laboratorio - Reg Desplazamiento y Contadores - VHDLDocumento12 pagineLaboratorio - Reg Desplazamiento y Contadores - VHDLvickysalazar6165Nessuna valutazione finora

- Practica Del SemaforoDocumento14 paginePractica Del SemaforoCristian EscobarNessuna valutazione finora

- Panel de Control Con PLC para La Obtención de Carbonato de Calcio"Documento120 paginePanel de Control Con PLC para La Obtención de Carbonato de Calcio"ENIC-AITCGNessuna valutazione finora

- Camus ColegioDocumento18 pagineCamus ColegioENIC-AITCGNessuna valutazione finora

- Calendario DIC 2022Documento1 paginaCalendario DIC 2022ENIC-AITCGNessuna valutazione finora

- Examen Diagnostico Temas Sel. FisicaDocumento2 pagineExamen Diagnostico Temas Sel. FisicaENIC-AITCGNessuna valutazione finora

- Reglamento CamusDocumento12 pagineReglamento CamusENIC-AITCGNessuna valutazione finora

- Examenes de 5to de PrimariaDocumento62 pagineExamenes de 5to de PrimariaENIC-AITCG50% (4)

- Formato - Planeacion SemanalDocumento2 pagineFormato - Planeacion SemanalENIC-AITCGNessuna valutazione finora

- Formato de CAEDDocumento6 pagineFormato de CAEDENIC-AITCG100% (1)

- Formato de OrientacionDocumento9 pagineFormato de OrientacionENIC-AITCGNessuna valutazione finora

- Carta de RecomendacionDocumento2 pagineCarta de RecomendacionENIC-AITCGNessuna valutazione finora

- Examen de Matematicas Primaria001Documento5 pagineExamen de Matematicas Primaria001ENIC-AITCGNessuna valutazione finora

- Contrato de ArrendamientoDocumento4 pagineContrato de ArrendamientoENIC-AITCGNessuna valutazione finora

- Examen de Matematicas Primaria010Documento5 pagineExamen de Matematicas Primaria010ENIC-AITCGNessuna valutazione finora

- Proceso de Anodizado Del AluminioDocumento13 pagineProceso de Anodizado Del AluminioLuisPa Flores100% (2)

- Artes y EtiquetasDocumento2 pagineArtes y EtiquetasJuan Pablo MarroquínNessuna valutazione finora

- L5 Característica de Magnetizacion Motor SincronicoDocumento8 pagineL5 Característica de Magnetizacion Motor SincronicoPablo HernandezNessuna valutazione finora

- Presentacion Cortadora CT-1000 PlusDocumento13 paginePresentacion Cortadora CT-1000 Plusrolando quispeNessuna valutazione finora

- Cktos y Sus ElementosDocumento36 pagineCktos y Sus ElementosAnonymous lrrwBxUYNessuna valutazione finora

- SistemadetelecomunicacionenunentornoDocumento7 pagineSistemadetelecomunicacionenunentornopathtrakNessuna valutazione finora

- Recepcion de HerramientasDocumento2 pagineRecepcion de HerramientasCristhian Bal LeonNessuna valutazione finora

- Fm/Am Compact Disc Player: CDX-GT350S CDX-GT350Documento2 pagineFm/Am Compact Disc Player: CDX-GT350S CDX-GT350Alejandro Luna OlmosNessuna valutazione finora

- Ensayo Industriales Motores ElectricosDocumento8 pagineEnsayo Industriales Motores ElectricosEddys BuriNessuna valutazione finora

- Terminología en FotografíaDocumento6 pagineTerminología en FotografíapamelataboadalozanoNessuna valutazione finora

- Revisión Diseño Electrico PolideportivoDocumento8 pagineRevisión Diseño Electrico Polideportivoignacio5173100% (1)

- Motores Sincronicos y AsincronicosDocumento12 pagineMotores Sincronicos y AsincronicossandyNessuna valutazione finora

- APM Codigos de AveriaDocumento4 pagineAPM Codigos de AveriaPedro Ruiz Aguirre81% (21)

- Electroplateado Con OroDocumento8 pagineElectroplateado Con OroBrayAndres CastañoNessuna valutazione finora

- Práctica No 4 - Circuito de Disparo Por DIACDocumento4 paginePráctica No 4 - Circuito de Disparo Por DIACMauricio GuevaraNessuna valutazione finora

- Hoja de VidaDocumento4 pagineHoja de VidaJoha PastranNessuna valutazione finora

- Informe 1Documento13 pagineInforme 1Felipe ChaconNessuna valutazione finora

- Informe Electronica de Potencia 1Documento4 pagineInforme Electronica de Potencia 1Jhon VargasNessuna valutazione finora

- K0000 03Documento13 pagineK0000 03Francisco HuitzilNessuna valutazione finora

- HIDROBORACIONDocumento11 pagineHIDROBORACIONCatalina Pardo LippeltNessuna valutazione finora

- L12 PDFDocumento1 paginaL12 PDFDavid Aurora MendozaNessuna valutazione finora

- 2012 Sierra Manual Propietario PDFDocumento554 pagine2012 Sierra Manual Propietario PDFEdgar Ta ValNessuna valutazione finora

- Cuestionario ConmutacionDocumento12 pagineCuestionario ConmutacionHenry FloresNessuna valutazione finora

- Ceramicos y AsfaltoDocumento6 pagineCeramicos y AsfaltoJavier Pillaca CámaraNessuna valutazione finora

- Manual QuirofanosDocumento37 pagineManual Quirofanoscrl22103650% (2)

- CAESDocumento1 paginaCAESAndres Alberto Soto JañaNessuna valutazione finora

- Mods de Clarificador para Radios CB - 10 MetrosDocumento7 pagineMods de Clarificador para Radios CB - 10 MetrosGerardo Hernández100% (1)

- Micro Seguridad Con Protección y Bobina PDFDocumento8 pagineMicro Seguridad Con Protección y Bobina PDFSergio A. A.Nessuna valutazione finora

- Fisica Iii Civ 221: Docente: Ing. Joel Paco SDocumento17 pagineFisica Iii Civ 221: Docente: Ing. Joel Paco SbrattNessuna valutazione finora

- Error F70 Solución de ProblemasDocumento24 pagineError F70 Solución de ProblemasJaime Alonso Olaya SánchezNessuna valutazione finora