Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

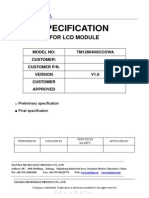

Traffic Control System

Caricato da

Sandhya DeviTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Traffic Control System

Caricato da

Sandhya DeviCopyright:

Formati disponibili

Traffic Control System The objective of the project is to design a traffic control system for a 3 way crossing.

Here three roads cross each other. In our design, one road one have the highest priority. Any moment a vehicle arrives the crossing it would have a GO signal. The other two roads, would have a STOP signal at that moment. When there is no vehicles on the crossing and there are vehicles on the second road to cross the highway; third road would have a STOP signal and second Road Vehicles would have a GO signal. But it depends on Highway traffic density. It highway traffic density is high then second road would not get a GO signal, vehicles on third road would keep going. UART In this project a UART is modeled using verilog HDL. UART is a device that has the capability to both receive and transmit serial data. UART exchanges text data in an American Standard Code for Information Interchange (ASCII) format in which each alphabetical character is encoded by 7 bits and transmitted as 8 data bits. For transmission the UART protocol wraps this 8 bit sub-word with a start bit in the least significant bit (LSB) and a stop bit in the most significant bit (MSB) resulting in a 10 bit word form. At UART transmitter controls transmission by fetching a data word in parallel format and directing the UART to transmit it in a serial format. Likewise, the Receiver must detect transmission, receive the data in serial format, strip of the start and stop bits, and store the data word in a parallel format. Since the UART is asynchronous in working, the receiver does not know when the data will come, so receiver generate local clock in order to synchronize to transmitter whenever start bit is received. Asynchronous transmission allows data to be transmitted without the sender having to send a clock signal to the receiver. The transmitter and receiver agree on timing parameters in advance and special bits are added to each word which is used to synchronize the sending and receiving units. Design of 16 bit RISC Processor using Verilog This project includes the designing of 16-Bit RISC processor and modeling of its components using Verilog HDL. The instruction set adopted here is extremely simple that gives an insight into the kind of hardware which should be able to execute the set of instructions properly. Along with sequential and combinational building blocks of NON- pipelined processor such as adders and registers more complex blocks i.e. ALU and Memories had been designed and simulated. The modeling of ALU which has been done in this project is fully structural starting from half adders. Complex blocks have been modeled using behavioral approach i.e. Memories, whereas simple blocks i.e. Adders had been done through structural approach. Implementation of Huffman decoder in fpga using verilog Compression technology has gained significance due to various reasons. A typical audio clip lasts for at least 3 minutes. This would amount to a storage requirement of around 8-9MB for PCM audio samples. Storing of an uncompressed signal requires a large amount of space. Data compression reduces the number of bits required to store and transmit the information . Due to the explosion of multimedia applications, effective compression techniques are becoming essential. Huffman coding is a loss- less compression technique, often used in lossy compression schemes as the final step after decomposition and quantization of a signal. Huffman coding uses unique variable length code words and no Huffman code is prefix of the other codes in the table. For a given probability density function of symbol set, by assigning short codes to frequently occurring symbols and longer codes to infrequently occurring symbols, Huffman's minimum redundancy encoding minimizes the average number of bi t s required to represent the data . Huffman coding is one of the Variable Length Coding (VLC). Huffman coding is useful for the reduction of bit-rate by exploring statistical redundancies and to encode a "minimum set" of information using entropy-coding technique. Usually entropy coders exploit the symbol probabilities independent of previous symbol , and hence they are optimal for uncorrelated sequences. Simulation and Synthesis of Advance Encryption Standard Algorithm This project implements fully pipelined FPGA of AES Encryption and Decryption (acronym for Advance Encryption Standard, also known as Rijndael Algorithm).The implementation of AES has been made both in sequential and pipeline architectures and we are able to compare the results as an area time trade-off. In sequential architecture, the design occupies 2744 CLB slices and achieved a throughput of 258.5 Mbits/s and there is no use of extra memory resources like FPGA BRAMs. On the other hand, pipeline design occupies a total of 2136 CLB slices and achieved a throughput of 2868 Mbits/s. Both designs were realized on VirtexE family of devices (XCV812). The performance figures

achieved by our implementations are not only efficient in terms of throughput but also area occupied by them are among the most economical reported up-to-date. AES has a fixed block size of 128 bits and a key size of 128, 192 or 256 bits, whereas Rijndael can be specified with key and block sizes in any multiple of 32 bits, with a minimum of 128 bits and a maximum of 256 bits. AES operates on a 44 array of bytes, termed the state. For encryption, each round of AES (except the last round) consists of four stages. a) SubBytes - a non-linear substitution step where each byte is replaced with another according to a lookup table (known as S Box). b) ShiftRows - a transposition step where each row of the state is shifted cyclically a certain number of steps. c) MixColumns - a mixing operation which operates on the columns of the state, combining the four bytes in each column using a linear transformation. d) AddRoundKey - each byte of the state is combined with the round key; each round key is derived from the cipher key using a key schedule.

Implementation of multichannel UART on FIFO technique The Multi Channel Uart Contains more than one transmit/receive per uart. All the channels can operate independently or together. Data can be received on one and transmitted on other and also the data rate on different channels can be same or different. The channels of the Multi channel uart are designed to reduce the CPU overhead when working with high speed modems and other devices. Here we are implementing a multi channel Uart which contains 4 Uarts. This multi channel uart operates in three modes one is Normal mode, second is Hub mode and last is Bridge Mode. In Normal mode all these Uarts are completely independent in functionality, but share common logic to reduce its overall size as compared to individual instantiations. In Hub mode the data received by the uart will be transmit by the other uarts. In Bridge mode the data received by the Uart1is Transmitted by the Uart2 and the data received by the Uart3 is transmitted by the Uart4. In this both the Uarts operates at different Baud rates. Each channel performs serial to parallel conversion on data characters received from a peripheral device, and parallel to serial conversion on data characters received from the CPU. The CPU can read the complete status of each channel at any time. Synchronization for the serial data stream is accomplished by adding start and stop bits to the transmit data to form a data character. An optional parity bit can be attached to the data character to enhance Data integrity. The receiver checks the parity bit for any transmission bit errors. Each channel has its own baud rate value, receive and transmit FIFO and CPU registers. The user has control over the configuration of the core by modifying the parameters in the top-level source file. This allows the core to be modified and reused easily. These parameters include number of channels and FIFO depth

Design of a 32-bit RISC Microprocessor with Floating Point Unit This project designs a 32-bit RISC microprocessor with a floating point unit. The Floating Point Unit which can be viewed as a coprocessor to the microprocessor that was designed. The 32-bit RISC microprocessor with floating point unit is a more specialized device, but it still maintains a wide range of possible implementations. It can store and manipulate large data sets, and handle real number calculations that may be necessary in the field. These applications would tend to be directed to mathintensive operations, such as data processing. With a more specialized functionality that provides faster and more accurate outputs compared to a general microprocessor. Due to the specialty of the processor it is often encouraged to implement it as part of a multi-core processing set. This particular processor can be implemented within web controllers, graphics processors, as well as mobile GPS devices. Implementation of floating point arithmetic on FPGA Floating point operations are hard to implement on FPGAs because of the complexity of their algorithms. On the other hand, many scientific problems require floating point arithmetic with high levels of accuracy in their calculations. This project explores fpga implementations of addition and multiplication for IEEE-754 single precision floating-point numbers. For floating point multiplication, in IEEE single precision format, we have to multiply two 24 bits. In this method existing 18 bit multiplier is replaced with a dedicated 24 bit multiplier designed with small 4 bit multiplier. For floating point addition, exponent matching and shifting of 24 bit mantissa and sign logic are coded in behavioural style. Convolutional Encoder and Viterbi Decoder In digital communication system, the transmitted data is presented in binary form that is modulated to analog waveforms and transmitted through a channel to a receiver. In the channel the

noise and interference corrupt the transmitted signal, which is mapped back to binary bits in the receiver. Some bit errors may occur if the interference is too strong so channel coding is often used to prevent these errors. The channel coding means that extra bits are added to the transmitted data and these bits are then used when reconstructing transmitted data sequence in the receiver. There are many different methods for channel coding like linear block codes and convolutional codes. In block coding, the encoder accepts a k-bit message block and generates an n-bit code word. Thus, code words are produced on a block by block basis. A provision has to be made in the encoder to buffer an entire message block buffer generating the associated code word. Generally, we have the message coming in serially rather than in blocks, in which case the use of the buffer may be undesirable. In such situations, convolutional coding might be preferred. A convolutional code is generated by passing the information sequence to be transmitted through a linear finite state shift register. Hence, the block of n code digits generated by a convolutional encoder at a time depends not only on the block of message bits at that time, but also on N-1 previous blocks of data. An advantage of convolutional coding is that it can be applied to a continuous data stream as well as to blocks of data. Like block codes, convolutional codes can be designed to either detect or correct errors. However, as data is retransmitted in blocks, block codes are better suited for error detection and convolutional codes are mainly used for error correction. DESIGN, VERIFICATION AND SYNTHESIS OF SYNCHRONOUS FIFO FIFO is a First-In-First-Out memory queue with control logic that manages the read and write operations, generates status flags, and provides optional handshake signals for interfacing with the user logic. It is often used to control the flow of data between source and destination. FIFO can be classified as synchronous or asynchronous depending on whether same clock or different (asynchronous) clocks control the read and write operations. In this project the objective is to design, verify and synthesize a synchronous FIFO using binary coded read and write pointers to address the memory array. FFIO full and empty flags are generated and passed on to source and destination logics, respectively, to pre-empt any overflow or underflow of data. In this way data integrity between source and destination is maintained. The RTL description for the FIFO is written using Verilog HDL.

Potrebbero piacerti anche

- L-TRI - Assembly-Operation-Maintenance Guide - AGS531883-01 - 2014-02Documento52 pagineL-TRI - Assembly-Operation-Maintenance Guide - AGS531883-01 - 2014-02Hani SamirNessuna valutazione finora

- IP Basics: Rajkumar DE (5ESS) ALTTC, GhaziabadDocumento55 pagineIP Basics: Rajkumar DE (5ESS) ALTTC, GhaziabadtlnarasimhamNessuna valutazione finora

- Article Antenna Mag Loop 2Documento33 pagineArticle Antenna Mag Loop 2PENIKMAT KOPI VESPA & RADIONessuna valutazione finora

- NPDCDocumento48 pagineNPDCEbby OnyekweNessuna valutazione finora

- FPGA Implementation of I C & SPI Protocols: A Comparative StudyDocumento4 pagineFPGA Implementation of I C & SPI Protocols: A Comparative StudyjanepriceNessuna valutazione finora

- Implementation of Uart and Ethernet Using FpgaDocumento15 pagineImplementation of Uart and Ethernet Using FpgaBANDARU SRI RAM SAI GANESH BANDARU SRI RAM SAI GANESHNessuna valutazione finora

- Luces John DeereDocumento26 pagineLuces John DeereIván CascudoNessuna valutazione finora

- Multichannel UartDocumento16 pagineMultichannel UartMani Bharath Nuti100% (2)

- Efficiently Triggering Debugging and Decoding Low-Speed Serial BusesDocumento19 pagineEfficiently Triggering Debugging and Decoding Low-Speed Serial BusesVipin JainNessuna valutazione finora

- Hypertransport Technology SeminarDocumento27 pagineHypertransport Technology Seminarvaishanvi50% (4)

- Design and Verification of High Speed Protocols and Algorithms in Digital Communication Systems Using Verilog and VHDLDocumento5 pagineDesign and Verification of High Speed Protocols and Algorithms in Digital Communication Systems Using Verilog and VHDLChristo ElginNessuna valutazione finora

- 20.verification of Four Port Router For Network On Chip (Noc)Documento5 pagine20.verification of Four Port Router For Network On Chip (Noc)vijaykannamallaNessuna valutazione finora

- Open Access: High Throughput Compact Delay Insensitive Asynchronous NOC RouterDocumento3 pagineOpen Access: High Throughput Compact Delay Insensitive Asynchronous NOC RouterAshok Siva Kumar PoojalaNessuna valutazione finora

- Documents - Pub Hyper Transport Technology 5584a1e483247Documento26 pagineDocuments - Pub Hyper Transport Technology 5584a1e483247shaheen sayyad 463Nessuna valutazione finora

- Nine port router design and verificationDocumento5 pagineNine port router design and verificationSamNessuna valutazione finora

- A Survey On Designing of Turbo Encoder & Turbo DecoderDocumento8 pagineA Survey On Designing of Turbo Encoder & Turbo DecoderIJAFRCNessuna valutazione finora

- Ijert Ijert: Implementation of Interleaving Switch Based Architecture For System On ChipDocumento7 pagineIjert Ijert: Implementation of Interleaving Switch Based Architecture For System On ChipAkhila ReddyNessuna valutazione finora

- Vlsi Imlememt of OdfmDocumento10 pagineVlsi Imlememt of OdfmShrey MalikNessuna valutazione finora

- Design Low Power Physical Layer of NB-IOT LTE Uplink ReceiverDocumento17 pagineDesign Low Power Physical Layer of NB-IOT LTE Uplink Receiversadsadasdsad asdasdaNessuna valutazione finora

- Computer Organization Short-1Documento5 pagineComputer Organization Short-1veyide7506Nessuna valutazione finora

- IEEE International Multi Topic Conference Paper Publication: E1 Stream Analyzer Capturing CSS-7Documento6 pagineIEEE International Multi Topic Conference Paper Publication: E1 Stream Analyzer Capturing CSS-7Ali AzharNessuna valutazione finora

- Abbreviations Advanced RCS 1Documento8 pagineAbbreviations Advanced RCS 1seba paezNessuna valutazione finora

- Ipv6 AddressDocumento51 pagineIpv6 AddressWeb TestNessuna valutazione finora

- 3D Multiprocessor With 3D Noc Architecture Based On Tezzaron TechnologyDocumento5 pagine3D Multiprocessor With 3D Noc Architecture Based On Tezzaron TechnologyMos RemNessuna valutazione finora

- Redes de Datos: María Jesús CarvajalDocumento34 pagineRedes de Datos: María Jesús CarvajalLuis Fernando ManzanoNessuna valutazione finora

- Eigrp 1Documento3 pagineEigrp 1Saif Ul IslamNessuna valutazione finora

- Synchronizing Two FPGA's For A Reliable Communication: Mercy SubaramanDocumento4 pagineSynchronizing Two FPGA's For A Reliable Communication: Mercy SubaramanIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalNessuna valutazione finora

- FPGA Implementation of AES Encryption and DecryptionDocumento16 pagineFPGA Implementation of AES Encryption and DecryptionSatya NarayanaNessuna valutazione finora

- FPGA-based multi-protocol data acquisition systemDocumento4 pagineFPGA-based multi-protocol data acquisition systemVibin MammenNessuna valutazione finora

- FPGA Based Efficient Implementation of Viterbi Decoder: Anubhuti KhareDocumento6 pagineFPGA Based Efficient Implementation of Viterbi Decoder: Anubhuti KhareKrishnateja YarrapatruniNessuna valutazione finora

- 8 Design of BISTDocumento54 pagine8 Design of BISTvsangvai26Nessuna valutazione finora

- Cisco ProtocolsDocumento9 pagineCisco ProtocolsEric ResuelloNessuna valutazione finora

- Implementation of UART With BIST Technique in Fpga: Bibin M C, Premananda B SDocumento5 pagineImplementation of UART With BIST Technique in Fpga: Bibin M C, Premananda B SdelviNessuna valutazione finora

- UartDocumento25 pagineUartWajeed Mohamad100% (2)

- Vlsi Impimentation of OfdmDocumento13 pagineVlsi Impimentation of Ofdmprashanth68760100% (1)

- Research Inventy: International Journal of Engineering and ScienceDocumento7 pagineResearch Inventy: International Journal of Engineering and ScienceresearchinventyNessuna valutazione finora

- The ONE simulatorDocumento27 pagineThe ONE simulatorABHISHEK KUMAR SAHNessuna valutazione finora

- High Speed Data Logging and Control SystemDocumento59 pagineHigh Speed Data Logging and Control SystemmknunwalNessuna valutazione finora

- VST Case StudyDocumento9 pagineVST Case StudyBobby NelsonNessuna valutazione finora

- CC C!C" C##: C C C C C CCJDocumento12 pagineCC C!C" C##: C C C C C CCJsatyagireeshNessuna valutazione finora

- Controller Area Network (CAN) Core - iCAN: Intelliga Integrated Design LTDDocumento6 pagineController Area Network (CAN) Core - iCAN: Intelliga Integrated Design LTDpeter003Nessuna valutazione finora

- Design and Verification of Five Port Router Network For Network On ChipDocumento8 pagineDesign and Verification of Five Port Router Network For Network On ChipMohammad Seemab AslamNessuna valutazione finora

- Operation of Pci BusDocumento7 pagineOperation of Pci BusRohini JosephNessuna valutazione finora

- Implementation Methodology of High Performance Multi Byte Data Access Control of AMBA BusDocumento5 pagineImplementation Methodology of High Performance Multi Byte Data Access Control of AMBA BusKumar Goud.KNessuna valutazione finora

- Design and Implementation of UartDocumento21 pagineDesign and Implementation of Uartbhanu455Nessuna valutazione finora

- OFDM in VerilogDocumento6 pagineOFDM in VerilogMarwan AhmedNessuna valutazione finora

- Encoder Communications HanbookDocumento16 pagineEncoder Communications HanbooksvinagaNessuna valutazione finora

- OPC & NetworkingDocumento60 pagineOPC & NetworkingAnil Nair100% (1)

- ADPCM ImplementationDocumento13 pagineADPCM ImplementationDumitru GheorgheNessuna valutazione finora

- Management-Design and Implementation of UART-Mahesh GiriDocumento6 pagineManagement-Design and Implementation of UART-Mahesh GiriBESTJournalsNessuna valutazione finora

- Snug04 Bromley Smith PaperDocumento16 pagineSnug04 Bromley Smith PaperDheeraj SinglaNessuna valutazione finora

- Circuit Emulation Over IP Network ModulesDocumento13 pagineCircuit Emulation Over IP Network ModulesΗλίας ΚαρρόςNessuna valutazione finora

- Presentation by Akhil GDocumento17 paginePresentation by Akhil GAkhil Akhil GNessuna valutazione finora

- Socwire: A Network-On-Chip Approach For Reconfigurable System-On-Chip Designs in Space ApplicationsDocumento17 pagineSocwire: A Network-On-Chip Approach For Reconfigurable System-On-Chip Designs in Space Applicationsv711Nessuna valutazione finora

- Ass 4 FatimaDocumento13 pagineAss 4 Fatima70131348Nessuna valutazione finora

- Hyper Transport Technology: The I/O Bandwidth ProblemDocumento8 pagineHyper Transport Technology: The I/O Bandwidth ProblemmnddddNessuna valutazione finora

- Key Cisco networking termsDocumento27 pagineKey Cisco networking termsnabinatorNessuna valutazione finora

- ES Assignment 3Documento12 pagineES Assignment 3satinder singhNessuna valutazione finora

- Idt CPS8-80KSW0003 PRB 20081015Documento2 pagineIdt CPS8-80KSW0003 PRB 20081015raghukumarkNessuna valutazione finora

- Routing Protocols CTDocumento70 pagineRouting Protocols CTgaurav_juneja_4Nessuna valutazione finora

- Effective Communication Protocols For Verification On Soc Using FpgaDocumento6 pagineEffective Communication Protocols For Verification On Soc Using FpgaSreekanth PagadapalliNessuna valutazione finora

- First Hop Redundancy Protocol: Network Redundancy ProtocolDa EverandFirst Hop Redundancy Protocol: Network Redundancy ProtocolNessuna valutazione finora

- Wye River Upper School: Application For AdmissionDocumento4 pagineWye River Upper School: Application For AdmissionSandhya DeviNessuna valutazione finora

- E-commerce, Payment Gateways, Security QuestionsDocumento6 pagineE-commerce, Payment Gateways, Security QuestionsSandhya DeviNessuna valutazione finora

- Exercise 1Documento3 pagineExercise 1davinciNessuna valutazione finora

- E-commerce, Payment Gateways, Security QuestionsDocumento6 pagineE-commerce, Payment Gateways, Security QuestionsSandhya DeviNessuna valutazione finora

- Cube RootDocumento1 paginaCube RootSandhya DeviNessuna valutazione finora

- AbstractDocumento1 paginaAbstractSandhya DeviNessuna valutazione finora

- Navigation of Blind People Using Passenger Bus Alert SystemDocumento1 paginaNavigation of Blind People Using Passenger Bus Alert SystemSandhya DeviNessuna valutazione finora

- Road Accident Information SystemDocumento1 paginaRoad Accident Information SystemSandhya DeviNessuna valutazione finora

- OrCAD PCB Design Tutorial: Complete Guide to Making Circuit BoardsDocumento1 paginaOrCAD PCB Design Tutorial: Complete Guide to Making Circuit BoardsSandhya DeviNessuna valutazione finora

- Textual Content: Uitextview - Keyboard Control - Alerts & Timers - Core Media: Audio, Still Photos and Video. - Core Motion: Accelerometer andDocumento1 paginaTextual Content: Uitextview - Keyboard Control - Alerts & Timers - Core Media: Audio, Still Photos and Video. - Core Motion: Accelerometer andSandhya DeviNessuna valutazione finora

- AzbsDocumento1 paginaAzbsSandhya DeviNessuna valutazione finora

- AbsnDocumento1 paginaAbsnSandhya DeviNessuna valutazione finora

- Fast and Enhanced Algorithm For Exemplar Based Image Inpainting (Java)Documento1 paginaFast and Enhanced Algorithm For Exemplar Based Image Inpainting (Java)Sandhya DeviNessuna valutazione finora

- BuckDocumento1 paginaBuckSandhya DeviNessuna valutazione finora

- Amplitude ModulationDocumento1 paginaAmplitude ModulationSandhya DeviNessuna valutazione finora

- Voltage SourceDocumento1 paginaVoltage SourceSandhya DeviNessuna valutazione finora

- ECA Summary JntuworldDocumento15 pagineECA Summary JntuworldDr-Priyadarsan ParidaNessuna valutazione finora

- OCR and RFID Enabled Vehicle Identification and Parking Allocation System C#Documento1 paginaOCR and RFID Enabled Vehicle Identification and Parking Allocation System C#Sandhya DeviNessuna valutazione finora

- Classification of Materials On The Basis of Electrical ConductivityDocumento1 paginaClassification of Materials On The Basis of Electrical ConductivitySandhya DeviNessuna valutazione finora

- Volt RegDocumento1 paginaVolt RegSandhya DeviNessuna valutazione finora

- Buck ConvDocumento1 paginaBuck ConvSandhya DeviNessuna valutazione finora

- IrledDocumento5 pagineIrledSandhya DeviNessuna valutazione finora

- Section 'B' Examinations (Electronics & Communication Engineering)Documento1 paginaSection 'B' Examinations (Electronics & Communication Engineering)Sandhya DeviNessuna valutazione finora

- Blind AssiDocumento1 paginaBlind AssiSandhya DeviNessuna valutazione finora

- Hardware and Software For ImageDocumento1 paginaHardware and Software For ImageSandhya DeviNessuna valutazione finora

- Image ProcDocumento1 paginaImage ProcSandhya DeviNessuna valutazione finora

- Image IntroDocumento2 pagineImage IntroSandhya DeviNessuna valutazione finora

- Basic Electronics 2Documento66 pagineBasic Electronics 2Sandhya DeviNessuna valutazione finora

- Syllabus For Written Examination of TGT (Work Experience)Documento4 pagineSyllabus For Written Examination of TGT (Work Experience)Sandhya DeviNessuna valutazione finora

- Exam Pattern of KVS TGT Exam 2013 (P&HE, WE, AE) and LibrarianDocumento1 paginaExam Pattern of KVS TGT Exam 2013 (P&HE, WE, AE) and LibrarianSandhya DeviNessuna valutazione finora

- Roland cm500Documento50 pagineRoland cm500Rafael RochaNessuna valutazione finora

- GL PMG 3500 Vertical Specification SheetDocumento1 paginaGL PMG 3500 Vertical Specification SheetAamir Sohail100% (1)

- 2.23 Ratio Control: F. G. Shinskey B. G. Lipták J. E. Jamison, A. RohrDocumento6 pagine2.23 Ratio Control: F. G. Shinskey B. G. Lipták J. E. Jamison, A. RohrjigjigawNessuna valutazione finora

- Infineon IHW30N120R5 DataSheet v02 - 03 ENDocumento15 pagineInfineon IHW30N120R5 DataSheet v02 - 03 ENAsad AhmedNessuna valutazione finora

- Decibel ⇄ Linear Conversions for Cable SystemsDocumento10 pagineDecibel ⇄ Linear Conversions for Cable SystemsHoussem TeberNessuna valutazione finora

- NX-series PROFINET® Coupler Unit NX-PNCDocumento15 pagineNX-series PROFINET® Coupler Unit NX-PNCNH KimNessuna valutazione finora

- Lesson in RoboticsDocumento10 pagineLesson in RoboticsScottie PollardNessuna valutazione finora

- RS-485 2X22/7 AWG SF/UTP PVC Low Temperature: Design & MaterialsDocumento2 pagineRS-485 2X22/7 AWG SF/UTP PVC Low Temperature: Design & MaterialsJuan Sebastian SanabriaNessuna valutazione finora

- EEC Equivalent CircuitsDocumento185 pagineEEC Equivalent CircuitsMert YılmazNessuna valutazione finora

- HFV 8040Documento3 pagineHFV 8040deyede2003Nessuna valutazione finora

- TM12864H6CCOWADocumento32 pagineTM12864H6CCOWASukumaran BalakrishnanNessuna valutazione finora

- Infineon TC39xXX - TC39xXP - PB PB v01 - 00 EN PDFDocumento2 pagineInfineon TC39xXX - TC39xXP - PB PB v01 - 00 EN PDFmikipejaNessuna valutazione finora

- CNC Lesson PlanDocumento8 pagineCNC Lesson Planmagesh.mxNessuna valutazione finora

- Factors That Affect the Strength of Electromagnets (37 charactersDocumento6 pagineFactors That Affect the Strength of Electromagnets (37 charactersDrake Athenaeus CaminongNessuna valutazione finora

- Introduction To Encoding and DecodingDocumento13 pagineIntroduction To Encoding and DecodingSusmitha Cherukuri0% (1)

- Test ShortDocumento52 pagineTest Shortsaikiran loyaNessuna valutazione finora

- AlteonOS 32-0-0 CLI Application GuideDocumento977 pagineAlteonOS 32-0-0 CLI Application GuideVitaly KroivetsNessuna valutazione finora

- LED Lamp Specs with 180 Lumens and 75 Hour RuntimeDocumento2 pagineLED Lamp Specs with 180 Lumens and 75 Hour RuntimeFerdi RukmantoNessuna valutazione finora

- Baumer Shortform Encoder 2021 EN 202110 CT 11248458 LowResDocumento98 pagineBaumer Shortform Encoder 2021 EN 202110 CT 11248458 LowResGianniNessuna valutazione finora

- PTTC Polytronics Tech SPR P260T - C209736Documento5 paginePTTC Polytronics Tech SPR P260T - C209736Kenneth MatthewNessuna valutazione finora

- Smart-Ups On-Line Srt3000xli ApcDocumento3 pagineSmart-Ups On-Line Srt3000xli ApcCarolina Espinoza VargasNessuna valutazione finora

- RF MEMS Switches and Switch Circuits: Shimul Chandra SahaDocumento174 pagineRF MEMS Switches and Switch Circuits: Shimul Chandra SahaRajNessuna valutazione finora

- Noise and Vibration Tester: MVH 90E, MVH 200E MVH 90el, MVH 200elDocumento8 pagineNoise and Vibration Tester: MVH 90E, MVH 200E MVH 90el, MVH 200ellaloNessuna valutazione finora

- Eaton 93PM 80-100kW UPS Technical SpecificationDocumento5 pagineEaton 93PM 80-100kW UPS Technical SpecificationFlorin MNessuna valutazione finora

- Chapter 16 - Filter CircuitsDocumento26 pagineChapter 16 - Filter CircuitsGeoFurrielNessuna valutazione finora

- MATLAB Transmission Line Fault AnalysisDocumento3 pagineMATLAB Transmission Line Fault AnalysisKALYAN KUMARNessuna valutazione finora