Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

555 Timer Integrated Circuit

Caricato da

Talha WaqarDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

555 Timer Integrated Circuit

Caricato da

Talha WaqarCopyright:

Formati disponibili

555 TIMER INTEGRATED CIRCUIT

[Type the document subtitle]

11/13/2012 talhawaqar1@hotmail.com TALHA WAQAR

555 TIMER INTEGRATED CIRCUIT

One of the most versatile linear ICs is the 555 timer which was first introduced in early 1970 by Signetic Corporation giving the name as SE/NE 555 timer. This IC is a monolithic timing circuit that can produce accurate and highly stable time delays or oscillation. Like other commonly used op-amps, this IC is also very much reliable, easy to use and cheaper in cost. It has a variety of applications including monostable andastable multivibrators, dc-dc converters, digital logic probes, waveform generators, analog frequency meters and tachometers, temperature measurement and control devices, voltage regulators etc. The timer basically operates in one of the two modes either as a monostable (one-shot) multivibrator or as an astable (free-running) multivibrator.The SE 555 is designed for the operating temperature range from 55C to 125 while the NE 555 operates over a temperature range of 0 to 70C.

The important features of the 555 timer are :

It operates from a wide range of power supplies ranging from + 5 Volts to + 18 Volts supply voltage. Sinking or sourcing 200 mA of load current. The external components should be selected properly so that the timing intervals can be made into several minutes Proper selection of only a few external components allows

555 TIMER INTEGRATED CIRCUIT

timing intervals of several minutes along with the frequencies exceeding several hundred kilo hertz. It has a high current output; the output can drive TTL. It has a temperature stability of 50 parts per million (ppm) per degree Celsius change in temperature, or equivalently 0.005 %/ C. The duty cycle of the timer is adjustable with the maximum power dissipation per package is 600 mW and its trigger and reset inputs are logic compatible.

Pin 1: Grounded Terminal: All the voltages are measured with respect to this terminal. Pin 2: Trigger Terminal: This pin is an inverting input to a comparator that is responsible for transition of flip-flop from set to reset. The output of the timer depends on the amplitude of the external trigger pulse applied to this pin. Pin 3: Output Terminal: Output of the timer is available at this pin. There are two ways in which a load can be connected to the output terminal either between pin 3 and ground pin (pin 1) or between pin 3 and supply pin (pin 8). The load connected between pin 3 and ground supply pin is called the normally on load and that connected between pin 3 and ground pin is called the normally off load. Pin 4: Reset Terminal: To disable or reset the timer a negative pulse is applied to this pin due to which it is referred to as reset terminal. When this pin is not to be used for reset purpose, it should be connected to + VCC to avoid any possibility of false triggering. Pin 5: Control Voltage Terminal: The function of this terminal is to control the threshold and trigger levels. Thus either the external voltage or a pot connected to this pin determines the pulse width of the output waveform. The external voltage applied to this pin can also be used to modulate the output waveform. When this pin is not used, it should be connected to ground through a 0.01 micro Farad to avoid any noise problem. Pin 6: Threshold Terminal: This is the non-inverting input terminal of comparator 1, which compares the voltage applied to the terminal with a reference voltage of 2/3 VCC. The amplitude of voltage applied to this terminal is responsible for the set state of flip-flop. Pin 7 : Discharge Terminal: This pin is connected internally to the collector of transistor and mostly a capacitor is connected between this terminal and ground. It is called discharge terminal because when transistor saturates, capacitor discharges through the transistor. When the transistor is cut-off, the capacitor charges at a rate determined by the external resistor and capacitor. Pin 8: Supply Terminal: A supply voltage of + 5 V to + 18 V is applied to this terminal with respect to ground (pin 1).

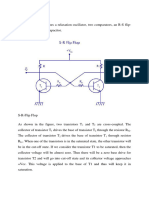

The 555 timer combines a relaxation oscillator, two comparators, an R-S flip-flop, and a discharge capacitor.

555 TIMER INTEGRATED CIRCUIT

R-S Flip-Flop: A pair of cross-coupled transistors is shown in figure. Each collector drives the opposite base through resistance RB. In such circuit one transistor is saturated while the other is cut-off. For instance, if transistor Q1 is saturated, its collector voltage is almost zero. So there is no base drive for transistor Q2 and it goes into cut-off and its collector voltage approaches + VCC. This high voltage produces enough base current to keep transistor Q1 in saturation. On the other hand if transistor Q1 is cut-off, its collector voltage, which is approximately equal to + VCC, drives the transistor Q2 into saturation. The low collector voltage (which is approximately to zero) of this transistor then keeps the transistor Q2 in cut-off.Depending on which transistor is saturated, the Q output is either low or high. By adding more components to the circuit, an R-S flip-flop is obtained. R-S flip-flop is a circuit that can set the Q output to high or reset it low. Incidentally, a complementary (opposite) output Q is available from the collector of the other transistor. Figure shows the schematic symbol for an R-S flip-flop of any design. The circuit latches in either two states. A high S input sets Q to high; a high R input resets Q to low. Output Q remains in a given state until it is triggered into the opposite state.

555 TIMER INTEGRATED CIRCUIT

Basic Timing Concept

Figure illustrates some basic ideas that will prove useful in coming blog posts of the 555 timer. Assuming output Q high, the transistor is saturated and the capacitor voltage is clamped at ground i.e. the capacitor C is shorted and cannot charge. The non-inverting input voltage of the comparator is referred to as the threshold voltage while the inverting input voltage is referred to as the control voltage. With R-S flip flop set, the saturated transistor holds the threshold voltage at zero. The control voltage, however, is fixed at 2/3 VCC (i.e. at 10 V) because of the voltage divider. Suppose that a high voltage is applied to the R input. This resets the flip-flop R-Output Q goes low and the transistor is cut-off. Capacitor C is now free to charge. As this capacitor C charges, the threshold voltage rises. Eventually, the threshold voltage becomes slightly greater than (+ 10 V). The output of the comparator then goes high, forcing the R S flip-flop to set. The high Q output saturates the transistor, and this quickly discharges the capacitor. The two waveforms are depicted in figure. An exponential rise is across the capacitor C, and a positive going pulse appears at the output Q. Thus capacitor voltage VC is exponential while the output is rectangular, as illustrated in figure.

555 TIMER INTEGRATED CIRCUIT

4. Block Diagram

Block Diagram -555 Timer

The block diagram of a 555 timer is shown in the above figure. A 555 timer has two comparators, which are basically 2 op-amps), an R-S flip-flop, two transistors and a resistive network. Resistive network consists of three equal resistors and acts as a voltage divider. Comparator 1 compares threshold voltage with a reference voltage + 2/3 VCC volts. Comparator 2 compares the trigger voltage with a reference voltage + 1/3 VCC volts. Output of both the comparators is supplied to the flip-flop. Flip-flop assumes its state according to the output of the two comparators. One of the two transistors is a discharge transistor of which collector is connected topin 7. This transistor saturates or cuts-off according to the output state of the flip-flop. The saturated transistor provides a discharge path to a capacitor connected externally. Base of another transistor is connected to a reset terminal. A pulse applied to this terminal resets the whole timer irrespective of any input.

555 TIMER INTEGRATED CIRCUIT

5. Working Principle

Refer Block Diagram of 555 timer IC given above:

Comparator 1 has a threshold input (pin 6) and a control input (pin 5). In most applications, the control input is not used, so that the control voltage equals +2/3 VCC. Output of this comparator is applied to set (S) input of the flip-flop. Whenever the threshold voltage exceeds the control voltage, comparator 1 will set the flip-flop and its output is high. A high output from the flip-flop saturates the discharge transistor and discharge the capacitor connected externally to pin 7. The complementary signal out of the flip-flop goes to pin 3, the output. The output available at pin 3 is low. These conditions will prevail until comparator 2 triggers the flip-flop. Even if the voltage at the threshold input falls below 2/3 VCC, that is comparator 1 cannot cause the flip-flop to change again. It means that the comparator 1 can only force the flip-flops output high. To change the output of flip-flop to low, the voltage at the trigger input must fall below + 1/3 Vcc. When this occurs, comparator 2 triggers the flip-flop, forcing its output low. The low output from the flip-flop turns the discharge transistor off and forces the power amplifier to output a high. These conditions will continue independent of the voltage on the trigger input. Comparator 2 can only cause the flip-flop to output low. From the above discussion it is concluded that for the having low output from the timer 555, the voltage on the threshold input must exceed the control voltage or + 2/3 VCC. They also turn the discharge transistor on. To force the output from the timer high, the voltage on the trigger input must drop below +1/3 VCC. This also turns the discharge transistor off. A voltage may be applied to the control input to change the levels at which the switching occurs. When not in use, a 0.01 nano Farad capacitor should be connected between pin 5 and ground to prevent noise coupled onto this pin from causing false triggering. Connecting the reset (pin 4) to a logic low will place a high on the output of flip-flop. The discharge transistor will go on and the power amplifier will output a low. This condition will continue until reset is taken high. This allows synchronization or resetting of the circuits operation. When not in use, reset should be tied to +VCC.

555 TIMER INTEGRATED CIRCUIT

R1 1000 R2 70k XMM1

U1

V1 6V

555_Timer

R3 330

J5 J4 J3 Key = AC1 Key = AC3 Key = AC2 0.1F 25F 100F

Working circuit analysed on multisim.

Potrebbero piacerti anche

- The Important Features of The 555 Timer AreDocumento7 pagineThe Important Features of The 555 Timer ArePathella SudhakarNessuna valutazione finora

- SE/NE 555 Timer. It Is Basically A Monolithic Timing Circuit That Produces Accurate and Highly Stable Time Delays orDocumento12 pagineSE/NE 555 Timer. It Is Basically A Monolithic Timing Circuit That Produces Accurate and Highly Stable Time Delays orEFraim Manzano FranciscoNessuna valutazione finora

- 555 Timer IC: The Important Features of The 555 Timer AreDocumento5 pagine555 Timer IC: The Important Features of The 555 Timer AreChara GalaNessuna valutazione finora

- Operation 555 Timer/OscillatorDocumento7 pagineOperation 555 Timer/OscillatoryuvakiraniNessuna valutazione finora

- IC 555 TimerDocumento6 pagineIC 555 Timeraditya pandeyNessuna valutazione finora

- 6.1 IC555 TIMER: Circuit ComponentsDocumento8 pagine6.1 IC555 TIMER: Circuit ComponentsManish PradhanNessuna valutazione finora

- 555 Timer IC-Block Diagram-Working-Pin Out Configuration-Data SheetDocumento13 pagine555 Timer IC-Block Diagram-Working-Pin Out Configuration-Data SheetΔημητριος ΣταθηςNessuna valutazione finora

- List The Features of 555 TimersDocumento3 pagineList The Features of 555 TimersDivyesh DivakarNessuna valutazione finora

- IC555 TimerDocumento8 pagineIC555 TimerRaflysyah PutraNessuna valutazione finora

- Timer 555 - ManualDocumento20 pagineTimer 555 - ManualXen XeonNessuna valutazione finora

- Theory:The 555 Timer Configured For Monostable OperationDocumento3 pagineTheory:The 555 Timer Configured For Monostable OperationkumararguruNessuna valutazione finora

- IC 555 Multivibrator CircuitsDocumento11 pagineIC 555 Multivibrator CircuitsKaran YadavNessuna valutazione finora

- Opamp Applicationpart30Documento31 pagineOpamp Applicationpart30KUNTALA DASNessuna valutazione finora

- 555 TimerDocumento3 pagine555 TimerchandrakanthNessuna valutazione finora

- 3.1555 TIMER:: Schematic SymbolDocumento10 pagine3.1555 TIMER:: Schematic SymbolnagpradasNessuna valutazione finora

- 555 Timer: by D.V.Kamat, Faculty Department of E&C Engg., MITDocumento21 pagine555 Timer: by D.V.Kamat, Faculty Department of E&C Engg., MITRupsa SahaNessuna valutazione finora

- LIC Mod 2Documento15 pagineLIC Mod 2Sona PrakashNessuna valutazione finora

- Multivibrator CircuitsDocumento11 pagineMultivibrator CircuitsSatyaki ChowdhuryNessuna valutazione finora

- Lab#10: Design and Study of IC 555 Multivibrator Circuits (2 Turns)Documento11 pagineLab#10: Design and Study of IC 555 Multivibrator Circuits (2 Turns)Ayushman ChoudharyNessuna valutazione finora

- Multivibrador Com Ci 555Documento11 pagineMultivibrador Com Ci 555joselito1juniorNessuna valutazione finora

- Integrated Circuits:) of Flip-Flop ThroughDocumento13 pagineIntegrated Circuits:) of Flip-Flop ThroughShubh MishraNessuna valutazione finora

- Ic Applications Lab NewDocumento12 pagineIc Applications Lab NewSandy RonaldoNessuna valutazione finora

- UNIT-4 Special Ics The 555 Timer IcDocumento10 pagineUNIT-4 Special Ics The 555 Timer IcVerloves LoveNessuna valutazione finora

- The 555 Timer IC (Adapted From) : CaseDocumento12 pagineThe 555 Timer IC (Adapted From) : CaseBiswajit Sarkar100% (1)

- ME 455/555 - Lab 2 - 555 TimersDocumento10 pagineME 455/555 - Lab 2 - 555 TimersGustavo KernNessuna valutazione finora

- Report IC 555 TimerDocumento17 pagineReport IC 555 TimerSantosh YadavNessuna valutazione finora

- Ic 555Documento25 pagineIc 555Ahmed SaȜed El-HadyNessuna valutazione finora

- 555Documento80 pagine555elpasanteNessuna valutazione finora

- Bistable MultivibratorDocumento28 pagineBistable MultivibratorMansi JaisinghNessuna valutazione finora

- Operational AmplifierDocumento10 pagineOperational AmplifierSalman AliNessuna valutazione finora

- Lic Eec-501 Notes Unit5 Iftm UniversityDocumento14 pagineLic Eec-501 Notes Unit5 Iftm UniversitySougata GhoshNessuna valutazione finora

- 4 555timer 120916082406 Phpapp02Documento14 pagine4 555timer 120916082406 Phpapp02sunil1237Nessuna valutazione finora

- Burglar Alarm ProjectDocumento4 pagineBurglar Alarm ProjectAvik PathakNessuna valutazione finora

- 1 Ic 555Documento6 pagine1 Ic 555Harish PatilNessuna valutazione finora

- ElectronicIII - L3Documento14 pagineElectronicIII - L3Aya MazinNessuna valutazione finora

- 555-Timer Class NotesDocumento1 pagina555-Timer Class NotesPraveen KumarNessuna valutazione finora

- Block Diagram of 555 Timer ICDocumento1 paginaBlock Diagram of 555 Timer ICSreedaharNessuna valutazione finora

- Block Diagram of 555 Timer ICDocumento1 paginaBlock Diagram of 555 Timer ICSreedaharNessuna valutazione finora

- Integratedelectronics (Unit2) 555 TIMER ASTABLE MONOSTABLE MVDocumento5 pagineIntegratedelectronics (Unit2) 555 TIMER ASTABLE MONOSTABLE MVYogeshwaranNessuna valutazione finora

- N555e Intergrated CircuitDocumento6 pagineN555e Intergrated CircuitGeorge Boman SethNessuna valutazione finora

- A Mono Stable Multi Vibrato 1Documento4 pagineA Mono Stable Multi Vibrato 1Noemi CaluzaNessuna valutazione finora

- 555 Timer As Monostable MultivibratorDocumento5 pagine555 Timer As Monostable MultivibratorDarshan BhansaliNessuna valutazione finora

- Tutorial Timmer 555Documento9 pagineTutorial Timmer 555gabrielamedeletNessuna valutazione finora

- E.C.E - 210Documento18 pagineE.C.E - 210xxkkassNessuna valutazione finora

- Introduction To IC 555 TimerDocumento66 pagineIntroduction To IC 555 TimermuraliNessuna valutazione finora

- 555 TimerDocumento12 pagine555 Timerlalaine reginaldoNessuna valutazione finora

- Ci 555Documento25 pagineCi 555Cristian VacaNessuna valutazione finora

- Dsa 265104Documento20 pagineDsa 265104foxx034Nessuna valutazione finora

- 555 Integrated Circuit (Timer Operation)Documento5 pagine555 Integrated Circuit (Timer Operation)Geet SehgalNessuna valutazione finora

- The 555 Timer: Monostable Bistable AstableDocumento10 pagineThe 555 Timer: Monostable Bistable AstableSrikanth ThulluriNessuna valutazione finora

- IC 555 TimerDocumento32 pagineIC 555 TimerAmaradi KondababuNessuna valutazione finora

- 555 Applications NoteDocumento19 pagine555 Applications NoteIsaac Herrera100% (1)

- 555 TimerDocumento28 pagine555 TimerNisha Kotyan G RNessuna valutazione finora

- Presentation On Ic 555 Timer: BY: Sandeep KumarDocumento24 paginePresentation On Ic 555 Timer: BY: Sandeep KumarSandeep Kamti BrzeeNessuna valutazione finora

- AUTO CONTROLLER FOR PETROL (Revised)Documento25 pagineAUTO CONTROLLER FOR PETROL (Revised)Hamed RazaNessuna valutazione finora

- Ic555 TimerDocumento5 pagineIc555 Timerps1976Nessuna valutazione finora

- 555 Timer - Oscillator TutorialDocumento14 pagine555 Timer - Oscillator TutorialfgaluppoNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Valutazione: 2.5 su 5 stelle2.5/5 (3)

- (Kashif Hasnain) - Lab Report # 1 - SMAW WeldingDocumento4 pagine(Kashif Hasnain) - Lab Report # 1 - SMAW WeldingAbrar HassanNessuna valutazione finora

- CBSE Class 12 Physics Electromagnetic Induction and Alternating CurrentDocumento4 pagineCBSE Class 12 Physics Electromagnetic Induction and Alternating CurrentPriyanshu BarnawalNessuna valutazione finora

- EEE 141 Final AssignmentsDocumento4 pagineEEE 141 Final AssignmentsTanjila RituNessuna valutazione finora

- 0460 443 301 GB (Caddy TIG 2200i - Manual 2019)Documento28 pagine0460 443 301 GB (Caddy TIG 2200i - Manual 2019)maverick kitaroNessuna valutazione finora

- SMITHS INTERCONNECT - Katalog - LHS - LHZ - LHT - Serie - A4Documento36 pagineSMITHS INTERCONNECT - Katalog - LHS - LHZ - LHT - Serie - A4Saadi SamirNessuna valutazione finora

- Data Sheet 3VA1225-4EE32-0AA0: ModelDocumento4 pagineData Sheet 3VA1225-4EE32-0AA0: ModelJagadeesan ShanmugamNessuna valutazione finora

- QuizbowlquestionsfinalDocumento7 pagineQuizbowlquestionsfinalKyLe Philip NgNessuna valutazione finora

- Half-Bridge Mosfet Driver IC IRS2153 (1) D Datasheet: Homemade Circuit ProjectsDocumento17 pagineHalf-Bridge Mosfet Driver IC IRS2153 (1) D Datasheet: Homemade Circuit ProjectsHerbert LopesNessuna valutazione finora

- Service ManualDocumento1 paginaService ManualJuan Carlos Desposorio Marmolejo86% (22)

- Ald1107/ald1117: A L D IDocumento6 pagineAld1107/ald1117: A L D ISantiago Cadena AlvarezNessuna valutazione finora

- B737-200 L3 ATA 23 Communications (Full)Documento130 pagineB737-200 L3 ATA 23 Communications (Full)Belisario Sergio Llacchas rodasNessuna valutazione finora

- DatasheetDocumento1 paginaDatasheetCalixto Milla EsauNessuna valutazione finora

- Solar AC On-Grid Solutions From Glonev 2023.12pdfDocumento3 pagineSolar AC On-Grid Solutions From Glonev 2023.12pdfalbertsui.iii14Nessuna valutazione finora

- Polytechnic of Namibia: M Ark Moderated M Ark Exam Ine RsDocumento3 paginePolytechnic of Namibia: M Ark Moderated M Ark Exam Ine Rsmoses kakwenaNessuna valutazione finora

- Catalogue Rotex KTR StandardDocumento3 pagineCatalogue Rotex KTR StandardNguyễn Hữu ĐồngNessuna valutazione finora

- KENDEIL Elkos 2015 PDFDocumento164 pagineKENDEIL Elkos 2015 PDFtegar sulistiantoNessuna valutazione finora

- RectifierDocumento26 pagineRectifierhemnphysic91Nessuna valutazione finora

- Experiment # 4 Amplitude Modulation (AM) (Part 2) : ObjectiveDocumento8 pagineExperiment # 4 Amplitude Modulation (AM) (Part 2) : ObjectiveGhaznooq AhmadNessuna valutazione finora

- Ind Module 7 - 4Q1920 PDFDocumento4 pagineInd Module 7 - 4Q1920 PDF抓愛恰Nessuna valutazione finora

- Sopan Pems Nayara (P) : CommentsDocumento7 pagineSopan Pems Nayara (P) : CommentssidharthNessuna valutazione finora

- Control de TraficoDocumento9 pagineControl de TraficoBrenyi Zanabria ConchaNessuna valutazione finora

- ZTX550 PDFDocumento2 pagineZTX550 PDFheruye mulugetaNessuna valutazione finora

- MCQ On Electricity and MagnetismDocumento3 pagineMCQ On Electricity and Magnetismsinosh79% (14)

- Piezoelectric Transducers Used For Piezoelectric Accelerometers With Integral ElectronicsDocumento16 paginePiezoelectric Transducers Used For Piezoelectric Accelerometers With Integral ElectronicsOzawa MagooNessuna valutazione finora

- AN2002 Application Note: Using The Demoboard For The TD350 Advanced IGBT DriverDocumento8 pagineAN2002 Application Note: Using The Demoboard For The TD350 Advanced IGBT Driverbokic88Nessuna valutazione finora

- FM-206 High Performance 3-Port Rework Station: 3 Stations-In-One!Documento4 pagineFM-206 High Performance 3-Port Rework Station: 3 Stations-In-One!jupalspy9870Nessuna valutazione finora

- 2-Series, 3-Series, and 4-Series Cell Lithium-Ion or Lithium-Polymer Battery Protection AfeDocumento32 pagine2-Series, 3-Series, and 4-Series Cell Lithium-Ion or Lithium-Polymer Battery Protection AfeGiridharan SanthakumarNessuna valutazione finora

- Physics Investigatory Class 12 Full Exclusive Project CbseDocumento21 paginePhysics Investigatory Class 12 Full Exclusive Project CbseAyu Harshal44% (16)

- RPL201H Traction Controller Error Code ListDocumento19 pagineRPL201H Traction Controller Error Code Listvictor laraNessuna valutazione finora

- Project 2024Documento23 pagineProject 2024عبدالله نافعNessuna valutazione finora