Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

EE 5301 - VLSI Design Automation I

Caricato da

Manoj GopalTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

EE 5301 - VLSI Design Automation I

Caricato da

Manoj GopalCopyright:

Formati disponibili

http:]]www.ece.umn.

edu]users]kIa]Courses]EE5301]

VLS DesIgn AutomatIon - KIa

8azargan

Fall 2003 EE 5301 - VLSI Design Automation I

149

EE 5301 VLSI Design Automation I EE 5301 VLSI Design Automation I

Kia Bazargan

University of Minnesota

Part V: Placement Part V: Placement

Fall 2003 EE 5301 - VLSI Design Automation I

150

References and Copyright

- Textbooks referred (none required)

[Nic9+| G. De Nicheli

Synthesis and Optimization of Digital Circuits"

NcGraw-Hill, 199+.

[CLR90| T. H. Cormen, C. E. Leiserson, R. L. Rivest

!ntroduction to Algorithms"

N!T Press, 1990.

[Sar96| N. Sarrafzadeh, C. K. Wong

An !ntroduction to vLS! Physical Design"

NcGraw-Hill, 1996.

[She99| N. Sherwani

Algorithms For vLS! Physical Design Automation"

Kluwer Academic Publishers, 3

rd

edition, 1999.

Fall 2003 EE 5301 - VLSI Design Automation I

151

References and Copyright (cont.)

- Slides used: (Nodified by Kia when necessary)

[Sarrafzadeh| Najid Sarrafzadeh, 2001;

Department of Computer Science, UCLA

[Sherwani| Naveed A. Sherwani, 1992

(companion slides to [She99|)

[Keutzer| Kurt Keutzer, Dept. of EECS,

UC-Berekeley

http:ffwww-cad.eecs.berkeley.eduf~nirajfee2++findex.htm

[Gupta| Rajesh Gupta

UC-!rvine

http:ffwww.ics.uci.eduf~rguptafics280.html

[Kang| Steve Kang

U!UC

http:ffwww.ece.uiuc.edufece+82f

http:]]www.ece.umn.edu]users]kIa]Courses]EE5301]

VLS DesIgn AutomatIon - KIa

8azargan

Fall 2003 EE 5301 - VLSI Design Automation I

152

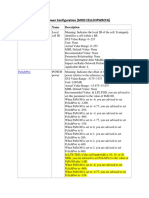

Placement

- Problem

Given a netlist, and fixed-shape cells (small, standard

cell), find the exact location of the cells to minimize

area and wire-length

Consistent with the standard-cell design methodology

o Row-based, no hard-macros

Nodules:

o Usually fixed, equal height (exception: double height cells)

o Some fixed (!fO pads)

o Connected by edges or hyperedges

- Objectives

Cost components: area, wire length

o Additional cost components: timing, congestion

Fall 2003 EE 5301 - VLSI Design Automation I

153

Placement Cost Components

- Area

Would like to pack all the modules very tightly

- Wire length (half-perimeter of the hnet bbox)

Ninimize the average wire length

Would result in tight packing of the modules with high

connectivity

- Overlap

Could be prohibited by the moves, or used as penalty

Keep the cells from overlapping (moves cells apart)

- Timing

Not a 1-1 correspondent with wire length minimization,

but consistent on the average

- Congestion

Neasure of routability

Would like to move the cells apart

Fall 2003 EE 5301 - VLSI Design Automation I

154

Placement Algorithms

- Top-Down

Partitioning-based placement

Recursive bi-partitioning or

quadrisection

o Cut direction?

o Partition vs. physical location

- !terative

Simulated annealing

OR: Force directed

Start with an initial placement,

iteratively improve the wire-length

and area

- Constructive

Start with a few cells in the center,

and place highly connected

adjacent modules around them

1

2

8

A

D 8

F

A

C

C

L

H

http:]]www.ece.umn.edu]users]kIa]Courses]EE5301]

VLS DesIgn AutomatIon - KIa

8azargan

Fall 2003 EE 5301 - VLSI Design Automation I

155

Simulated Annealing Placement

- Cost

Area (usually fixed # of rows, variable row width)

Wirelength (Euclidian or Nanhattan)

Cell overlap (penalty increases with temperature)

- Noves

Exchange two cells within a radius R

(R temperature dependent?)

Displace a cell within a row

Flip a cell horizontally

- Low vs. High temperature

!f used as a post processing, start with low-temp

- Post-processing?

Night be needed if there are still overlaps

Fall 2003 EE 5301 - VLSI Design Automation I

156

Force-Directed Placement

- Nodel

Wires simulated as springs

(if the only force, what will happen?)

Force

ij

= Weight

ij

x distance

ij

.

Cell sizes as repellant forces

[Eisenmann, DAC'98|:

vacant" regions work as attracting" forces

overcrowded" regions work as repelling" forces

- Algorithm

Solve a set of linear equations to find an intermediate

solution (module locations)

Repeat the process until equilibrium

Fall 2003 EE 5301 - VLSI Design Automation I

157

Force-Directed Placement (cont.)

- Nodel (details):

Cell distances: either

OR:

Forces:

Objective: find x,y coordinates for all cells such that

total force exerted on each cell is zero.

| | | |

j i ij j i ij

y y y x x x = =

2 2

) ( ) (

j i j i ij

y y x x d + =

) ( ) (

1 1

ij

n

j

ij

i

y ij

n

j

ij

i

x

y k F x k F = =

= =

http:]]www.ece.umn.edu]users]kIa]Courses]EE5301]

VLS DesIgn AutomatIon - KIa

8azargan

Fall 2003 EE 5301 - VLSI Design Automation I

158

Force-Directed Placement (cont.)

- Avoiding overlaps or collapsing in one point?

Use fixed boundary !fO cells

Use repelling force between cells that are not

connected by a net

Do not allow a move that results in overlap

Use repelling field" forces from congested areas to

sparse ones [Eisenmann, DAC'98|

- Problems with force directed:

Overlap still might occur (cell sizes model artificially)

Flat design, not hierarchy

) , ( ) (

1

i i x ij

n

j

ij

i

x

y x E x k F +

=

=

Fall 2003 EE 5301 - VLSI Design Automation I

159

Partitioning-based Placement

- Simultaneously perform:

Circuit partitioning

Chip area partitioning

Assign circuit partitions to chip slots

- Problem:

Circuit partitioning unaware of the physical location

Solution: Terminal propagation (add dummy terminals)

A

8

A

8

A

8

[She99] p.239

A 8

Fall 2003 EE 5301 - VLSI Design Automation I

160

Partitioning-based Placement

- Nore problems:

Direction of the cut? [Yildiz, DAC'01|

How to handle fixed blocks? (area assigned to a

partition might not be enough)

How to correct a bad decision made at a higher level?

- Advantages:

Hierarchical, scalable

!nherently apt for congestion minimization, easily

extendable to timing optimization

1

2 3

4 5

6 7

1

2 3

4 5

1

2

3

4

5

6

7

8

9

(a) (b) (c)

1 2

3

(d)

http:]]www.ece.umn.edu]users]kIa]Courses]EE5301]

VLS DesIgn AutomatIon - KIa

8azargan

Fall 2003 EE 5301 - VLSI Design Automation I

161

To Probe Further...

- Hans Eisenmann and Frank N. Johannes

Generic Global Placement and Floorplanning",

Design Automation Conference (DAC), pp. 269-27+, 1998.

(force directed method)

- Naogang Wang, Xiaojian Yang and Najid Sarrafzadeh

Dragon2000: Standard-Cell Placement Tool for Large !ndustry

Circuits",

!nternational Conference on Computer-Aided Design (!CCAD),

pp. 260-263, 2000.

(partitioning-based placement)

- Dennis J.-H. Huang and Andrew B. Kahng

Partitioning-based Standard-cell Global Placement With An Exact

Objective",

!nternational Symposium on Physical Design (!SPD), pp. 18-25, 1997.

(quadrisection-based placement)

Fall 2003 EE 5301 - VLSI Design Automation I

162

To Probe Further...

- Xiaojian Yang, Elaheh Bozorgzadeh and Najid Sarrafzadeh,

Wirelength Estimation based on Rent Exponents of Partitioning and

Placement",

System Level !nterconnect Prediction (SL!P), pp. 25-31, 2001.

- Nehmet Can Yildiz and Patrick H. Nadden

!mproved Cut Sequences for Partitioning Based Placement",

Design Automation Conference (DAC), pp. 776-779, 2001.

(cut directions in partitioning-based placement)

- Chandra Nulpuri and Scott Hauck

Runtime and Quality Tradeoffs in FPGA Placement and Routing",

!nternational Symposium on Field Programmable Gate Arrays (FPGA),

pp. 29-36, 2001.

(placement and routing qualityfspeed trade-off)

Potrebbero piacerti anche

- Individual-Factsheet Sep 2012Documento34 pagineIndividual-Factsheet Sep 2012Manoj GopalNessuna valutazione finora

- Manu FILEDocumento2 pagineManu FILEManoj GopalNessuna valutazione finora

- QuestuinDocumento3 pagineQuestuinManoj GopalNessuna valutazione finora

- Cad Vlsi SyllabusDocumento1 paginaCad Vlsi SyllabusManoj GopalNessuna valutazione finora

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Transistor As A SwitchDocumento3 pagineTransistor As A SwitchbofshafiqueNessuna valutazione finora

- Digital and Analog Signals-Exp1Documento2 pagineDigital and Analog Signals-Exp1MEHEDI HASANNessuna valutazione finora

- Chapter 1 - Ladder Diagram FundamentalsDocumento5 pagineChapter 1 - Ladder Diagram FundamentalsRitesh SharmaNessuna valutazione finora

- BEI-TT10K Product Datasheet - CDocumento2 pagineBEI-TT10K Product Datasheet - CSergio Ivan Merchan MejiaNessuna valutazione finora

- 4.3 The Non-Inverting AmplifierDocumento5 pagine4.3 The Non-Inverting Amplifierlizhi0007Nessuna valutazione finora

- Binary Numbers and Logic GatesDocumento25 pagineBinary Numbers and Logic GatesJohn Paulo De LeonNessuna valutazione finora

- Electrical Part List FELCOM 15 PDFDocumento1 paginaElectrical Part List FELCOM 15 PDFMiguel MartinezNessuna valutazione finora

- PIC16F872 - Data Sheet 28-Pin, 8-Bit CMOS Flash Microcontroller With 10-Bit A/D - 30221cDocumento168 paginePIC16F872 - Data Sheet 28-Pin, 8-Bit CMOS Flash Microcontroller With 10-Bit A/D - 30221cGuillermo HernandezNessuna valutazione finora

- Differential Amplifier - The Voltage SubtractorDocumento4 pagineDifferential Amplifier - The Voltage Subtractorsudheer52Nessuna valutazione finora

- Modify Cell Channel Power ConfigurationDocumento15 pagineModify Cell Channel Power ConfigurationRaul Rambo100% (1)

- Ksz8873Mll/Fll/Rll: Integrated 3-Port 10/100 Managed Switch With PhysDocumento95 pagineKsz8873Mll/Fll/Rll: Integrated 3-Port 10/100 Managed Switch With PhyskushliakNessuna valutazione finora

- Proximity Sensor TutorialDocumento13 pagineProximity Sensor TutorialShubham AgrawalNessuna valutazione finora

- The Impact of Current Transformer Saturation On The Distance ProtectionDocumento6 pagineThe Impact of Current Transformer Saturation On The Distance ProtectionIRELECNessuna valutazione finora

- Poynting PATCH-26Documento6 paginePoynting PATCH-26Carlos CostaNessuna valutazione finora

- B70010Documento18 pagineB70010Salvador FayssalNessuna valutazione finora

- PLC Editor ManualEN V13Documento46 paginePLC Editor ManualEN V13S KumarNessuna valutazione finora

- Basic Electrical and Electronics and Instrumentation Engineering - Lecture Notes, Study Material and Important Questions, AnswersDocumento15 pagineBasic Electrical and Electronics and Instrumentation Engineering - Lecture Notes, Study Material and Important Questions, AnswersM.V. TV100% (1)

- Analog Electronics Practice QuestionsDocumento19 pagineAnalog Electronics Practice Questionssharma_rockstarNessuna valutazione finora

- EE210 Assignment5 SolutionDocumento4 pagineEE210 Assignment5 Solutionsarah alshNessuna valutazione finora

- De Lab Manual-EEE New1Documento77 pagineDe Lab Manual-EEE New1selva_raj215414Nessuna valutazione finora

- Avm-P 8000 CRT2519Documento102 pagineAvm-P 8000 CRT2519Caio Jean MoraesNessuna valutazione finora

- Sebury K3-3Documento1 paginaSebury K3-3Alexandru BurbuleaNessuna valutazione finora

- Dwnload Full Digital Systems Design Using Verilog 1st Edition Roth Solutions Manual PDFDocumento35 pagineDwnload Full Digital Systems Design Using Verilog 1st Edition Roth Solutions Manual PDFhaodienb6qj100% (13)

- Introduction To CSS Pre-TestDocumento1 paginaIntroduction To CSS Pre-TestRusty Ugay Lumbres100% (1)

- Epson R800 SMDocumento174 pagineEpson R800 SMInteletracNessuna valutazione finora

- FMG3015-R20A: Gigabit Active Fiber Bridge With CATVDocumento4 pagineFMG3015-R20A: Gigabit Active Fiber Bridge With CATVppancxooNessuna valutazione finora

- AWD-25-1300-Datasheet UVHF Antenna ExpertDocumento1 paginaAWD-25-1300-Datasheet UVHF Antenna Expertson nguyenNessuna valutazione finora

- On Hacking MicroSD Cards Bunnie's BlogDocumento13 pagineOn Hacking MicroSD Cards Bunnie's BlogDiego HernandezNessuna valutazione finora

- Automatic Control of Street LightDocumento63 pagineAutomatic Control of Street LightMani RaoNessuna valutazione finora

- HPTB 32 TR Ao 01Documento2 pagineHPTB 32 TR Ao 01Ahmed WaheedNessuna valutazione finora