Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Problem: Switch Bounce: Initial Connection Finally Contact Closed

Caricato da

jlistiyadiDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Problem: Switch Bounce: Initial Connection Finally Contact Closed

Caricato da

jlistiyadiCopyright:

Formati disponibili

1

(SLP56 1

A Switch is Pressed. So \hat

5V

V

s

t

V

5

0

Problem: Switch Bounce

Initial

Connection

Finally

Contact Closed

Typically 10-20ms

(SLP56 2

Debouncing

When a switch (any type) changes

state (on -> off or off -> on), it presents

a mechanical bouncing which

generates a signal similar to the one

shown at the right.

The resistor R is needed because the

signal S can not be left floating in na

undefined state when the switch

changes from state 1 to 2.

Without debouncing the signal can

generate several interrupts (or status

changes) corresponding to just one

action.

Debouncing consists in Filtering the

signal S so that a proper operation of

the switch action is sensed.

Debouncing can be done in hardware

of software

Microcontroller

1

2

C

5V

R

5V

S

Read Key (should

be stable)

Techniques that can be used:

-If status loop: after first status change,

program timer and after elapsed time

read key status.

-If Interrupt: on first interrupt program

timer which will interrupt after elapsed

time. Then read key status.

t t

(SLP56 3

Light Dependent Resistors LDRs,

Devices whose resistance changes (usually

decreases) with light striking it

(also called photocells, photoconductors)

Light striking a semiconducting material can provide

sufficient energy to cause electrons to break away

from atoms.

Free electrons and holes can be created which

causes resistance to be reduced

(SLP56 4

Light Dependent Resistors LDRs,

Typical materials used are Cadmium Sulphide

(CdS), Cadmium Selenide (CdSe), Lead Sulphide

With no illumination, resistance can be greater than

1 M (dark resistance).

Resistance varies inversely proportional to light

intensity.

Reduces down to 10-100s ohms

100ms/10ms response time

2

(SLP56 5

Light Dependent Resistors LDRs,

1 N

100k

10k

1k

100

1 10 100 1000 lm/m

2

!llumination

R

e

s

i

s

t

a

n

c

e

CdS LDR

Top view

(SLP56 6

Light Dependent Resistors LDRs,

LDRs have a low energy gap

Operate over a wide wavelengths (some, into

infrared)

Indium antimonide is good for IR. When

cooled is very sensitive, used for thermal

scanning of earths surface

(SLP56

Analog to digital conersion

Use charge-redistribution technique

no sample and hold circuitry needed

even with perfect circuits quantization error occurs

Basic capacitors

sum parallel capacitance

C C 2C C 2C +C

C 3C /C

(SLP56 8

Analog to digital conersion cont`d,

Two reference voltage

mark bottom and top end of range of analog values that

can be converted ( V

L

and V

H

)

voltage to convert must be within these bounds ( V

X

)

Successive approximation

most approaches to A/D conversion are based on this

8 to 16 bits of accuracy

Approach

sample value

hold it so it doesnt change

successively approximate

report closest match

V

X

V

L

V

H

3

(SLP56 9

A-to-D - sample

During the sample time the top plate of all capacitors

is switched to reference low V

L

Bottom plate is set to unknown analog input V

X

Q = CV

Q

S

= 16 (V

X

- V

L

)

V

X

V

L

V

H

-

+

v

!

v

L

v

X

8 + 2 1 1

v

L

(SLP56 10

A-to-D - hold

Hold state using logically controlled analog switches

Top plates disconnected from V

L

Bottom plates switched from V

X

to V

L

Q

H

= 16 (V

L

- V

I

)

conservation of charge Q

S

= Q

H

16 (V

X

- V

L

) = 16 (V

L

- V

I

)

V

X

- V

L

= V

L

- V

I

(output of op-amp)

V

X

V

L

V

H

-

+

v

!

v

L

8 + 2 1 1

v

L

(SLP56 11

A-to-D - successie approximation

Each capacitor successively switched from V

L

to V

H

Largest capacitor corresponds to MSB

Output of comparator determines bottom plate

voltage of cap

> 0 : remain connected to V

H

< 0 : return to V

L

-

+

v

!

v

L

8 + 2 1 1

v

L

v

H

MS8 LS8

1 1 1 1 0 0 0 0

(SLP56 12

A-to-D example - MSB

Suppose V

X

= 21/32 (V

H

- V

L

) and already sampled

Compare after shifting half of capacitance to V

H

V

I

goes up by + 8/16 (V

H

-V

I

) - 8/16 (V

L

-V

I

) = + 8/16 (V

H

- V

L

)

original V

L

- V

I

goes down and becomes

V

L

- ( V

I

+ .5 (V

H

- V

L

) ) = V

L

- V

I

- .5 (V

H

- V

L

)

Output > 0

V

X

V

L

V

H

V

I

(nexf)

.b (V

H

- V

L

)

-

+

v

!

v

L

v

L

v

H

8

+ 2 1 1

4

(SLP56 13

A-to-D example - MSB-1,

Compare after shifting another part of cap. to V

H

V

I

goes up by + 4/16 (V

H

-V

I

) - 4/16 (V

L

-V

I

) = + 4/16 (V

H

- V

L

)

original V

L

- V

I

goes down and becomes

V

L

- ( V

I

+ .25 (V

H

- V

L

) ) = V

L

- V

I

- .25 (V

H

- V

L

)

Output < 0 (went too far)

V

X

V

L

V

H

V

I

(prev)

.Zb (V

H

- V

L

)

V

I

(nexf)

-

+

v

!

v

L

v

L

v

H

8 +

2 1 1

(SLP56 14

A-to-D example - MSB-2,

Compare after shifting another part of cap. to V

H

V

I

goes up by + 2/16 (V

H

-V

I

) - 2/16 (V

L

-V

I

) = + 2/16 (V

H

- V

L

)

original V

L

- V

I

goes down and becomes

V

L

- ( V

I

+ .125 (V

H

- V

L

) ) = V

L

- V

I

- .125 (V

H

- V

L

)

Output > 0

V

X

V

L

V

H

V

I

(prev)

.IZb (V

H

- V

L

)

V

I

(nexf)

-

+

v

!

v

L

v

L

v

H

8

+

2

1 1

(SLP56 15

A-to-D example - LSB

Compare after shifting another part of cap. to V

H

V

I

goes up by + 1/16 (V

H

-V

I

) - 1/16 (V

L

-V

I

) = + 1/16 (V

H

-

V

L

)

original V

L

- V

I

goes down and becomes

V

L

- ( V

I

+ .0625 (V

H

- V

L

) ) = V

L

- V

I

- .0625 (V

H

- V

L

)

Output < 0 (went too far again)

V

X

V

L

V

H

.0oZb (V

H

- V

L

)

-

+

v

!

v

L

v

L

v

H

8

+

2 1

1

(SLP56 16

A-to-D example inal result

Input sample of 21/32

Gives result of 1010 or 10/16 = 20/32

3% error

-

+

v

!

v

L

v

L

v

H

8

+

2

1 1

5

(SLP56 1

A-to-D (onersion Lrrors

(SLP56 18

(loser Look at A-to-D (onersion

Needs a comparator

and a D-to-A converter

Takes time to do

successive

approximation

Interrupt generated

when conversion is

completed

(SLP56 19

A-to-D (onersion on the A1mega16

10-bit resolution (adjusted to 8 bits as needed)

65-260 usec conversion time

8 multiplexed input channels

Capability to do differential conversion

Difference of two pins

Optional gain on differential signal (amplifies difference)

Interrupt on completion of A-to-D conversion

0-V

CC

input range

2*LSB accuracy (2 * 1/1024 = ~0.2%)

Susceptible to noise special analog supply pin (AVCC)

and capacitor connection for reference voltage (AREF)

(SLP56 20

A-to-D (onersion cont`d,

6

(SLP56 21

A-to-D (onersion

cont`d,

Single-ended or differential

1 of 8 single-ended

ADCx ADC1 at 1x gain

ADC{0,1} ADC0 at 10x

ADC{0,1} ADC0 at 200x

ADC{2,3} ADC2 at 10x

ADC{2,3} ADC3 at 200x

ADC{0,1,2,3,4,5} ADC2 at 1x

(SLP56 22

A-to-D (onersion cont`d,

(SLP56 23

A-to-D (onersion cont`d,

(SLP56 24

A-to-D (onersion cont`d,

7

(SLP56 25

\riting an Interrupt landler in (

again,

Ensure main program sets up all registers

Enable interrupts as needed

Enable global interrupts (SEI)

Write handler routine for each enabled interrupt

What if an interrupt occurs and a handler isnt defined?

Make sure routine does not disrupt others

Data sharing problem

Save any state that might be changed (done by compiler)

Re-enable interrupts upon return

done by compiler with RETI

(SLP56 26

Power modes

Processor can go to sleep and save power

Different modes put different sets of modules

to sleep

Which one to use depends on which modules are

needed to wake up processor

Timers, external interrupts, ADC, serial

communication lines, etc.

set_sleep_mode (mode);

sleep_mode ();

(SLP56 2

Power modes cont`d,

(SLP56 28

Power modes cont`d,

Wake up sources and active clocks

Potrebbero piacerti anche

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Valutazione: 2.5 su 5 stelle2.5/5 (3)

- Zero Crossing Detector and Window DetectorDocumento7 pagineZero Crossing Detector and Window DetectorTimoth Dev50% (2)

- Wiring Diagram ATS 160kva-COS FortDocumento5 pagineWiring Diagram ATS 160kva-COS Fortprihharmanto antok100% (1)

- Pee Lab ManualDocumento77 paginePee Lab ManualRajendraTuraka100% (1)

- Switch Mode ConvertersDocumento28 pagineSwitch Mode ConvertersHemantha KumarNessuna valutazione finora

- Gree-44814 09K 12K (LCLH)Documento87 pagineGree-44814 09K 12K (LCLH)MatyoJNessuna valutazione finora

- VSWR and S ParameterDocumento48 pagineVSWR and S ParameterJaime JarrinNessuna valutazione finora

- Power SuplyDocumento91 paginePower SuplyThomas SmithNessuna valutazione finora

- SECTION 15180 BMS and Automatic ControlsDocumento32 pagineSECTION 15180 BMS and Automatic ControlskdpmansiNessuna valutazione finora

- RoboTek-Makeblock-Grade 4Documento281 pagineRoboTek-Makeblock-Grade 4Michael Angelo Garcia0% (1)

- Lecture On Basic Concept Operation and Control of HVDCDocumento74 pagineLecture On Basic Concept Operation and Control of HVDCpongpum0% (1)

- Hef4053 PDFDocumento9 pagineHef4053 PDFSiêu Nhân Bụng MỡNessuna valutazione finora

- LMC7660 Switched Capacitor Voltage Converter PDFDocumento19 pagineLMC7660 Switched Capacitor Voltage Converter PDFePotyNessuna valutazione finora

- Two-Output LNB Supply and Control-Voltage Regulator: Advance InformationDocumento8 pagineTwo-Output LNB Supply and Control-Voltage Regulator: Advance InformationNam HoangNessuna valutazione finora

- Features Descriptio: LTC1546 Software-Selectable Multiprotocol Transceiver With TerminationDocumento20 pagineFeatures Descriptio: LTC1546 Software-Selectable Multiprotocol Transceiver With Terminationvsc2012Nessuna valutazione finora

- Half Wave and Full Wave RectifiersDocumento5 pagineHalf Wave and Full Wave RectifiersRajesh PylaNessuna valutazione finora

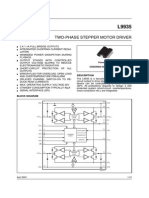

- Two-Phase Stepper Motor Driver: DescriptionDocumento19 pagineTwo-Phase Stepper Motor Driver: DescriptionDan EsentherNessuna valutazione finora

- Solution To Ele22Emi 2004 November Exam: V V 0) Is Called The Zero Offset.)Documento12 pagineSolution To Ele22Emi 2004 November Exam: V V 0) Is Called The Zero Offset.)سعيد ابوسريعNessuna valutazione finora

- MOS Transistors and CMOS InvertersDocumento34 pagineMOS Transistors and CMOS InverterssivapothiNessuna valutazione finora

- LM111-N/LM211-N/LM311-N Voltage Comparator: FeaturesDocumento30 pagineLM111-N/LM211-N/LM311-N Voltage Comparator: FeaturesJuan GomezNessuna valutazione finora

- SS VariacDocumento6 pagineSS VariacVíctor RojasNessuna valutazione finora

- Electronic Circuits - II Lab ManualDocumento26 pagineElectronic Circuits - II Lab Manualbalabasker100% (1)

- Power 2Documento6 paginePower 2parveen1001Nessuna valutazione finora

- Thyristor Commutation PDFDocumento40 pagineThyristor Commutation PDFalbert agung matondangNessuna valutazione finora

- DAC0800/DAC0802 8-Bit Digital-to-Analog Converters: General DescriptionDocumento0 pagineDAC0800/DAC0802 8-Bit Digital-to-Analog Converters: General DescriptionMiguel Angel García ValerioNessuna valutazione finora

- CH 3sDocumento67 pagineCH 3sSantosh GoudarNessuna valutazione finora

- Thyristor CommutationsDocumento41 pagineThyristor CommutationsRohan Bose100% (1)

- Carlo Gavazzi Level RelayDocumento5 pagineCarlo Gavazzi Level RelayPeter CalvoNessuna valutazione finora

- Topology Review DC DC ConvertersDocumento54 pagineTopology Review DC DC ConvertersaknuslNessuna valutazione finora

- ET1006 - 1213S2Exam - With Answers For RevisionDocumento15 pagineET1006 - 1213S2Exam - With Answers For RevisionfastNessuna valutazione finora

- UE AAE 13 Resonant Voltage ConvertersDocumento22 pagineUE AAE 13 Resonant Voltage ConvertersYung SangNessuna valutazione finora

- CMOS SubcircuitsDocumento80 pagineCMOS SubcircuitsashishmanyanNessuna valutazione finora

- Data SheetDocumento20 pagineData SheetLuis Fernando ChiavegatiNessuna valutazione finora

- Chapter 6 - OpAmpDocumento7 pagineChapter 6 - OpAmpOm PrakashNessuna valutazione finora

- Lect 3Documento42 pagineLect 3Supriya Rakshit0% (1)

- PEexp01 Comp IDocumento10 paginePEexp01 Comp Ijackychen101Nessuna valutazione finora

- Switch Mode ConvertersDocumento28 pagineSwitch Mode ConvertersAniruddh KashyapNessuna valutazione finora

- LM2663中文资料Documento12 pagineLM2663中文资料翟铭Nessuna valutazione finora

- 1mrk509006-Ben en Impedance Relay and Protection Assemblies RXZK 21h-23h RazkDocumento20 pagine1mrk509006-Ben en Impedance Relay and Protection Assemblies RXZK 21h-23h Razkpb21Nessuna valutazione finora

- LIC Lab Manual PDFDocumento102 pagineLIC Lab Manual PDFUdhayakumar SelvarajNessuna valutazione finora

- Makalah Signal ConditioningDocumento64 pagineMakalah Signal Conditioningw4w4n_s3mk4n1s4Nessuna valutazione finora

- SN 65 HVD 230Documento33 pagineSN 65 HVD 230correudebassuraNessuna valutazione finora

- 5V To 12 V Step-Up (Boost) Voltage Regulator With LM2577Documento2 pagine5V To 12 V Step-Up (Boost) Voltage Regulator With LM2577Taha AmjadNessuna valutazione finora

- +2.7V, Low-Power, 12-Bit Serial Adcs in 8-Pin SoDocumento16 pagine+2.7V, Low-Power, 12-Bit Serial Adcs in 8-Pin Sojnax101Nessuna valutazione finora

- Voltage Comperator3 LM397Documento10 pagineVoltage Comperator3 LM397ΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNessuna valutazione finora

- Lec 11 Sequential Logic CircuitsDocumento49 pagineLec 11 Sequential Logic CircuitsDeependra NigamNessuna valutazione finora

- Lecture EEE 447 Chap 5 DC DC ConvertersDocumento41 pagineLecture EEE 447 Chap 5 DC DC ConvertersMd. Anisur RahmanNessuna valutazione finora

- Design Considerations For An LLC Resonant ConverterDocumento29 pagineDesign Considerations For An LLC Resonant Converterbacuoc.nguyen356Nessuna valutazione finora

- CMOS Logic Circuits: Inverter 2 Input NOR 2 Input NAND Other FunctionsDocumento23 pagineCMOS Logic Circuits: Inverter 2 Input NOR 2 Input NAND Other FunctionsKumar Amit VermaNessuna valutazione finora

- 100 V Regulators: Gregor KleineDocumento1 pagina100 V Regulators: Gregor KleineEdward SlametNessuna valutazione finora

- Final Review PDFDocumento19 pagineFinal Review PDFurfriend_jjn05Nessuna valutazione finora

- EE 42/43/100 Introduction To Digital Electronics: Review of Ch. 4-7.3 7/19/13Documento43 pagineEE 42/43/100 Introduction To Digital Electronics: Review of Ch. 4-7.3 7/19/13ozanistzNessuna valutazione finora

- Power Electronics LabDocumento6 paginePower Electronics LabRafeyNessuna valutazione finora

- LT1144Documento8 pagineLT1144Brzata PticaNessuna valutazione finora

- Differential Clock TranslationDocumento12 pagineDifferential Clock Translationtian yuNessuna valutazione finora

- Dual ConverterDocumento16 pagineDual ConverterUdayakumar VengatesanNessuna valutazione finora

- Differential Voltage Current Conveyor (DVCC)Documento81 pagineDifferential Voltage Current Conveyor (DVCC)raam0006100% (1)

- Lec8 PDFDocumento36 pagineLec8 PDFPhan Phuong NgocNessuna valutazione finora

- Linear - 16-Bit, Ultra Precise, Fast Settling VOUT DACDocumento16 pagineLinear - 16-Bit, Ultra Precise, Fast Settling VOUT DACAtakan OzturKNessuna valutazione finora

- LM358 PDFDocumento14 pagineLM358 PDFChetan KotwalNessuna valutazione finora

- Circuit Theory - EM II: DR David Ottaway Braggs 412 PH 8313 5165 David - Ottaway@adelaide - Edu.auDocumento51 pagineCircuit Theory - EM II: DR David Ottaway Braggs 412 PH 8313 5165 David - Ottaway@adelaide - Edu.augfshhdNessuna valutazione finora

- Technical English - Lesson N°01Documento4 pagineTechnical English - Lesson N°01Hadj Ben Aichouche Maroua C1 B1Nessuna valutazione finora

- Kit Focal 165 v30 User ManualDocumento16 pagineKit Focal 165 v30 User ManualFelipe BonoraNessuna valutazione finora

- Manuel Radiocommande Futaba FP-9vhpDocumento28 pagineManuel Radiocommande Futaba FP-9vhpSébastien MunozNessuna valutazione finora

- 4G Database Myanmar 20160621 V1Documento73 pagine4G Database Myanmar 20160621 V1Boby SharifNessuna valutazione finora

- Automatic Adjustable Sex Machine With Dildo STCSFM-003 PDFDocumento1 paginaAutomatic Adjustable Sex Machine With Dildo STCSFM-003 PDFJoelNessuna valutazione finora

- TR-296 Series Service ManualDocumento29 pagineTR-296 Series Service Manualbellscb100% (1)

- C Pen 3.5 Product SheetDocumento1 paginaC Pen 3.5 Product Sheetjaggy286Nessuna valutazione finora

- Radiation Damage in Sentaurus TCADDocumento25 pagineRadiation Damage in Sentaurus TCADqiwinzhengNessuna valutazione finora

- 2822 HDocumento3 pagine2822 HKrank101Nessuna valutazione finora

- IGBT - Field Stop, Trench FGH40T120SMD, FGH40T120SMD-F155: DescriptionDocumento11 pagineIGBT - Field Stop, Trench FGH40T120SMD, FGH40T120SMD-F155: DescriptionSerjik FremenNessuna valutazione finora

- TQMA70E1-5 Bayard-Alpert Pirani Gauge 720 Short Operating InstructionsDocumento47 pagineTQMA70E1-5 Bayard-Alpert Pirani Gauge 720 Short Operating InstructionsSigit KurniawanNessuna valutazione finora

- Service Manual: KD-27FS130Documento76 pagineService Manual: KD-27FS130André LeftNessuna valutazione finora

- Optimize Hitachi Storage and Server Platforms in Vmware Vsphere 5 5 Environments Best Practices Guide PDFDocumento49 pagineOptimize Hitachi Storage and Server Platforms in Vmware Vsphere 5 5 Environments Best Practices Guide PDFLars GlöcknerNessuna valutazione finora

- A Novel High-Gain DC-DC Converter Applied in Fuel Cell VehiclesDocumento13 pagineA Novel High-Gain DC-DC Converter Applied in Fuel Cell Vehiclesrock starNessuna valutazione finora

- DX DiagDocumento28 pagineDX DiagAri NurdiansyahNessuna valutazione finora

- Otn Framing v1.0 PDFDocumento17 pagineOtn Framing v1.0 PDFDerrick Senyo100% (1)

- Technicolor Tc7200Documento4 pagineTechnicolor Tc7200grudva2Nessuna valutazione finora

- Spaj 140 CDocumento8 pagineSpaj 140 CaktifiantoNessuna valutazione finora

- Compressor L7044GSI-7045 - 1210Documento2 pagineCompressor L7044GSI-7045 - 1210Dedy Chasan Aflah MutoharNessuna valutazione finora

- KingtoneDocumento2 pagineKingtoneUlla WirtanenNessuna valutazione finora

- SerialsDocumento7 pagineSerialsapi-3708126Nessuna valutazione finora

- MD1D Evalmanual A1en - EvalBoardDocumento8 pagineMD1D Evalmanual A1en - EvalBoardS Puneeth Kumar100% (1)

- Camera Alignment For Series 7700 CCD Camera: Necessary Test ToolsDocumento6 pagineCamera Alignment For Series 7700 CCD Camera: Necessary Test ToolsEduardo Saul MendozaNessuna valutazione finora

- ANPC-5L Technology Applied To Medium Voltage Variable Speed Drives ApplicationsDocumento8 pagineANPC-5L Technology Applied To Medium Voltage Variable Speed Drives ApplicationsRen Hong GiangNessuna valutazione finora

- Digital Communications - Viva Voce QuestionsDocumento3 pagineDigital Communications - Viva Voce QuestionsAllanki Sanyasi Rao100% (1)

- SAIC-RTR4 User Manual 20 PagesDocumento20 pagineSAIC-RTR4 User Manual 20 PagesJim ToewsNessuna valutazione finora