Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Flancter App Note

Caricato da

bigdogguruDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Flancter App Note

Caricato da

bigdogguruCopyright:

Formati disponibili

July 2000 Application Note: The "Flancter" by Rob Weinstein

How To Set a Status Flag in One Clock Domain, Clear It in Another, and Never, Ever Have to Use an Asynchronous Clear for Anything but Reset

Overview

There are times when it is important to generate a status flag that is set by an event in one clock domain and reset by an event in a different clock domain. Using a D-type flip-flop where a is clocked in from one clock domain, and its 1 asynchronous reset is pulsed by logic in the second clock domain is the timehonored method to achieve this function. While there is nothing logically wrong with this, it introduces other problems such as combinational logic driving an asynchronous reset pin, uncertainty in timing constraint boundaries, and muddying the global reset function. Here I present an alternative method for generating a multiple clock domain flag register that mitigates these problems. It called the s Flancter(named by my colleague, Mark Long), and is shown in Figure 1. As you can see, it is made up of two D-type flip-flops, an inverter, and an

FF1

SET_CE SET_CLK

D Q CE CLR

Q1

OUT

FF2

RESET_CE RESET_CLK

D Q CE CLR

Q2

Figure 1 - Basic Flancter. exclusive OR (XOR) gate. Notice that the asynchronous reset inputs to the flipflops are shown unconnected for clarity only. Normally, these would be tied to the global set/reset net in the system. Operation of the Flancter is simple; when FF1 is clocked (rising edge of SET_CLK while SET_CE is asserted), OUT goes high. Contrariwise, when FF2 is clocked (rising edge of RESET_CLK while RESET_CE is asserted), OUT goes low. Note that this circuit must be used in an interlocked system where the flip-

Page 1 of 11

Application Note

The Flancter

flops won be continuously clocked by the two clock domains. Also, the output t must be synchronized with additional flip-flops to mitigate metastability when crossing clock domains (more about this later).

How It Works

To explain its operation, I like to rearrange the circuit as shown in Figure 2.

RESET_CE RESET_CLK

Q1 D Q CE D Q CE CLR CLR FF1 FF2

OUT

Q2

SET_CE SET_CLK

Figure 2 - Rearranged Flancter. This is exactly the same circuit as shown in Figure 1, but untwisted so that the two inputs to the XOR gate are clearly visible. You can see that the XOR gate s upper input is labeled Q1, while its lower input is labeled Q2. Also, Q1 and Q2 are the Q outputs of FF1 and FF2, respectively. Now for the trick part of this magic trick: the D input to FF1 comes from an inverter, so whenever FF1 is clocked, Q1 assumes the opposite state of Q2 and the output of the XOR gate will go high. When FF2 is clocked, Q2 becomes the same as Q1, and the output will go low. In summary, clocking FF1 causes OUT to go high and clocking FF2 causes OUT to go low. A timing diagram will help describe the Flancter operation. Figure 3 shows the s basic timing diagram:

Page 2 of 11

Application Note

The Flancter

SET_CLK SET_CE Q1 A C

RESET_CLK RESET_CE Q2 B OUT D

Figure 3 - Basic Flancter Timing. The basic points of interest in the timing diagram are: SET_CLK and RESET_CLK are asynchronous to each other. At point A, the rising edge of SET_CLK while SET_CE is high causes Q1 to go high because it gets the inverted value of Q2. Also, OUT goes high because it is the XOR of Q1 and Q2. At point B, the rising edge of RESET_CLK while RESET_CE is high causes Q2 to go high because it gets the value of Q1. Also, OUT goes low because it is the XOR of Q1 and Q2. At point C, Q1 again gets the inverted value of Q2, causing OUT to go high. At point D, Q2 goes low because it gets the value of Q1, causing OUT to go low.

So What Wrong With It? s

There are a few things wrong with the Flancter from the start. One problem is that it uses two flip-flops to create a single flag bit. This is a minor fault when you consider that most FPGAs have an abundant supply of flip-flops. A more serious issue is how to use the output. Remember that the output can change synchronously to either clock domain. You need to resynchronize the output to whichever clock domain needs to see it; often both clock domains. It is common to use two flip-flops in series as a metastability-resistant synchronizer. However, the most serious drawback to the Flancter is that operating the set and reset flip-flops must be mutually exclusive in time. This means that when logic in clock domain 1 sets the Flancter, it doesn attempt to set the Flancter again until t it sees that it has been reset. Likewise, the logic in clock domain 2 never attempts to reset the Flancter unless it sees that it has been set. Establishing this kind of interlocked protocol guarantees that both of the Flancter flip-flops won s t be clocked simultaneously (or within each other setup and hold time windows). s

Page 3 of 11

Application Note

The Flancter

Applications of the Flancter

There are many applications of the Flancter, but a very common application is interfacing a microprocessor to an FPGA. Typically, the microprocessor and FPGA logic run on separate clocks. When the microprocessor writes a control register within the FPGA, the Flancter can be used as a status flag to tell an internal state machine that new data is available. Likewise, a state machine within the FPGA can use the Flancter to generate an interrupt to the microprocessor that is subsequently cleared by a read or interrupt-acknowledge cycle from the microprocessor, as shown in Figure 4.

Part of FPGA

FF4 FF3

Q4

Q3

SYSCLK

D SYSCLK

CLR Control Inputs

CLR

FF1 SYSCLK State Machine SET_CE SYSCLK D Q CE CLR

Q1

SYSCLK Domain INT

uP Clock Domain

FF2 D Q CE CLR

Q2

uP

RD_L

RESET_CE

Address Decode

ADDRESS

PCLK

Figure 4 - Flancter Used for Microprocessor Interrupt.

Page 4 of 11

Application Note

The Flancter

Things to notice in Figure 4: The Flancter is made up of FF1, FF2, the inverter, and the XOR gate. The state machine, FF1, FF3, and FF4 are all synchronous to SYSCLK. The microprocessor (uP) runs off its own clock, PCLK. The state machine pulses SET_CE for one SYSCLK cycle when it needs to request an interrupt. The microprocessor performs a read cycle from a predefined address to reset the interrupt. Although not shown, reading from this address may also cause a status register to be driven onto the microprocessor data bus allowing s simultaneous reading of status and resetting of interrupt. FF3 and FF4 are resynchronizing flip-flops used to filter any metastable logic conditions from propagating into the state machine. The particular microprocessor used in this example employs metastable resistant techniques on its INT input. The interrupt sequence is defined such that setting and resetting the interrupt flag cannot occur simultaneously. The following timing diagram helps illustrate the operation:

SYSCLK SET_CE Q1 A

RD_L ADDRESS RESET_CE Q2 B INT Status Address

Figure 5 - Flancter Interrupt Timing Diagram. Things to notice in Figure 5: The FPGA state machine sets the interrupt request (INT) at point A. s Sometime later, the microprocessor responds to the interrupt by reading a status register, thus resetting the interrupt request at point B.

Page 5 of 11

Application Note

The Flancter

HDL Examples

Verilog Example

//--------------------------------------------------------------------// FileName : flancter.v // Author : Rob Weinstein // -------------------------------------------------------------------module flancter ( // Inputs ASYNC_RESET, SET_CLK, SET_CE, RESET_CLK, RESET_CE, // Outputs FLAG_OUT ) ; input input input input input output ASYNC_RESET; SET_CLK; SET_CE; RESET_CLK; RESET_CE; FLAG_OUT;

// Internal Registers reg SetFlop; reg RstFlop; // Output assignments assign FLAG_OUT = SetFlop ^ RstFlop ; // The Set flip-flop always @(posedge SET_CLK or posedge ASYNC_RESET) begin : set_proc if (ASYNC_RESET) SetFlop <= 0; else if (SET_CE) SetFlop <= ~RstFlop; // Flops get opposite logic levels. end // The Reset flip-flop always @(posedge RESET_CL K or posedge ASYNC_RESET) begin : reset_proc if (ASYNC_RESET) RstFlop <= 0; else if (RESET_CE) RstFlop <= SetFlop; // Flops get the same logic levels. end endmodule

Page 6 of 11

Application Note

The Flancter

VHDL Example

------------------------------------------------------------------ ------ FileName : flancter.vhd -- Author : Rob Weinstein ----------------------------------------------------------------------library IEEE; use IEEE.std_logic_1164.all; entity flancter is port ( ASYNC_RESET SET_CLK SET_CE RESET_CLK RESET_CE FLAG_OUT ); end flancter;

: : : : : :

in in in in in out

std_logic; std_logic; std_logic; std_logic; std_logic; std_logic

architecture flancter of flancter is signal SetFlop : std_logic; signal RstFlop : std_logic; begin --The Set flip-flop set_proc:process(ASYNC_RESET, SET_CLK) begin if ASYNC_RESET = '1' then SetFlop <= '0'; elsif rising_edge(SET_CLK) then if SET_CE = '1' then -- Flops get opposite logic levels. SetFlop <= not RstFlop; end if; end if; end process; --The Reset flip-flop reset_proc:process(ASYNC_RESET, RESET_CLK) begin if ASYNC_RESET = '1' then RstFlop <= '0'; elsif rising_edge(RESET_CLK) then if RESET_CE = '1' then -- Flops get the same logic levels. RstFlop <= SetFlop; end if; end if; end process; FLAG_OUT <= SetFlop xor RstFlop; end flancter;

Page 7 of 11

Application Note

The Flancter

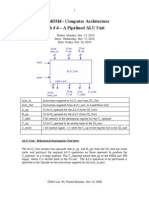

Synthesis Result The Verilog example was run through Synplify and the resulting HDL Analyst RTL view is shown in Figure below:

SET_CLK SET_CE RESET_CE 0 1 D Q R 1 0 D Q R FLAG_OUT

reset_proc_RstFlop_5 RstFlop

RESET_CLK ASYNC_RESET

set_proc_SetFlop_5 SetFlop

FLAG_OUT

Figure 6 - Synthesized Flancter. Note that in the RTL view, clock-enabled flip-flops are shown as multiplexers in front of D-type flip-flops.

Variations on a Flancter

While the basic Flancter is very simple, many useful variations are possible. I describe some of the more interesting variations below. Flancter Variation #1 One interesting variation lets you use a Flancter in lieu of a D-type flip-flop whose async clear input is used to save a clock cycle. In some single-clock-domain systems, the original designer relied on an async clear to immediately reset a flip-flop so that it would be reset by the next rising clock edge. A variation of a Flancter can give you the same functionality without relying on an async clear input. Figure 7 shows this variation:

FF1 SET_CE D Q CE CLR OUT CLK FF2 RESET_CE D Q CE CLR Falling Edge Triggered Q2 Q1

Figure 7 - Flancter Variation #1.

Page 8 of 11

Application Note

The Flancter

Note that this is the same as the Basic Flancter, but it uses a single clock input, CLK, and the reset flip-flop is clocked on the falling edge of that clock. Its operation is depicted in th timing diagram in Figure 8: e

CLK SET_CE Q1

RESET_CE Q2

OUT

Figure 8 - Flancter Timing for Variation #1. Things to notice in Figure 8: OUT goes high on the rising edge of CLK at point A in response to SET_CE. Sometime later, RESET_CE is pulsed for one CLK cycle, synchronous to the rising edge of CLK, but OUT responds to RESET_CE by going low on thefalling edge of CLK at point B. OUT is already low by the next rising edge of CLK at point C. If a synchronous reset had been used, OUT would still be high at point C. Flancter Variation #2 Another variation on the Flancter is to have OUT come up high after global reset. This is easily achieved by making sure that either FF1 or FF2 (but not both) uses an async preset instead of an async clear. Figure 9 shows wh I mean: at

Page 9 of 11

Application Note

The Flancter

SET_CE SET_CLK

FF1 PRE D Q CE

Q1

OUT

FF2 RESET_CE RESET_CLK D Q CE CLR Q2

Figure 9 - Flancter Variation #2.

Flancter Variation #3 This variation operates in three different clock domains.

FF1 SET_CE SET_CLK Q2 Q3 D Q CE CLR Q1

FF2 RESET1_CE RESET1_CLK Q1 Q3 D Q CE CLR Q2 OUT

FF3 RESET2_CE RESET2_CLK Q1 Q2 D Q CE CLR Q3

Figure 10 - 3-Way Flancter. The particular configuration shown inFigure 10 is set by one clock domain and reset by either of two other clock domains. Note that the flip -flop connected to the setting domain, FF1, has an inverter on its D input, while the flip -flops connected to the resetting domains, FF2 and FF3, do not. This variation works equally well with two setting domains and one resetting domain. The rule is to use inverters on the flip-flops in the setting domains and no inverters on the flip -flops in the

Page 10 of 11

Application Note

The Flancter

resetting domains. The inputs to the XO gates are simply the Q outputs of all R the registers except the one we are driving. For instance, the D input of FF1 uses the XOR of Q2 and Q3. Note that Q1 is not used in the input function to FF1. Likewise, FF2 is based on Q1 and Q3, but not Q2 and FF3is based on Q1 and Q2, but not Q3. A Flancter variation can be built with any number of setting and resetting clock domains; this is an n-way Flancter. The rules for building an n -way Flancter are: Use n flip-flops, one for each clock domain (FF1...FFn). The output of the n-way Flancter is simply the XOR of all of the Q outputs. The D input to any particular flip -flop (call it FFm), is the logical XOR of the Q outputs of all the flip-flops except the one we are driving (Q1 Qn except Qm). An inverter is inserted at the D inputs of a flip -flop based on whether that particular flip-flop is used for setting or resetting the n -way Flancter. Use inverters for setting flip-flops or no inverters for resetting flip -flops. Designing a protocol in which only one flip -flop is clocked at a time is the biggest problem with the n -way Flancter. Remember, the Flancter is only reliable when the flip -flops are never clocked simultaneously.

Summary

I turned 37 this year and I got to thinking that all the greatsdid their best work long before they reached my age. As I look back on my design career, I realize that I haven designed any circuits or developed any theorems that will bear my t name like the Pierce Oscillator or Shannon Sampling Theorem. The best I can s do is to offer the Flancter as my legacy. Perhaps someday, the Weinstein Flancter will be found in the indexes of engineering tomes right between Watt Hour and Wien-Bridge.

Page 11 of 11

Potrebbero piacerti anche

- PIC Architecture and Assembler Programming: (Including Software Time Delay Subroutine)Documento16 paginePIC Architecture and Assembler Programming: (Including Software Time Delay Subroutine)Ashim KumarNessuna valutazione finora

- Chapter 4: One-Shots, Counters, and Clocks: I. The Monostable Multivibrator (One-Shot)Documento6 pagineChapter 4: One-Shots, Counters, and Clocks: I. The Monostable Multivibrator (One-Shot)amitpatel1991Nessuna valutazione finora

- Part 1 - FSM DesignDocumento3 paginePart 1 - FSM DesignMENANI ZineddineNessuna valutazione finora

- Lab 04Documento6 pagineLab 04Bodour MohamedNessuna valutazione finora

- Report Clock Tree and Report Clock TimingDocumento8 pagineReport Clock Tree and Report Clock TimingDharma PangaNessuna valutazione finora

- ECET 105 Week 7 Lab Project Detailed DirectionsDocumento14 pagineECET 105 Week 7 Lab Project Detailed DirectionsMicro EmissionNessuna valutazione finora

- Over Current ProctectionDocumento25 pagineOver Current ProctectionSarah FrazierNessuna valutazione finora

- DLD Ch5Documento55 pagineDLD Ch5aboodNessuna valutazione finora

- Pic Microcontroller: Technological University of The PhilippinesDocumento15 paginePic Microcontroller: Technological University of The PhilippinesRonnel Joseph Cooper Renedo100% (1)

- BER MeterDocumento8 pagineBER Metersakti prasad nandaNessuna valutazione finora

- Demystifying Resets Synchronous Asynchronous Other Design Considerations Part 1Documento7 pagineDemystifying Resets Synchronous Asynchronous Other Design Considerations Part 1alexNessuna valutazione finora

- Lab 4 - Finite State Machines: GoalsDocumento7 pagineLab 4 - Finite State Machines: GoalsJoey WangNessuna valutazione finora

- Asynchronous FIFODocumento21 pagineAsynchronous FIFOMarium Mazhar50% (2)

- EC 303 Chapter 2Documento48 pagineEC 303 Chapter 2PrevenaManiamNessuna valutazione finora

- Name of The Experiment: Sequential Circuit Design - Latch, Flip Flop and Registers Important: Submit Your Prelab at The Beginning of The LabDocumento7 pagineName of The Experiment: Sequential Circuit Design - Latch, Flip Flop and Registers Important: Submit Your Prelab at The Beginning of The LabAurongo NasirNessuna valutazione finora

- DSD Lab 9 HandoutDocumento5 pagineDSD Lab 9 HandoutFaiza Tabassam 546-FET/BSEE/F19Nessuna valutazione finora

- App of CFC Logic in Intel DevicesDocumento14 pagineApp of CFC Logic in Intel Devicesiwan.satyaNessuna valutazione finora

- Ic 693 Cpu 313Documento5 pagineIc 693 Cpu 313mubashersaeedNessuna valutazione finora

- Interrupt and ReturnDocumento75 pagineInterrupt and ReturnAlex PérezNessuna valutazione finora

- Design and Implementation of Synchronous 4-Bit Up Counter Using 180Nm Cmos Process TechnologyDocumento6 pagineDesign and Implementation of Synchronous 4-Bit Up Counter Using 180Nm Cmos Process TechnologyreyysummerNessuna valutazione finora

- Latticexp2 Sysclock PLL Design and Usage Guide: March 2012 Technical Note Tn1126Documento28 pagineLatticexp2 Sysclock PLL Design and Usage Guide: March 2012 Technical Note Tn1126Krishnakumar SomanpillaiNessuna valutazione finora

- Latch and Flip-FlopDocumento58 pagineLatch and Flip-FlopDalila Nadia RazaliNessuna valutazione finora

- Lect17 SeqDocumento18 pagineLect17 SeqorengeneralNessuna valutazione finora

- VCLASS-2 M5 Perc Sintetik-28102020Documento10 pagineVCLASS-2 M5 Perc Sintetik-28102020Fatah Nur HidayatNessuna valutazione finora

- ECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitDocumento8 pagineECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitsantoshmphilNessuna valutazione finora

- uPF1 Monitor Program Listing (Original Scan)Documento59 pagineuPF1 Monitor Program Listing (Original Scan)Jose Luis Abasolo MayorNessuna valutazione finora

- Digital Electronics Module 05Documento44 pagineDigital Electronics Module 05Yadana1Nessuna valutazione finora

- Activity 3.1.1 Sequential Logic - D Flip-Flops and JK Flip-Flops PDFDocumento5 pagineActivity 3.1.1 Sequential Logic - D Flip-Flops and JK Flip-Flops PDFChris Ronald CherestalNessuna valutazione finora

- Step Replace Module Flexi BSC NokiaDocumento19 pagineStep Replace Module Flexi BSC Nokiarudibenget0% (1)

- LABDCT 2002 (Guide) Nexus.5020.Lab - GuideDocumento52 pagineLABDCT 2002 (Guide) Nexus.5020.Lab - Guidekds20850Nessuna valutazione finora

- 512 ManualDocumento77 pagine512 ManualHamada AlmasalmaNessuna valutazione finora

- DSD Lab 9 HandoutDocumento5 pagineDSD Lab 9 HandoutMuhammad AnasNessuna valutazione finora

- MSP Devie ErratasheetDocumento8 pagineMSP Devie ErratasheetmaanviNessuna valutazione finora

- PIC16F628A ExperimentosDocumento11 paginePIC16F628A ExperimentosCesar Matos100% (2)

- Sequential CircuitsDocumento22 pagineSequential CircuitsBaeNessuna valutazione finora

- SN1-2223-Lab3 1-2 EngDocumento4 pagineSN1-2223-Lab3 1-2 EngBoualem MestafaNessuna valutazione finora

- Search For DocumentsDocumento9 pagineSearch For DocumentsdineshvhavalNessuna valutazione finora

- Lab 1Documento8 pagineLab 1Mulugeta AbebawNessuna valutazione finora

- Gated Clock ConversionDocumento8 pagineGated Clock ConversionKillivalavan KaliyamoorthyNessuna valutazione finora

- DVP Ss ManualDocumento459 pagineDVP Ss ManualjoaokalatecNessuna valutazione finora

- Grupo 23 - Tarea 4Documento23 pagineGrupo 23 - Tarea 4alexis pedrozaNessuna valutazione finora

- Experiment 9 Sequential Circuits Introduction To CountersDocumento3 pagineExperiment 9 Sequential Circuits Introduction To CountersKeshav MusunuriNessuna valutazione finora

- Mod 5Documento83 pagineMod 5Jane BillonesNessuna valutazione finora

- VWV FinalyDocumento11 pagineVWV FinalyYogesh PolNessuna valutazione finora

- 555 GreenpackDocumento17 pagine555 GreenpackRuboto BotoNessuna valutazione finora

- The Flancter DoulosDocumento2 pagineThe Flancter DoulosMiguel BrunoNessuna valutazione finora

- Equations and Impacts of Setup and Hold TimeDocumento5 pagineEquations and Impacts of Setup and Hold Timepavithra reddyNessuna valutazione finora

- Equations and Impacts of Setup and Hold Time: SkewDocumento5 pagineEquations and Impacts of Setup and Hold Time: SkewVardhan KarnatiNessuna valutazione finora

- Clock PowerDocumento8 pagineClock PowerSathish BalaNessuna valutazione finora

- Equations and Impacts of Setup and Hold TimeDocumento5 pagineEquations and Impacts of Setup and Hold TimeShravan Kumar AshannagariNessuna valutazione finora

- Family Questions A Swers: Zao CRCDocumento27 pagineFamily Questions A Swers: Zao CRCfrankNessuna valutazione finora

- A3 1 1IntroductionFlipFlopsDocumento5 pagineA3 1 1IntroductionFlipFlopsGoran MateiaseviciNessuna valutazione finora

- TIMER Radovan RabrenovicDocumento15 pagineTIMER Radovan RabrenovicRadovan RabrenovicNessuna valutazione finora

- Clock Optimization Techniques For Abutted Channelless Floorplanning MethodologiesDocumento5 pagineClock Optimization Techniques For Abutted Channelless Floorplanning MethodologiesBaluvu JagadishNessuna valutazione finora

- DigSilent TechRef - RecloserDocumento17 pagineDigSilent TechRef - RecloserАлишер ГалиевNessuna valutazione finora

- MG4 HD4Documento9 pagineMG4 HD4VIJAYPUTRANessuna valutazione finora

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksDa EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksNessuna valutazione finora

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosDa EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosValutazione: 5 su 5 stelle5/5 (1)

- M Oscillator SeriesDocumento2 pagineM Oscillator SeriesbigdogguruNessuna valutazione finora

- Krell KST-100 Owners ManualDocumento16 pagineKrell KST-100 Owners ManualbigdogguruNessuna valutazione finora

- Crystals: VCXO Voltage Controlled Crystal Oscillator R SeriesDocumento2 pagineCrystals: VCXO Voltage Controlled Crystal Oscillator R SeriesbigdogguruNessuna valutazione finora

- DMM32v2 64Documento57 pagineDMM32v2 64bigdogguruNessuna valutazione finora

- DMM 32 atDocumento1 paginaDMM 32 atbigdogguruNessuna valutazione finora

- Op Amps PT2Documento3 pagineOp Amps PT2bigdogguruNessuna valutazione finora

- A Primer of Quaternions - Arthur S. HathawayDocumento70 pagineA Primer of Quaternions - Arthur S. HathawayKevin G. RhoadsNessuna valutazione finora

- Spru889 - High Speed DSP Systems DesignDocumento77 pagineSpru889 - High Speed DSP Systems DesignAriana Ribeiro LameirinhasNessuna valutazione finora

- Op Amps PT1Documento4 pagineOp Amps PT1bigdogguruNessuna valutazione finora

- Microchipc An245 mcp23016Documento18 pagineMicrochipc An245 mcp23016Kevin Paul Garrido100% (1)

- AUBTM-22 AT CommandsDocumento36 pagineAUBTM-22 AT Commandscris_sabrinaNessuna valutazione finora

- 4727Documento21 pagine4727bigdogguruNessuna valutazione finora

- PIC 16F690 and 62256 32K SRAM - Nexuslite DevelopmentDocumento3 paginePIC 16F690 and 62256 32K SRAM - Nexuslite DevelopmentbigdogguruNessuna valutazione finora

- P160Analog UserGuide 1 2Documento21 pagineP160Analog UserGuide 1 2bigdogguruNessuna valutazione finora

- Honda Accord 2008-2010 v6 OemDocumento1.794 pagineHonda Accord 2008-2010 v6 OemAlbertoCòrdovaNessuna valutazione finora

- Ducon Construction Chemicals Industries LTD - Concrete Admixtures in BangladeshDocumento3 pagineDucon Construction Chemicals Industries LTD - Concrete Admixtures in BangladeshFounTech612Nessuna valutazione finora

- Longman General Practice Exercises 1-4 Merged and AnsweredDocumento64 pagineLongman General Practice Exercises 1-4 Merged and AnsweredHowaida El MadawyNessuna valutazione finora

- (Sears) DeluxeDemandWaterSoftenersownersmanualsDocumento32 pagine(Sears) DeluxeDemandWaterSoftenersownersmanualsGreg Reyneke100% (1)

- User Manual: Touch Control LED LampDocumento1 paginaUser Manual: Touch Control LED LampHector LuisNessuna valutazione finora

- Mechanical ComprehensionDocumento14 pagineMechanical Comprehensiondanielhealy100% (6)

- As 3638-1993 Test Sieving ProceduresDocumento7 pagineAs 3638-1993 Test Sieving ProceduresSAI Global - APACNessuna valutazione finora

- Index of Green Room MagazineDocumento2 pagineIndex of Green Room MagazineRita AgostiNessuna valutazione finora

- Pantaloons FinalDocumento30 paginePantaloons FinalAnkit SharmaNessuna valutazione finora

- Unit - 2 SatcommDocumento35 pagineUnit - 2 SatcommVerzeo group projectNessuna valutazione finora

- A1NM Rev 30 TYPE CERTIFICATE DATA SHEET A1NM 767Documento16 pagineA1NM Rev 30 TYPE CERTIFICATE DATA SHEET A1NM 767MuseNessuna valutazione finora

- Yamaha A-S2000 PDFDocumento90 pagineYamaha A-S2000 PDFpeti5_1Nessuna valutazione finora

- Duty Statements Office Technician Typing PDFDocumento3 pagineDuty Statements Office Technician Typing PDFremon4hrNessuna valutazione finora

- Liquid Distribution and Falling Film Wetting in Dairy EvaporatorsDocumento227 pagineLiquid Distribution and Falling Film Wetting in Dairy Evaporatorsyadavmihir63Nessuna valutazione finora

- ECE 551 Assignment 2: Ajit R Kanale, 200132821 January 25, 2017Documento5 pagineECE 551 Assignment 2: Ajit R Kanale, 200132821 January 25, 2017Ajit KanaleNessuna valutazione finora

- Hyb 96 MhuaDocumento13 pagineHyb 96 Mhuaأبو زينب المهندسNessuna valutazione finora

- Seipl Profile and CapabilitiesDocumento32 pagineSeipl Profile and CapabilitiesAbhishek GuptaNessuna valutazione finora

- EEPW3142 QP Version-ADocumento8 pagineEEPW3142 QP Version-A3nathNessuna valutazione finora

- Resume: Gayathri.SDocumento2 pagineResume: Gayathri.SKeyar SrinivasanNessuna valutazione finora

- Crane GBLDocumento2 pagineCrane GBLbudi setiawanNessuna valutazione finora

- Trailler On JettyDocumento4 pagineTrailler On JettyFuad Andaru BaskaraNessuna valutazione finora

- Obtaining Technology - ImplementationDocumento13 pagineObtaining Technology - ImplementationEric EugenioNessuna valutazione finora

- International StrategyDocumento34 pagineInternational StrategymanicatewatiaNessuna valutazione finora

- Employee Departure Clearance FormDocumento1 paginaEmployee Departure Clearance FormJery TomNessuna valutazione finora

- SEO For Growth: The Ultimate Guide For Marketers, Web Designers & EntrepreneursDocumento7 pagineSEO For Growth: The Ultimate Guide For Marketers, Web Designers & EntrepreneursJoyce M LaurenNessuna valutazione finora

- Penilaian Kinerja Malcolm BaldridgeDocumento24 paginePenilaian Kinerja Malcolm BaldridgeHijrah Saputro RaharjoNessuna valutazione finora

- Tapered Hub Guidelines Rev3-28-03 PDFDocumento4 pagineTapered Hub Guidelines Rev3-28-03 PDFPedro RiveraNessuna valutazione finora

- H07RN-F - (LTC) - 4Documento6 pagineH07RN-F - (LTC) - 4Faizal AzwaryNessuna valutazione finora

- Design of Anchor Bolts Embedded in Concrete MasonryDocumento9 pagineDesign of Anchor Bolts Embedded in Concrete MasonryYoesuf DecipherNessuna valutazione finora

- Proses Manufaktur: Machining Operation and Machine ToolsDocumento34 pagineProses Manufaktur: Machining Operation and Machine ToolsLyndaNessuna valutazione finora