Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Notation M: MSB L: LSB In: Input

Caricato da

Jatin NagpalTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Notation M: MSB L: LSB In: Input

Caricato da

Jatin NagpalCopyright:

Formati disponibili

1 CSE370, Lecture 21

Overview

Last lecture

!ntroduction to finite-state machines

Noore versus Nealy machines

Synchronous Nealy machines

Example: A parity checker

Today

Example: A sequence detector FSN

Example: A vending machine FSN

FSNs in verilog

2 CSE370, Lecture 21

FSN design

FSN-design procedure

1. State diagram and state-transition table

2. State minimization

3. State assignment (or state encoding)

+. Ninimize next-state logic

5. !mplement the design

3 CSE370, Lecture 21

Example: Sequence detector

Design a circuit to detect 3 or more 1's in a bit string

Assume Noore machine

Assume D flip-flops

Assume flip-flops have a reset

+ CSE370, Lecture 21

1. State diagram and state-transition table

B/0

C/0

A/0

D/1

1

0

0

1

1

1

reset

0

0

current next current

reset state input state output

1 A 0

0 A 0 A 0

0 A 1 B 0

0 B 0 A 0

0 B 1 C 0

0 C 0 A 0

0 C 1 D 0

0 D 0 A 1

0 D 1 D 1

5 CSE370, Lecture 21

2. State minimization 8 3. State encoding

State diagram is already minimized

Try a binary encoding

B/0

C/0

A/0

D/1

1

0

0

1

1

1

reset

0

0

current next current

reset state input state output

1 00 0

0 00 0 00 0

0 00 1 01 0

0 01 0 00 0

0 01 1 10 0

0 10 0 00 0

0 10 1 11 0

0 11 0 00 1

0 11 1 11 1

6 CSE370, Lecture 21

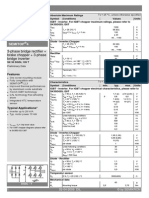

+. Ninimize next-state logic

N

L

!n

0 0 0 0

0 1 1 1

NSB+

N

L

!n

0 0 0 0

1 0 1 1

LSB+

N

L

!n

0 0 1 0

0 0 1 0

OUT+

Out+ = ML MSB+ = LIn + MIn LSB+ = L'In + MIn

Notation

M := MSB

L := LSB

In := Input

7 CSE370, Lecture 21

5. !mplement the design

LSB

MSB

Clock

Reset

LSB

In

MSB

In

Reset Out

LSB

In

MSB

In

45

NOT

51

AND2

44

OR2

42

D

DFF

CLRN

Q

PRN

52

AND2

53

AND2

48

AND2

47

OR2

41

D

DFF

CLRN

Q

PRN

43

AND2

Out+ = ML

MSB+ = LIn + MIn

LSB+ = L'In + MIn

8 CSE370, Lecture 21

Design example: A vending machine

Release item after receiving 15 cents

Single coin slot for dimes and nickels

Sensor specifies coin type

Nachine does not give change

vending

Nachine

FSN

N

D

Reset

Clock

Open

Coin

Sensor

Release

Nechanism

9 CSE370, Lecture 21

1a. State diagram

Consider input sequences

3 nickels

2 nickels, dime

nickel, dime

dime, nickel

two dimes

Draw state diagram

Assume Noore machine

!nputs: N, D, reset

Output: Open

S0

Reset

N

S1 S2

S3

S4 S5 S6

S7

N

N

N D

D

D

[open] [open] [open]

[open]

S8

[open]

D

10 CSE370, Lecture 21

present inputs next present

state D N state output

0 0 0 0 0

0 1 5 0

1 0 10 0

1 1

5 0 0 5 0

0 1 10 0

1 0 15 0

1 1

10 0 0 10 0

0 1 15 0

1 0 15 0

1 1

15 15 1

1b. Symbolic state-transition table

11 CSE370, Lecture 21

2. State minimization

Reuse states where possible

Notice we can use the deposited

coin values for states

State is the same if we input 2

nickels or 1 dime

0

Reset

5

N

N

N + D

10

D

15

[open|

D

12 CSE370, Lecture 21

3. State encoding

Encode states uniquely

+ states:

2 bits minimum

+ bits maximum

Look for optimal

encoding

Assume D flip-flops

present state inputs next state present

Q0 Q1 D N P1 P0 output

0 0 0 0 0 0 0

0 1 0 1 0

1 0 1 0 0

1 1

0 1 0 0 0 1 0

0 1 1 0 0

1 0 1 1 0

1 1

1 0 0 0 1 0 0

0 1 1 1 0

1 0 1 1 0

1 1

1 1 1 1 1

13 CSE370, Lecture 21

+. Ninimize the logic

N

0 0 1 1

0 1 1 1

X X X X

1 1 1 1

Q1Q0

DN

Q1

00 01 11 10

00

01

11

10

D

Q0

K-map for P1 K-map for P0

N

0 1 1 0

1 0 1 1

X X X X

0 1 1 1

Q1Q0

DN

Q1

00 01 11 10

00

01

11

10

D

Q0

K-map for Open

N

0 0 1 0

0 0 1 0

X X X X

0 0 1 0

Q1Q0

DN

Q1

00 01 11 10

00

01

11

10

D

Q0

P

1

= Q

1

+ D + Q

0

N

P

0

= Q

0

'N + Q

0

N' + Q

1

N + Q

1

D

OPEN = Q

1

Q

0

if FFs do not have a reset pin then

P

1

= reset'(Q

1

+ D + Q

0

N)

P

0

= reset'(Q

0

'N + Q

0

N' + Q

1

N + Q

1

D)

1+ CSE370, Lecture 21

5. !mplement the design

P

1

= Q

1

+ D + Q

0

N

P

0

= Q

0

'N + Q

0

N' + Q

1

N + Q

1

D

OPEN = Q

1

Q

0

15 CSE370, Lecture 21

Retime design

OPEN is delayed by AND gate after Q

1

and Q

0

Can remove this delay by retiming

Nove output logic (AND gate) to eliminate delay

OPEN = Q

1

Q

0

= (Q

1

+D+Q

0

N)(Q

0

'N+Q

0

N'+Q

1

N+Q

1

D)

Original Design Retimed Design

16 CSE370, Lecture 21

Noore versus Nealy vending machine

Noore machine Nealy machine

D/1

D/0

0

Reset

5

10

15

N'D'/0

N'D'/0

N'D'/0

/1

N+D

D

D

0

[0]

Reset

5

[0]

10

[0]

15

[1]

N

N

N'D'

N'D'

N'D'

N+D/1

N/0

N/0

17 CSE370, Lecture 21

Hardware Description Languages and

Sequential Logic

Flip-flops

representation of clocks - timing of state changes

asynchronous vs. synchronous

FSNs

structural view (FFs separate from combinational logic)

behavioral view (synthesis of sequencers - not in this course)

Data-paths = data computation (e.g., ALUs,

comparators) + registers

use of arithmeticflogical operators

control of storage elements

18 CSE370, Lecture 21

Example: reduce-1-string-by-1

Remove one 1 from every string of 1s on the input

1

0

0

0

1

1

zero

[0|

one1

[0|

two1s

[1|

1f0 0f0

0f0

1f1

zero

[0|

one1

[0|

Noore Nealy

19 CSE370, Lecture 21

`define zero 0

`define one1 1

`define two1s 2

module reduce (clk, reset, in, out);

input clk, reset, in;

output out;

reg out;

reg [2:1] state; // state variables

reg [2:1] next_state;

always @(posedge clk)

if (reset) state = `zero;

else state = next_state;

state assignment

verilog FSN - Reduce 1s example

Noore machine

1

0

0

0

1

1

zero

[0|

one1

[0|

two1s

[1|

20 CSE370, Lecture 21

always @(in or state)

case (state)

`zero:

// last input was a zero

begin

if (in) next_state = `one1;

else next_state = `zero;

end

`one1:

// we've seen one 1

begin

if (in) next_state = `two1s;

else next_state = `zero;

end

`two1s:

// we've seen at least 2 ones

begin

if (in) next_state = `two1s;

else next_state = `zero;

end

endcase

crucial to include

all signals that are

input to state determination

Noore verilog FSN (cont'd)

note that output

depends only on state

always @(state)

case (state)

`zero: out = 0;

`one1: out = 0;

`two1s: out = 1;

endcase

endmodule

21 CSE370, Lecture 21

module reduce (clk, reset, in, out);

input clk, reset, in;

output out;

reg out;

reg state; // state variables

reg next_state;

always @(posedge clk)

if (reset) state = `zero;

else state = next_state;

always @(in or state)

case (state)

`zero: // last input was a zero

begin

out = 0;

if (in) next_state = `one;

else next_state = `zero;

end

`one: // we've seen one 1

if (in) begin

next_state = `one; out = 1;

end else begin

next_state = `zero; out = 0;

end

endcase

endmodule

Nealy verilog FSN

1J0 0J0

0J0

1J1

zero

[0]

one1

[0]

22 CSE370, Lecture 21

module reduce (clk, reset, in, out);

input clk, reset, in;

output out;

reg out;

reg state; // state variables

always @(posedge clk)

if (reset) state = `zero;

else

case (state)

`zero: // last input was a zero

begin

out = 0;

if (in) state = `one;

else state = `zero;

end

`one: // we've seen one 1

if (in) begin

state = `one; out = 1;

end else begin

state = `zero; out = 0;

end

endcase

endmodule

Synchronous Nealy Nachine

Potrebbero piacerti anche

- Honda Prezintă Noua CMX 1100 Rebel DCT - Motobikes 2Documento1 paginaHonda Prezintă Noua CMX 1100 Rebel DCT - Motobikes 2Suciu BiancaNessuna valutazione finora

- Raport KTSPDocumento4 pagineRaport KTSPdjumiranNessuna valutazione finora

- Home at Last - New Originals ArrangementDocumento2 pagineHome at Last - New Originals Arrangementedskeyboard100% (1)

- C ProgramsDocumento9 pagineC ProgramsGopi ChanduNessuna valutazione finora

- Serial KeysDocumento9 pagineSerial KeysRiicardo RosaNessuna valutazione finora

- RS 70 - Conexel - Relé de InterposiçãoDocumento1 paginaRS 70 - Conexel - Relé de InterposiçãoKim Nicolas SaikiNessuna valutazione finora

- LBO ModelDocumento13 pagineLBO ModelSonali Dash100% (1)

- Arabic Ccna VoiceDocumento42 pagineArabic Ccna VoiceMorad AlabsyNessuna valutazione finora

- Surat Ijin Meninggalkan DinasDocumento2 pagineSurat Ijin Meninggalkan DinasJoko LelonoNessuna valutazione finora

- NL9 7 TakahashiDocumento20 pagineNL9 7 TakahashiAnand KrishnaNessuna valutazione finora

- B0a, 740D 'E) ?$%e, 30F?#) - ) G0 (#-,: !C! !C! !C! !C!Documento2 pagineB0a, 740D 'E) ?$%e, 30F?#) - ) G0 (#-,: !C! !C! !C! !C!Natasha MyersNessuna valutazione finora

- Block Diagram of A Sequential Logic Circuit: Combinational Circuit Memory Elements Inputs OutputsDocumento51 pagineBlock Diagram of A Sequential Logic Circuit: Combinational Circuit Memory Elements Inputs OutputsJagan RajendiranNessuna valutazione finora

- Venus 2Documento33 pagineVenus 2mahsam58Nessuna valutazione finora

- All 200 Series CPU's Wiring DrawingDocumento15 pagineAll 200 Series CPU's Wiring DrawingpandubhargaviNessuna valutazione finora

- Concentrado FinancieroDocumento10 pagineConcentrado FinancieroDrNetasNessuna valutazione finora

- Exp No: Usage of Cursor Date:: Branch Name, House No (PK), AmountDocumento6 pagineExp No: Usage of Cursor Date:: Branch Name, House No (PK), AmountaaanathanNessuna valutazione finora

- Credit Risk ManagementDocumento6 pagineCredit Risk ManagementAshadur Rahman JahedNessuna valutazione finora

- BI I I I A A A A: Beyond Innovation Technology Co., LTDDocumento10 pagineBI I I I A A A A: Beyond Innovation Technology Co., LTDVirginiaJ92Nessuna valutazione finora

- 2005-04-11 Mobile Content. Let Everyone Be Happy - Vittorio Maffei - La Netro ZEDDocumento11 pagine2005-04-11 Mobile Content. Let Everyone Be Happy - Vittorio Maffei - La Netro ZEDMobile Monday ItalyNessuna valutazione finora

- FeaturesDocumento75 pagineFeaturesindustronicaNessuna valutazione finora

- Phatty CCsDocumento4 paginePhatty CCssvitilla0% (1)

- Chronicles v3Documento407 pagineChronicles v3Transação autorizadaNessuna valutazione finora

- Meridiano de Greenwich - Toda MatériaDocumento1 paginaMeridiano de Greenwich - Toda MatériaIzabella SantosNessuna valutazione finora

- Drug Price Control Order 2013Documento73 pagineDrug Price Control Order 2013Latest Laws TeamNessuna valutazione finora

- Flexi EDGE BTS Troubleshooting: C C C C !""#Documento104 pagineFlexi EDGE BTS Troubleshooting: C C C C !""#Alexander TyshchenkoNessuna valutazione finora

- R5Sr&Ttug Gu% Vur Uw: Cap. 5,51,21 DRF 19,35,04 WMS 3,43,77Documento2 pagineR5Sr&Ttug Gu% Vur Uw: Cap. 5,51,21 DRF 19,35,04 WMS 3,43,77Ashish Kumar PandeyNessuna valutazione finora

- Chuong 2 Tin Hoc Can BanDocumento36 pagineChuong 2 Tin Hoc Can BanTrang LeNessuna valutazione finora

- Ofertório em Procissão Vão o Pão e o Vinho - PáscoaDocumento2 pagineOfertório em Procissão Vão o Pão e o Vinho - PáscoaDamilson SantosNessuna valutazione finora

- Bates V Post Office: Paula Vennells Email ChainDocumento5 pagineBates V Post Office: Paula Vennells Email ChainNick WallisNessuna valutazione finora

- Digital and Logic Devices No 5 DLD Basic DevicesBasic Flip-Flop Sequential CircuitDocumento51 pagineDigital and Logic Devices No 5 DLD Basic DevicesBasic Flip-Flop Sequential CircuitSanthi SriNessuna valutazione finora

- By James Demeo and The Orgone Biophysical Research Laboratory, IncDocumento24 pagineBy James Demeo and The Orgone Biophysical Research Laboratory, IncchrifotiNessuna valutazione finora

- Order Form SilverDocumento4 pagineOrder Form SilverekaaprilNessuna valutazione finora

- Executive Summary - 25580828Documento2 pagineExecutive Summary - 25580828Ken Worawuth SathianhiranNessuna valutazione finora

- 08 Poredos Lavor JerkovicDocumento7 pagine08 Poredos Lavor JerkovicDragana MuticNessuna valutazione finora

- Samuel Sagan Awakening The Third Eye PDFDocumento279 pagineSamuel Sagan Awakening The Third Eye PDFSónia RibeiroNessuna valutazione finora

- Verificacion POESDocumento7 pagineVerificacion POESinsegalconsultoresNessuna valutazione finora

- Key Sponsors Held inDocumento2 pagineKey Sponsors Held injuliafriedman69Nessuna valutazione finora

- Doreyeh 4 Erfaneh Halgheh Keyhani Faradarmani Psymentology Dr. Mohammad Ali TaheriDocumento22 pagineDoreyeh 4 Erfaneh Halgheh Keyhani Faradarmani Psymentology Dr. Mohammad Ali TaheriMohammad Ali Taheri100% (1)

- SK 50 DGDL 126 T: Converter, Inverter, BrakeDocumento4 pagineSK 50 DGDL 126 T: Converter, Inverter, Brakemurugan_parvathyNessuna valutazione finora

- ' (C) C' C+,C - (C: CC C CC CCC C CDocumento91 pagine' (C) C' C+,C - (C: CC C CC CCC C CnuckcheddyNessuna valutazione finora

- SmeaDocumento3 pagineSmeaBoiwtosNessuna valutazione finora

- Jar of Hearts (Accompaniment) : Christina PerriDocumento5 pagineJar of Hearts (Accompaniment) : Christina Perricar0lynNessuna valutazione finora

- SR22 Insurance FAQs Answers To Common SR22 QuestionsDocumento1 paginaSR22 Insurance FAQs Answers To Common SR22 QuestionsbroteliliNessuna valutazione finora

- RPS Ners Jiwa 2021 2022-DikonversiDocumento13 pagineRPS Ners Jiwa 2021 2022-DikonversiResa ErlinaNessuna valutazione finora

- Geanta Manoliu - Manual de VioaraDocumento22 pagineGeanta Manoliu - Manual de VioaraMatei B81% (36)

- Lab 1 PDFDocumento45 pagineLab 1 PDFBrian PahapayNessuna valutazione finora

- Comentario Al Nuevo Testamento - Tomo 2 - Evangelio Según San Mateo (II)Documento21 pagineComentario Al Nuevo Testamento - Tomo 2 - Evangelio Según San Mateo (II)ArninRamirezNessuna valutazione finora

- Tower Crane Footing Structural Design ReDocumento14 pagineTower Crane Footing Structural Design ReNeil WayneNessuna valutazione finora

- Tower Crane Footing Structural Design ReDocumento14 pagineTower Crane Footing Structural Design ReVirah Sammy ChandraNessuna valutazione finora

- A Capitalist Road To Communism 20 Years AfterDocumento23 pagineA Capitalist Road To Communism 20 Years AfterTopeteNessuna valutazione finora

- Buy Bitcoin Instantly PaxfulDocumento1 paginaBuy Bitcoin Instantly PaxfulHudson HarmonNessuna valutazione finora

- Dorotea Fotivec Prijevodi Tekstova Na Muzejskoj IzložbiDocumento32 pagineDorotea Fotivec Prijevodi Tekstova Na Muzejskoj IzložbiDženan DautovićNessuna valutazione finora

- Philippine Banking System: K, I2E.023G?3B.L3?I7Documento15 paginePhilippine Banking System: K, I2E.023G?3B.L3?I7Delica JaneyNessuna valutazione finora

- Divided States: Strategic Divisions in EU-Russia RelationsDa EverandDivided States: Strategic Divisions in EU-Russia RelationsNessuna valutazione finora

- Creativity and Change in Nigerian ChristianityDa EverandCreativity and Change in Nigerian ChristianityNessuna valutazione finora

- Cell Characterization ConceptsDocumento70 pagineCell Characterization Conceptshex0x1Nessuna valutazione finora

- CharFlo-Memory Compiler Tech Rev10.3-2010JuneDocumento33 pagineCharFlo-Memory Compiler Tech Rev10.3-2010Junevikramkolanu100% (1)

- Multi Cycle PathsDocumento15 pagineMulti Cycle PathsgpraveenroyNessuna valutazione finora

- Gmat Handbook: Everything You Need To Know and Agree To When Scheduling Your GMAT ExamDocumento17 pagineGmat Handbook: Everything You Need To Know and Agree To When Scheduling Your GMAT ExamGirish SeshadriNessuna valutazione finora

- BCD-to-Gray Code Converter . - Example Truth TableDocumento3 pagineBCD-to-Gray Code Converter . - Example Truth TableDen GuizzaganNessuna valutazione finora

- GATE 2016 How To Prepare For Electronics and Communication Engineering (ECE)Documento14 pagineGATE 2016 How To Prepare For Electronics and Communication Engineering (ECE)vikramkolanuNessuna valutazione finora

- RTL Vs Technology SchematicDocumento1 paginaRTL Vs Technology SchematicvikramkolanuNessuna valutazione finora

- BCD-to-Gray Code Converter . - Example Truth TableDocumento3 pagineBCD-to-Gray Code Converter . - Example Truth TableDen GuizzaganNessuna valutazione finora

- Yacoub-Ammar FSM CH 10Documento25 pagineYacoub-Ammar FSM CH 10Anubroto MitroNessuna valutazione finora

- UART Is A Asynchronous Transmission Protocol To Communicate Based On The Baud Ra TeDocumento1 paginaUART Is A Asynchronous Transmission Protocol To Communicate Based On The Baud Ra TevikramkolanuNessuna valutazione finora

- Exam Notice CGLE 12-02-2016Documento54 pagineExam Notice CGLE 12-02-2016Saicharan BashabathiniNessuna valutazione finora

- 1Documento2 pagine1Mahesh PandeyNessuna valutazione finora

- April 2004Documento15 pagineApril 2004vikramkolanuNessuna valutazione finora

- FlipflopsDocumento80 pagineFlipflopsvikramkolanuNessuna valutazione finora

- CDVL Application 2015Documento2 pagineCDVL Application 2015KaranGargNessuna valutazione finora

- SomiDocumento1 paginaSomivikramkolanuNessuna valutazione finora

- TimeDocumento1 paginaTimevikramkolanuNessuna valutazione finora

- CounterDocumento19 pagineCounterPayal SinghalNessuna valutazione finora

- Fundamentals of Computer Systems: Finite State MachinesDocumento32 pagineFundamentals of Computer Systems: Finite State Machinesjp_20_20Nessuna valutazione finora

- UnixDocumento3 pagineUnixvenitiaNessuna valutazione finora

- 001 Course OutlineDocumento35 pagine001 Course OutlineJubin JainNessuna valutazione finora

- 23 TrafficLightControllerDocumento3 pagine23 TrafficLightControllerKishore Kumar100% (1)

- 6htxhqwldo /RJLF, Psohphqwdwlrq $evwudfwlrq Ri 6Wdwh (OhphqwvDocumento13 pagine6htxhqwldo /RJLF, Psohphqwdwlrq $evwudfwlrq Ri 6Wdwh (OhphqwvakzeNessuna valutazione finora

- Working With Combinational Logic: SimplificationDocumento24 pagineWorking With Combinational Logic: SimplificationMain RizwanNessuna valutazione finora

- Career Objective:: M Agastya Srivatsav Mobile: +91-9491647647 E-MailDocumento2 pagineCareer Objective:: M Agastya Srivatsav Mobile: +91-9491647647 E-MailvikramkolanuNessuna valutazione finora

- Chp8 PDFDocumento15 pagineChp8 PDFRaffi SkNessuna valutazione finora

- State: Zero 1s Detected State: One 1 Detected State: Two 1s Detected State: Three 1s DetectedDocumento8 pagineState: Zero 1s Detected State: One 1 Detected State: Two 1s Detected State: Three 1s DetectedvikramkolanuNessuna valutazione finora

- Tocc DownDocumento19 pagineTocc DownvikramkolanuNessuna valutazione finora

- Object-Oriented Programming (OOP) Lecture No. 4Documento26 pagineObject-Oriented Programming (OOP) Lecture No. 4Muhammad ZeeshanNessuna valutazione finora

- Panel Check ListDocumento6 paginePanel Check ListSatheesh Kumar89% (44)

- Gati LimitedDocumento30 pagineGati Limitedthundercoder9288Nessuna valutazione finora

- Important Characterstics of 555 Timer IC: Circuits Based On 5555 ICDocumento6 pagineImportant Characterstics of 555 Timer IC: Circuits Based On 5555 ICManohar PotnuruNessuna valutazione finora

- OperatorsDocumento13 pagineOperatorsadfadfNessuna valutazione finora

- Administering A SQL Database Infrastructure-20764B-ENU-TrainerHandbook PDFDocumento530 pagineAdministering A SQL Database Infrastructure-20764B-ENU-TrainerHandbook PDFhungNessuna valutazione finora

- CSFBDocumento8 pagineCSFBmohamedNessuna valutazione finora

- FormSprint ManualDocumento208 pagineFormSprint Manualronny45Nessuna valutazione finora

- Qmodmanager log-SubnauticaZeroDocumento6 pagineQmodmanager log-SubnauticaZeroErwin R. PrasajaNessuna valutazione finora

- Mother BoardDocumento29 pagineMother BoardSwayamprakash PatelNessuna valutazione finora

- Autoscan DS MIX - ENDocumento4 pagineAutoscan DS MIX - ENc.palacios1510Nessuna valutazione finora

- De Thi Thu Vao THPT 2022 - Online 03.4.2022Documento5 pagineDe Thi Thu Vao THPT 2022 - Online 03.4.2022mai.nguyen.thi.phuongNessuna valutazione finora

- Class II, Type A2 Biosafety Cabinet: Operator'S ManualDocumento29 pagineClass II, Type A2 Biosafety Cabinet: Operator'S ManualDewiq ParuraNessuna valutazione finora

- AutocadDocumento17 pagineAutocadRaju Kumar GuptaNessuna valutazione finora

- BTech CSE SyllabusDocumento38 pagineBTech CSE SyllabusShubham ShendeNessuna valutazione finora

- Using Fast FormulaDocumento92 pagineUsing Fast FormulaRohit Singh100% (1)

- CAPM QuestionsDocumento49 pagineCAPM QuestionsrahimNessuna valutazione finora

- Patent OptimizerDocumento49 paginePatent Optimizer9716755397Nessuna valutazione finora

- Service Oriented ArchitectureDocumento418 pagineService Oriented ArchitectureTsiory HeriniavoNessuna valutazione finora

- Numark Mixtrack: (NKC4) Service ManualDocumento21 pagineNumark Mixtrack: (NKC4) Service ManualjoseNessuna valutazione finora

- B66273L Vol1Documento244 pagineB66273L Vol1sami belkhiria100% (1)

- Bukupanduan t300Documento60 pagineBukupanduan t300Riefal Al100% (1)

- Tableau - Online MaterialDocumento1.167 pagineTableau - Online MaterialGaneshNessuna valutazione finora

- Presented By:-: Temperature Controlled DC FanDocumento19 paginePresented By:-: Temperature Controlled DC FanAkash HalliNessuna valutazione finora

- Mine Blast AlgorithmDocumento21 pagineMine Blast Algorithmnarottam jangirNessuna valutazione finora

- Users of SRS DocumentDocumento1 paginaUsers of SRS DocumentDineshNessuna valutazione finora

- Einhell BC-BG 43 AsDocumento16 pagineEinhell BC-BG 43 AsCristiana LaviniaNessuna valutazione finora

- Takeuforward Org C Vector in C STLDocumento3 pagineTakeuforward Org C Vector in C STLDesi GamersNessuna valutazione finora

- 9.13 Surge Protection For PROFIBUS FMS, PROFIBUS DP, and Profibus PaDocumento4 pagine9.13 Surge Protection For PROFIBUS FMS, PROFIBUS DP, and Profibus PaRodrigoBurgosNessuna valutazione finora

- Machtelt Garrels Bash Guide For Beginners 2nd EdDocumento65 pagineMachtelt Garrels Bash Guide For Beginners 2nd EdZrkkrzNessuna valutazione finora