Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Spock: Power Serial I/O

Caricato da

Sanyi OcsaiDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Spock: Power Serial I/O

Caricato da

Sanyi OcsaiCopyright:

Formati disponibili

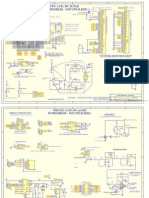

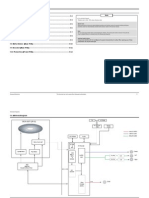

1

2 RNG0 RNG1

COUNT F CH-AB VCC VCC

Y1

Option 8MHz, 10MHz, 20MHz

F

PG0

SEL2 SEL1 SEL0

C5 104 R3

IO15 IO14 IO13 IO12 IO11 IO10 IO9 IO8 IO7 IO6 IO5 IO4 IO3 IO2 IO1 IO0 32 31 30 29 28 27 26 25 22 21 20 19 18 17 16 15 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 TRIG7 DD6 DD5 DD4 DD3 DD2 DD1 DD0

4MHz C1 20pF

GND GND

C2 20pF

U6

COUNT ZZ-CLK READ 20 27 22 CE WE OE A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 1 26 2 23 21 24 25 3 4 5 6 7 8 9 10 PG0 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 PG0 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 X 3 SI 10 9 8 7 6 5 4 3 44 43 42 41 40 39 38 37 2 36 DD7 24 14 33

U2

IO31 IO30 IO29 IO28 IO27 IO26 IO25 IO24 IO23 IO22 IO21 IO20 IO19 IO18 IO17 IO16 IN3 MODE/IN2 SDO/IN1 SDI/IN0 SCLK/Y2 Y1/RESET Y0 35 11

4K7

GND

U1 Channel A/B clock control D-DATA

1 2 3 4 GND 5 6 7 8 9 RA2 RA3 RA4 MCLR VSS RB0 RB1 RB2 RB3 RA1 18 17 16 15 14 13 12 11 10 E

SEL2 SEL1 SEL0 GND AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0

9 10 11 6 4 2 5 1 12 15 14 13

U4

C B A INH X7 X6 X5 X4 X3 X2 X1 X0

Range 1 Range 0

E VCC

C11 104

GND

AD3 AD0 AD1 AD2 AD4 AD6 AD7 AD5

19 18 17 16 15 13 12 11

Spock

PIC

RA0 CLKI CLKO VDD RB7 RB6 RB5 RB4

D7 D6 D5 D4 D3 D2 D1 D0

A-DATA SEL 0 SEL 1 SEL 2

____ store/read Serial In Serial Out ____ shift/count

5C2568

MAX4051

Scope BUS

U7

COUNT D ZZ-CLK READ 20 27 22 CE WE OE A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 1 26 2 23 21 24 25 3 4 5 6 7 8 9 10 PG0 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

ISPEN

13

VCC

PIC16F84

LSI-1016 U5

SEL2 SEL1 SEL0 GND TRIG7 DD6 DD5 DD4 DD3 DD2 DD1 DD0 9 10 11 6 4 2 5 1 12 15 14 13 C B A INH X7 X6 X5 X4 X3 X2 X1 X0 A-DATA D-DATA

____ shift/count ____ store/read R1

VCC

DD3 DD0 DD1 DD2 DD4 DD6 DD7 DD5

19 18 17 16 15 13 12 11

D7 D6 D5 D4 D3 D2 D1 D0

VCC

VCC

ZZ-CLK U3B 5 4 6 3 U3A

470R

VCC

4

R42 47K

3

2 1 74AHC86 U3D 13 6 VCC 5

R2 2K2

2 3

U8A

Q

D CLK

74AHC86

5C2568

MAX4051

Logic Analyser BUS

CL

R43 47K

11 GND

PR

12 74AHC86

R11 470R

74AHC74

VCC

U19

STOR

C54

GND

DIG-801

RNG1 RNG0 COUNT B STOR ZZ-CLK DD[0..7] RNG1 RNG0 COUNT STOR ZZ-CLK DD[0..7]

Interface

20pF

OUT

50MHz

8 Bit Logic Analyzer

POD-A POD-B

SER-I

SER-I

SER-O

SER-O

POWER SERIAL I/O

MCLR

MCLR

R4

B

2K2

C53 10n

2 4 6 8 10 VCC GND

JP1

VCC 1 3 5 7 9

A/D-401

RNG1 RNG0 CH-AB PG0 STOR ZZ-CLK ZZ-CLK* AD[0..7] RNG1 RNG0 PG1 PG0 STOR ZZ-CLK ZZ-CLK* AD[0..7]

pico-3.sch

POD-B POD-A

C6 104

GND GND

2 Channel Osilloscope

Modular ADC

isp-PIC

Normally Shorted GND

CNT-1 CNT-2

VDD

VCC

Designed by:- N.J.Jackson

Title

BitScope CPU and Storage Engine

Sheet 1 of 5

Rev 1

(C) N.J.Jackson 1998

1 2 3

pico-4.sch

4

pico-2.sch

5 6

A3

GND 7 VSS VEE

Document Number

17-Jul-1998

8

Date:

C:\NJJ\BITSCOPE\SCH\PICO-1.SCH

9

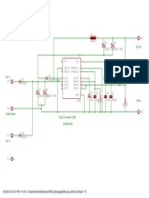

VRAW+

SOCKET P1

D1

R16

U9

1 IN G

7805

OUT 3 A+5

PV+

10V AC

10VAC - 12VAC

C14 104

1N4002

10R/DIODE

C15 1000uF

C17 104 L1 150uH

C19 100uF

C21 104

C23 104

Analogue Power

C16 470uF

C18 104 R17

C20 100uF

C22 104

G 1

C24 104

D2

E

PVGND

IN

OUT

A-5

1N4002

10R/DIODE

U10

7905

VRAW-

U11

1 IN G

7805

OUT 3 VCC

C3 1000uF

C25 104

2

C26 104

Digital

GND

C4 470uF

C55 104

2

C12 104

OUT 3 -5

Power

IN

VCC

VCC

U20

R12 2K2 P4

1 14 2 15 3 16 4 17 5 18

Q1

R6

SER-O

7905

BC558 R10 10K

10K

Rx Tx

SER-I

Tx

VCC

Rx

VCC

RESET

JP2

VCC

RS-232

B

6 19 7 20 8 21 9 22 10 23 11 24 12 25 13 GND GND GND GND GND

Q2 BC548 L2 150uH D7 1N4148

R7 4K7 LD2 RED LD1 GRN

R5 10K

MCLR

R9 1K0

R8 1K0

2 1

HEADER 2 C13 100nF

DB25-F

-5 A

VCC

VCC

VCC

C7 104

(C) N.J.Jackson 1998

1 2 3 4 5 6 GND

C8 104

GND

C9 104

GND 7

Designed by:- N.J.Jackson

Title

A3

BitScope Power Supply and Comms

Sheet 2 of 5

Rev 1

Document Number

17-Jul-1998

8

Date:

C:\NJJ\BITSCOPE\SCH\PICO-2.SCH

9

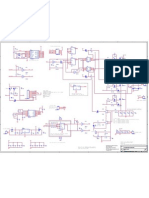

VCC E

RN1 - Typically 1M for minimum load - 10K, 47K for Active POD R18 4K7

VCC

1

FUSE1

VRAW+

500mA C28 1 +10V

D

P5

1 14 2 15 3 16 4 17 5 18 6 19 7 20 8 21 9 22 10 23 11 24 12 25 13

VCC

2 3 4 5 6 7 8 9 10

RN1

S I P 1 0 P I N

GND GND POD-A POD-B D

C30 104

+5 Logic 2 CHAN A 3 CHAN B

104

Logic Termination

Logic Pod

IO-1 IO-0 5 Logic 7 6 Logic 6 7 Logic 5 8 Logic 4 9 Logic 3 10 Logic 2 11 Logic 1 12 Logic 0

U12

2 3 4 5 6 7 8 9 D1 D2 D3 D4 D5 D6 D7 D8 C OC Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 19 18 17 16 15 14 13 12 DD7 DD6 DD5 DD4 DD3 DD2 DD1 DD0

13 -10V

C29 104

GND

11 1

DB25-M

74HC573

DD[0..7]

DD[0..7]

STOR

FUSE2

VRAWB

ZZ-CLK

500mA

1

4066

A

C

NOTE: For TTL Level Inputs substitute 74HCT573

13

U22A

RNG1

Analog switch provides control path for Intelligent POD device

4066

11 A

C

RNG0 B 10 COUNT

12

U22B

Designed by:- N.J.Jackson

Title

A3

BitScope Digital Capture

Sheet 3 of 5

Rev 1

Document Number

17-Jul-1998

8

(C) N.J.Jackson 1998

1 2 3 4 5 6 7

Date:

C:\NJJ\BITSCOPE\SCH\PICO-3.SCH

9

POD-A

R19

18K0

Range Buffer

A+5

x(4.583) Gain Buffer

A+5

ADC Buffer

(1.6667)

A+5 F

(4.8298) U14 R20 4K7

3

U15

3

1.20Vpp R38 220R

3

20K X5

C56

20pF

U16

v+

MAX477

6

v+

AD8048

6

v+

MAX477

6

2.00Vpp

POD-B

R22

20K X5

(4.8298)

E

18K0

v-

v-

v-

C57

20pF

A-5

A-5

D5 R37

D6

A-5

1N4148

1N4148

R40 220R R39 330R

E

R23

4K7

430R R35 120R

Logic Pod

U18 INPUT BUFFERS 1:1 R29 220R

12 14 15 11 1 5 2 4 6 10 9 X0 X1 X2 X3 Y0 Y1 Y2 Y3 INH A B X Y VDD VSS 13 3 16 8 A+5

C37 104 RV1 4K7 ZERO SET C27

7

Q5 BC558

C38 104

C39 10uF

2:1

D

R30 220R R31

VCC

Vertical Input

C

SIG-A

220R C52 R32 5:1 (5.273) 470R C69 cspeed R33 104

GND

VEE

A-5

A-5

10nF

CNT-2

MAX4052

Range Select

RNG1 RNG0

Buffers

110R

PG0 PG1 EVENT C

SIG-B

TP3

TP4

TP5 U13

14 15 A-IN VCCA

* SOCKET for ADC Adapter

AD[0..7] D8 D7 D6 D5 D4 D3 D2 D1 CLK OE OE OVER A-5 4 5 6 7 8 9 10 21 18 20 19 3 STOR AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 ZZ-CLK STOR AD[0..7]

DIV64

Analogue Source

U17

12 14 15 11 BNC-B BNC-A POD-B POD-A 1 5 2 4 6 10 9 X0 X1 X2 X3 Y0 Y1 Y2 Y3 INH A B X Y VDD VSS 13 3 16 8

A+5

SCALE ADJUST

JP3

VCC 1 2 3

MC10319 SMT ADC

pico-5.sch

RV2

A+5

24

CNT-1 B

C40 330R 104

C41 104

C42

VRT VRM VRB

zz-clk

ZZ-CLK* ZZ-CLK B

+

10uF

C43 104

1 23

CH-A

VCC

CH-B

VCC

CH-C

VCC

CH-D

VCC

VEE

13 A-5

VEE

MAX4052

* BNC/Pod

MC10319

LD3 YEL

LD4 YEL

LD5 YEL

LD6 YEL

CH-A/B

A+5 POD-B POD-A BNC-B BNC-A

R41

+

1K0

C44 1uF

C46 104 C47 104

C48 104 C49 104

C50 104 C51 104

A-5

Flash ADC

* NOTE:- SMT ADC chips may be mounted on 24 pin DIP PCB header Recommend AD9057, TLC5510, TLC5540

C45

Designed by:- N.J.Jackson

Title

A3

BitScope Analog Capture

SAMPLE

* NOTE:- Substitute 74HC4052 for slightly degraded performance.

(C) N.J.Jackson 1998

1 2 3 4 5 6

+

1uF

Sheet 4 of 5

Rev 1

Document Number

17-Jul-1998

8

Date:

C:\NJJ\BITSCOPE\SCH\PICO-4.SCH

9

A+5

A+5

C31 R25 10K

100pF

D8 1N4148 Q6 D9 1N4148 J309

Input Buffer

7 A+5

R26

Channel A

E

1M0

A-5

Q3 BC548

3

U23

v+

MAX477

6 SIG-A E

Q7 J309 J1 C32

4 2

vA+5 A-5

BNC DC

100nF

RV3 200R

C35 104

C61 1uF

C63 104 C64 104

A-5

S1 SPDT AC

A-5

C62

+

1uF

D A+5 A+5 A+5

C33 R27 10K

100pF

D10 1N4148 Q8 D11 1N4148 J309

C65 1uF

C67 104 C68 104

A-5

Input Buffer

7 A+5

C66

+

1uF

R28

Channel B

1M0

A-5

Q10 BC548

3

U24

v+

MAX477

6 SIG-B

Q9 J309 J2 C34 100nF DC S2 SPDT AC

B A-5 2

v-

BNC

RV4 200R

C36 104

A-5

VCC

VCC

1GHz Prescaler

U25 C59 S3 SPDT R21 50R

A 8

1nF 1nF

VCC

Q12 BC558

OUT+ 7

IN+

R24 150R

C58

100pF D3 1N4148 D4 1N4148

C60

div64

INGND OUT-

DIV64

MC12073

R34 5K6

R36 1K0

Designed by:- N.J.Jackson

Title

BitScope Channel Buffer Amplifiers

Sheet 5 of 5

Rev 1

GND

GND

A3

Document Number

17-Jul-1998

8

(C) N.J.Jackson 1998

1 2 3 4 5 6 7

Date:

C:\NJJ\BITSCOPE\SCH\PICO-5.SCH

9

Potrebbero piacerti anche

- Some Solutions To Enderton LogicDocumento16 pagineSome Solutions To Enderton LogicJason100% (1)

- OV7670 + AL422B (FIFO) Camera Module (V2.0) SchematicDocumento1 paginaOV7670 + AL422B (FIFO) Camera Module (V2.0) SchematicMuhammad Alfiansyah100% (3)

- Acdc - DC Motor - Lecture Notes 5Documento30 pagineAcdc - DC Motor - Lecture Notes 5Cllyan ReyesNessuna valutazione finora

- CSCI 123 - Final ExamDocumento15 pagineCSCI 123 - Final ExamBrianYoungNessuna valutazione finora

- Cable Schedule - Instrument - Surfin - Malanpur-R0Documento3 pagineCable Schedule - Instrument - Surfin - Malanpur-R0arunpandey1686Nessuna valutazione finora

- Ce Project 1Documento7 pagineCe Project 1emmaNessuna valutazione finora

- Hws 13642Documento3 pagineHws 13642dhieward100% (2)

- FPP3Documento1 paginaFPP3uzunku100% (1)

- DOP7Documento2 pagineDOP7Nghia Do100% (1)

- Caraca Node by Lancos 1.10: Claudio LanconelliDocumento2 pagineCaraca Node by Lancos 1.10: Claudio LanconelliMohamed Zayed100% (1)

- PT2314Documento4 paginePT2314Yamir Sandoval100% (1)

- Nex-Robotics 20x4 Serial LCD ModuleDocumento9 pagineNex-Robotics 20x4 Serial LCD ModuleAshok Kumar100% (1)

- Design and Functional Verification of I2C Master Core Using OVMDocumento6 pagineDesign and Functional Verification of I2C Master Core Using OVMPraveen Kumar100% (1)

- Schem AnticDocumento1 paginaSchem Anticthanhv_25100% (1)

- Aoc 2436saDocumento45 pagineAoc 2436saatomo33100% (1)

- PT2033Documento5 paginePT2033mite100% (1)

- PcbdesigningDocumento16 paginePcbdesigningPraveen Kumar Chitluri100% (1)

- ENEL3CA/DA: Electronic/Computer Design 1: PCB Philosophy and Design Using UltiboardDocumento43 pagineENEL3CA/DA: Electronic/Computer Design 1: PCB Philosophy and Design Using Ultiboardbknaruma100% (1)

- DMA Versus Polling or Interrupt Driven I/ODocumento13 pagineDMA Versus Polling or Interrupt Driven I/OCyrus Patrick Dacoco100% (1)

- USB Chip - Choices Jul2000Documento5 pagineUSB Chip - Choices Jul2000Jameskrazy100% (1)

- Ultrasonic Range Finder Using 8051Documento6 pagineUltrasonic Range Finder Using 8051Jason Hendricks100% (3)

- Embedded System and Design ReportDocumento86 pagineEmbedded System and Design ReportGulati Rohit100% (1)

- Document Mini Project No 1.117Documento8 pagineDocument Mini Project No 1.117rahmat100% (1)

- PIC Tutorial 3Documento10 paginePIC Tutorial 3api-3801984100% (3)

- List IC Maxim DallasDocumento2 pagineList IC Maxim DallasFudin Safudin100% (1)

- An-960 RS 485 Incl Termination DetailsDocumento12 pagineAn-960 RS 485 Incl Termination Detailsqafqgibsonq4543100% (1)

- PT2312 SDocumento4 paginePT2312 SPlasticos Fatec100% (1)

- Modbus Protocol UGDocumento33 pagineModbus Protocol UGMuhammad Sa'ad100% (1)

- Distance CounterDocumento4 pagineDistance Counterkvamsee112100% (1)

- 8086 PPTDocumento30 pagine8086 PPTKavitha Subramaniam100% (1)

- Agribot Project PresentationDocumento21 pagineAgribot Project Presentationumaiya1990100% (1)

- Sel ProdDocumento70 pagineSel Prodnad2702100% (1)

- VCC GND: Simple Dds - Based Signal GeneratorDocumento1 paginaVCC GND: Simple Dds - Based Signal GeneratorM'hamed Klouz100% (1)

- More On SQLDocumento29 pagineMore On SQLrahuldhole33100% (2)

- Guia Basica de Ejercicios-ProtonDocumento59 pagineGuia Basica de Ejercicios-ProtonFatality Joseph100% (1)

- L296 SchematicDocumento1 paginaL296 SchematicmyEbooks100% (1)

- 4.6.2 Universal Serial Bus (USB)Documento18 pagine4.6.2 Universal Serial Bus (USB)kollavivek_534195858100% (2)

- CircuitDocumento1 paginaCircuitShahid Naseem100% (1)

- PT2313L PDFDocumento3 paginePT2313L PDFMaugrys Castillo100% (1)

- Hobby Servo Motor Control Via PIC Pulse Width Modulation: Nathan Markey April 4, 2003Documento7 pagineHobby Servo Motor Control Via PIC Pulse Width Modulation: Nathan Markey April 4, 2003Luciana Gutierrez Salazar100% (1)

- IrsolwibDocumento4 pagineIrsolwibleko17100% (2)

- Nec Ir For PicDocumento14 pagineNec Ir For Picsudhakar5472100% (1)

- Sg8V1 Programing Schematic: IC Design Research & Education CenterDocumento1 paginaSg8V1 Programing Schematic: IC Design Research & Education CenterKit Vi Điều Khiển100% (1)

- Schematic Diagrams: Special NoteDocumento12 pagineSchematic Diagrams: Special NoteAlexandre S. Corrêa100% (1)

- Bascom and AVR, RS-232Documento10 pagineBascom and AVR, RS-232akbar100% (1)

- Interfacing Example - 16 Character X 2 Line LCD: DescriptionDocumento5 pagineInterfacing Example - 16 Character X 2 Line LCD: DescriptionManish Kumar sharma100% (1)

- Aerosemi: Features ApplicationsDocumento9 pagineAerosemi: Features Applicationsttnaing100% (1)

- History of The I2C BusDocumento24 pagineHistory of The I2C BusManoj Kavedia100% (1)

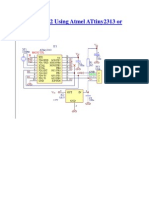

- USB-to-RS232 Using Atmel ATtiny2313 or ATmega8Documento4 pagineUSB-to-RS232 Using Atmel ATtiny2313 or ATmega8mikcomi100% (1)

- Schematic1 - Page1Documento1 paginaSchematic1 - Page1Sajid Baloch100% (1)

- 001-57294 AN57294 USB 101 An Introduction To Universal Serial Bus 2.0Documento57 pagine001-57294 AN57294 USB 101 An Introduction To Universal Serial Bus 2.0Arturo Picolin100% (1)

- Introduction I2c and SPIDocumento14 pagineIntroduction I2c and SPIHaris Jeelani100% (1)

- CAN DemoDocumento1 paginaCAN DemoTrí Nguyễn100% (1)

- Up & Down CounterDocumento3 pagineUp & Down Counteraudio video100% (1)

- PIC PPT 13104022 (4th Year)Documento41 paginePIC PPT 13104022 (4th Year)Daman Deep Singh100% (1)

- PT2312E SDocumento5 paginePT2312E Sguillecompaq100% (1)

- Dead TimeDocumento1 paginaDead Timebuiphuoclai100% (1)

- LCD - GDM1602BDocumento10 pagineLCD - GDM1602BElanio Julio100% (1)

- Noblex - RCD - 138Documento8 pagineNoblex - RCD - 138pablo190381Nessuna valutazione finora

- MMB0 RevC SchematicDocumento1 paginaMMB0 RevC SchematicbiotekyNessuna valutazione finora

- Mach Ngly Sim300czDocumento2 pagineMach Ngly Sim300czViet Bui QuocNessuna valutazione finora

- Labx 1 SCHDocumento2 pagineLabx 1 SCHercervantesNessuna valutazione finora

- LAB-X1 SchematicDocumento2 pagineLAB-X1 SchematicRenato MirandaNessuna valutazione finora

- Bs11 3Documento1 paginaBs11 3Sanyi OcsaiNessuna valutazione finora

- Bit SopeDocumento4 pagineBit SopeSanyi OcsaiNessuna valutazione finora

- Programmer'S Manual: BitscopeDocumento20 pagineProgrammer'S Manual: BitscopeSanyi OcsaiNessuna valutazione finora

- Bs11 5Documento1 paginaBs11 5Sanyi OcsaiNessuna valutazione finora

- Bs11 4Documento1 paginaBs11 4Sanyi OcsaiNessuna valutazione finora

- Bs11 3Documento1 paginaBs11 3Sanyi OcsaiNessuna valutazione finora

- Bs11 2Documento1 paginaBs11 2Sanyi OcsaiNessuna valutazione finora

- Car Section 2 Series (H) Part-IiDocumento6 pagineCar Section 2 Series (H) Part-Iipandurang nalawadeNessuna valutazione finora

- Debate Lesson PlanDocumento3 pagineDebate Lesson Planapi-280689729Nessuna valutazione finora

- Conference Paper 2Documento5 pagineConference Paper 2Sri JayanthNessuna valutazione finora

- Project 4 Close TestDocumento7 pagineProject 4 Close TestErika MolnarNessuna valutazione finora

- Hospital Furniture: Project Profile-UpdatedDocumento7 pagineHospital Furniture: Project Profile-UpdatedGaurav GuptaNessuna valutazione finora

- Perbandingan Implementasi Smart City Di Indonesia: Studi Kasus: Perbandingan Smart People Di Kota Surabaya Dan Kota MalangDocumento11 paginePerbandingan Implementasi Smart City Di Indonesia: Studi Kasus: Perbandingan Smart People Di Kota Surabaya Dan Kota Malanglely ersilyaNessuna valutazione finora

- Diffrent Types of MapDocumento3 pagineDiffrent Types of MapIan GamitNessuna valutazione finora

- Leadership Nursing and Patient SafetyDocumento172 pagineLeadership Nursing and Patient SafetyRolena Johnette B. PiñeroNessuna valutazione finora

- Modicon PLC CPUS Technical Details.Documento218 pagineModicon PLC CPUS Technical Details.TrbvmNessuna valutazione finora

- 009 Attached-1 NAVFAC P-445 Construction Quality Management PDFDocumento194 pagine009 Attached-1 NAVFAC P-445 Construction Quality Management PDFSor sopanharithNessuna valutazione finora

- Day 2 - Evident's Official ComplaintDocumento18 pagineDay 2 - Evident's Official ComplaintChronicle Herald100% (1)

- Volvo HU 803Documento8 pagineVolvo HU 803GiegloNessuna valutazione finora

- Real Options BV Lec 14Documento49 pagineReal Options BV Lec 14Anuranjan TirkeyNessuna valutazione finora

- Busbusilak - ResearchPlan 3Documento4 pagineBusbusilak - ResearchPlan 3zkcsswddh6Nessuna valutazione finora

- 10 - SHM, Springs, DampingDocumento4 pagine10 - SHM, Springs, DampingBradley NartowtNessuna valutazione finora

- Consequences of Self-Handicapping: Effects On Coping, Academic Performance, and AdjustmentDocumento11 pagineConsequences of Self-Handicapping: Effects On Coping, Academic Performance, and AdjustmentAlliah Kate SalvadorNessuna valutazione finora

- Bleed Valve FunctionDocumento7 pagineBleed Valve FunctionUWT10Nessuna valutazione finora

- Editorial WritingDocumento38 pagineEditorial WritingMelanie Antonio - Paino100% (1)

- Sunrise - 12 AB-unlockedDocumento81 pagineSunrise - 12 AB-unlockedMohamed Thanoon50% (2)

- MT Im For 2002 3 PGC This Is A Lecture About Politics Governance and Citizenship This Will HelpDocumento62 pagineMT Im For 2002 3 PGC This Is A Lecture About Politics Governance and Citizenship This Will HelpGen UriNessuna valutazione finora

- Master Thesis On Smart GridDocumento6 pagineMaster Thesis On Smart Gridsandraandersondesmoines100% (2)

- Operation ManagementDocumento4 pagineOperation ManagementHananiya GizawNessuna valutazione finora

- 3 - Risk Opportunity RegisterDocumento4 pagine3 - Risk Opportunity RegisterArmando CorboNessuna valutazione finora

- EHVACDocumento16 pagineEHVACsidharthchandak16Nessuna valutazione finora

- What Is Public RelationsDocumento52 pagineWhat Is Public RelationsMarwa MoussaNessuna valutazione finora